# 1.0 Product Description

## 1.1 Overview

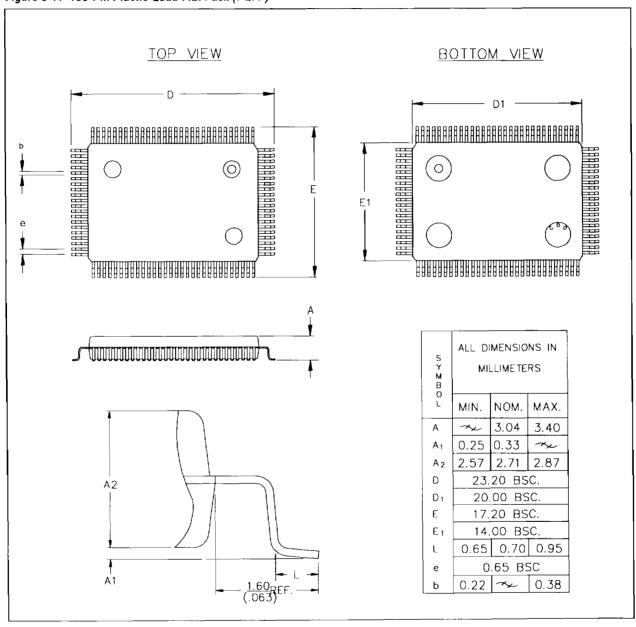

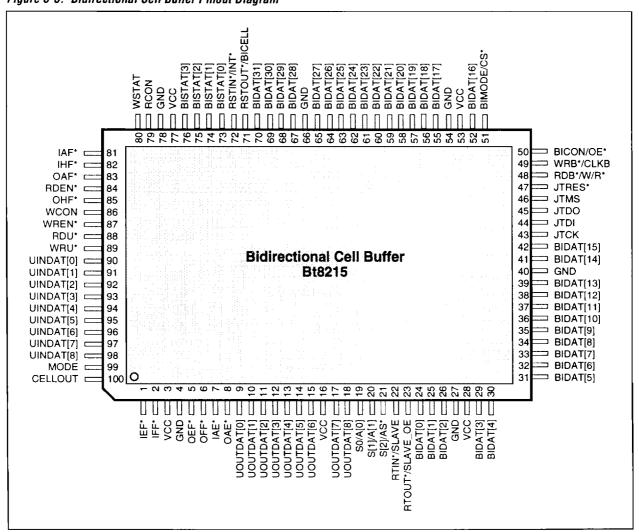

The Bt8215 is a bidirectional buffer with a 36-bit bidirectional port and 9-bit unidirectional ports that can be configured to transfer fixed-length cells. Each direction can store up to 512 36-bit words. This part, therefore, replaces eight unidirectional FIFOs and associated control circuitry for communication between asynchronous byte-wide ports, a 32-bit-wide processor, or other synchronous systems. This product is designed as a single CMOS integrated circuit, packaged in a 100-pin Plastic Quad Flat Pack (PQFP).

The bidirectional port reads data from the input buffer and writes data to the output buffer. Each port can be programmed to be synchronous or asynchronous. The bidirectional port can also be configured to connect directly to a microprocessor. Buffer status indications include empty, full, almost-full, almost-empty and half-full flags. A padding function that controls unidirectional reading and writing of data blocks that do not end on a word boundary is available.

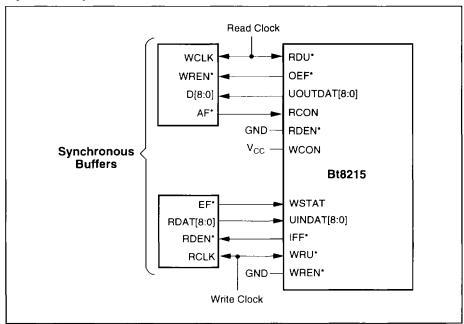

The product can autonomously control catalog synchronous or asynchronous buffers (FIFOs) to increase buffer depth at a reduced cost. No additional circuitry other than the generic FIFO is required to implement a deeper buffer. The generic FIFOs can be cascaded among themselves for even greater depth. The Bt8215 also has the ability to autonomously transfer data to the unidirectional port of another Bt8215 buffer. The unidirectional port can be configured to interface with Brooktree's Bt8222 ATM/PLCP and Bt8330 HDLC formatter chips and also with an AMD TAXI® chip.

There are two principal modes of operation for this product: stand-alone smart FIFO mode and microprocessor mode. In stand-alone smart FIFO mode, the bidirectional port has a common buffer interface. In microprocessor mode, features are controlled through a microprocessor control register, including fixed-size cell formatting and delineation as well as additional parity operations. Also, microprocessor mode supports a cell mode that allows cell headers to be read and written and the cell data to be burst read or burst written. This reduces the processing power needed in the processor to transfer cells.

### 1.2 Brief Block Description

## 1.2 Brief Block Description

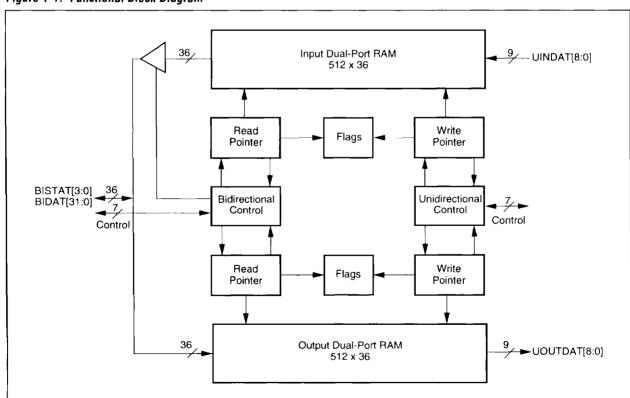

A block diagram of the bidirectional cell buffer is shown in Figure 1-1. Each 512 x 36 dual-port RAM bank has an associated read and write pointer and flag circuitry. The read and write pointers are sequentially incremented on read and write operations, respectively. The pointers are 9 bits wide to cover the address range of the dual-port RAM. The flag circuitry compares the flags to determine empty, almost-empty, half-full, almost-full, and full conditions.

The unidirectional control block controls read and write pointers, flags, and strobe outputs for the unidirectional port, and supports padding and cascade operations. The unidirectional interface operates with synchronous or asynchronous timing operation, and supports a parity check/generate operation in microprocessor mode.

The bidirectional control block controls the read and write pointers, flags, and strobes for the bidirectional port. It supports either the stand-alone smart FIFO mode or the microprocessor mode. The bidirectional interface supports synchronous or asynchronous timing operation in the stand-alone smart FIFO mode and a dedicated synchronous processor interface in the microprocessor mode.

Control of features is performed through input pins in the stand-alone smart FIFO mode and through control registers in the microprocessor mode.

Figure 1-1. Functional Block Diagram

2 Brooktree<sup>x</sup>

# 2.0 Stand-Alone Smart FIFO Mode

## 2.1 System Overview

Stand-alone smart FIFO mode provides a basic buffer interface for the bidirectional port. Several clocking schemes and multiple interface options are available for connecting unidirectional byte-wide signals to a bidirectional 32-bit interface. The buffer absorbs timing differences and can pack an odd number of bytes into a 32-bit word format. Figure 2-1 illustrates a block diagram of the Bt8215.

## 2.1 System Overview

Figure 2-1. Stand-Alone Smart FIFO Mode Block Diagram

2.2 Pin Descriptions

## 2.2 Pin Descriptions

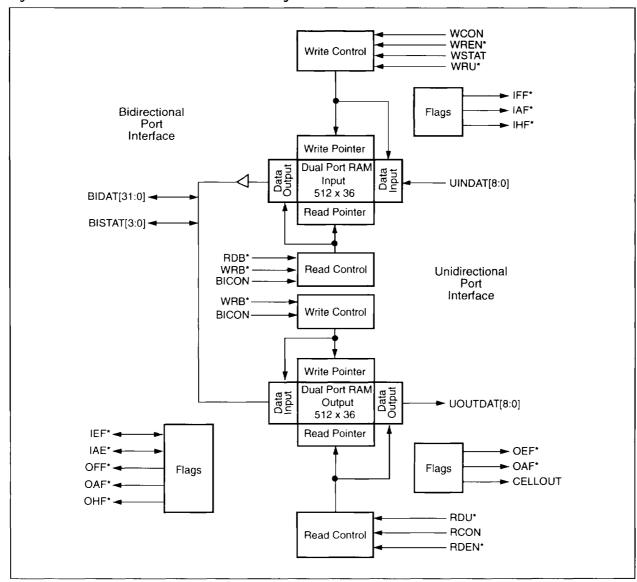

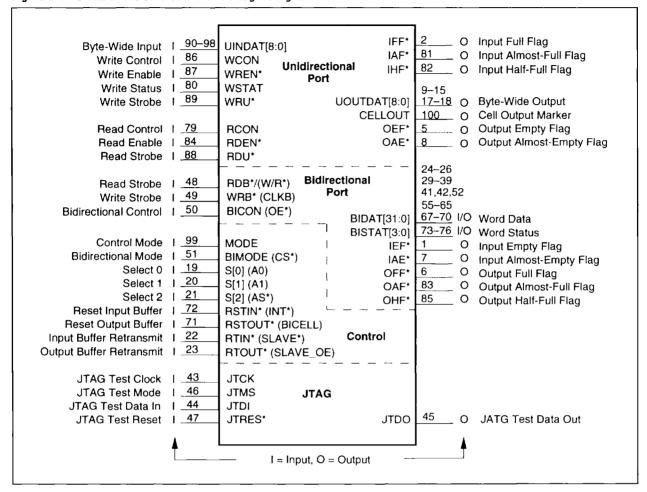

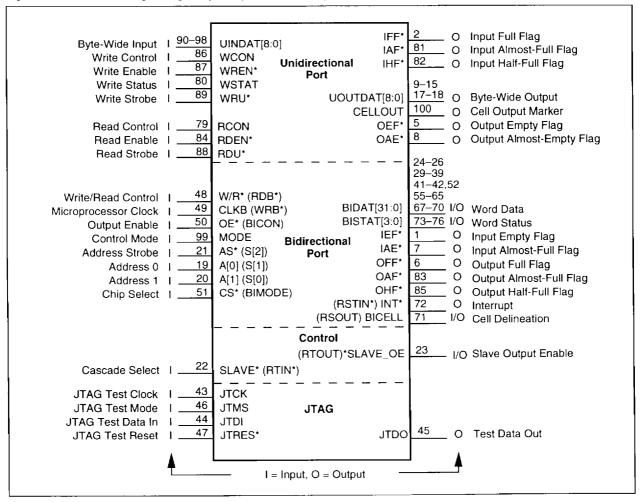

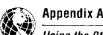

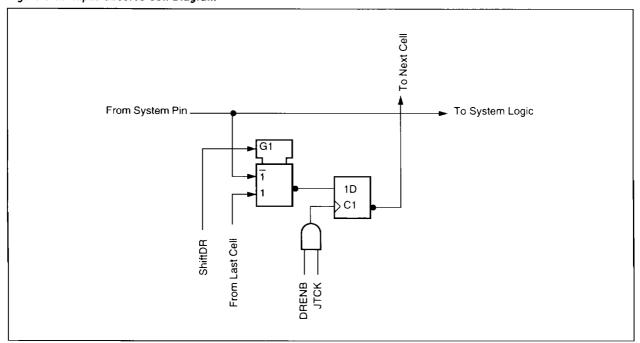

A functionally partitioned logic diagram of the bidirectional cell formatter in stand-alone smart FIFO mode is shown in Figure 2-2. The unidirectional port inputs and outputs are shown at the top of the diagram. The inputs to this interface consist of byte-wide input (UINDAT), write control signals (WCON, WREN\*, WSTAT, and WRU\*), and read control signals (RCON, RDEN\*, and RDU). The outputs from the unidirectional byte-wide port are cell markers and full, almostfull, half-full, almost-empty, and empty flags.

The bidirectional interface consists of input strobes to initiate read and write operations and a single control lead. Bidirectional pins provide 32 bits of data and 4 status bits. Output pins are provided for flags.

All control in stand-alone smart FIFO mode is hard-wired. There are retransmit controls for the input and output buffers, five control inputs, and one reset for each of the input and output buffers. To select stand-alone smart FIFO mode, the MODE input must be a logic low. The bidirectional port modes are selected through the BIMODE input; unidirectional port modes are selected through inputs S[0], S[1], and S[2]. The input buffer read and write pointers are reset by a logic low on RSTIN\* and the output buffer pointers are reset by a logic low on RSTOUT\*. The RTIN\* input will asynchronously reset the input buffer read pointer to the physical beginning of the buffer. The RTOUT\* input will asynchronously reset the output buffer read pointer to the beginning of the output buffer. Table 2-1 gives the pin descriptions, labels, and I/O assignments for the standalone smart FIFO mode.

### 2.2 Pin Descriptions

Figure 2-2. Stand-Alone Smart FIFO Mode Logic Diagram

Table 2-1. Hardware Signal Definitions—Stand-Alone Smart FIFO Mode (1 of 2)

|                     | Pin Label               | Signal Name                 | 1/0 | Definition                                                                                                                                 |

|---------------------|-------------------------|-----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

|                     | MODE                    | Control Mode                | 1   | Set to a logic low to select stand-alone smart FIFO mode.                                                                                  |

|                     | BIMODE (CS*)            | Bidirectional Mode          | ı   | Selects the bidirectional port modes. A logic low selects the asynchronous timing operation while a logic high selects synchronous timing. |

|                     | S[2:0] (A[1,0],<br>AS*) | Select[2:0]                 | I   | Selects the unidirectional port modes. Refer to Table 2-3                                                                                  |

| Control Signals     | RSTIN* (INT*)           | Reset Input Buffer          | I   | An active-low input that resets the input buffer read and write pointers.                                                                  |

| Control             | RSTOUT*<br>(BICELL)     | Reset Output Buffer         | I   | An active-low input that resets the output buffer read and write pointers.                                                                 |

|                     | RTIN* (SLAVE*)          | Retransmit Input Buffer     | -   | An active-low input that asynchronously resets the input buffer read pointer to the physical beginning of the input buffer.                |

|                     | RTOUT*<br>(SLAVE_OE)    | Retransmit Output<br>Buffer | I   | An active-low input that asynchronously resets the output buffer read pointer to the physical beginning of the output buffer.              |

|                     | RCON                    | Read Control                | 1   | Provides control of the unidirectional output port.                                                                                        |

|                     | RDEN*                   | Read Enable                 | ı   | An active-low input that enables reading of the unidirectional output port.                                                                |

|                     | RDU*                    | Read Strobe                 | ı   | Clocks the unidirectional output port.                                                                                                     |

|                     | WRU*                    | Write Strobe                | 1   | Clocks the unidirectional input port.                                                                                                      |

|                     | WSTAT                   | Write Status                | 1   | Provides control of the unidirectional input port.                                                                                         |

| or                  | WREN*                   | Write Enable                | I   | An active-low input that enables writing of the unidirectional input port.                                                                 |

| Unidirectional Port | WCON                    | Write Control               | 1   | Provides control of the unidirectional input port.                                                                                         |

| rectio              | UINDAT[8:0]             | Byte-Wide Input             | ı   | The unidirectional byte-wide input data.                                                                                                   |

| Jaid                | IFF*                    | Input Full Flag             | 0   | Provides full status for the input buffer.                                                                                                 |

| -                   | IAF*                    | Input Almost-Full Flag      | 0   | Provides almost-full status for the input buffer.                                                                                          |

| ]                   | IHF*                    | Input Half-Full Flag        | 0   | Provides half-full status for the input buffer.                                                                                            |

|                     | OAE*                    | Output Almost-Empty<br>Flag | 0   | Provides almost-empty status for the output buffer.                                                                                        |

|                     | OEF*                    | Output Empty Flag           | 0   | Provides empty status for the output buffer.                                                                                               |

|                     | CELLOUT                 | Cell Output                 | 0   | Used as a TAXI interface transmit strobe.                                                                                                  |

|                     | UOUTDAT[8:0]            | Byte-Wide Output            | 0   | The unidirectional byte-wide output data.                                                                                                  |

### 2.2 Pin Descriptions

Table 2-1. Hardware Signal Definitions—Stand-Alone Smart FIFO Mode (2 of 2)

| -                  | Pin Label       | Signal Name                  | 1/0 | Definition                                                                                                                      |

|--------------------|-----------------|------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------|

|                    | RDB* (W/R*)     | Read Strobe                  |     | Used as a read strobe in asynchronous timing operation and as a read enable in synchronous mode.                                |

|                    | WRB*(CLKB)      | Write Strobe                 | I   | Used as a write strobe in asynchronous timing mode. In synchronous timing mode, this pin is used as a bidirectional port clock. |

| 핕                  | BICON (OE*)     | Bidirectional Control        | 1   | Not used in asynchronous timing mode, and should be tied low. Used as a write enable in synchronous timing mode.                |

| Bidirectional Port | OHF*            | Output Half-Full Flag        | 0   | Provides half-full status for the output buffer.                                                                                |

| ction              | OAF*            | Output Almost-Full Flag      | 0   | Provides almost-full status for the output buffer.                                                                              |

| idire              | OFF*            | Output Full Flag             | 0   | Provides full status for the output buffer.                                                                                     |

| <b></b>            | IAE*            | Input Almost-Empty<br>Flag   | 0   | Provides almost-empty status for the input buffer.                                                                              |

|                    | IEF*            | Input Empty Flag             | 0   | Provides empty status for the input buffer.                                                                                     |

|                    | BISTAT[3:0]     | Bidirectional Word<br>Status | 1/0 | Provides a status bit for each byte on BIDAT[31:0].                                                                             |

|                    | BIDAT[31:0]     | Bidirectional Data Word      | 1/0 | The bidirectional 32-bit wide data bus.                                                                                         |

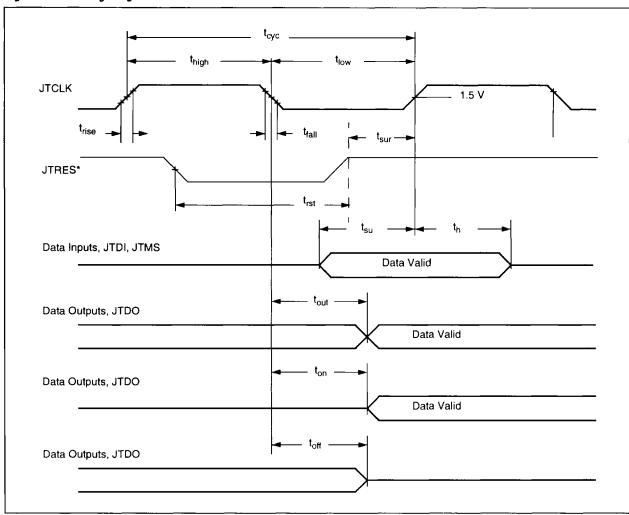

|                    | JTCK            | JTAG Test Clock              |     | The test clock input.                                                                                                           |

|                    | JTMS            | JTAG Test Mode               | 1   | A serial command input that sets up various JTAG tests.                                                                         |

| JTAG               | JTDI            | JTAG Test Data In            | 1   | The JTAG serial data input.                                                                                                     |

| 5                  | JTRES*          | JTAG Test Reset              | 1   | An active-low signal that asynchronously resets the JTAG test circuitry.                                                        |

|                    | JTDO            | JTAG Test Data Out           | 0   | The JTAG serial data output.                                                                                                    |

| 9                  | V <sub>CC</sub> | Supply Voltage               | _   | Five pins are provided for power.                                                                                               |

| VCC and GND        | GND             | Ground                       | _   | Six pins are provided for ground.                                                                                               |

## 2.3 Bidirectional Port Control

The bidirectional port has two interface timing selections: asynchronous and synchronous. A logic low on the BIMODE input selects asynchronous timing operation. In this case, reading and writing are controlled by the use of strobes, providing identical operation to that of conventional buffers. With synchronous timing, reading and writing are controlled by a clock input and enable control signals on the input pins. Table 2-2 gives the pin functionality for both timing functions. This mode provides a full complement of buffer status flags. These flag indications provide empty and full status for the input and output buffers.

Table 2-2. Bidirectional Mode Selection

| BIMODE           | RDB*        | WRB*         | BICON        |

|------------------|-------------|--------------|--------------|

| 0 = Asynchronous | Read Strobe | Write Strobe | 0(1)         |

| 1 = Synchronous  | Read Enable | Clock        | Write Enable |

Notes: (1). BICON is not used as a signal input and should be grounded for asynchronous timing operation

## 2.3.1 Asynchronous Timing Operation

Asynchronous timing operation is provided for both reading from and writing to the bidirectional port. Since this port is bidirectional, the read and write operations cannot be active at the same time, except to transfer data from the input buffer to the output buffer. Detailed timing specifications for guard time between read and write operations are given in Chapter 5.0.

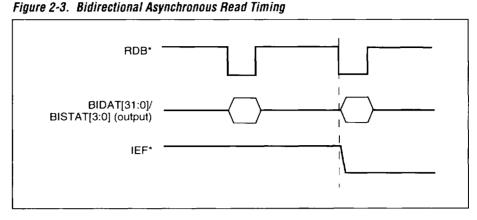

The read cycle begins when RDB\* goes to a low state. The BIDAT[31:0] and BISTAT[3:0] buses are driven as outputs and the data being read becomes valid. The rising edge of RDB\* clocks the output buffer read pointer and disables the BIDAT[31:0] and BISTAT[3:0] buses. When the last location of the input buffer containing data is read, IEF\* goes active on the falling edge of RDB\* and inhibits further reading of the input buffer.

A functional timing diagram for this operation is shown in Figure 2-3, where the input buffer empty flag is active on the second read operation.

IEF\* goes high after an input buffer write operation from the byte-wide port to a 36-bit boundary. This occurs when either 4 bytes have been written to the input buffer or a padding operation has been performed at the byte-wide port. A read cycle can start while IEF\* is active, thus decreasing the read on empty time. While IEF\* is active, RDB\* can be applied. Upon a valid write, data is present at BIDAT[31:0] and IEF\* goes high. The read cycle can then be completed by setting RDB\* high.

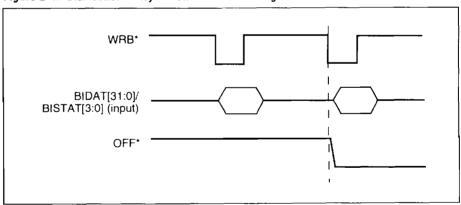

Bidirectional Port Control

As shown in Figure 2-4, the write cycle begins when WRB\* goes to a low state. Setup of the data on BIDAT[31:0] and BISTAT[3:0] to the buffer starts when WRB\* is low. On the rising edge of WRB\*, the data is stored in the buffer and the write pointer is incremented. The full flag, OFF\*, goes active on the falling edge of WRB\* when writing to the last available memory location of the output buffer. While OFF\* is active, writing to the output buffer is inhibited. The output buffer full flag is shown going active after the second write operation.

OFF\* goes inactive when a word has been read from the output buffer. A write cycle can start while OFF\* is active. WRB\* is applied while OFF\* is active. Upon a valid read, OFF\* will go inactive and WRB\* can then go high to clock data into the buffer.

Data can be transferred from the input buffer to the output buffer by operating WRB\* and RDB\* together. Data should not be applied to the bidirectional data port when this operation is taking place.

Figure 2-4. Bidirectional Asynchronous Write Timing

## 2.3.2 Synchronous Timing Operation

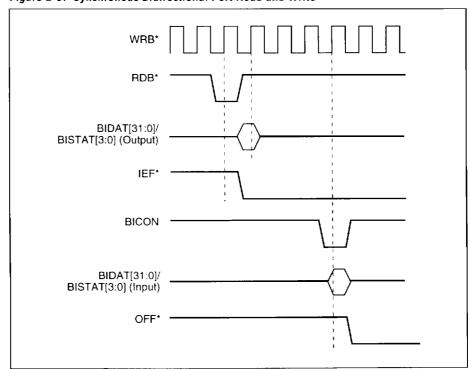

In synchronous timing operation, reading and writing are controlled by enable signals and a common clock. This function allows connection of the bidirectional port to a Reduced Instruction Set Computer (RISC) microprocessor or other statemachine implementation.

A read operation is performed by setting RDB\* low before the clock cycle for which the read is to be performed. When RDB\* is sampled low by the rising edge of the clock on WRB\*, the port is enabled and valid data is applied to the bus. If the last location of the input buffer is being read, then IEF\* will go low and the data from the last location will be valid. After a word write to the input buffer, IEF\* will go high on the next rising edge of the clock. While IEF\* is low, reading of the input buffer is inhibited; read-enable signals will be ignored.

Data on BIDAT[31:0] is written to the output buffer when BICON is sampled low on a rising edge of the clock signal on WRB\*. This also increments the write pointer. The full flag, OFF\*, goes active on the rising edge of the clock during a write to the last available location of the output buffer. While OFF\* is active, writing to the output buffer is inhibited. OFF\* goes inactive on the rising edge of WRB\* after a word read from the output buffer.

Figure 2-5 shows a read operation followed by a write operation, with each function initiating flags. RDB\* and BICON can be low on the same clock cycle, resulting in a write on that clock cycle and a read on the following cycle.

Figure 2-5. Synchronous Bidirectional Port Read and Write

### **Bidirectional Port Control**

### 2.3.3 Bidirectional Almost-Empty, Almost-Full, and Half-Full Flags

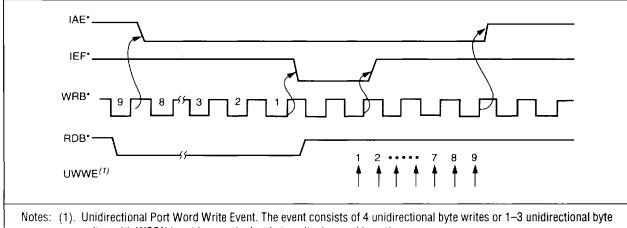

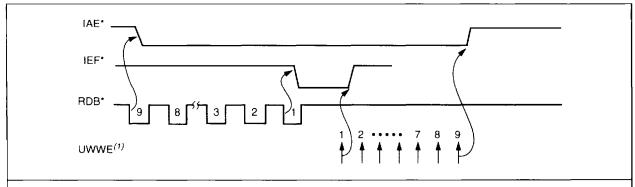

IAE\* provides almost-empty status for the input buffer. The offset is preset at eight words for the stand-alone smart FIFO mode. Flag timing depends on the port timing. The flag goes active in conjunction with a read of the input buffer. If the reading port is synchronous, the flag goes active on the rising edge of the read clock (see Figure 2-6). If it is asynchronous, it goes active when the read strobe goes low (see Figure 2-7). Similarly, the flag goes inactive in conjunction with a write of the buffer. It goes inactive in response to either the rising edge of a write strobe in asynchronous operation or the rising edge of the read clock input following a write operation in synchronous mode. Transitions of the flag only occur on word boundaries.

Figure 2-6. IAE\* Synchronous Operation

writes with WCON input low on the last byte write, i.e., pad insertion.

Figure 2-7. IAE\* Asynchronous Operation

Notes: (1). Unidirectional Port Word Write Event. The event consists of 4 unidirectional byte writes or 1-3 unidirectional byte writes with WCON input low on the last byte write, i.e., pad insertion.

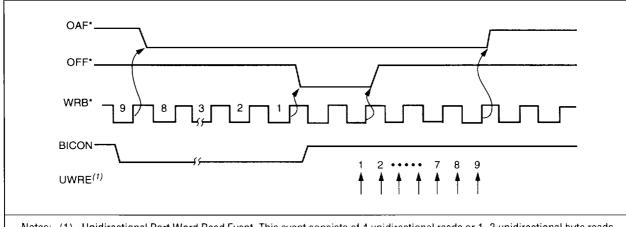

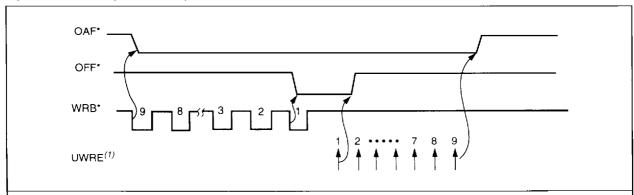

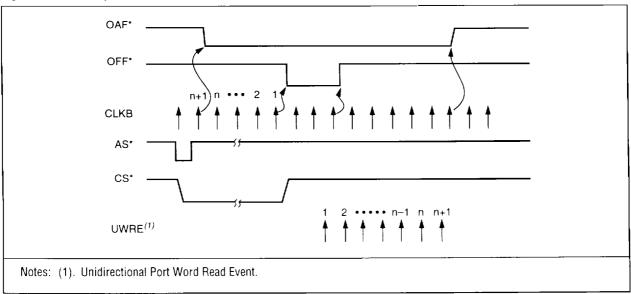

OAF\* provides almost-full status for the output buffer. The offset is preset at eight words for the stand-alone smart FIFO mode. Flag timing depends on the port timing. The flag goes active in conjunction with a write of the output buffer. If the writing port is synchronous, the flag goes active on the rising edge of the write clock (see Figure 2-8). If it is asynchronous, it goes active when the write strobe goes low (see Figure 2-9). Similarly, the flag goes inactive in conjunction with a read of the buffer in response to either the rising edge of a read strobe in asynchronous operation or the rising edge of the write clock input following a read operation in synchronous mode. Transitions of the flag only occur on word boundaries.

Figure 2-8. OAF\* Synchronous Operation

Notes: (1). Unidirectional Port Word Read Event. This event consists of 4 unidirectional reads or 1–3 unidirectional byte reads with RCON input low on last byte read, i.e., pad extraction.

Figure 2-9. OAF\* Asynchronous Operation

Notes: (1). Unidirectional Port Word Read Event. This event consists of 4 unidirectional reads or 1–3 unidirectional byte reads with RCON input low on last byte read, i.e., pad extraction.

### 2.3 Bidirectional Port Control

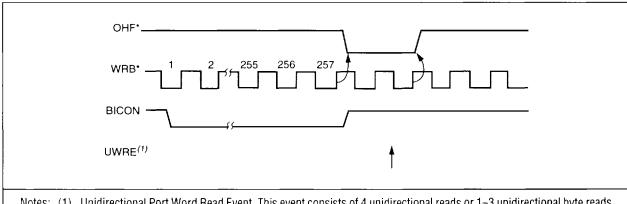

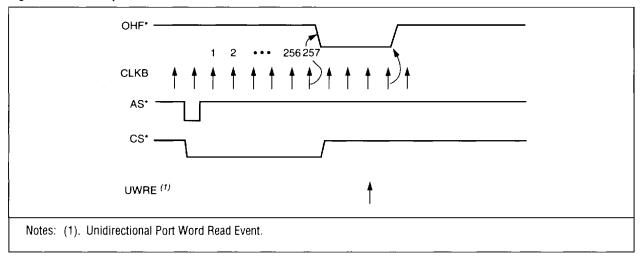

OHF\* provides half-full status for the output buffer. An active flag indicates that the output buffer is greater than half full. Flag timing depends on the port timing. The flag goes active in conjunction with a write of the buffer. If the writing port is synchronous, the flag goes active on the rising edge of the write clock (see Figure 2-10). If it is asynchronous, it goes active when the write strobe goes low (see Figure 2-11). Similarly, the flag goes inactive in conjunction with a read of the buffer. It goes inactive in response to either the rising edge of a read strobe in asynchronous timing operation or the rising edge of the write clock input following a read operation in synchronous mode. Transitions of the flag only occur on word boundaries.

Figure 2-10. OHF\* Synchronous Operation

Notes: (1). Unidirectional Port Word Read Event. This event consists of 4 unidirectional reads or 1–3 unidirectional byte reads with RCON input low on last byte read, i.e., pad extraction.

Figure 2-11. OHF\* Asynchronous Operation

Notes: (1). Unidirectional Port Word Read Event. This event consists of 4 unidirectional reads or 1–3 unidirectional byte reads with RCON input low on last byte read, i.e., pad extraction.

14 Brooktree<sup>\*</sup>

In the stand-alone smart FIFO mode, the unidirectional port can operate in various timing interface regimes selected by the S[0], S[1], and S[2] input pins. The unidirectional timing interface selections are listed in Table 2-3.

Table 2-3. Unidirectional Byte Mode Selection

| Function      | S[2] | S[1]       | S[0] |

|---------------|------|------------|------|

| Asynchronous  | 0    | 0          | 0    |

| Synchronous   | 0    | 0          | 1    |

| HDLC          | 1    | Enable FCS | 1    |

| TAXI          | 0    | 1          | 1    |

| Cascade-Async | 0    | 1          | 0    |

| Cascade-Sync  | 1    | 1          | 0    |

Synchronous and asynchronous timing operations are identical for both unidirectional and bidirectional interfaces. Selecting HDLC provides a parallel interface to the Brooktree Bt8330 HDLC controller. The TAXI mode interface connects directly to the AMD TAXI® part set. The two Cascade selections provide the ability to cascade the unidirectional port with conventional asynchronous and synchronous buffers, respectively.

All parallel interface selections have a 9-bit unidirectional port. Bit mapping from the bidirectional port to the unidirectional port is detailed in Table 2-4.

Table 2-4. Bidirectional to Unidirectional Bit Mappings

| Bidirectional<br>Pin | Unidirectional<br>Input | Unidirectional<br>Output | Description        |

|----------------------|-------------------------|--------------------------|--------------------|

| BIDAT[31:24]         | UINDAT[7:0]             | UOUTDAT[7:0]             | First Byte         |

| BIDAT[23:16]         | UINDAT[7:0]             | UOUTDAT[7:0]             | Second Byte        |

| BIDAT[15:8]          | UINDAT[7:0]             | UOUTDAT[7:0]             | Third Byte         |

| BIDAT[7:0]           | UINDAT[7:0]             | UOUTDAT[7:0]             | Fourth Byte        |

| BISTAT[3]            | UINDAT[8]               | UOUTDAT[8]               | First Byte Status  |

| BISTAT[2]            | UINDAT[8]               | UOUTDAT[8]               | Second Byte Status |

| BISTAT[1]            | UINDAT[8]               | UOUTDAT[8]               | Third Byte Status  |

| BISTAT[0]            | UINDAT[8]               | UOUTDAT[8]               | Fourth Byte Status |

Brooktree<sup>\*</sup>

## 2.4.1 Asynchronous Timing Operation

Asynchronous timing provides a conventional strobed 9-bit buffer interface. Table 2-5 lists the control input and output pin functions for the unidirectional port.

Table 2-5. Asynchronous Pin Functions for Unidirectional Port

| Pin Name | Function                                  |

|----------|-------------------------------------------|

| WCON     | End Write Command for Padding, Active Low |

| WREN*    | Not Used, Connect to Ground               |

| WSTAT    | Not Used, Connect to Ground               |

| WRU*     | Write Strobe, Active Low                  |

| RCON     | End Read Command for Padding, Active Low  |

| RDEN*    | Not Used, Connect to Ground               |

| RDU*     | Read Strobe, Active Low                   |

| CELLOUT  | Not Used                                  |

| IFF*     | Input Buffer Full Flag, Active Low        |

| OEF*     | Output Buffer Empty Flag, Active Low      |

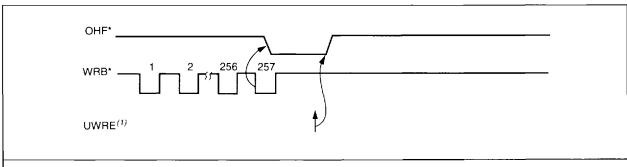

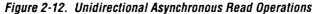

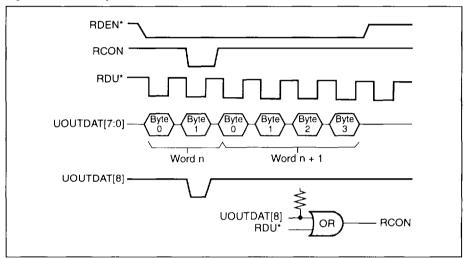

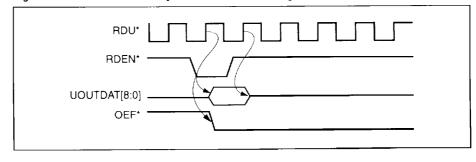

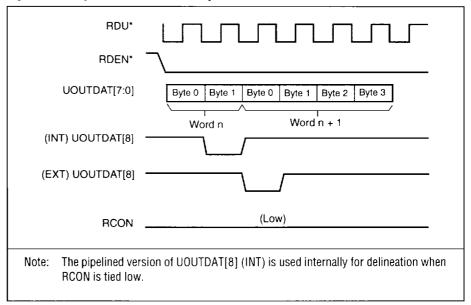

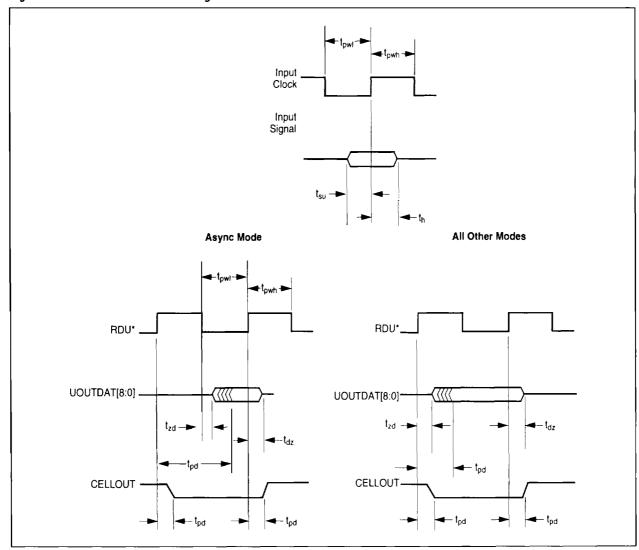

As illustrated in Figure 2-12, the read cycle begins when RDU\* goes to a low state. The data output drivers are enabled and the data on UOUTDAT[8:0] becomes valid. The rising edge of RDU\* clocks the output buffer read pointer and three-states UOUTDAT[8:0]. Upon reading the last location of the output buffer, OEF\* goes active on the falling edge of RDU\* and inhibits further reading of the output buffer. An output buffer write operation occurring while OEF\* is low causes this flag to change to a logic high. A read cycle can start while OEF\* is active by applying RDU\*. Upon a valid write, data is present at UOUTDAT[8:0] and OEF\* goes high. The read cycle is then completed by setting RDU\* high.

The second read operation empties the output buffer, so the output buffer empty flag goes low. It stays low, and if the read strobe is low when a write operation from the bidirectional port causes the buffer to read, the OEF\* will pulse high and data will be enabled until the read strobe is released.

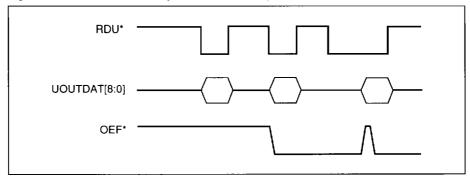

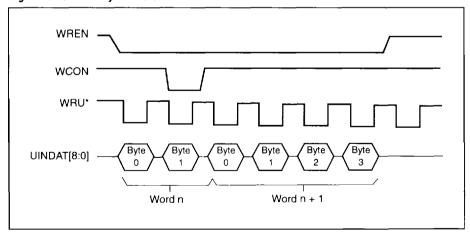

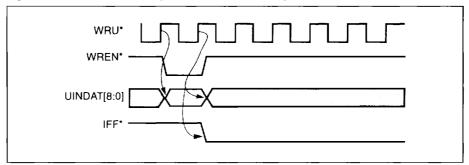

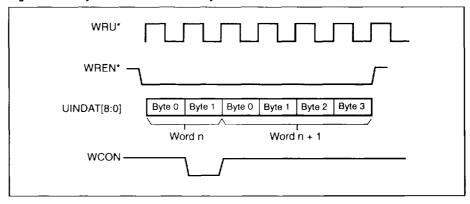

The write cycle begins when the write strobe WRU\* goes to a low state (see Figure 2-13). Setup of the data on UINDAT[8:0] to the buffer starts when the write strobe is low. On the rising edge of the write strobe, the data is stored in the buffer and the write pointer is incremented. The full flag, IFF\*, goes active on the falling edge of WRU\* when writing to the last memory location of the input buffer. While IFF\* is active, writing to the input buffer is inhibited. IFF\* goes inactive on the first read of the input buffer. A write cycle can start while IFF\* is active by applying WRU\*, thus decreasing the write on full time. Upon a valid read, IFF\* will go inactive and WRU\* can then go high to clock data into the buffer.

Figure 2-13. Unidirectional Asynchronous Write Operations

18

### 2.4 Unidirectional Byte-Wide Port Control

### 2.4.1.1 Insertion and Extraction of Pad Bytes, Asynchronous Mode

As shown in Figure 2-14 and Figure 2-15, asynchronous timing operation allows for the insertion of pad bytes in the 9-bit input port to fill to a 36-bit boundary, and for removal of pad bytes on the 9-bit output port. When RCON is low during a unidirectional read cycle, the read pointer is incremented to a 36-bit boundary at the end of the cycle. Bit 9 can be used as a delineation bit by connecting it to RCON. Due to the three-stated UOUTDAT[8] output, the user must ensure that RCON is a logic high before RDU\* goes to a logic low. This can be accomplished by gating UOUTDAT[8] with RDU\* externally.

Figure 2-14. Pad Byte Extraction

When WCON is a logic low during a write cycle, the next write cycle will store data starting on a 36-bit boundary. The pad byte value is undefined. The padding operation can be disabled during asynchronous operation by holding both RCON and WCON at a logic high.

Figure 2-15. Pad Byte Insertion

## 2.4.2 Synchronous Timing Operation

Synchronous timing operation provides a clocked 9-bit buffer interface. Separate read and write clocks and read-enable and write-enable signal inputs are provided. The control input and output pin functions for the unidirectional port are given in Table 2-6.

Table 2-6. Synchronous Pin Functions

| Pin Name | Function                                  |  |

|----------|-------------------------------------------|--|

| WCON     | End Write Command For Padding, Active Low |  |

| WREN*    | Write Enable, Active Low                  |  |

| WSTAT    | Not Used, Connect to Ground               |  |

| WRU*     | Write Clock                               |  |

| RCON     | End Read Command for Padding, Active Low  |  |

| RDEN*    | Read Enable, Active Low                   |  |

| RDU*     | Read Clock                                |  |

| CELLOUT  | Not Used                                  |  |

| IFF*     | Input Buffer Full Flag, Active Low        |  |

| OEF*     | Output Buffer Empty Flag, Active Low      |  |

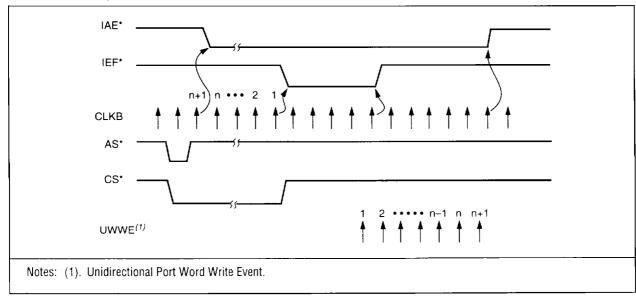

RDU\* provides a free-running read clock to the unidirectional port (see Figure 2-16). When RDEN\* is sampled low by the rising edge of the read clock on RDU\*, the output unidirectional port is enabled and valid data is set up before the next rising clock edge. If the last location of the output buffer is being read, OEF\* goes low and data from the last location becomes valid. After a write to the output buffer, OEF\* goes high synchronous to the rising edge of RDU\*. While OEF\* is low, reading of the output buffer is inhibited.

Figure 2-16. Unidirectional Synchronous Read Timing

Brooktree<sup>\*</sup>

WRU\* provides a free-running write clock to the unidirectional port (see Figure 2-17). When WREN\* is sampled low by a rising edge of WRU\*, unidirectional input data is written to the input register on the same rising clock edge. If a write to the last location of the input buffer occurs, IFF\* goes low synchronous to the rising edge of WRU\*. Upon reading the input buffer, IFF\* goes inactive synchronous to WRU\*. Writing to the input buffer is inhibited while IFF\* is active.

Figure 2-17. Unidirectional Synchronous Write Timing

### 2.4.2.1 Insertion and Extraction of Pad Bytes, Synchronous Mode

As shown in Figure 2-18 and Figure 2-19, a capability for the insertion of pad bytes in the 9-bit input port to fill to a 36-bit boundary and for removal of pad bytes on the 9-bit output port is provided. When RCON is a logic low during a unidirectional read cycle, the read pointer is incremented to a 36-bit boundary at the end of the read cycle. Bit 9 can be used as a delineation bit by connecting the RCON input to ground. If this input is not tied to ground, it must be a logic high during reset to properly initialize the circuit.

When WCON is active during a write cycle, the next write cycle will store data starting on a 36-bit boundary. The pad byte value is undefined. By holding both RCON and WCON at a logic high, the padding operation can be disabled.

Figure 2-18. Synchronous Mode Pad Byte Insertion

## 2.4.3 HDLC Operation

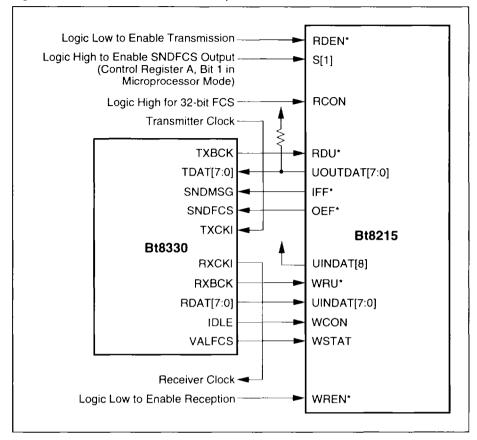

HDLC configures the unidirectional port to interface directly with the Bt8330 HDLC formatter. All HDLC-framed messages start on a 32-bit boundary for the buffer enabling easy reading and writing by a 32-bit processor. Bit 9 of each byte is used as a message delineation bit to indicate the last byte of each message.

The control input and output pin functions, as required for connection to the Bt8330, are shown in Figure 2-20. UINDAT[8] input must be tied to the power supply for proper operation. Pullup resistors are suggested on the UOUT-DAT[7:0] bus since it is set to a high-impedance state during Frame Check Sequence (FCS) octets and when no message is being transferred.

Figure 2-20. Pin Connections for HDLC Operation with the Bt8330

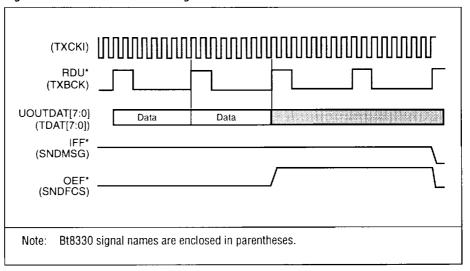

The HDLC formatter provides a transmit clock (TXBCK) to the output buffer. External circuitry provides the RDEN\*, S[1], and RCON inputs, which control HDLC transmit functions. The output buffer provides the byte data, SNDMSG, and SNDFCS signals to the HDLC formatter.

Each transmitted frame starts on a 32-bit boundary when written to the output buffer. The delineation bit is low on the last octet of the frame prior to the FCS bytes. Transmission will start when RDEN\* is at a logic low. If the output buffer is not empty and RDEN\* is low, then the IFF\* output goes to a logic high. The frame is continuously transmitted until the delineation bit is encountered. Therefore, the output buffer must not be allowed to empty while a message is being transferred to the Bt8330. If SNDFCS is enabled (by setting the S[1] input to a logic high), OEF\* will go to a logic high for 2 bytes if RCON is a logic low, or 4 bytes if RCON is a logic high. If SNDFCS is not enabled, the FCS is assumed to be generated by the microprocessor and the Bt8330 will not overwrite an FCS at the end of a message. At the end of the message, the read pointer is incremented to the next 32-bit boundary. Both IFF\* and OEF\* will be inactive for at least one clock period. Functional timing is shown in Figure 2-21

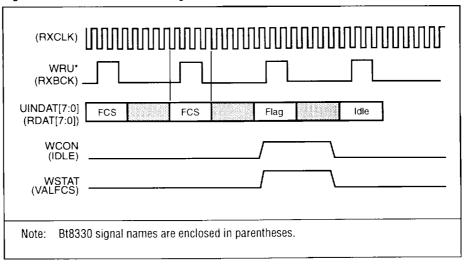

For reception, the HDLC formatter provides a receive clock RXBCK, IDLE, VALFCS, a receive status input to WREN\*, and byte data to the input buffer. A frame starts on a 32-bit boundary. To initialize the writing of a frame, WREN\* must be low and IDLE must be high. Writing starts when IDLE goes low. Functional timing is shown in Figure 2-22 (refer also to the Bt8330 specification).

Figure 2-22. HDLC Receive Timing

Brooktree<sup>4</sup> 23

When VALFCS, IDLE or WREN\* are high, a status byte and delineation bit (active low) are written to the input buffer. Note that the status byte is an additional byte position appended to the received HDLC frame. The read pointer is incremented to the next 32-bit boundary when the status byte is written, so that the next frame received will begin on a word boundary. The status word has four values:

- 1 End of message with invalid FCS (VALFCS = 0, IDLE = 1) results in a status value of 1;

- 2 End of message with good FCS (VALFCS = 1, IDLE = 1) results in a status value of 3

- 3 Abort sequence detected (VALFCS = 1, IDLE = 0) with status of 2

- 4 External abort error (caused by WREN\* high during the message) with a status of greater than or equal to four (see Table 2-7).

Table 2-7. HDLC Receive Status Byte

| Status Byte | Description           |  |  |

|-------------|-----------------------|--|--|

| 000         | Unused                |  |  |

| 001         | Message with Bad FCS  |  |  |

| 010         | Abort Received        |  |  |

| 011         | Message with Good FCS |  |  |

| 1xx         | External Abort        |  |  |

## 2.4.4 TAXI Operation

TAXI timing configuration allows the unidirectional port to interface directly with the TAXI chipset. External circuitry can be added to control the interface to allow insertion of TAXI commands or data into the transmit path. Bit 9 can be configured to provide delineation or parity, or to mark violations. Pin connections for this configuration are shown in Figure 2-23. Pullup resistors should be attached to UOUTDAT[8:0] signals since they are three-stated when the interface is inactive.

RDEN\* Logic Low to Enable Buffer Output **RCON** Logic Low to Enable Internal Padding RDU\* TX\_CLK Am7968 Transmitter DI[8:0] UOUTDAT[8:0] STRB CELLOUT Bt8215 TAXI Chipset RX\_CLK WRU\* DO[8:0] UINDAT[8:0] Am7969 Receiver **DSTRB** WREN\* VLTN WSTAT Logic Low to Pad Word **WCON**

Figure 2-23. Pin Connections for Operation with TAXI Chipset

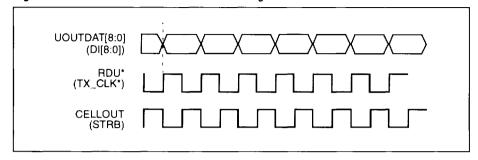

To transmit, the TAXI chipset provides the output buffer with a transmit clock connected to RDU\*. The output buffer returns transmit data and a transmit strobe connected to STRB. Data is read from the output buffer synchronously to TX\_CLK\* whenever RDEN\* is active and the buffer is not empty.

If RCON is connected to ground, bit 9 will be used for internal padding; this allows the Bt8215 to transfer partial words to the TAXI chipset. Otherwise, bit 9 can be used for parity or data and transmitted by the TAXI part. If RCON is not tied to ground, it must be a logic high during reset. Functional timing is shown in Figure 2-24.

Brooktree<sup>4</sup> 25

Figure 2-24. TAXI Transmitter Functional Timing

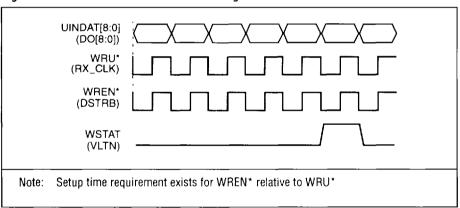

To receive, the TAXI chipset provides a receive clock (RX\_CLK), receive strobe (DSTRB), violation indication (VLTN), and receive data signal (DO[8:0]), connected as shown in Figure 2-23. Whenever DSTRB is a logic high, data is written to the input buffer synchronously with RX\_CLK. If padding is desired, this information must be transmitted in the TAXI by one of the data bits. This data output must be connected both to UINDAT[8] and WCON. When it is low, the following data will be written to the first byte in a word.

The VLTN output of the TAXI chipset may be connected to the WSTAT input of the Bt8215. A logic high on the VLTN output indicates a transmission error in the TAXI output data. A logic high on the WSTAT input inhibits the writing of data to the buffer. If this function is not desired, WSTAT can be tied to ground. Functional timing for the receiver is shown in Figure 2-25

Figure 2-25. TAXI Receiver Functional Timing

26 Brooktree<sup>4</sup>

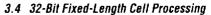

## 2.4.5 Cascade with Asynchronous Buffers

This configuration allows cascading of the buffer with catalog asynchronous buffers. These buffers can be further cascaded among themselves for added depth. Padding is not supported in this mode. The pin connections are shown in Figure 2-26.

The interface to catalog buffers is autonomous and only requires a unidirectional read and write port clock. RDU\* and WRU\* can be tied together for single port clock operation. The basic timing of the unidirectional port is synchronous except that control signals pass between the devices.

Read Clock RDU\* WR OEF\* D[8:0] UOUTDAT[8:0] FF. **RCON** Asynchronous Bt8215 **Buffers WSTAT** EF UINDAT[8:0] RDAT[8:0] IFF\* RD\* Write Clock WRU\*

Figure 2-26. Asynchronous Buffer Cascade Interface

On the input side, the generic FIFO empty flag will be high when it has data. If the input buffer is not full and the generic FIFO has data, then the IFF\* will toggle to read data into the input buffer until either the input buffer is full or the generic FIFO is empty. A similar control occurs on the output side. When the generic FIFO's full flag is high and the output buffer is not empty, then the OEF\* will toggle to write data into the generic FIFO. This will continue until the slave is full or the master is empty.

Empty and full unidirectional indications are derived from generic FIFOs. On the input side, if the generic FIFO is full then the input buffer is also full; otherwise, it would be transferring data. On the output side, an empty generic FIFO indicates an empty output buffer; otherwise, it also would be transferring data.

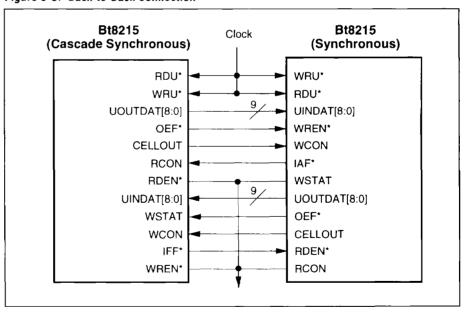

## 2.4.6 Cascade with Synchronous Buffers

This is the same as asynchronous cascade except that the generic FIFOs are port synchronous. In this case, RSTB\* and WSTB\* do not have to toggle to perform reads or writes. The pin connections are shown in Figure 2-27. Also the generic FIFO must supply an almost-full flag instead of a full flag.

Figure 2-27. Synchronous Buffer Cascade Interface

28 Brooktree<sup>1</sup>

## 2.4.7 Unidirectional Half-Full, Almost-Empty and Almost-Full Flags

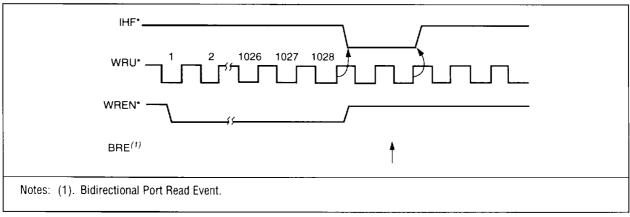

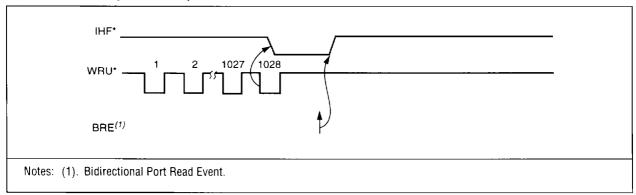

IHF\* provides half-full status for the input buffer. An active flag indicates that the input buffer is greater than half full. Flag timing depends on the port timing. The flag goes active in conjunction with a write of the input buffer. If the writing port is not asynchronous, e.g., sync, TAXI, HDLC, the flag goes active on the rising edge of the write clock (see Figure 2-28). If it is asynchronous, it goes active when the write strobe goes low (see Figure 2-29). Similarly, the flag goes inactive in conjunction with a read of the buffer. It goes inactive in response to either the rising edge of a read strobe in asynchronous timing operation or the rising edge of the write clock following a read operation in synchronous mode. Flag transitions occur only on word boundaries.

Figure 2-28. IHF\* Synchronous Operation

Figure 2-29. IHF\* Asynchronous Operation

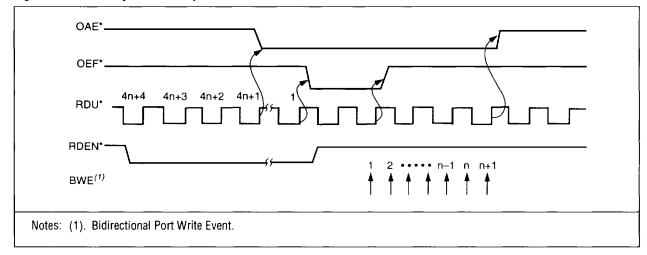

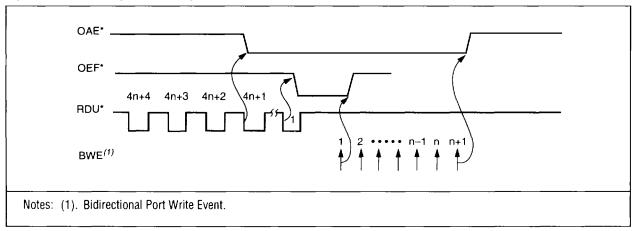

OAE\* provides almost-empty status for the output buffer. The offset is preset at eight words (n = 8) for the stand-alone smart FIFO mode. Flag timing depends on the port timing. The flag goes active in conjunction with a read of the output buffer. If the reading port is not asynchronous, e.g., synchronous, TAXI, HDLC, the flag goes active on the rising edge of the read clock (see Figure 2-30). If it is asynchronous, the flag goes active when the read strobe goes low (see Figure 2-31). Similarly, the flag goes inactive in conjunction with a write of the buffer. It goes inactive in response to either the rising edge of a write strobe in asynchronous timing operation or the rising edge of the read clock input following a write operation in synchronous mode. Flag transitions occur only on word boundaries.

Figure 2-30. OAE\* Synchronous Operation

Figure 2-31. OAE\* Asynchronous Operation

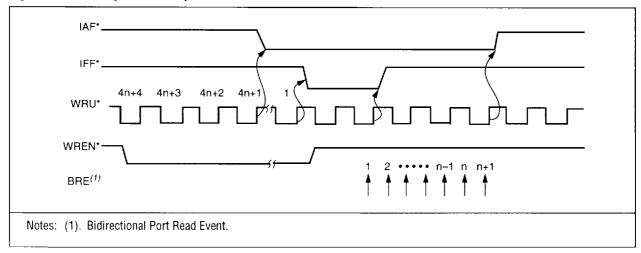

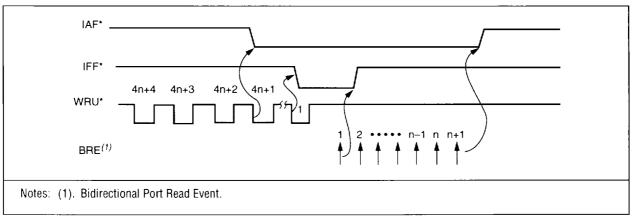

IAF\* provides almost-full status for the input buffer. The offset is preset at eight words (n = 8) for the stand-alone smart FIFO mode. Flag timing depends on the port timing. The flag goes active in conjunction with a write of the input buffer. If the writing port is not asynchronous, e.g., synchronous, TAXI, HDLC, the flag goes active on the rising edge of the write clock (see Figure 2-32). If it is asynchronous, it goes active when the write strobe goes low (see Figure 2-33). Similarly, the flag goes inactive in conjunction with a read of the buffer and in response to either the rising edge of a read strobe in asynchronous timing operation or the rising edge of the write clock input following a read operation in synchronous mode. Flag transitions occur only on word boundaries.

30 Brooktree<sup>3</sup>

Figure 2-32. IAF\* Synchronous Operation

Figure 2-33. IAF\* Asynchronous Operation

# 3.0 Microprocessor Control Mode

## 3.1 System Overview

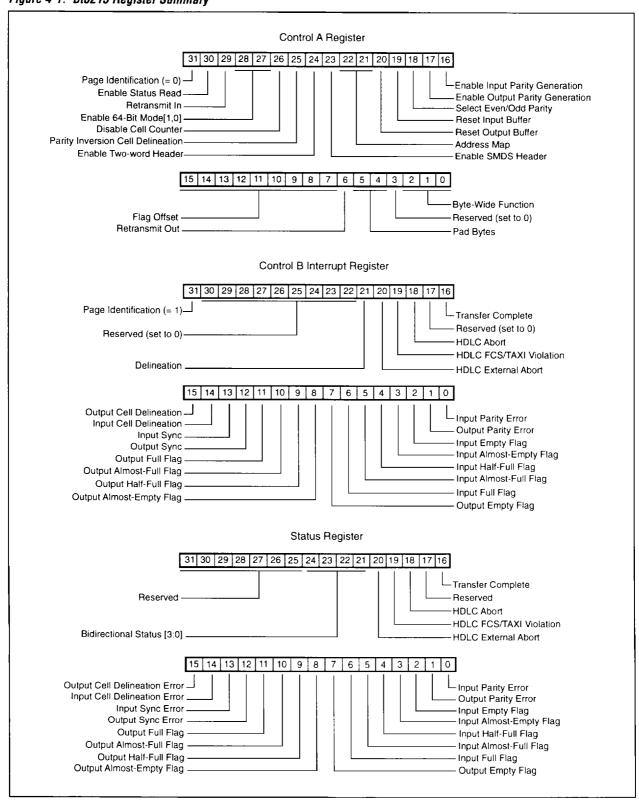

The microprocessor control mode is selected by setting the MODE input to a logic high. The microprocessor interface is synchronous and can be configured to work with most 32-bit microprocessors. The microprocessor has access to two 32-bit control registers and one 32-bit status register. The control registers select the operational modes, the status register provides operational status.

The microprocessor control mode provides identical functionality to the stand-alone smart FIFO mode, in addition to providing a cell processing feature. The cell processing feature allows the buffer to process both fixed-length cells containing one- and two-word headers as well as variable length cells. Broadcast, start-cell, and end-cell operations are all modes of the cell processing operation. The broadcast mapping can be used to implement a hub or switch. The start-cell or end-cell operation can be used to implement an end point station. The difference in these submodes is in the way that cell headers are processed.

The minimum cell size is 8 octets and the maximum is 2047 octets. Operating modes are selected by bits 21 and 22 of Control Register A and are given in Table 3-1.

Table 3-1. Bidirectional Port Address Map

| Mode                             | AddrMap[1]<br>CRA.22 | AddrMap(0)<br>CRA.21 |

|----------------------------------|----------------------|----------------------|

| Smart FIFO Mode                  | 0                    | 0                    |

| Cell Processing: Broadcast Mode  | 0                    | 1                    |

| Cell Processing: Start-Cell Mode | 1                    | 0                    |

| Cell Processing: End-Cell Mode   | _ 1                  | 1                    |

### System Overview

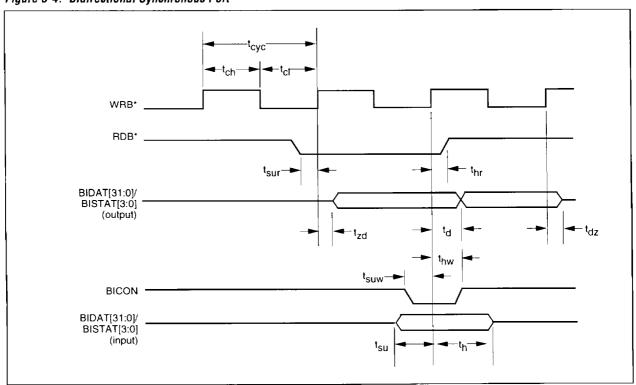

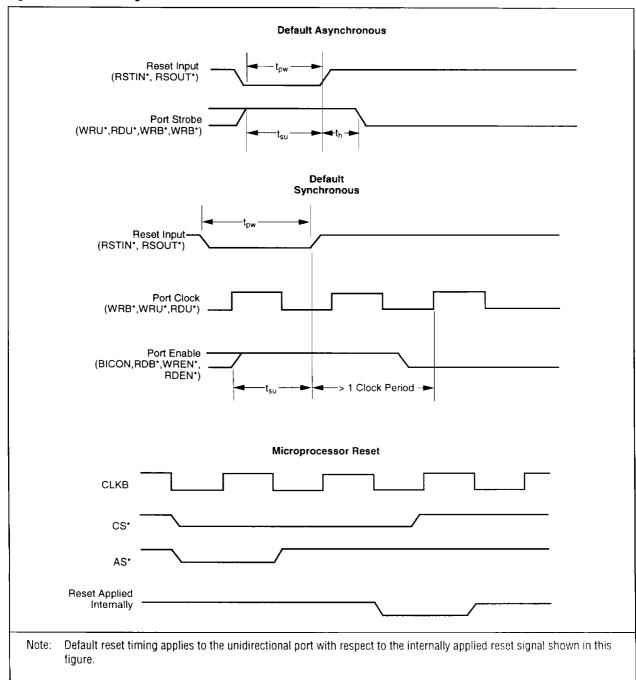

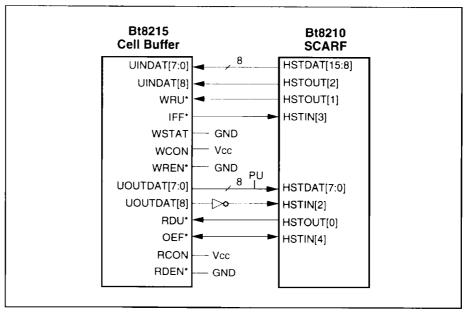

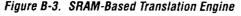

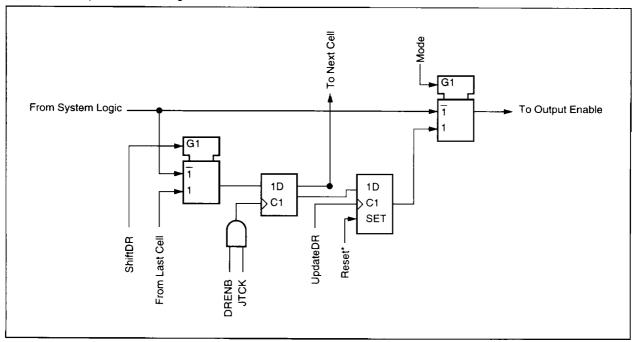

Figure 3-1 illustrates the block diagram for microprocessor mode. The bidirectional port operates under control of the microprocessor interface. All access (reading and writing) of the input and output buffers is accomplished with the A[0] and A[1] address pins (refer to Table 3-3 and Table 3-5). Multiple reads or writes may be performed (burst read/write cycle) and these cycles are limited only by the FIFO depth. Both the Bidirectional and Unidirectional ports may be active at the same time. Control Register A [CRA;0x00] may be used to configure the available options for both the unidirectional and the bidirectional ports. Control Register B [CRB;0x00] enables an interrupt capability upon a change of state of the buffer flags. The status register makes available various buffer status flags, parity, and delineation indications. These indicators are also available as external pins. The maximum clock rate for the bidirectional port is 33 MHz and the maximum clock rate for the unidirectional port is 20 MHz.

**WCON** WREN\* Write Control **WSTAT** ► IAF\* Flags Bidirectional - IHF\* Port Interface Write Pointer Dual Port RAM Input UINDAT[8:0] 512 x 36 BIDAT[31:0] Read Pointer BISTAT[3:0] **◄** Unidirectional Port Interface CLKB CS\* OE\* vicroprocessor R/W\* - INT\* Control AS\* **A1** A0 Write Pointer Dual Port RAM Output UINDAT[8:0] 512 x 36 Read Pointer Flags OEF\* OAF\* OHF\* Flags **CELLOUT RCON** RDU\* Read Control RDEN'

Figure 3-1. Cell Buffer System Diagram (Microprocessor Mode)

## 3.2 Pin Description

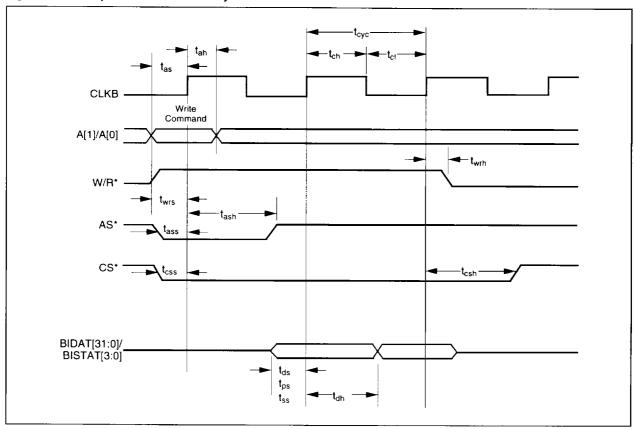

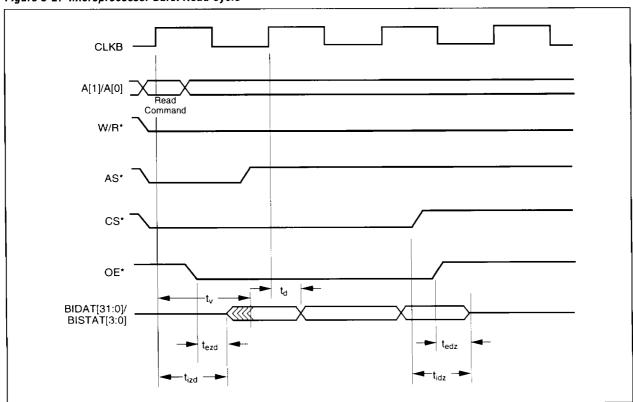

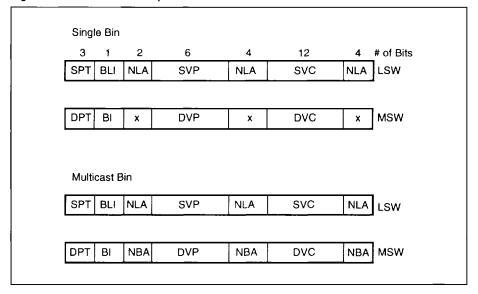

The microprocessor interface consists of nine pins: Chip Select (CS\*), Address Strobe (AS\*), Clock (CLKB), Write/Read\* (W/R\*), Output Enable (OE\*), two address pins (A[0,1]), a control (MODE), and an interrupt (INT\*). A logic diagram of the Bt8215 cell buffer is shown in Figure 3-2. Pins names shown in Figure 3-2 within parentheses have dual functions and alternate names defined for the stand-alone smart FIFO mode. The BICELL and INT\* pins are open-drain outputs and may require pullup resisters for proper operation depending upon the application. Table 3-2 lists the pin descriptions, labels, and I/O assignments.

Figure 3-2. Cell Buffer Logic Diagram (Microprocessor Mode)

### 3.2 Pin Description

Table 3-2. Hardware Signal Definitions—Microprocessor Control Mode (1 of 2)

|                          | Pin Label           | Signal Name               | 1/0 | Definition                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|---------------------|---------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | MODE                | Control Mode              | I   | Must be set to a logic high to select microprocessor control mode.                                                                                                                                                                                                                                                                            |

|                          | CS* (BIMODE)        | Chip Select               | I   | Must be low to cause a read or write operation. CS* can not be high while AS* is high during multiple clock cycles unless bursting is desired. CS* must stay low during the access for proper operation, i.e., must not have decoding glitches.                                                                                               |

|                          | A[0] (S[0])         | Address Bit 0             | l   | Address bit available in microprocessor control mode to select between types of access of the input/output buffer.                                                                                                                                                                                                                            |

| 93                       | A[1] (S[1])         | Address Bit 1             | I   | Address bit available in microprocessor control mode to select between types of access of the input/output buffer.                                                                                                                                                                                                                            |

| Microprocessor Interface | AS* (S[2])          | Address Strobe            | l   | If low, a new address is loaded for the operation when AS* goes high. When it is high and CS* is low, a read or a write operation is executed. The address strobe can stay low for multiple clock periods. This allows for the insertion of wait states.                                                                                      |

|                          | OE* (BICON)         | Output Enable             | 1   | Must be low to enable the data output. The data is enabled between rising clock edges on a read cycle when this pin is low. For most applications this can be tied to ground.                                                                                                                                                                 |

|                          | CLKB (WRB*)         | Clock Input               | ı   | Clock input to the microprocessor interface. All inputs are synchronous to the rising edge of this clock except OE*.                                                                                                                                                                                                                          |

|                          | W/R* (RDB*)         | Write/Read                | l   | If low when chip select is low, the subsequent cycle is a read operation. If the operation is a read-and-modify, the register contents are latched during read operation. If this signal is high when chip select is low, the data presented at the end of the next clock cycle will be written if the chip select is still low at that time. |

|                          | INT* (RSTIN*)       | Interrupt                 | 0   | An active low output with open drain.                                                                                                                                                                                                                                                                                                         |

|                          | IEF*                | Input Empty Flag          | 0   | Provides an empty status for the input buffer.                                                                                                                                                                                                                                                                                                |

|                          | IAE*                | Input Almost-Empty Flag   | 0   | Provides an almost-empty status for the input buffer.                                                                                                                                                                                                                                                                                         |

| 펕                        | OFF*                | Output Full Flag          | 0   | Provides a full status for the output buffer.                                                                                                                                                                                                                                                                                                 |

| al Po                    | OAF*                | Output Almost-Full Flag   | 0   | Provides an almost-full status for the output buffer.                                                                                                                                                                                                                                                                                         |

| ction                    | OHF*                | Output Half-Full Flag     | 0   | Provides a half-full status for the output buffer.                                                                                                                                                                                                                                                                                            |

| Bidirectional Port       | BICELL<br>(RSTOUT*) | Cell Delineation          | 1/0 | Used in the cell mode. Should be tied to a pullup resistor to the supply voltage since it is a bidirectional open drain pin.                                                                                                                                                                                                                  |

|                          | BISTAT[3:0]         | Bidirectional Status Word | 1/0 | Provides a status bit for each byte on BIDAT[31:0].                                                                                                                                                                                                                                                                                           |

|                          | BIDAT[31:0]         | Bidirectional Data Word   | 1/0 | The bidirectional 32-bit-wide data bus.                                                                                                                                                                                                                                                                                                       |

Table 3-2. Hardware Signal Definitions—Microprocessor Control Mode (2 of 2)

| 111-                | Pin Label            | Signal Name              | 1/0 | Definition                                                                                                                                                                              |

|---------------------|----------------------|--------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | RCON                 | Read Control             | 1   | Provides control of the unidirectional output port.                                                                                                                                     |

|                     | RDEN*                | Read Enable              | ı   | An active-low input that enables reading of the unidirectional output port.                                                                                                             |

|                     | RDU*                 | Read Strobe              | 1   | Clocks the unidirectional output port.                                                                                                                                                  |

|                     | WRU*                 | Write Strobe             | I   | Clocks the unidirectional input port.                                                                                                                                                   |

|                     | WSTAT                | Write Status             | ı   | Provides control of the unidirectional input port.                                                                                                                                      |

| Ħ                   | WREN*                | Write Enable             | ļ   | An active-low input that enables writing of the unidirectional input port.                                                                                                              |

| Unidirectional Port | WCON                 | Write Control            | 1   | Provides control of the unidirectional input port.                                                                                                                                      |

| ction               | UINDAT[8:0]          | Byte-Wide Input          | ı   | The unidirectional byte-wide input data bus.                                                                                                                                            |

| idire               | IFF*                 | Input Full Flag          | 0   | Provides a full status for the input buffer.                                                                                                                                            |

| בֿ                  | IAF*                 | Input Almost-Full Flag   | 0   | Provides an almost-full status for the input buffer.                                                                                                                                    |

|                     | IHF*                 | Input Half-Full Flag     | 0   | Provides a half-full status for the input buffer.                                                                                                                                       |

|                     | OAE*                 | Output Almost-Empty Flag | 0   | Provides an almost-empty status for the output buffer.                                                                                                                                  |

|                     | OEF*                 | Output Empty Flag        | 0   | Provides an empty status for the output buffer.                                                                                                                                         |

|                     | CELLOUT              | Cell Output              | 0   | Provides unidirectional output port cell delineation in cell modes. In TAXI mode, this pin is used as a TAXI interface transmit strobe.                                                 |

|                     | UOUTDAT[8:0]         | Byte-Wide Output         | 0   | The unidirectional byte-wide output data bus.                                                                                                                                           |

| Control             | SLAVE*<br>(RTIN*)    | Slave Select             | I   | Used in the 64-bit cell mode. For all other modes tie this input to the supply voltage. Master device is selected by pulling this pin high; slave device is selected by pulling it low. |

|                     | SLAVE_OE<br>(RTOUT*) | Slave Output Enable      | 1/0 | Provides unidirectional output port three-state synchronization between master and slave device.                                                                                        |

|                     | JTCK                 | JTAG Test Clock          | I   | The test clock input.                                                                                                                                                                   |

|                     | JTMS                 | JTAG Test Mode           | I   | A serial command input that sets up various JTAG tests.                                                                                                                                 |

| JTAG                | JTDI                 | JTAG Test Data In        | 1   | The JTAG serial data input.                                                                                                                                                             |

| 5                   | JTRES*               | JTAG Test Reset          | 1   | An active-low signal that asynchronously resets the JTAG test circuitry.                                                                                                                |

|                     | JTDO                 | JTAG Test Data Out       | 0   | The JTAG serial data output.                                                                                                                                                            |

| 9                   | VCC                  | Supply Voltage           | -   | Five pins are provided for power.                                                                                                                                                       |

| VCC and GND         | GND                  | Ground                   | -   | Six pins are provided for ground.                                                                                                                                                       |

#### 3.3 Smart FIFO Mode Operation

# 3.3 Smart FIFO Mode Operation

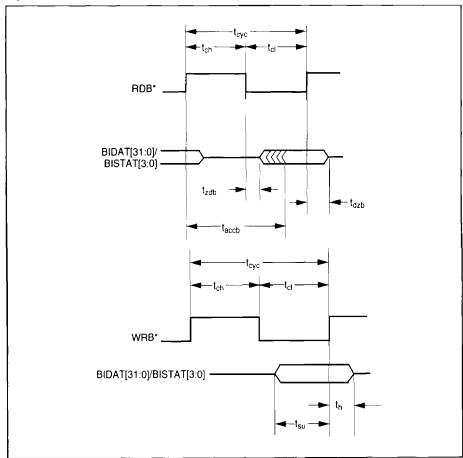

Table 3-3 is the smart FIFO mode (non-cell) address map of the microprocessor port (bits 21 and 22 of Control Register A both set to 0). Control Register A configures available options in the microprocessor control mode and the Status Register reports buffer status and parity. The *Read Buffer* and *Write Buffer* commands access the contents of the input and output buffers, respectively. One or more words can be written if the microprocessor interface is operating in burst mode. *The Write Last Word* command writes the 9th bit as a delineation bit so that the unidirectional interface can pad to a word boundary. The *Transfer Word* command writes a word from the input buffer to the output buffer. Detailed timing for the microprocessor interface is given in Section 5.1.

Table 3-3. Smart FIFO Mode Address Map

| A[1] A[0]<br>Pin 20 Pin 19 |   | Read Commands         | Write Commands         |

|----------------------------|---|-----------------------|------------------------|

| 0                          | 0 | Read Buffer           | Write Buffer           |

| 0                          | 1 | Transfer Word         | Write Last Word        |

| 1                          | 0 | Read Status           | (Null Operation)       |

| 1                          | 1 | Read Control Register | Write Control Register |

38 Brooktree<sup>3</sup>

3.3 Smart FIFO Mode Operation

#### 3.3.1 Bidirectional Port Control

Table 3-3 gives the address map for access to the bidirectional port. The microprocessor initialization procedure is as follows:

- Write Control Register A and Control Register B with the desired configuration and buffer resets active.

- Read Status Register A to release interrupts.

The *Read Buffer* command causes one word to be read from the input buffer and driven on the bidirectional bus. Multiple reads can occur if the microprocessor interface performs a burst operation. The *Write Buffer* command causes a word to be written to the output buffer. Again, multiple writes can occur if the microprocessor interface performs a burst operation. The IEF\* and OFF\* flags are the same as described in the subsection 2.3.2. The *Transfer Word* command transfers a word from the input buffer to the output buffer. Multiple word transfers can occur if a microprocessor burst cycle takes place.

The Bidirectional Status bits [BiStat[3:0]:SRA.21:24] can be read and written through the 32-bit interface; they correspond to the BISTAT[3:0] pins and the respective 9th bits of the input and output buffers. These status bits can be used for delineation purposes when the words are being padded. On the output buffer side, delineation is provided by the *Write Last Word* command. This command causes a pad field to be inserted and a delineation bit to be written to a logic zero.

The length of the pad field is determined by the Pad Bytes field [Pad-Bytes[1,0]; CRA.4,5]. Pad Bytes = 0 causes no padding and Pad Bytes = 3 delineates for three pad bytes. The last active byte of a word is delineated with a logic zero in bit 9 of the byte. The BISTAT[3:0] pins must be a logic high when writing to the output buffer for the *Write Last Word* command to work properly. The first read of the status register after a read of the input buffer will report delineation on the BiStat[3:0] bits. A Bistat[3:0] bit will be a logic high if the corresponding BiStat[3:0] bit was a logic low during the previous read of the input buffer. Since the content of pad bytes is undefined, more than one delineation bit can occur in a word. The most significant delineation bit indicates the last active byte of a word.

#### 3.3 Smart FIFO Mode Operation

#### 3.3.2 Unidirectional Port Control

The Byte-Wide Function bits [ByteMode[2:0];CRA.2:0] select unidirectional port operation. The functions of these bits are given in Table 3-4. These bits functionally replace inputs S[0], S[1], and S[2] used in the stand-alone smart FIFO mode. The operation of each timing interface given in Table 3-4 is identical to that of the stand-alone smart FIFO mode. Status interrupts can be generated by the unidirectional ports in TAXI and HDLC modes.

| directional Port Selection |

|----------------------------|

|                            |

| Function             | ByteMode[2] | ByteMode[1] | ByteMode(0) |

|----------------------|-------------|-------------|-------------|

| Asynchronous         | 0           | 0           | 0           |

| Synchronous          | 0           | 0           | 1           |

| HDLC                 | 1           | Enable FCS  | 1           |

| TAXI                 | 0           | 1           | 1           |

| Cascade-Asynchronous | 0           | 1           | 0           |

| Cascade-Synchronous  | 1           | 1           | 0           |

In TAXI mode, if the WSTAT pin (violation) is a logic high and the WREN\* pin (data strobe) is a logic low when the clock is going high on the rising edge of WRU\* (receive clock), an interrupt is generated if TAXI Violation Interrupt Enable [EnTAXIViol;CRB.19] is enabled. WSTAT set to a logic high inhibits the writing of data to the input buffer.

For HDLC timing, *HDLC Abort*, *HDLC FCS* errors, and *HDLC External Abort* can be programmed to interrupt the microprocessor if a bad FCS or abort sequence error is written in the HDLC status byte at the end of a message or WREN\* input goes high in the middle of a message (refer to Table 2-7).

### 3.3.3 Parity

On the input buffer side, parity can be applied to bit 9 or internally generated. The parity is checked and passed out in the BISTAT[3:0] pins of the bidirectional port. On the output buffer side, parity can be applied to the BISTAT[3:0] pins or generated internally, passed through the output buffer, and checked at the unidirectional output port. Parity is always checked. If an error occurs, Status Register A bits are latched until read. If the parity error interrupt is enabled, an interrupt occurs.

The interrupt clears when the status register is read. These checks occur even if bit 9 is not used for parity; in this case the status bits can be ignored and should not be enabled to cause interrupts. If Enable Input Parity Generation [EnInpParity; CRA.16] or Enable Output Parity Generation [EnOutParity; CRA.17] is set, then bit 9 of each byte is overwritten to a parity value calculated at that port input. Even or odd parity can be selected with the Select Even/Odd Parity [SelParity; CRA.18] control bit. A logic high selects even parity.

#### 3.3.4 Buffer Flags

The full complement of flags is always present in Status Register A, bits 2 through 11. If the corresponding interrupt bit is not set, these bits will always reflect the current buffer status when read. If an interrupt is enabled, then an interrupt will occur whenever the appropriate flag changes state. The status bits will be latched until read. The almost empty/full flag offsets are common to bits 7 through 15 of Control Register A. The offset is binary encoded and has a range of 0 to 511.

Figure 3-3, Figure 3-4, and Figure 3-5 show the operation of the bidirectional port flags. In all figures, n = offset value in the Control A Register. The unidirectional port flags are shown in Figures 2-28 through 2-33.

Figure 3-3. IAE\* Operation

Figure 3-4. OAF\* Operation

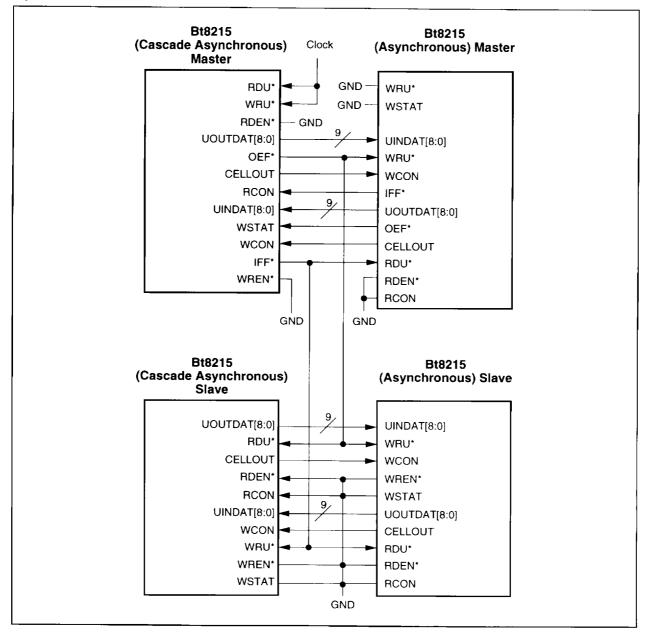

#### 3.4 32-Bit Fixed-Length Cell Processing

Figure 3-5. OHF\* Operation

# 3.4 32-Bit Fixed-Length Cell Processing

Broadcast, start-cell, and end-cell operations are all modes of the 32-bit cell processing operation. The address mapping for each of these modes is given in Table 3-1. Broadcast mapping can be used to implement a hub or switch. Start-cell or end-cell operation can be used to implement an endpoint station. The difference in these submodes is in the way that cell headers are processed.

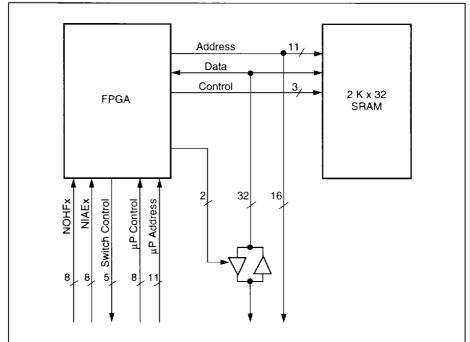

Cell delineation for each submode is provided by an internal 37th bit of the buffer. The BiStat[3:0] bits are available for parity checking. Cell counters check the length of cells entering both input and output buffers when fixed-length cells are being processed. Synchronization circuitry at each buffer output will report an error if the delineation does not occur with the proper data and will realign to a cell boundary.

The operating modes for the microprocessor interface operate on fixed-length cells and allow the processing of these cells with one- and two-word headers. The cell length is defined by the Flag Offset [FlagOfst[8:0];CRA.15:7] and Pad Bytes [PadBytes[1,0];CRA.4,5] fields. An 11-bit counter is provided for the byte-wide input port. A 9-bit counter is provided for the bidirectional port to count the cell length. The cell size in bytes is four times the value of the FlagOfst[8:0] field plus the value of the PadBytes[1,0] field. The minimum cell size is 8 octets, the maximum is 2047 octets. The PadBytes[1,0] field does not reflect the number of pad bytes inserted into the last word, but rather indicates the number of active bytes present in the last word.

# 3.4.1 Bidirectional Port Operation

# 3.4.1.1 Broadcast Operation

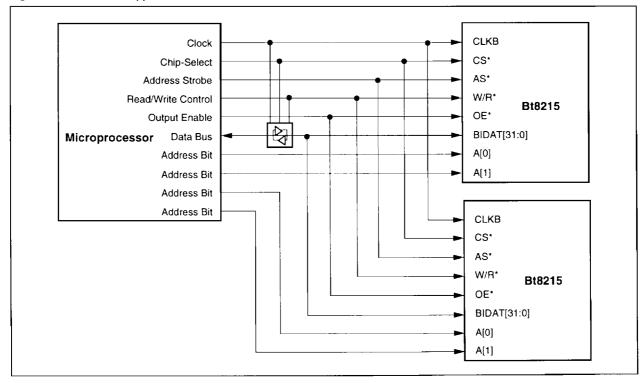

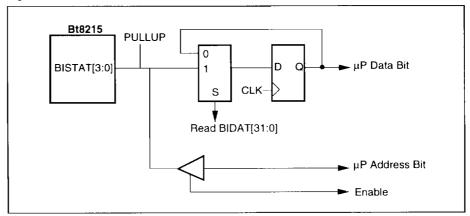

Broadcast mapping (bits 21 and 22 of Control Register A set to 1 and 0, respectively) implements a broadcast algorithm. Each time a header is read by the microprocessor, the rest of the cell is autonomously read onto the output bus on the subsequent clock cycles and simultaneously transferred to the output buffers. If other bidirectional buffers are connected to this bus, they will be able to read the output data as well. This configuration is illustrated in Figure 3-6, where two Bt8215s are connected to a single microprocessor. The BICELL pins of the Bt8215s must be tied together with a pullup resistor.

Figure 3-6. Broadcast Application Connection

43

# 3.4 32-Bit Fixed-Length Cell Processing

In this configuration, the microprocessor clock and control outputs are connected to every bidirectional port. The data is also bused. Each Bt8215 has individual address bit connections that allow different operations to be simultaneously performed on the devices connected to the microprocessor. The bidirectional transceiver isolates the bus from the microprocessor when the microprocessor has not selected any Bt8215 devices.

This broadcast operation reads a one- or two-word header from the source input buffer and then broadcasts the rest of the cell to all output buffers. After this transfer is complete, a header is written to the intended output buffer or buffers and the cell is deleted from all other output buffers. The address functions to accomplish this are given in Table 3-5

| A[1]<br>Pin 20 | A[0]<br>Pin 19 | Read Commands         | Write Commands         |

|----------------|----------------|-----------------------|------------------------|

| 0              | 0              | Read Header           | Write Header           |

| 0              | 1              | Broadcast Write       | Delete Cell            |

| 1              | 0              | Read Status           | (Null Operation)       |

| 1              | 1              | Read Control Register | Write Control Register |

Table 3-5. Broadcast Operating Mode Address Map

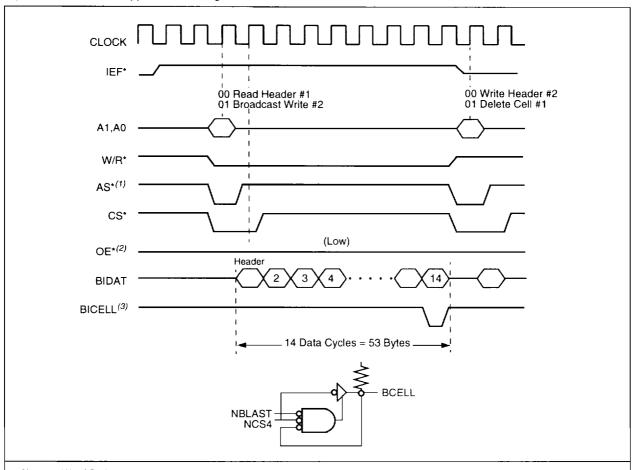

Cells are transferred from one input buffer to a selected group of output buffers in the following sequence (see Figure 3-7):

- At least one input buffer is detected that is not empty. This data is obtained from the IEF\* or IAE\* pins and indicates that a full cell is present in that input buffer. Upon reading the last cell in the input buffer, IEF\* goes active only after the last word has been read, whereas IAE\* goes active after approximately one-half of the cell has been read.

- A read operation is executed to all buffers. The address bus on the selected Bt8215 is set to 00 for a read cell operation. The address bus for each of the other Bt8215s is set to 01, initiating a cell transfer to each output buffer. This enables the entire cell to be copied to all output buffers. Note that this will occur even though the read operation takes but a single cycle.

- After the first word of the cell is read by the processor (En2WordHdr = 0), the transceiver isolates the bus for the rest of the cell-transfer clock cycles. This allows the processor to use its address and data bus to execute whatever program is necessary to determine which output buffers should retain the cell after it is transferred.

- After a new output header is calculated for the cell, a write header cycle is executed for each device that is to retain the transferred cell. For these devices the address bus is set to 00. The same operation can be a delete cell operation to output buffers that are not retaining the transferred cell; for this the address bus is set to 01. When multiple write header commands are required for different cells, the null operation can be used for unaffected buffers.

For the example shown in Figure 3-7, the FlagOffset = 0x0D (indicating 14 words, including Pad Bytes) and the PadBytes = 0x01 in Control Register A.

Figure 3-7. Broadcast Application Timing

Notes: (1). AS\* input must be high during broadcast.

(2). OE\* may be tied low unless default timing is not satisfactory.

(3). See bullet 4 of errata. Circuit used on evaluation board as shown above. Pullup resistor needed since open drain.