# 3.3V 64/32K X 18 SYNCHRONOUS FOURPORT™ STATIC RAM

# IDT70V5388/78 **OBSOLETE PARTS**

### Features

- True four-ported memory cells which allow simultaneous ٠ access of the same memory location

- Synchronous Pipelined device - 64/32K x 18 organization

- Pipelined output mode allows fast 200MHz operation

- High Bandwidth up to 14 Gbps (200MHz x 18 bits wide x 4 ports)

- LVTTL I/O interface

- High-speed clock to data access 3.0ns (max.)

- 3.3V Low operating power

- Interrupt flags for message passing

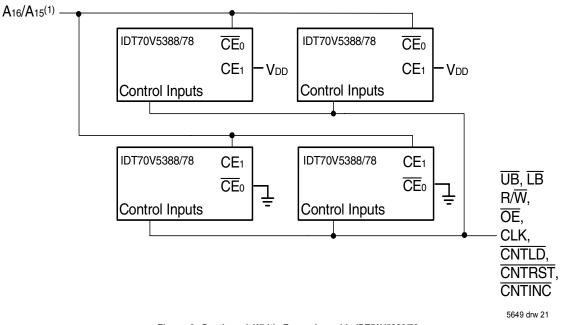

- Width and depth expansion capabilities

- Counter readback on address lines

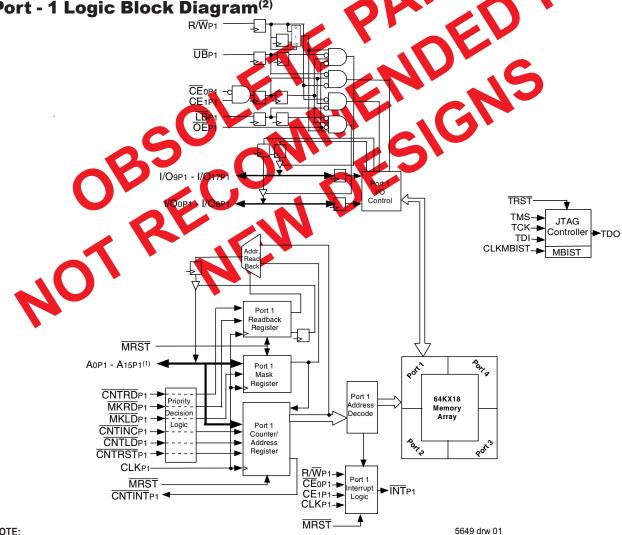

### Port - 1 Logic Block Diagram<sup>(2)</sup>

- Counter wrap-around control

- Internal mask register controls counter wrap-around

- Counter-Interrupt flags to indicate wrap-around

- Mask register readback on address lines

- ٠ **Global Master reset for all ports**

- Dual Chip Enables on all ports for easy depth expansion

- Separate upper-word and lower-word controls on all ports

- ٠ 272-BGA package (27mm x 27mm 1.27mm ball pitch) and 256-BGA package (17mm x 17mm 1.0mm ball pitch)

- ٠ Commercial and Industrial temperature ranges

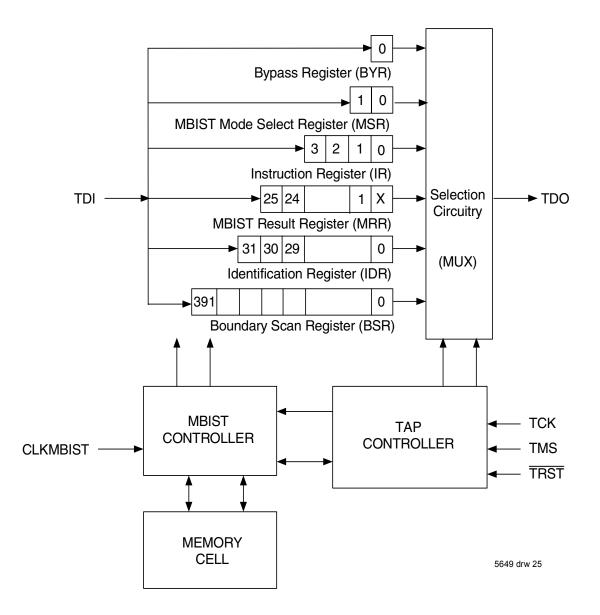

- JTAG boundary scan

- MBIST (Memory Built-In Self Test) controller

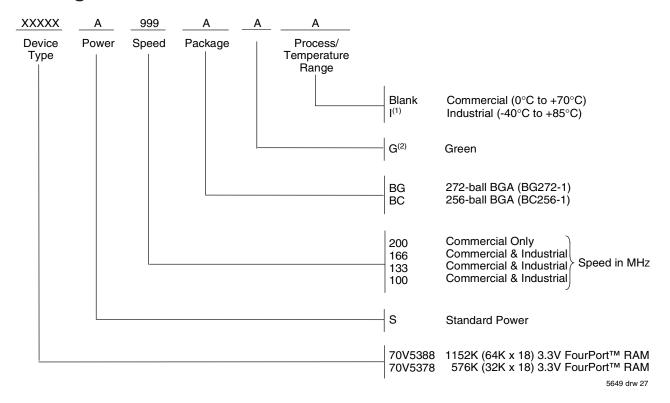

- Green parts available, see ordering information

#### NOTE:

1. A15x is a NC for IDT70V5378

Port 2, Port 3, and Port 4 Logic Blocks are similar to Port 1 Logic Blocks. 2

### **OCTOBER 2008**

### **Description**

The IDT70V5388/78 is a high-speed 64/32Kx18 bit synchronous FourPort RAM. The memory array utilizes FourPort memory cells to allow simultaneous access of any address from all four ports. Registers on control, data, and address inputs provide minimal setup and hold times. The timing latitude provided by this approach allows systems to be designed with very short cycle times.

With an input data register and integrated burst counters, the 70V5388/78 has been optimized for applications having unidirectional or bi-directional data flow in bursts. An automatic power down feature, controlled by CEo and CE1, permits the on-chip circuitry of each port to enter a very low standby power mode.

The IDT70V5388/78 provides a wide range of func-

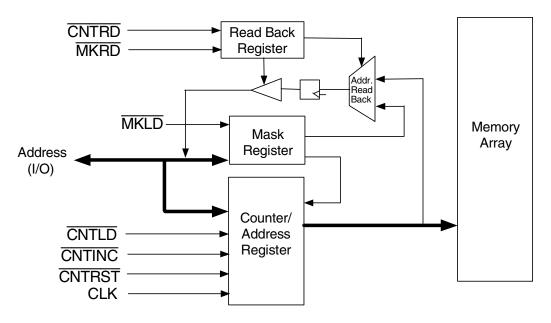

tions specially designed to facilitate system operations. These include full-boundary, maskable address counters with associated interrupts for each port, mailbox interrupt flags on each port to facilitate inter-port communications, Memory Built-In Self-Test (MBIST), JTAG support and an asynchronous Master Reset to simplify device initialization. In addition, the address lines have been set up as I/O pins, to permit the support of CNTRD (the ability to output the current value of the internal address counter on the address lines) and MKRD (the ability to output the current value of the support of counter mask register). For specific details on the device operation, please refer to the Functional Description and subsequent explanatory sections, beginning on page 21.

# **Pin Configuration**<sup>(4)</sup>

### 70V5388/78BG BG-272<sup>(2)</sup>

| 0.010 |                  |                          |              |              |             |             |             |             |                    | 2-Pir<br>op V      |                    |                    |             |             |             |             |              |              |                          |           |   |

|-------|------------------|--------------------------|--------------|--------------|-------------|-------------|-------------|-------------|--------------------|--------------------|--------------------|--------------------|-------------|-------------|-------------|-------------|--------------|--------------|--------------------------|-----------|---|

| 09/2  | 5/02<br><b>1</b> | 2                        | 3            | 4            | 5           | 6           | 7           | 8           | 9                  | 10                 | 11                 | 12                 | 13          | 14          | 15          | 16          | 17           | 18           | 19                       | 20        |   |

| Α     | LB<br>P1         | I/O17<br>P2              | I/O15<br>P2  | I/O13<br>P2  | I/O11<br>P2 | I/O9<br>P2  | I/O16<br>P1 | I/O14<br>P1 | I/O12<br>P1        | I/O10<br>P1        | I/O10<br>P4        | I/O12<br>P4        | I/O14<br>P4 | I/O16<br>P4 | I/O9<br>P3  | I/O11<br>P3 | I/O13<br>P3  | I/O15<br>P3  | I/O17<br>P3              | LB<br>P4  | A |

| В     | Vdd              | UB<br>P1                 | l/O16<br>P2  | I/O14<br>P2  | I/O12<br>P2 | I/O10<br>P2 | l/O17<br>P1 | I/O13<br>P1 | I/O11<br>P1        | TMS                | TDI                | I/O11<br>P4        | I/O13<br>P4 | I/O17<br>P4 | I/O10<br>P3 | I/O12<br>P3 | I/O14<br>P3  | I/O16<br>P3  | UB<br>P4                 | VDD       | в |

| С     | A14<br>P1        | A15 <sup>(1)</sup><br>P1 | CE1<br>P1    | CE₀<br>P1    | R/W<br>P1   | I/O15<br>P1 | Vss         | Vss         | I/O9<br>P1         | тск                | TDO                | I/O9<br>P4         | Vss         | Vss         | I/O15<br>P4 | R/W<br>P4   | CEo<br>P4    | CE1<br>P4    | A15 <sup>(1)</sup><br>P4 | A14<br>P4 | с |

| D     | Vss              | A12<br>P1                | A13<br>P1    | OE<br>P1     | VDD         | Vss         | Vss         | VDD         | VDD                | Vss                | Vss                | VDD                | VDD         | Vss         | Vss         | Vdd         | OE<br>P4     | A13<br>P4    | A12<br>P4                | Vss       | D |

| Ε     | A10<br>P1        | A11<br>P1                | MKRD<br>P1   | CNTRD<br>P1  |             |             |             | 1           | 1                  | 1                  | 1                  | 1                  | 1           | 1           | 1           | 1           | CNTRD<br>P4  | MKRD<br>P4   | A11<br>P4                | A10<br>P4 | E |

| F     | A7<br>P1         | A8<br>P1                 | A9<br>P1     | CNTINT<br>P1 |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTINT<br>P4 | A9<br>P4     | A8<br>P4                 | A7<br>P4  | F |

| G     | Vss              | A5<br>P1                 | A6<br>P1     | CNTINC<br>P1 |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTINC<br>P4 | A6<br>P4     | A5<br>P4                 | Vss       | G |

| н     | Аз<br>Р1         | A4<br>P1                 | MKLD<br>P1   | CNTLD<br>P1  |             |             |             |             |                    |                    |                    |                    | _           |             |             |             | CNTLD<br>P4  | MKLD<br>P4   | A4<br>P4                 | A3<br>P4  | н |

| J     | Vdd              | A1<br>P1                 | A2<br>P1     | VDD          |             |             |             |             | GND <sup>(5)</sup> | GND <sup>(5)</sup> | GND <sup>(5)</sup> | GND <sup>(5)</sup> |             |             |             |             | VDD          | A2<br>P4     | A1<br>P4                 | Vdd       | J |

| К     | Ao<br>P1         | INT<br>P1                | CNTRST<br>P1 | CLK<br>P1    |             |             |             |             | GND <sup>(5)</sup> | GND <sup>(5)</sup> | GND <sup>(5)</sup> | GND <sup>(5)</sup> |             |             |             |             | CLK<br>P4    | CNTRST<br>P4 | INT<br>P4                | Ao<br>P4  | κ |

| L     | A0<br>P2         | INT<br>P2                | CNTRST<br>P2 | Vss          |             |             |             |             | GND <sup>(5)</sup> | GND <sup>(5)</sup> | GND <sup>(5)</sup> | GND <sup>(5)</sup> |             |             |             |             | Vss          | CNTRST<br>P3 | INT<br>P3                | Ao<br>P3  | L |

| Μ     | Vdd              | A1<br>P2                 | A2<br>P2     | CLK<br>P2    |             |             |             |             | GND <sup>(5)</sup> | GND <sup>(5)</sup> | GND <sup>(5)</sup> | GND <sup>(5)</sup> |             |             |             |             | CLK<br>P3    | A2<br>P3     | A1<br>P3                 | Vdd       | м |

| Ν     | A3<br>P2         | A4<br>P2                 | MKLD<br>P2   | CNTLD<br>P2  |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTLD<br>P3  | MKLD<br>P3   | A4<br>P3                 | A3<br>P3  | N |

| Ρ     | Vss              | A5<br>P2                 | A6<br>P2     | CNTINC<br>P2 |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTINC<br>P3 | A6<br>P3     | A₅<br>P3                 | Vss       | Р |

| R     | A7<br>P2         | A8<br>P2                 | A9<br>P2     | CNTINT<br>P2 |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTINT<br>P3 | A9<br>P3     | A8<br>P3                 | A7<br>P3  | R |

| Т     | A10<br>P2        | A11<br>P2                | MKRD<br>P2   | CNTRD<br>P2  |             | 1           | 1           |             | 1                  |                    | 1                  |                    | 1           |             | 1           |             | CNTRD<br>P3  | MKRD<br>P3   | A11<br>P3                | A10<br>P3 | Т |

| U     | Vss              | A12<br>P2                | A13<br>P2    | OE<br>P2     | Vdd         | Vss         | Vss         | VDD         | VDD                | Vss                | Vss                | VDD                | VDD         | Vss         | Vss         | Vdd         | OE<br>P3     | A13<br>P3    | A12<br>P3                | Vss       | U |

| V     | A14<br>P2        | A15 <sup>(1)</sup><br>P2 | CE1<br>P2    | CE₀<br>P2    | R/W<br>P2   | I/O6<br>P2  | Vss         | Vss         | I/O0<br>P2         | TRST               | NC                 | I/O0<br>P3         | Vss         | Vss         | I/O6<br>P3  | R/W<br>P3   | CE0<br>P3    | CE1<br>P3    | A15 <sup>(1)</sup><br>P3 | A14<br>P3 | V |

| W     | Vdd              | UB<br>P2                 | I/O7<br>P1   | I/O5<br>P1   | I/O3<br>P1  | I/O1<br>P1  | I/O8<br>P2  | I/O4<br>P2  | I/O2<br>P2         | MRST               | CLKMBIST           | I/O2<br>P3         | I/O4<br>P3  | I/O8<br>P3  | I/O1<br>P4  | I/O3<br>P4  | I/O5<br>P4   | I/O7<br>P4   | UB<br>P3                 | Vdd       | w |

| Y     | LB<br>P2         | I/O8<br>P1               | I/O6<br>P1   | I/O4<br>P1   | I/O2<br>P1  | I/O0<br>P1  | I/O7<br>P2  | I/O5<br>P2  | I/O3<br>P2         | I/O1<br>P2         | I/O1<br>P3         | I/O3<br>P3         | I/O₅<br>P3  | I/O7<br>P3  | I/O0<br>P4  | I/O2<br>P4  | I/O4<br>P4   | I/O6<br>P4   | I/O8<br>P4               | LB<br>P3  | Y |

|       | 1                | 2                        | 3            | 4            | 5           | 6           | 7           | 8           | 9                  | 10                 | 11                 | 12                 | 13          | 14          | 15          | 16          | 17           | 18           | 19                       | 20        |   |

#### NOTES:

1. A15x is a NC for IDT70V5378.

2. This package code is used to reference the package diagram.

3. This text does not indicate orientation of the actual part marking.

4. Package body is approximately 27mm x 27mm x 2.33mm, with 1.27mm ball-pitch.

5649 drw 03

<sup>5.</sup> Central balls are for thermal dissipation only. They are connected to device Vss.

# Pin Configuration<sup>(2)</sup>

### 70V5388/78BC BC-256<sup>(3)</sup>

256-Pin BGA<sup>(4)</sup> Top View

|   | 09/25/0                  | 2                |                  |                  |                  |             |             | l op V      | lew        |             |              |                  |                  |                  |                          |                          |    |

|---|--------------------------|------------------|------------------|------------------|------------------|-------------|-------------|-------------|------------|-------------|--------------|------------------|------------------|------------------|--------------------------|--------------------------|----|

|   | 1                        | 2                | 3                | 4                | 5                | 6           | 7           | 8           | 9          | 10          | 11           | 12               | 13               | 14               | 15                       | 16                       |    |

| Α | R/W<br>P1                | OE<br>P1         | LB<br>P1         | I/O16<br>P2      | I/O13<br>P2      | I/O9<br>P2  | I/O14<br>P1 | I/O10<br>P1 | I/O9<br>P4 | I/O12<br>P4 | I/O16<br>P4  | I/O11<br>P3      | I/O15<br>P3      | I/O17<br>P3      | UB<br>P4                 | CE1<br>P4                | Α  |

| В | A15 <sup>(1)</sup><br>P1 | CE1<br>P1        | UB<br>P1         | I/O17<br>P2      | I/O14<br>P2      | I/O10<br>P2 | I/O15<br>P1 | I/O11<br>P1 | TDI        | I/O13<br>P4 | I/O17<br>P4  | I/O12<br>P3      | I/O16<br>P3      | LB<br>P4         | R/W<br>P4                | CE0<br>P4                | в  |

| С | A14<br>P1                | A13<br>P1        | CE0<br>P1        | I/O15<br>P2      | I/O12<br>P2      | I/O17<br>P1 | I/O12<br>P1 | I/O9<br>P1  | TDO        | I/O11<br>P4 | I/O15<br>P4  | I/O10<br>P3      | I/O14<br>P3      | OE<br>P4         | A15 <sup>(1)</sup><br>P4 | A14<br>P4                | С  |

| D | A10<br>P1                | A12<br>P1        | A11<br>P1        | <b>A</b> 9<br>P1 | I/O11<br>P2      | I/O16<br>P1 | I/O13<br>P1 | TMS         | тċк        | I/O10<br>P4 | I/O14<br>P4  | I/O9<br>P3       | I/O13<br>P3      | A11<br>P4        | A12<br>P4                | A13<br>P4                | D  |

| Е | <b>A</b> 7<br>P1         | <b>A</b> 8<br>P1 | <b>A</b> 6<br>P1 | <b>A</b> 5<br>P1 | VDD              | Vdd         | Vdd         | Vdd         | Vdd        | Vdd         | Vdd          | <b>A</b> 6<br>P4 | <b>A</b> 7<br>P4 | <b>A</b> 8<br>P4 | A10<br>P4                | A9<br>P4                 | Е  |

| F | <b>А</b> з<br>Р1         | <b>A</b> 4<br>P1 | A2<br>P1         | A1<br>P1         | Vdd              | Vdd         | Vss         | Vss         | Vss        | Vdd         | Vdd          | A1<br>P4         | A2<br>P4         | Аз<br>Р4         | <b>A</b> 5<br>P4         | A4<br>P4                 | F  |

| G | CLK<br>P1                | <b>A</b> 0<br>P1 | CNTRD<br>P1      | CNTINC<br>P1     | Vdd              | Vss         | Vss         | Vss         | Vss        | Vss         | Vss          | CNTLD<br>P4      | CNTINC<br>P4     | CNTRD<br>P4      | <b>A</b> 0<br>P4         | CLK<br>P4                | G  |

| н | Vss                      | CNTLD<br>P1      | CNTRST<br>P1     | CNTINT<br>P1     | INT<br>P1        | MKLD<br>P1  | Vss         | Vss         | Vss        | Vss         | CNTRST<br>P4 | MKRD<br>P4       | INT<br>P4        | CNTINT<br>P4     | MKLD<br>P4               | Vss                      | н  |

| J | CLK<br>P2                | CNTRST<br>P2     | INT<br>P2        | CNTINT<br>P2     | MKRD<br>P1       | Vss         | Vss         | Vss         | Vss        | Vss         | Vss          | CNTRST<br>P3     | INT<br>P3        | CNTINT<br>P3     | MKLD<br>P3               | CLK<br>P3                | J  |

| Κ | CNTRD<br>P2              | MKRD<br>P2       | CNTINC<br>P2     | CNTLD<br>P2      | MKLD<br>P2       | Vss         | Vss         | Vss         | Vss        | Vss         | Vss          | CNTLD<br>P3      | CNTINC<br>P3     | MKRD<br>P3       | <b>A</b> 0<br>P3         | CNTRD<br>P3              | κ  |

| L | Аз<br>Р2                 | <b>A</b> 4<br>P2 | <b>A</b> 2<br>P2 | A1<br>P2         | <b>A</b> 0<br>P2 | Vdd         | Vdd         | Vss         | Vss        | Vss         | Vdd          | Vdd              | <b>A</b> 1<br>P3 | <b>А</b> з<br>Р3 | A4<br>P3                 | <b>A</b> 2<br>P3         | L  |

| Μ | <b>A</b> 8<br>P2         | <b>A</b> 9<br>P2 | A7<br>P2         | A6<br>P2         | <b>A</b> 5<br>P2 | Vdd         | Vdd         | Vdd         | Vdd        | Vdd         | Vdd          | Vdd              | <b>A</b> 5<br>P3 | A7<br>P3         | <b>A</b> 8<br>P3         | <b>А</b> 6<br>Р3         | М  |

| Ν | A11<br>P2                | A12<br>P2        | A10<br>P2        | I/O5<br>P1       | I/O1<br>P1       | I/O6<br>P2  | I/O2<br>P2  | TRST        | CLKMBIST   | I/O3<br>P3  | I/O7<br>P3   | I/O2<br>P4       | A9<br>P3         | A11<br>P3        | A12<br>P3                | A10<br>P3                | Ν  |

| Ρ | A13<br>P2                | A14<br>P2        | R/W<br>P2        | I/O7<br>P1       | I/O2<br>P1       | I/O7<br>P2  | I/O3<br>P2  | MRST        | I/O0<br>P3 | I/O4<br>P3  | I/O8<br>P3   | I/O3<br>P4       | I/O6<br>P4       | CE0<br>P3        | A14<br>P3                | A13<br>P3                | Ρ  |

| R | A15 <sup>(1)</sup><br>P2 | CE1<br>P2        | UB<br>P2         | I/O8<br>P1       | I/O4<br>P1       | I/O0<br>P1  | I/O5<br>P2  | I/O1<br>P2  | I/O2<br>P3 | I/O6<br>P3  | I/O1<br>P4   | I/O5<br>P4       | I/O7<br>P4       | UB<br>P3         | CE1<br>P3                | A15 <sup>(1)</sup><br>P3 | R  |

| т | CE0<br>P2                | OE<br>P2         | LB<br>P2         | I/O6<br>P1       | I/O3<br>P1       | I/O8<br>P2  | I/O4<br>P2  | I/O0<br>P2  | I/O1<br>P3 | I/O5<br>P3  | I/O0<br>P4   | I/O4<br>P4       | I/O8<br>P4       | LB<br>P3         | OE<br>P3                 | R/W<br>P3                | т  |

|   | 1                        | 2                | 3                | 4                | 5                | 6           | 7           | 8           | 9          | 10          | 11           | 12               | 13               | 14               | 15<br>₅                  | <b>16</b><br>649 drw (   | )4 |

#### NOTES:

1. A15x is a NC for IDT70V5378.

2. Package body is approximately 17mm x 17mm x 1.4mm, with 1.0mm ball-pitch.

3. This package code is used to reference the package diagram.

4. This text does not indicate orientation of the actual part-marking.

### **Pin Definitions**

| Port 1                      | Port 2                      | Port 3                      | Port 4                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0P1 - A15P1 <sup>(1)</sup> | A0p2 - A15p2 <sup>(1)</sup> | A0p3 - A15p3 <sup>(1)</sup> | A0p4 - A15p4 <sup>(1)</sup> | Address Inputs. In the CNTRD and MKRD operations, these pins serve as outputs for the internal address counter and the internal counter mask register respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I/O0P1 - I/O17P1            | I/O0P2 - I/O17P2            | I/O0P3 - I/017P3            | I/O0P4 - I/O17P4            | Data Bus Input/Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLKP1                       | CLKP2                       | СЬКРЗ                       | CLKP4                       | Clock Input. The maximum clock input rate is fMAX. The clock signal can be free running or strobed depending on system requirements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MRST                        |                             |                             |                             | Master Reset Input. $\overline{\text{MRST}}$ is an asycnchronous input, and affects all ports. It must be asserted LOW ( $\overline{\text{MRST}} = \text{V}_{\mathbb{L}}$ ) at initial power-up. Master Reset sets the internal value of all address counters to zero, and sets the counter mask registers for each port to 'unmasked'. It also resets the output flags for the mailboxes and the counter interrupts ( $\overline{\text{INT}} = \overline{\text{CNTINT}} = \text{V}_{  }$ ) and deselects all registered control signals.                                                                                                                                                                                                                                                                             |

| CE0P1, CE1P1                | CE0P2, CE1P2                | CE0P3, CE1P3                | CE0P4, CE1P4                | Chip Enable Inputs. To activate any port, both signals must be asserted to their active states ( $\overline{CE}_0 = V_{I\!L}$ , CE <sub>1</sub> = V <sub>I</sub> ). A given port is disabled if either chip enable is deasserted ( $\overline{CE}_0 = V_{I\!H}$ and/or CE <sub>1</sub> = V <sub>L</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| R/₩pi                       | R/Wp2                       | R/Wp3                       | R/WP4                       | Read/Write Enable Input. This signal is asserted LOW ( $R/\overline{W} = V_{IL}$ ) in order to write to the FourPort memory array, and it is asserted HIGH ( $R/\overline{W} = V_{IH}$ ) in order to read from the array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LB <sub>P1</sub>            | LBP2                        | LBP3                        | LBP4                        | Lower Byte Select Input (I/O <sub>0</sub> - I/O <sub>8</sub> ). Asserting this signal LOW ( $\overline{LB}$ = V <sub>L</sub> ) enables read/write operations to the lower byte. For read operations, this signal is used in conjunction with $\overline{OE}$ in order to drive output data on the lower byte of the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| UB <sub>P1</sub>            | ŪBp2                        | ŪBp3                        | UBP4                        | Upper Byte Select Input ( $I/O_9 - I/O_{17}$ ). Asserting this signal LOW ( $\overline{LB} = V_{IL}$ ) enables read/write operations to the upper byte. For read operations, this signal is used in conjunction with $\overline{OE}$ in order to drive output data on the upper byte of the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OE <sub>P1</sub>            | OEP2                        | <del>OE</del> P3            | ŌĒp4                        | Output Enable Input. Asserting this signal LOW ( $\overline{OE}$ = VL) enables the device to drive data on the I/O pins during read operation. $\overline{OE}$ is an asychronous input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

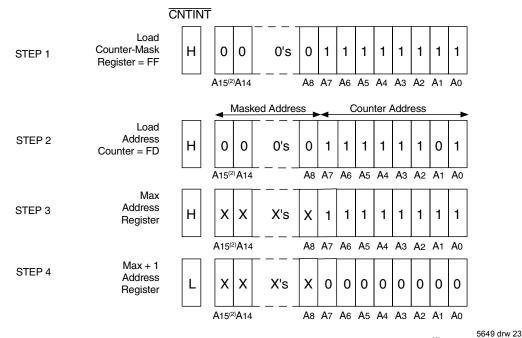

| CNTLD <sub>P1</sub>         | CNTLDP2                     | <b>CNTLD</b> P3             | CNTLDP4                     | Counter Load Input. Asserting this signal LOW ( $\overline{\text{CNTLD}}$ = V <sub>IL</sub> ) loads the address on the address lines (A <sub>0</sub> - A <sub>15</sub> <sup>(1)</sup> ) into the internal address counter for that port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CNTINCP1                    | CNTINCP2                    | <b>CNTINC</b> P3            | CNTINCP4                    | Counter Increment Input. Asserting this signal LOW ( $\overline{\text{CNTINC}} = \text{VL}$ ) increments the internal address counter for that port on each rising edge of the clock signal. The counter will increment as defined by the counter mask register for that port (default mode is to advance one address on each clock cycle).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CNTRD <sub>P1</sub>         | CNTRD <sub>P2</sub>         | CNTRDP3                     | CNTRD <sub>P4</sub>         | Counter Readback Input. When asserted LOW ( $\overline{\text{CNTRD}} = \text{V}_{\mathbb{L}}$ ) causes that port to output the value of its internal address counter on the address lines for that port. Counter readback is independent of the chip enables for that port. If the port is activated ( $\overline{\text{CE0}} = \text{V}_{\mathbb{L}}$ and $\text{CE1} = \text{V}_{\mathbb{H}}$ ), during the counter readback operation, then the data bus will output the data associated with that readback address in the FourPort memory array (assuming that the byte enables and output enables are also asserted). Truth Table III indicates the required states for all other counter controls during this operation. The specific operation and timing of this function is described in detail in the text. |

| CNTRST <sub>P1</sub>        | CNTRST <sub>P2</sub>        | <b>CNTRST</b> P3            | CNTRSTP4                    | Counter Reset Input. Asserting this signal LOW ( $\overline{\text{CNTRST}} = V\mathbb{L}$ ) resets the address counter for that port to zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CNTINTP1                    | CNTINT <sub>P2</sub>        | CNTINT <sub>P3</sub>        | CNTINTP4                    | Counter Interrupt Flag Output. This signal is asserted LOW ( $\overline{\text{CNTINT}} = V_{\text{L}}$ ) when the internal address counter for that port 'wraps around' from max address [(the counter will increment as defined by the counter mask register for that port (default mode is to advance one address on each clock cycle)] to address min. as the result of counter increment ( $\overline{\text{CNTINT}} = V_{\text{L}}$ ). The signal goes LOW for one clock cycle, then automatically resets.                                                                                                                                                                                                                                                                                                       |

5649 tbl 01

# **Pin Definitions (con't.)**

| Port 1             | Port 2 | Port 3 | Port 4 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|--------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MKLD <sub>P1</sub> | MKLDp2 | MKLDP3 | MKLDP4 | Counter Mask Register Load Input. Asserting this signal LOW ( $\overline{\text{MKLD}}$ = VL) loads the address on the address lines (A <sub>0</sub> - A <sub>15</sub> <sup>(1)</sup> ) into the counter mask register for that port. Counter mask register operations are described in detail in the text.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MKRDp1             | MKRDp2 | MKRDp3 | MKRDP4 | Counter Mask Register Readback Input. Asserting this signal LOW ( $\overline{MKRD} = V_{IL}$ ) causes that port to output the value of its internal counter mask register on the address lines (A <sub>0</sub> - A <sub>15</sub> <sup>(1)</sup> ) for that port. Address Counter and Counter-Mask Operational Table indicates the required states for all other counter controls during this operation. Counter mask register readback is independent of the chip enables for that port. If the port is activated ( $\overline{CE_0} = V_{IL}$ and $CE_1 = V_{IH}$ ) during the counter mask register readback operation, then the data bus will output the data associated with that address in the FourPort memory array ( assuming that the byte enables and output enables are also asserted). The specific operation and timing of this function is described in detail in the text. |

| ÎNT <sub>P1</sub>  | ĪNTp2  | ĪNTp3  | ĪNTp4  | Interrupt Flag Output. The FourPort is equipped with mailbox functions:<br>each port has a specific address within the memory array which, when<br>written by any of the other ports, will generate an interrupt flag to that<br>port. The port clears its interrupt by reading that address. The memory<br>location is a valid address for data storage: a full 18-bit word can be<br>stored for recall by the target port or any other port. The mailbox<br>functions and associated interrupts are described in detail in the text.                                                                                                                                                                                                                                                                                                                                                    |

| TMS                |        |        |        | JTAG Input: Test Mode Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TRST               |        |        |        | JTAG Input: Test Mode Reset (Intialize TAP Controller and reset the MBIST Controller)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ТСК                |        |        |        | JTAG Input: Test Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TDI                |        |        |        | JTAG Input: Test Data Input (serial)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDO                |        |        |        | JTAG Output: Test Data Output (serial)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLKMBIST           |        |        |        | MBIST Input: MBIST Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GND                |        |        |        | Thermal Grounds (should be treated like Vss)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vdd                |        |        |        | Core Power Supply (3.3V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vss                |        |        |        | Electrical Grounds (0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

NOTE:

1. A15x is a NC for IDT70V5378.

5649 tbl 02

Industrial and Commercial Temperature Ranges

# Truth Table I—Read/Write and Enable Control<sup>(1,2,3)</sup>

| ŌĒ    | CLK        | Ē₽ | CE1 | ŪB | LB | R/W | Upper Byte<br>I/O9-17 | Lower Byte<br>I/O₀-8 | MODE                     |

|-------|------------|----|-----|----|----|-----|-----------------------|----------------------|--------------------------|

| Х     | $\uparrow$ | Н  | Х   | Х  | Х  | Х   | High-Z                | High-Z               | Deselected–Power Down    |

| Х     | ↑          | Х  | L   | Х  | Х  | Х   | High-Z                | High-Z               | Deselected–Power Down    |

| Х     | ←          | L  | Н   | Н  | Н  | Х   | High-Z                | High-Z               | All Bytes Deselected     |

| Х     | Ŷ          | L  | Н   | Н  | L  | L   | High-Z                | Din                  | Write to Lower Byte Only |

| Х     | ←          | L  | Н   | L  | Н  | L   | Din                   | High-Z               | Write to Upper Byte Only |

| Х     | Ŷ          | L  | Н   | L  | L  | L   | Din                   | Din                  | Write to Both Bytes      |

| L     | ↑          | L  | Н   | Н  | L  | Н   | High-Z                | Dout                 | Read Lower Byte Only     |

| L     | ↑          | L  | Н   | L  | Н  | Н   | Dout                  | High-Z               | Read Upper Byte Only     |

| L     | Ŷ          | L  | Н   | L  | L  | Н   | Dout                  | Dout                 | Read Both Bytes          |

| Н     | Ŷ          | Х  | Х   | Х  | Х  | Х   | High-Z                | High-Z               | Outputs Disabled         |

| NOTES |            |    |     |    |    |     |                       |                      | 5649 tbl 03              |

#### NOTES:

1. "H" = VIH, "L" = VIL, "X" = Don't Care.

2.  $\overline{\text{CNTLD}}$ ,  $\overline{\text{CNTINC}}$ ,  $\overline{\text{CNTRST}}$  = VIH.

3. OE is an asynchronous input signal.

| External<br>Address | Previous<br>Internal<br>Address | Internal<br>Address<br>Used | CLK        | CNTLD            | CNTINC           | CNTRST           | MKLD | I/O                     | MODE                                                  |

|---------------------|---------------------------------|-----------------------------|------------|------------------|------------------|------------------|------|-------------------------|-------------------------------------------------------|

| Х                   | Х                               | 0                           | $\uparrow$ | Х                | Х                | L <sup>(3)</sup> | Х    | Dvo(0)                  | Counter Reset to Address 0                            |

| An                  | Ap                              | Ap                          | $\uparrow$ | Х                | Х                | Н                | L    | Dvo(p)                  | Counter disabled (Ap reused)                          |

| An                  | Х                               | An                          | $\uparrow$ | L <sup>(3)</sup> | Х                | Н                | Н    | Dvo (n)                 | External Address Used                                 |

| An                  | Ap                              | Ар                          | $\uparrow$ | Н                | Н                | Н                | Н    | Dvo(p)                  | External Address Blocked—Counter disabled (Ap reused) |

| Х                   | Ар                              | Ap + 1 <sup>(5)</sup>       | ↑          | Н                | L <sup>(4)</sup> | Н                | Н    | Dvo(p+1) <sup>(5)</sup> | Counter Enabled—Internal Address generation           |

|                     |                                 |                             |            |                  |                  |                  |      |                         | 5649 tbl 04                                           |

#### NOTES:

1. "H" = VIH, "L" = VIL, "X" = Don't Care.

2. Read and write operations are controlled by the appropriate setting of R/ $\overline{W}$ ,  $\overline{CE}_0$ , CE1,  $\overline{LB}$ ,  $\overline{UB}$  and  $\overline{OE}$ .

3. CNTLD and CNTRST are independent of all other memory control signals including CE0, CE1 and LB, UB.

4. The address counter advances if CNTINC = VIL on the rising edge of CLK, regardless of all other memory control signals including CE0, CE1, LB, UB.

5. The counter will increment as defined by the counter mask register for that port (default mode is to advance one address on each clock cycle).

5649 tbl 05

# Address Counter and Counter-Mask Control Operational Table (Any Port)<sup>(1,2)</sup>

| CLK        | MRST | CNTRST | MKLD             | CNTLD | CNTINC | CNTRD | MKRD | Mode             | Operation                                                                                           |

|------------|------|--------|------------------|-------|--------|-------|------|------------------|-----------------------------------------------------------------------------------------------------|

| х          | L    | Х      | Х                | Х     | Х      | Х     | Х    | Master-<br>Reset | Counter/Address Register Reset and Mask Register<br>Set (resets chip as per reset state definition) |

| $\uparrow$ | Н    | L      | Х                | Х     | Х      | Х     | Х    | Reset            | Counter/Address Register Reset                                                                      |

| $\uparrow$ | Н    | Н      | L                | Х     | Х      | Х     | Х    | Load             | Load of Address Lines into Mask Register                                                            |

| ↑          | Н    | Н      | Н                | L     | Х      | Х     | Х    | Load             | Load of Address Lines into Counter/Address<br>Register                                              |

| $\uparrow$ | Н    | Н      | Н                | Н     | L      | Х     | Х    | Increment        | Counter Increment                                                                                   |

| ↑          | Н    | Х      | Х                | Х     | Х      | L     | Х    | Read-<br>back    | Readback Counter on Address Lines                                                                   |

| ¢          | Н    | Х      | Х                | Х     | Х      | Н     | L    | Read-<br>back    | Readback Mask Register on Address Lines                                                             |

| ↑          | Н    | Н      | H <sup>(3)</sup> | Н     | Н      | Х     | Х    | Hold             | Counter Hold                                                                                        |

NOTES:

1. "X" = "don't care", "H" = VIH, "L" = VIL.

2. Counter operation and mask register operation is independent of Chip Enable.

3. MKLD = VIL will also hold the counter. Please refer to Truth Table II.

# Recommended Operating Temperature and Supply Voltage<sup>(1)</sup>

| Grade      | Ambient<br>Temperature | GND | VDD                 |

|------------|------------------------|-----|---------------------|

| Commercial | 0°C to +70°C           | 0V  | 3.3V <u>+</u> 150mV |

| Industrial | -40°C to +85°C         | 0V  | 3.3V <u>+</u> 150mV |

NOTES:

1. This is the parameter TA. This is the "instant on" case temperature.

# **Recommended DC Operating** Conditions

| Symbol | Parameter                                             | Min.    | Тур. | Max.                       | Unit |  |  |  |  |

|--------|-------------------------------------------------------|---------|------|----------------------------|------|--|--|--|--|

| Vdd    | Supply Voltage                                        | 3.15    | 3.3  | 3.45                       | ۷    |  |  |  |  |

| Vss    | Ground                                                | 0       | 0    | 0                          | ۷    |  |  |  |  |

| Vн     | Input High Voltage<br>(Address, Control & I/O Inputs) | 2.0     | _    | Vdd + 150mV <sup>(2)</sup> | ۷    |  |  |  |  |

| VIL    | Input Low Voltage                                     | -0.3(1) | _    | 0.8                        | ۷    |  |  |  |  |

| NOTES  | 5649 tbl 07                                           |         |      |                            |      |  |  |  |  |

NOTES:

5649 tbl 06

1. Undershoot of VIL  $\geq$  -1.5V for pulse width less than 10ns is allowed.

2. VTERM must not exceed VDD + 150mV.

# Absolute Maximum Ratings<sup>(1)</sup>

| Symbol               | Rating                                  | Commercial & Industrial | Unit |

|----------------------|-----------------------------------------|-------------------------|------|

| Vterm <sup>(2)</sup> | Terminal Voltage<br>with Respect to GND | -0.5 to +4.6            | V    |

| TBIAS <sup>(3)</sup> | Temperature Under Bias                  | -55 to +125             | °C   |

| Tstg                 | Storage Temperature                     | -65 to +150             | °C   |

| Tjn                  | Junction Temperature                    | +150                    | °C   |

| Ιουτ                 | DC Output Current                       | 50                      | mA   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- VTERM must not exceed VDD + 150mV for more than 25% of the cycle time or 4ns maximum, and is limited to ≤ 20mA for the period of VTERM ≥ VDD + 150mV.

Achieved Termson and the DOD Price No. Achieved Termson and termson and

- 3. Ambient Temperature under DC Bias. No AC conditions. Chip Deselected.

# Capacitance<sup>(1)</sup>

### (TA = +25°C, F = 1.0MHz)

| Symbol              | Parameter          | Conditions <sup>(2)</sup> | Max. | Unit     |

|---------------------|--------------------|---------------------------|------|----------|

| CIN                 | Input Capacitance  | Vin = 3dV                 | 8    | pF       |

| Cout <sup>(3)</sup> | Output Capacitance | Vout = 3dV                | 10.5 | pF       |

|                     |                    |                           | 564  | 9 tbl 09 |

NOTES:

1. These parameters are determined by device characterization, but are not production tested.

2. 3dV references the interpolated capacitance when the input and output switch from 0V to 3V or from 3V to 0V.

3. COUT also references CI/O.

### DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (VDD = 3.3V ± 150mV) 70V5388/7

5623 tbl 06

|        |                                             |                                             | 70V53 | 88/785 |           |

|--------|---------------------------------------------|---------------------------------------------|-------|--------|-----------|

| Symbol | Parameter                                   | Test Conditions                             | Min.  | Max.   | Unit      |

| lu     | Input Leakage Current <sup>(1)</sup>        | $V_{DD} = Max., V_{IN} = 0V$ to $V_{DD}$    | —     | 10     | μA        |

| Lu     | JTAG Input Leakage Current <sup>(1,2)</sup> | $V_{DD} = Max., V_{IN} = 0V$ to $V_{DD}$    | —     | 30     | μA        |

| llo    | Output Leakage Current <sup>(1)</sup>       | Vout = 0V to VDD, Outputs in tri-state mode | —     | 10     | μA        |

| Vol    | Output Low Voltage                          | Iol = +4mA, Vdd = Min.                      | —     | 0.4    | V         |

| Vон    | Output High Voltage                         | IOH = -4mA, VDD = Min.                      | 2.4   | _      | V         |

| NOTE   |                                             |                                             |       | 56     | 49 tbl 10 |

NOTE:

1. At  $V_{DD} \leq 2.0V$  leakages are undefined.

2. Applicable only for TMS, TDI and TRST inputs.

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(3)</sup> (VDD = 3.3V ± 150mV)

|        |                                          |                                                                                                                                                                |        |   |                     | 3/78S200<br>I Only | Co                  | 8/78S166<br>m'l<br>Ind | Co                  | 8/78S133<br>m'I<br>Ind | Co                  | 8/78S100<br>m'I<br>Ind |      |

|--------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---|---------------------|--------------------|---------------------|------------------------|---------------------|------------------------|---------------------|------------------------|------|

| Symbol | Parameter                                | Test Condition                                                                                                                                                 | Versio | n | Typ. <sup>(4)</sup> | Max.               | Typ. <sup>(4)</sup> | Max.                   | Typ. <sup>(4)</sup> | Max.                   | Typ. <sup>(4)</sup> | Max.                   | Unit |

| IDD    | Dynamic Operating                        | $\overline{CE}1 = \overline{CE}_2 = \overline{CE}_3 = \overline{CE}_4^{(5)} = VIL,$                                                                            | COM'L  | S | 405                 | 470                | 340                 | 395                    | 275                 | 320                    | 205                 | 240                    |      |

|        | Current (All<br>Ports Active)            | Outputs Disabled,<br>f = fMAX <sup>(1)</sup>                                                                                                                   | IND    | S | _                   | -                  | 340                 | 400                    | 275                 | 325                    | 205                 | 245                    | mA   |

| ISB1   | Standby Current                          | $\overline{CE}1 = \overline{CE}_2 = \overline{CE}_3 = \overline{CE}_4^{(5)} = V_{IH},$                                                                         | COM'L  | S | 195                 | 225                | 160                 | 190                    | 130                 | 155                    | 100                 | 120                    |      |

|        | (All Ports - TTL<br>Level Inputs)        | Outputs Disabled,<br>f = fMAX <sup>(1)</sup>                                                                                                                   | IND    | S | _                   | -                  | 160                 | 195                    | 130                 | 160                    | 100                 | 125                    | mA   |

| ISB2   | Standby Current                          | $\overline{CEA} = VIL and \overline{CEB} = \overline{CEC} = \overline{CED} = VIH^{(5)}$                                                                        | COM'L  | S | 250                 | 290                | 210                 | 240                    | 170                 | 195                    | 130                 | 150                    |      |

|        | (One Port - TTL<br>Level Inputs)         | Active Port, Outputs Disabled,<br>f=fMAX <sup>(1)</sup>                                                                                                        | IND    | S | _                   | -                  | 210                 | 245                    | 170                 | 200                    | 130                 | 155                    | mA   |

| ISB3   | Full Standby Current (All                | All Ports Outputs Disabled,                                                                                                                                    | COM'L  | S | 1.5                 | 15                 | 1.5                 | 15                     | 1.5                 | 15                     | 1.5                 | 15                     |      |

|        | Ports - CMOS<br>Level Inputs)            | $\frac{\overline{\text{CE}}^{(5)} \ge \text{VDD} - 0.2\text{V}, \text{ VIN} \ge \text{VDD} - 0.2\text{V}}{\text{or VIN} \le 0.2\text{V}, \text{ f} = 0^{(2)}}$ | IND    | S | _                   | -                  | 1.5                 | 15                     | 1.5                 | 15                     | 1.5                 | 15                     | mA   |

| ISB4   | Full Standby Current<br>(One Port - CMOS | $\overline{CEA} \leq 0.2V$ and $\overline{CEB} = \overline{CEC} = \overline{CED} \geq VDD - 0.2V^{(5)}$                                                        | COM'L  | S | 250                 | 290                | 210                 | 240                    | 170                 | 195                    | 130                 | 150                    |      |

|        | Level Inputs)                            | $VIN \ge VDD - 0.2V$ or $VIN \le 0.2V$<br>Active Port, Outputs Disabled, f = fMAX <sup>(1)</sup>                                                               |        | S | _                   | _                  | 210                 | 245                    | 170                 | 200                    | 130                 | 155                    | mA   |

5649 tbl 11

#### NOTES:

1. At f = fMAX, address and control lines (except Output Enable) are cycling at the maximum frequency clock cycle of 1/tcyc, using "AC TEST CONDITIONS" at input levels of GND to 3V.

2. f = 0 means no address, clock, or control lines change. Applies only to input at CMOS level standby.

- 3. Parameters are identical for all ports.

- 4. VDD = 3.3V, TA =  $25^{\circ}C$  for Typ, and are not production tested. IDD DC(f=0) = 120mA (Typ).

- 5.  $\overline{CE}x = VIL$  means  $\overline{CE}_{0X} = VIL$  and  $CE_{1X} = VIH$

- $\overline{CE}x = VIH$  means  $\overline{CE}0x = VIH$  or CE1x = VIL

$\overline{CEx} \le 0.2V$  means  $\overline{CE} x \le 0.2V$  and  $CE_{1X} \ge V_{DD} - 0.2V$

$\overline{\text{CEx}} \ge \text{VDD} - 0.2\text{V}$  means  $\overline{\overline{\text{CE}}} \text{ox} \ge \text{VDD} - 0.2\text{V}$  or CE1x - 0.2V

"X" represents indicator for appropriate port.

| IDT70V5388/78                            |            |

|------------------------------------------|------------|

| 3.3V 64/32K x 18 Synchronous FourPort™ 3 | Static RAM |

Industrial and Commercial Temperature Ranges

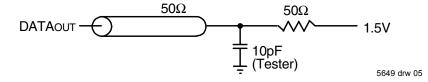

# AC Test Conditions (VDDQ - 3.3V)

| Input Pulse Levels (Address & Controls) | GND to 3.0V |  |  |  |  |

|-----------------------------------------|-------------|--|--|--|--|

| Input Pulse Levels (I/Os)               | GND to 3.0V |  |  |  |  |

| Input Rise/Fall Times                   | 2ns         |  |  |  |  |

| Input Timing Reference Levels           | 1.5V        |  |  |  |  |

| Output Reference Levels                 | 1.5V        |  |  |  |  |

| Output Load                             | Figure 1    |  |  |  |  |

5649 tbl 12

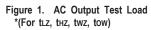

Figure 2. Typical Output Derating (Lumped Capacitive Load).

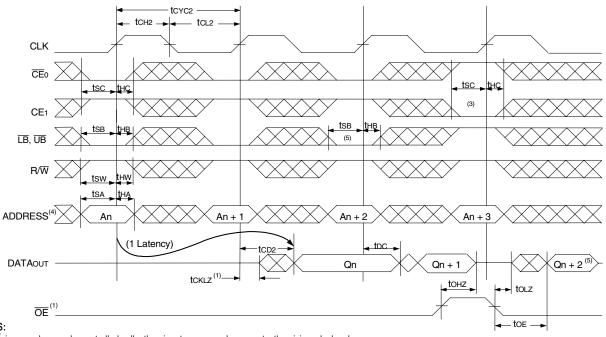

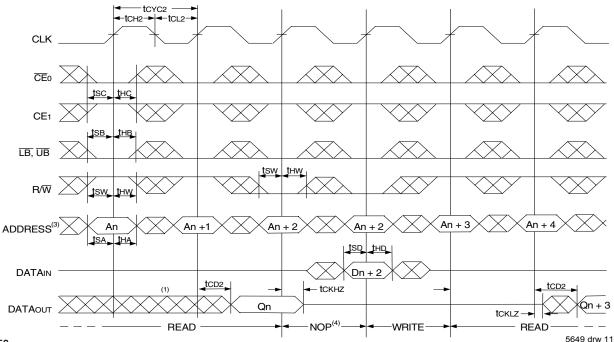

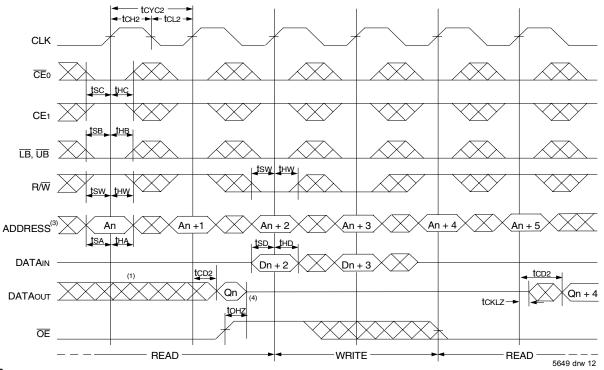

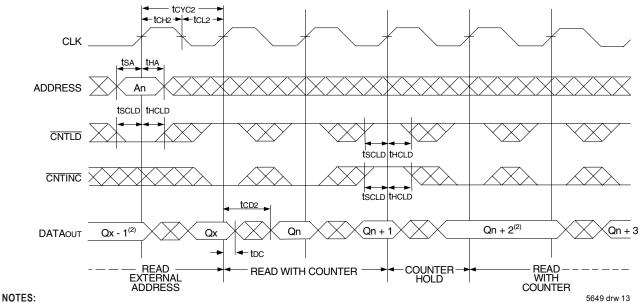

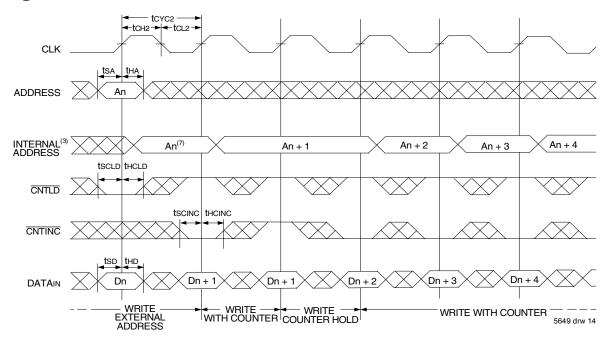

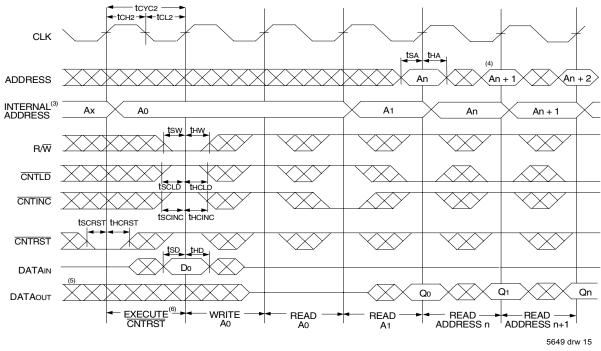

# AC Electrical Characteristics Over the Operating Temperature Range (Read and Write Cycle Timing) (VDD = 3.3V ± 150mV, TA = 0°C to +70°C)

|                          |                                         | 70V538 | 8/78S200<br>I Only | 70V538<br>Co | 8/78S166<br>om'l<br>Ind | 70V5388<br>Co | 8/78S133<br>om'l<br>Ind | 70V5388/78S100<br>Com'l<br>& Ind |      |      |

|--------------------------|-----------------------------------------|--------|--------------------|--------------|-------------------------|---------------|-------------------------|----------------------------------|------|------|

| Symbol                   | Parameter                               | Min.   | Max.               | Min.         | Max.                    | Min.          | Max.                    | Min.                             | Max. | Unit |

| fMAX2                    | Maximum Frequency                       | _      | 200                |              | 166                     |               | 133                     | _                                | 100  | MHz  |

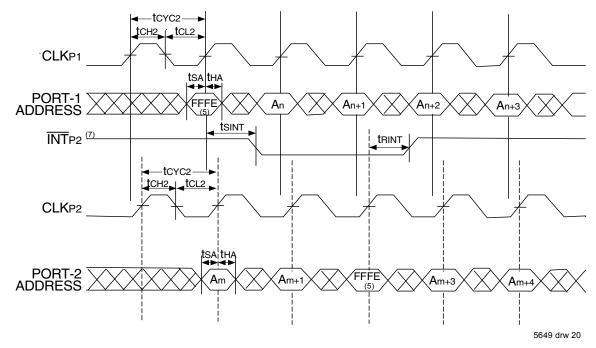

| tCYC2                    | Clock Cycle Time                        | 5      | -                  | 6            | _                       | 7.5           | _                       | 10                               | -    | ns   |

| tCH2                     | Clock HIGH Time                         | 2.0    | _                  | 2.1          | _                       | 2.6           | _                       | 4                                | _    | ns   |

| tCL2                     | Clock LOW Time                          | 2.0    | —                  | 2.1          |                         | 2.6           | _                       | 4                                | —    | ns   |

| tsa                      | Address Setup Time                      | 1.5    | —                  | 1.7          | _                       | 1.8           | _                       | 2                                | —    | ns   |

| tHA                      | Address Hold Time                       | 0.5    |                    | 0.5          |                         | 0.5           |                         | 0.7                              | —    | ns   |

| tsc                      | Chip Enable Setup Time                  | 1.5    |                    | 1.7          |                         | 1.8           |                         | 2                                | —    | ns   |

| tHC                      | Chip Enable Hold Time                   | 0.5    | —                  | 0.5          | _                       | 0.5           | _                       | 0.7                              | —    | ns   |

| tsw                      | R/W Setup Time                          | 1.5    |                    | 1.7          |                         | 1.8           |                         | 2                                | —    | ns   |

| tHW                      | R/W Hold Time                           | 0.5    | —                  | 0.5          | _                       | 0.5           | _                       | 0.7                              | —    | ns   |

| tsD                      | Input Data Setup Time                   | 1.5    | —                  | 1.7          | _                       | 1.8           | —                       | 2                                | —    | ns   |

| tHD                      | Input Data Hold Time                    | 0.5    | —                  | 0.5          |                         | 0.5           | _                       | 0.7                              | —    | ns   |

| tsв                      | Byte Setup Time                         | 1.5    | -                  | 1.7          | _                       | 1.8           | _                       | 2                                | _    | ns   |

| tнв                      | Byte Hold Time                          | 0.5    | —                  | 0.5          | _                       | 0.5           | _                       | 0.7                              | —    | ns   |

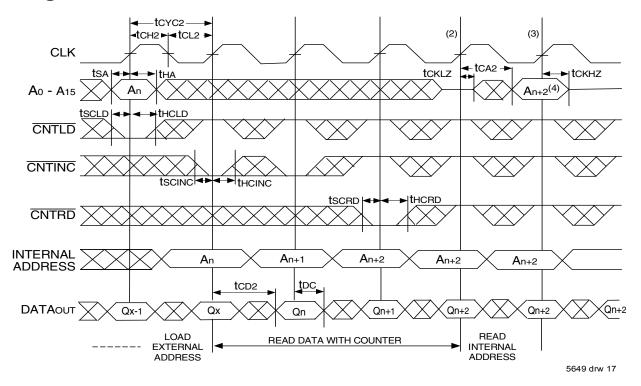

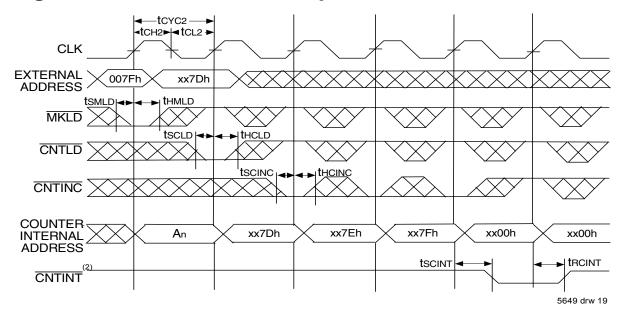

| tsclD                    | CNTLD Setup Time                        | 1.5    | _                  | 1.7          | _                       | 1.8           | _                       | 2                                | _    | ns   |

| tHCLD                    | CNTLD Hold Time                         | 0.5    | -                  | 0.5          | _                       | 0.5           | _                       | 0.7                              | _    | ns   |

| tscinc                   | CNTINC Setup Time                       | 1.5    |                    | 1.7          | —                       | 1.8           |                         | 2                                | —    | ns   |

| THCINC                   | CNTINC Hold Time                        | 0.5    |                    | 0.5          | —                       | 0.5           |                         | 0.7                              | —    | ns   |

| tSCRST                   | CNTRST Setup Time                       | 1.5    |                    | 1.7          | _                       | 1.8           |                         | 2                                | —    | ns   |

| tHCRST                   | CNTRST Hold Time                        | 0.5    |                    | 0.5          | _                       | 0.5           |                         | 0.7                              | —    | ns   |

| tSCRD                    | CNTRD Setup Time                        | 1.5    |                    | 1.7          |                         | 1.8           | _                       | 2                                |      | ns   |

| tHORD                    | CNTRD Hold Time                         | 0.5    |                    | 0.5          | _                       | 0.5           |                         | 0.7                              | —    | ns   |

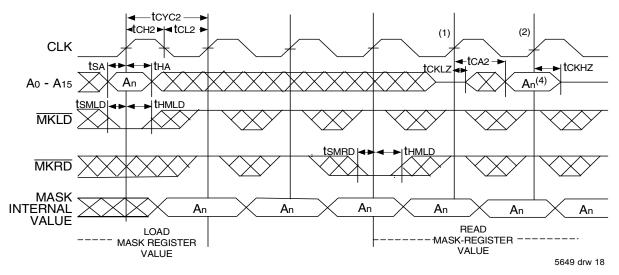

| tsmld                    | MKLD Setup Time                         | 1.5    |                    | 1.7          |                         | 1.8           | _                       | 2                                |      | ns   |

| thmld                    | MKLD Hold Time                          | 0.5    | _                  | 0.5          | _                       | 0.5           | _                       | 0.7                              | —    | ns   |

| tsmrd                    | MKRD Setup Time                         | 1.5    | _                  | 1.7          | _                       | 1.8           | _                       | 2                                | _    | ns   |

| tHMRD                    | MKRD Hold Time                          | 0.5    | _                  | 0.5          | _                       | 0.5           | _                       | 0.7                              | _    | ns   |

| tOE                      | Output Enable to Data Valid             | _      | 4.0                | _            | 4.0                     | _             | 4.2                     |                                  | 5    | ns   |

| tolz (1,5)               | OE to LOW-Z                             | 1      | _                  | 1            | _                       | 1             | _                       | 1                                | _    | ns   |

| toHZ (1,5)               | OE to HIGH-Z                            | 1      | 3.4                | 1            | 3.6                     | 1             | 4.2                     | 1                                | 4.5  | ns   |

| tCD2                     | Clock to Data Valid                     | _      | 3.0                |              | 3.2                     |               | 3.4                     |                                  | 3.6  | ns   |

| tCA2                     | Clock to Counter Address Readback Valid | _      | 3.4                |              | 3.6                     | _             | 4.2                     | _                                | 5    | ns   |

| tCM2                     | Clock to Mask Register Readback Valid   | _      | 3.4                |              | 3.6                     | _             | 4.2                     |                                  | 5    | ns   |

| tDC                      | Data Output Hold After Clock HIGH       | 1      | —                  | 1            |                         | 1             |                         | 1                                | —    | ns   |

| tckhz (1.2.5)            | Clock HIGH to Output HIGH-Z             | 1      | 3                  | 1            | 3                       | 1             | 3                       | 1                                | 3    | ns   |

| tcklz <sup>(1,2,5)</sup> | Clock HIGH to Output LOW-Z              | 1      |                    | 1            |                         | 1             |                         | 1                                | _    | ns   |

5649 tbl 13a

# AC Electrical Characteristics Over the Operating Temperature Range (Read and Write Cycle Timing) (VDD = 3.3V ± 150mV, TA = 0°C to +70°C)

|                |                                                      | 70V538 | 8/78S200<br>I Only | 70V538<br>Co | 8/78S166<br>m'l<br>Ind | 70V538<br>Co | 8/78S133<br>om'l<br>Ind | 70V5388<br>Coi<br>& I | m'l  |      |

|----------------|------------------------------------------------------|--------|--------------------|--------------|------------------------|--------------|-------------------------|-----------------------|------|------|

| Symbol         | Parameter                                            | Min.   | Max.               | Min.         | Max.                   | Min.         | Max.                    | Min.                  | Max. | Unit |

| Interrupt Tim  | ing                                                  |        |                    |              |                        |              |                         |                       | •    |      |

| tsint          | Clock to INT Set Time                                |        | 5                  |              | 6                      |              | 7.5                     |                       | 10   | ns   |

| TRINT          | Clock to INT Reset Time                              |        | 5                  | -            | 6                      | _            | 7.5                     |                       | 10   | ns   |

| tscint         | Clock to CNTINT Set Time                             |        | 5                  |              | 6                      |              | 7.5                     |                       | 10   | ns   |

| <b>t</b> RCINT | Clock to CNTINT Reset Time                           |        | 5                  |              | 6                      |              | 7.5                     |                       | 10   | ns   |

| Master Reset   | Timing                                               |        |                    |              |                        |              |                         |                       |      |      |

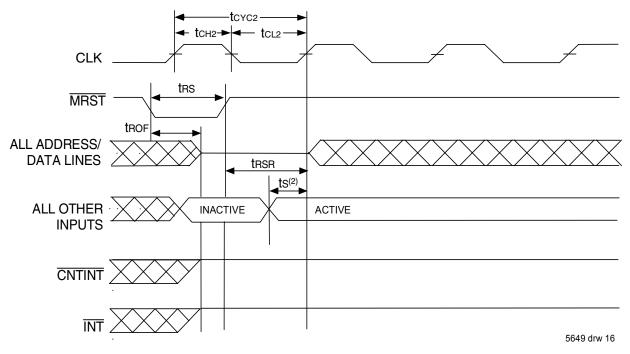

| tRS            | Master Reset Pulse Width                             | 7.5    |                    | 7.5          |                        | 7.5          |                         | 10                    |      | ns   |

| tRSR           | Master Reset Recovery Time                           | 7.5    |                    | 7.5          |                        | 7.5          | _                       | 10                    | —    | ns   |

| tROF           | Master Reset to Output Flags Reset Time              | —      | 6.5                | _            | 6.5                    | —            | 6.5                     |                       | 8    | ns   |

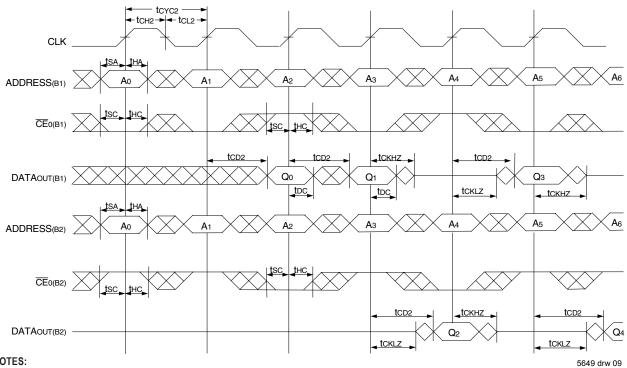

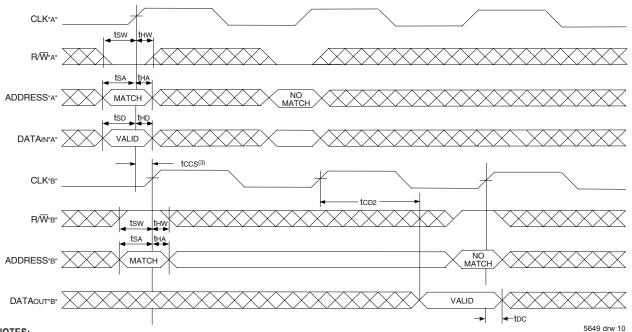

| Port to Port I | Delays                                               |        |                    |              |                        |              |                         |                       |      |      |

| tocs(3)        | Clock-to-Clock Setup Time                            | 4.5    |                    | 5            |                        | 6.5          |                         | 9                     |      | ns   |

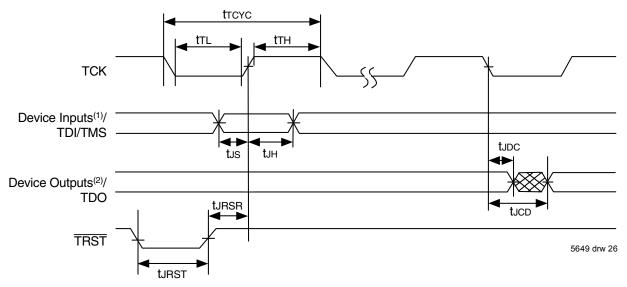

| JTAG Timing    | (4)                                                  |        |                    |              |                        |              |                         |                       |      |      |

| fjtag          | Maximum JTAG TAP Controller Frequency                |        | 10                 |              | 10                     | -            | 10                      |                       | 10   | MHz  |