# MTC-20278/9 ILT

Quad ISDN U-Interface ISDN Standard Products

Data Sheet Rev. 2.0 - February 2000

### **Key Features**

- Quad ISDN LT 'U' interface functions in a single monolithic integrated circuit

- Pin compatible 2B1Q and 4B3T line code versions

- \* MTC-20278 ILTQ for 2B1Q

- \* MTC-20279 ILTT for 4B3T

- Full compliance with the applicable ETSI, FTZ and ITU requirements

- DECT Synchronization Support (2BTQ)

- Digital interface bus using industry-standard GCI

- Minimal external components

- 3.3V operating voltage

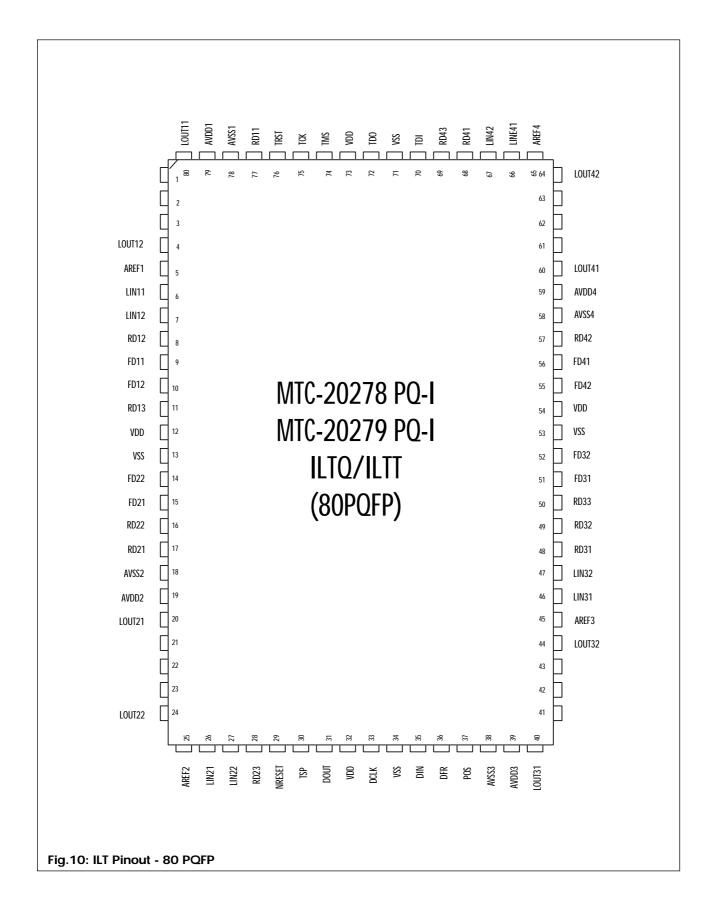

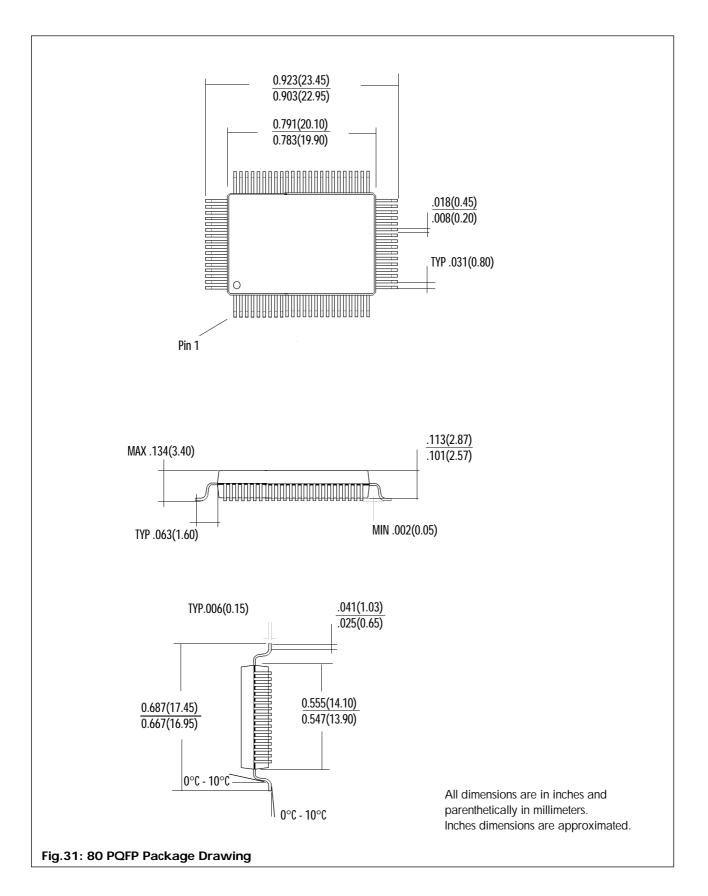

- 80 pin Plastic Quad Flat Pack package

### **Key Applications**

- ▼ ISDN Exchange Line Cards

- Remote Access Multiplex Systems

- FTTx Systems

### **General Description**

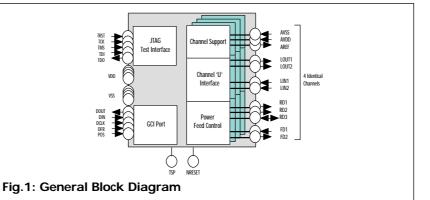

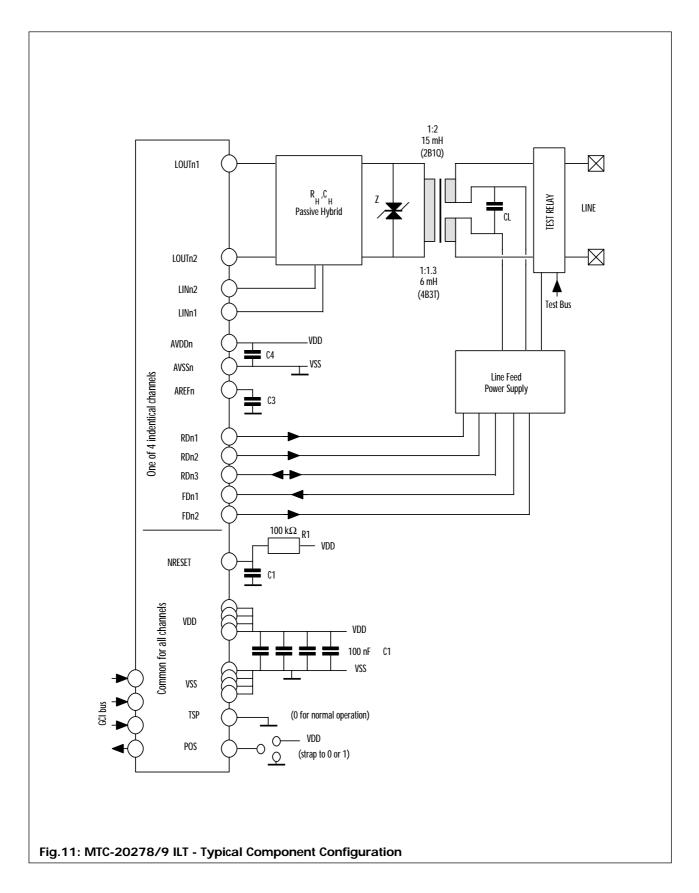

The MTC-20278/9 chip contains all the functions necessary to make 4 'U' interfaces in an ISDN Line Termination card. It comprises 4, fully integrated echo-canceling 'U' interfaces, plus the necessary support and test functions. The general block diagram is shown in Figure 1. By integrating 4 complete U Interfaces in a single high density package, the MTC-20278/9 makes it possible to integrate more lines on one card, this reducing the cost per line. Two versions of the device are available - the MTC-20278 offering the 2B1Q line code, and the MTC-20279 which has 4B3T line coding. Both devices are pin compatible, and are fully compliant with the relevant parts of ETSI, FTZ and ITU requirements for ISDN connection.

The MTC-20278/9 device offers a user transport rate of 144kbit/s full duplex (2B + D) per channel, as well as fully automatic control of activate/deactivate protocols, and full support of the maintenance channel. Digital I/O for Powerfeed Control, and DECT Synchronization (MTC-20278 only) are provided for 4 identical channels.

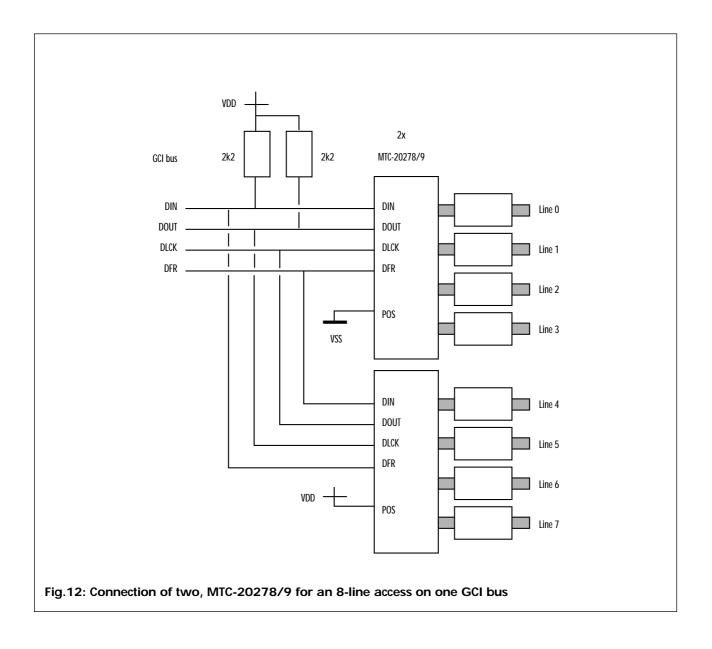

The digital interface on the 'exchange' side uses the industry-standard GCI interface in 2 Mbit burst mode. This mode allows for 8 channels to be multiplexed onto the same interface. The MTC-20278/9 can be set to respond to either the first 4 or the last 4 timeslots in the GCI frame. This allows two devices, totalling 8 ISDN lines, to be multiplexed onto the same GCI interface.

The MTC-20278/9 takes all timing information from the GCI clocks, and so does not require a separate clock oscillator.

#### **Ordering Information**

| Part number   | Package | Temp.         |

|---------------|---------|---------------|

| MTC-20278PQ-I | 80PQFP  | -40 to + 85°C |

| MTC-20278PQ-C | 80PQFP  | 0 to + 70°C   |

| MTC-20279PQ-I | 80PQFP  | -40 to + 85°C |

| MTC-20279PQ-C | 80PQFP  | 0 to + 70°C   |

### **Relevant Standards**

- ETSI TS 102 080, 1998

- ETS 300 012

- ETS 300 297

- CCITT / ITU Recommendation G.961

- ANSI T1.601, BA ISDN specifications 1992

### **Functional Characteristics**

### The U-Interface

NOTE: Some of the specifications in this section refer to the UO Interface and not to the line ports (LOUT1, LOUT2, LIN1, LIN2). The characteristics at the line port are affected by the design of the transformer and the other external components.

### MTC-20278

#### **Physical Characteristics**

The quaternary symbol stream on the U-interface complies to the following physical characteristics:

#### 1) Symbol Rate

The symbol rate is 80 kbaud  $\pm$ 1 ppm and applies to synchronous symbol transmission. The symbol rate is controlled by the external clock.

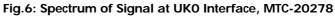

#### 2) Input Jitter

The ILTQ tolerates a sinusoidal input jitter of the quaternary symbols as shown in Figure 5.

#### 3) Output Jitter

The peak-to-peak jitter produced by the ILTQ doesn't exceed 0.02 UI when measured via a high pass filter with a cut-off frequency of 30Hz. Without this filter, the same measurement doesn't read more than 0.1 UI. To obtain this performance, the jitter on the GCI input clock should not exceed 15ns peak-to-peak

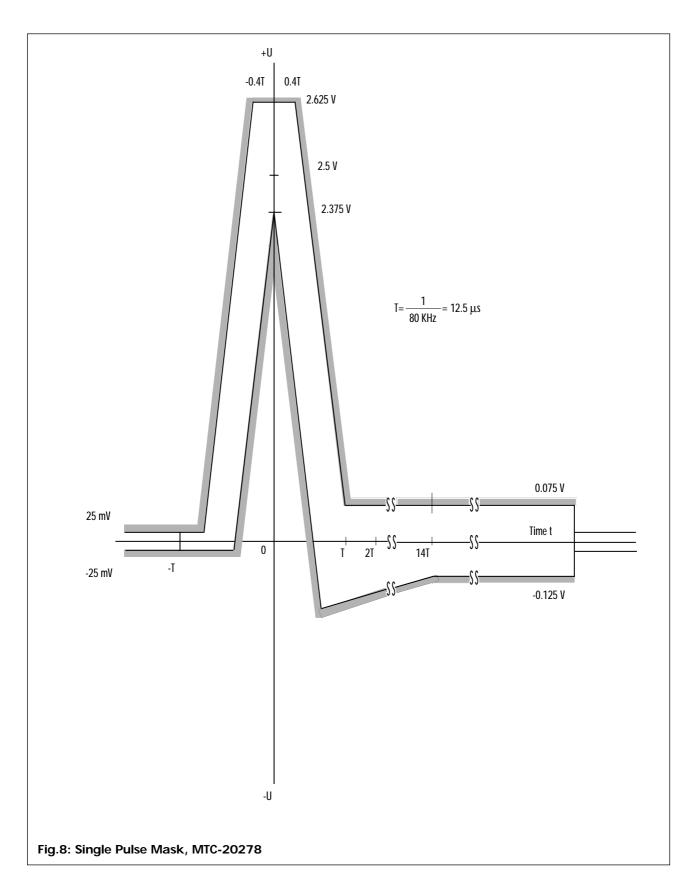

### 4) Transmit Signal Amplitude

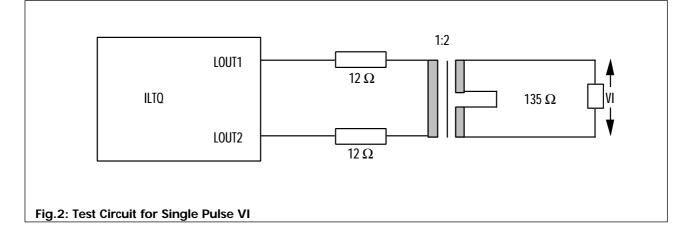

The absolute peak value VImax of a single pulse VI at UO interface terminated with a  $135\Omega$  resistance is 2.5V ± 5%. See Figure 2 and 8.

#### 5) Stability

The transmit signal amplitude measured over a periode of one minute doesn't vary by more than 1% beginning 5ms after the ILTQ is switched into power-up state.

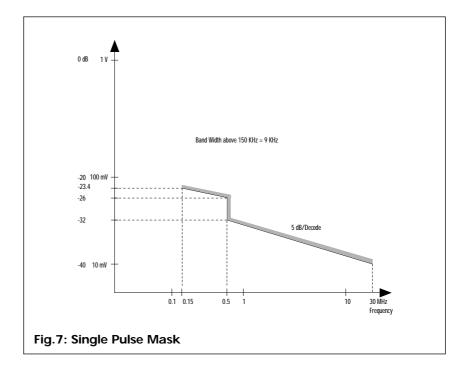

### 6) Transmit Spectrum

The spectrum of the quaternary transmit signal at UO interface doesn't exceed the limits given in Figure 7.

#### 7) Pulse Shape

A single pulse measured across a  $135\Omega$  resistance at UO interface complies to the spectral requirements presented in Figure 7 and the pulse mask requirements given in Figure 8.

#### 8) Maximum Voltage

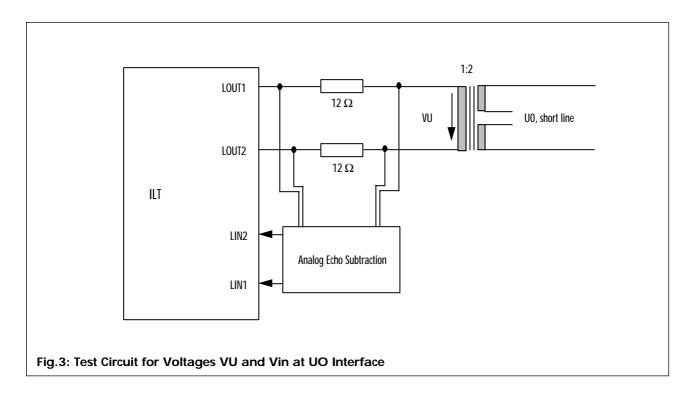

The maximum peak-to-peak value VUmax of the voltage VU as shown in Figure 3 with full receive signal (short line) is 2.5V. Due to the analog echo subtraction the maximum peak-to-peak value Vinmax of the voltage Vin between LIN1 and LIN2 is 1.7V.

### 9) Input/Output Impedance

The line terminating impedance is  $135\Omega$  in power-up and in power-down state. The return loss at U0 measured against  $135\Omega$  (real) exceeds; 20 dB between 10kHz and 25kHz.

- slope below 10kHz: 20 dB / decade

- slope above 25kHz: -20 dB / decade

### 10) Load

The load is given by the line transformer and the subscriber line. The loops are standardized by the ANSI and ETSI documents. Turns ratio of line transformer 1:2 Transformer coil inductance (from line side):  $15 \text{ mH} \pm 10\%$

### MTC-20279

### Requirements for the U- Line Ports

NOTE: Some of the specifications in this section refer to the UKO Interface and not to the line ports (LOUT1, LOUT2, LIN1, LIN2). The characteristics at the line port are affected by the design of the transformer and the other external components.

#### **Physical Characteristics**

The ternary symbol stream on the Uinterface must comply to the following physical characteristics:

#### 1) Symbol Rate

The symbol rate is 120 kbaud ± 1 ppm and applies to synchronous symbol transmission. The symbol rate is controlled by an external clock.

#### 2) Input Jitter

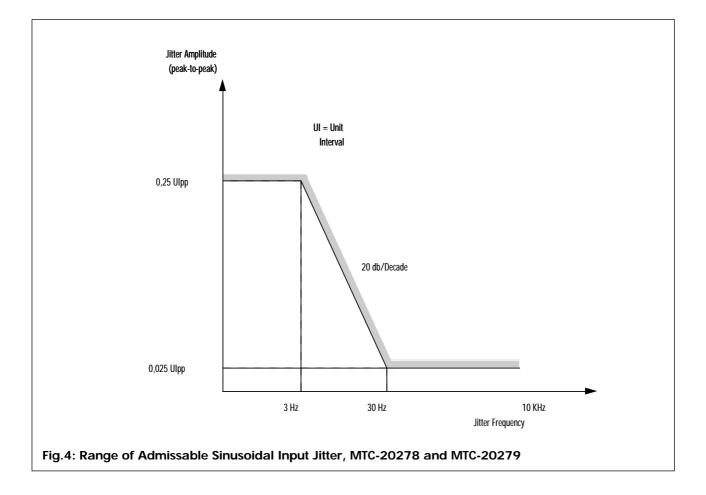

The ILTT tolerates a sinusoidal input jitter of the ternary symbols as indicated in Figure 4.

#### 3) Output Jitter

The peak-to-peak jitter produced by the ILTT doesn't exceed 0.02 UI (166ns), when measured via a high pass filter with a cut-off frequency of 30Hz. Without this filter the same measurement doesn't read more than 0.1 UI. This performance is only guaranteed when the input jitter at the GCI clock is less than 15ns peak-to-peak.

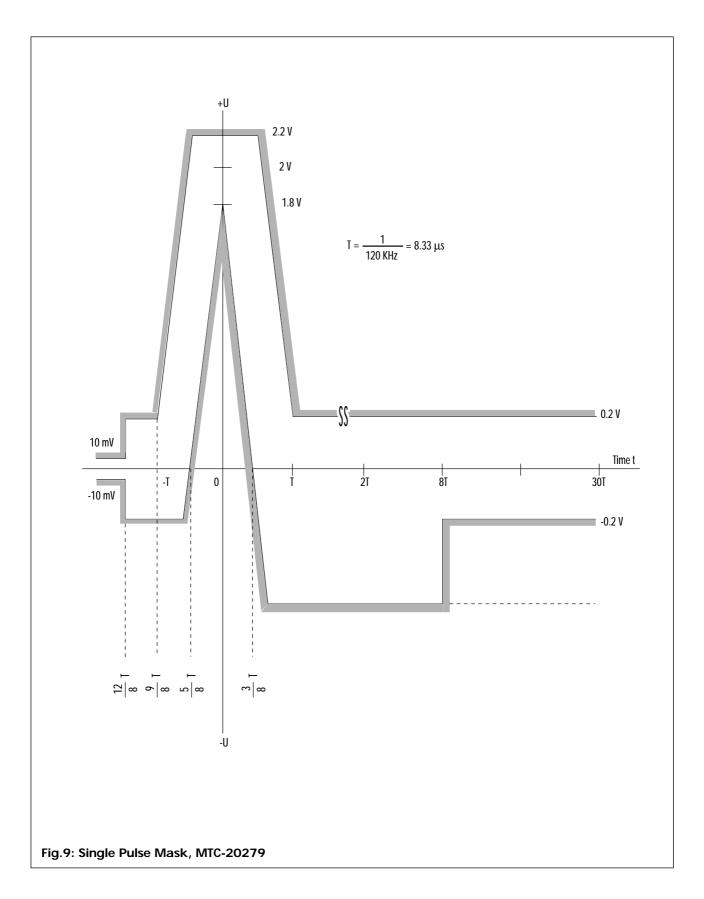

### 4) Transmit Signal Amplitude

The absolute peak value VImax of a single pulse VI at UKO interface terminated with a 150 $\Omega$  resistance is 2V ± 0.2V. See the following Figure. The absolute peak value of the coded ternary signal measured at UKO interface terminated with 150 $\Omega$  doesn't exceed 4V. See Figure 4.

#### 5) Stability

The transmit signal amplitude measured over a period of one minute doesn't vary by more than 1% beginning 5ms after the ILTT is switched into power-up state.

#### 6) Transmit Spectrum

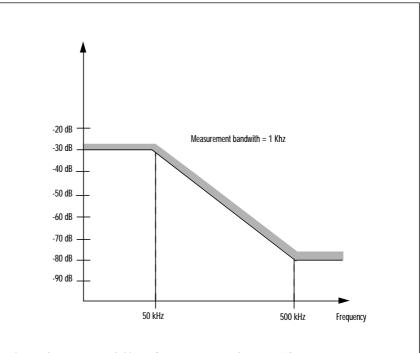

The spectrum of the ternary transmit signal at UKO interface doesn't exceed the limits given in Figure 6.

### 7) Pulse Shape

A single pulse measured across a  $150\Omega$  resistance at the UKO interface

comply to the spectral requirements presented in Figure 7 and the pulse mask requirements given in Figure 8.

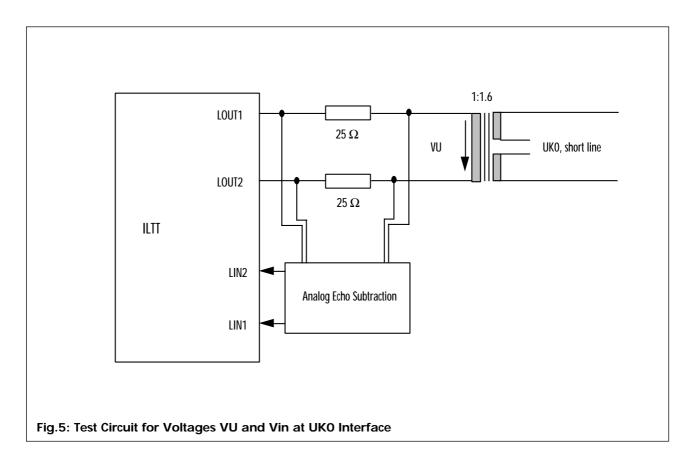

### 8) Maximum Voltage

The maximum peak-to-peak value VUmax of the voltage VU as shown in Figure 5 with full receive signal (short line), that must be accepted, is 4V. Due to the analog echo subtraction the maximum peak-to-peak value Vinmax of the voltage Vin between LIN1 and LIN2 is 2.7V. For ILTT, the value of n must be 1.6.

### 9) Input/Output Impedance

The line terminating impedance must be  $150\Omega$  in power-up and in power-down state. The return loss at UKO measured against  $150\Omega$  real must exceed 16 dB between 12kHz and 50kHz.

- slope below 12kHz: 20 dB/decade

- slope above 50kHz: -10 dB/decade

### 10) Load

The load is given by the line transformer and the subscriber line. Turns ratio of line transformer: 1.6Transformer coil inductance (from line side): 6.8mH  $\pm$  10%.

# **Pin Description**

| Nr. | Function  | Name         | Dir. | Description                                                                   |

|-----|-----------|--------------|------|-------------------------------------------------------------------------------|

| 80  |           | LOUT11       | 0    | U-Interface analog outputs. The pins LOUT11 and LOUT12                        |

|     |           |              |      | connect the U-driver outputs via termination resistors and the line           |

|     |           |              |      | coupling transformer to the UO reference point.                               |

| 4   |           | LOUT12       | 0    |                                                                               |

| 6   |           | LIN11        | I    | U-Interface analog inputs from the analog hybrid                              |

| 7   |           | LIN12        | I    |                                                                               |

| 5   | U1        | AREF1        | 0    | Analog ground. Used as reference voltage for A/D and D/A.                     |

| 79  | Interface | AVDD1        | Р    | +3.3V power supply for analog U-Interface functions                           |

| 78  |           | AVSS1        | P    | OV ground for analog U-Interface functions                                    |

| 77  |           | RD11 / SPICS | 0    | Relay drivers 1                                                               |

| 8   |           | RD12 / SPICK | 0    |                                                                               |

| 11  |           | RD13         | IO   | Bidirectional I/O. Put in Input mode after HW reset, not affected by SW reset |

| 9   |           | FD11 / SPIDI | 1    | Power feed status and control 1                                               |

| 10  |           | FD12 / SPIDO | 0    |                                                                               |

| 20  |           | LOUT21       | 0    | U-Interface analog outputs. The pins LOUT21 and LOUT22                        |

|     |           |              |      | connect the U-driver outputs via termination resistors and the line           |

|     |           |              |      | coupling transformer to the UO reference point.                               |

| 24  |           | LOUT22       | 0    |                                                                               |

| 26  |           | LIN21        | I.   | U-Interface analog inputs from the analog hybrid                              |

| 27  |           | LIN22        | I    |                                                                               |

| 25  | U2        | AREF2        | 0    | Analog ground. Used as reference voltage for A/D and D/A                      |

| 19  | Interface | AVDD2        | Р    | +3.3V power supply for analog U-Interface functions                           |

| 18  |           | AVSS2        | Р    | OV ground for analog U-Interface functions                                    |

| 17  |           | RD21         | 0    | Relay drivers 2                                                               |

| 16  |           | RD22         | 0    |                                                                               |

| 28  |           | RD23         | IO   | Bidirectional I/O. Put in Input mode after HW reset, not affected by SWreset  |

| 15  |           | FD21 / SELO  | I    | Power feed status and control 2                                               |

| 14  |           | FD22         | 0    |                                                                               |

| 40  |           | LOUT31       | 0    | U-Interface analog outputs. The pins LOUT31 and LOUT32                        |

|     |           |              |      | connect the U-driver outputs via termination resistors and the line           |

|     |           |              |      | coupling transformer to the UO reference point.                               |

| 44  |           | LOUT32       | 0    |                                                                               |

| 46  |           | LIN31        | I    | U-Interface analog inputs from the analog hybrid                              |

| 47  |           | LIN32        | I    |                                                                               |

| 45  |           | AREF3        | 0    | Analog ground. Used as reference voltage for A/D and D/A.                     |

| 39  | U3        | AVDD3        | Р    | +3.3V power supply for analog U-Interface functions                           |

| 38  | Interface | AVSS3        | Р    | OV ground for analog U-Interface functions                                    |

| 48  |           | RD31         | 0    | Relay drivers 3                                                               |

| 49  |           | RD32         | 0    |                                                                               |

| 50  |           | RD33         | IO   | Bidirectional I/O. Put in Input mode after HW reset, not affected by SW reset |

| 51  |           | FD31 / SEL1  | I    | Power feed status and control 3                                               |

| 52  |           | FD32         | 0    |                                                                               |

| 60 |           | LOUT41   | 0  | U-Interface analog outputs. The pins LOUT<br>connect the U-driver outputs via terminatic | n resistors and the line       |

|----|-----------|----------|----|------------------------------------------------------------------------------------------|--------------------------------|

| 64 |           | LOUT42   | 0  | coupling transformers to the UO reference                                                | point.                         |

| 66 |           | LIN41    |    | U-Interface analog inputs from the analog                                                | hybrid                         |

| 67 | U4        | LIN41    |    | o menace analog inpus nom me analog                                                      | nyona                          |

| 65 | Interface | AREF4    | 0  | Analog ground. Used as reference voltag                                                  | e for A/D and D/A              |

| 59 | interface | AVDD4    | P  | +3.3V power supply for analog U-Interfac                                                 |                                |

| 58 |           | AVSS4    | P. | OV ground for analog U-Interface function                                                |                                |

| 68 |           | RD41     | 0  | Relay drivers 4                                                                          | 5                              |

| 57 |           | RD42     | 0  |                                                                                          |                                |

| 69 |           | RD43     | IO | Bidirectional I/O. Put in Input mode after                                               | HW reset, not affected by      |

|    |           | 112 10   |    | SW reset                                                                                 |                                |

| 56 |           | FD41     |    | Power feed status and control 4                                                          |                                |

| 55 |           | FD42     | 0  |                                                                                          |                                |

| 31 |           | DOUT     | 0  | GCI data output at 2048 Kbits/s. Open o                                                  | drain output.                  |

| 35 | GCI       | DIN      | I  | GCI data input at 2048 Kbit/s                                                            |                                |

| 33 | Interface | DCLK     | I  | 4096kHz GCI clock                                                                        |                                |

| 36 |           | DFR      | I  | 8kHz GCI frame clock which identifies the                                                | e beginning of the frame of    |

|    |           |          |    | DIN and DOUT                                                                             |                                |

|    |           |          |    |                                                                                          | Normal use                     |

| 76 |           | TRST     | I  | TAP controller reset, active low                                                         | 0                              |

| 75 | JTAG      | TCK      | I  | TAP controller clock, maximum 10MHz                                                      | 0                              |

| 74 | Test      | TMS      | I  | TAP controller mode selection                                                            | 0                              |

| 70 | Interface | TDI      | I  | TAP controller input                                                                     | 0                              |

| 72 |           | TDO      | 0  | TAP controller output                                                                    | open                           |

| 29 |           | NRESET   | I  | Hardware reset, active low. Schmit trigge<br>(CMOS level).                               | r input with treshold at 1.65V |

| 30 |           | TSP/DECT |    | 1. Transmit Single Pulses. ILT transmits sing                                            | ale pulses of alternating      |

| 30 | General   | ISF/DLCI | I  | maximum positive and negative polarity.                                                  | 0                              |

|    | General   |          |    | Applications: test purposes and search to                                                |                                |

|    |           |          |    | 2. DECT synchronization of the U-superfra                                                |                                |

|    |           |          |    | The distinction between the 2 modes is ma                                                | . 5.                           |

|    |           |          |    | the applied input signal: if logic '1' is pre-                                           |                                |

|    |           |          |    | TSP is assumed ; otherwise, a DECT sync                                                  |                                |

| 37 |           | POS      |    | ILT works in burst mode and consists of 4                                                |                                |

|    |           | 100      |    | POS = '0' means the 4 first GCI bursts are                                               |                                |

|    |           |          |    | POS = '1' means the 4 last GCI bursts are                                                |                                |

| 12 |           | VDD      | Р  | +3.3V power supply for digital functions                                                 |                                |

| 32 |           | VDD      | P  |                                                                                          |                                |

| 54 | Power     | VDD      | P  |                                                                                          |                                |

| 73 |           | VDD      | P. |                                                                                          |                                |

| 13 |           | VSS      | P  | OV Ground for digital functions                                                          |                                |

| 34 |           | VSS      | P. |                                                                                          |                                |

| 53 |           | VSS      | P  |                                                                                          |                                |

|    |           |          | P. |                                                                                          |                                |

| 71 |           | VSS      | Р  |                                                                                          |                                |

### **Transformer-Recommended Specifications**

### Table 1a (MTC-20278)

| Table 1a (MTC-20278)               |                    |                   | Table 1b (MTC-2      | 0279)          |

|------------------------------------|--------------------|-------------------|----------------------|----------------|

|                                    | Min/Typ            | Мах               | Min/Typ              | Max            |

| Turns Ratio                        | 2:1                |                   |                      | 1.6:1          |

| Prelimary Inductance (mH)          | 14.25              | 15.75             | 5.25                 | 6.75           |

| Leakage Inducatance (uH)           |                    | 60                |                      | 60             |

| Interwinding Capacitance (pF max.) | 90                 |                   |                      | 90             |

| PRI DCR (Ohms)                     | 6                  | 7                 | 6                    | 7              |

| SEC DCR (Ohms)                     | 2.8                | 3.3               | 3.5                  | 4.2            |

|                                    | (Alcatel Part Code | e TMP 00087 0003) | (Alcatel Part Code T | MP 00087 0002) |

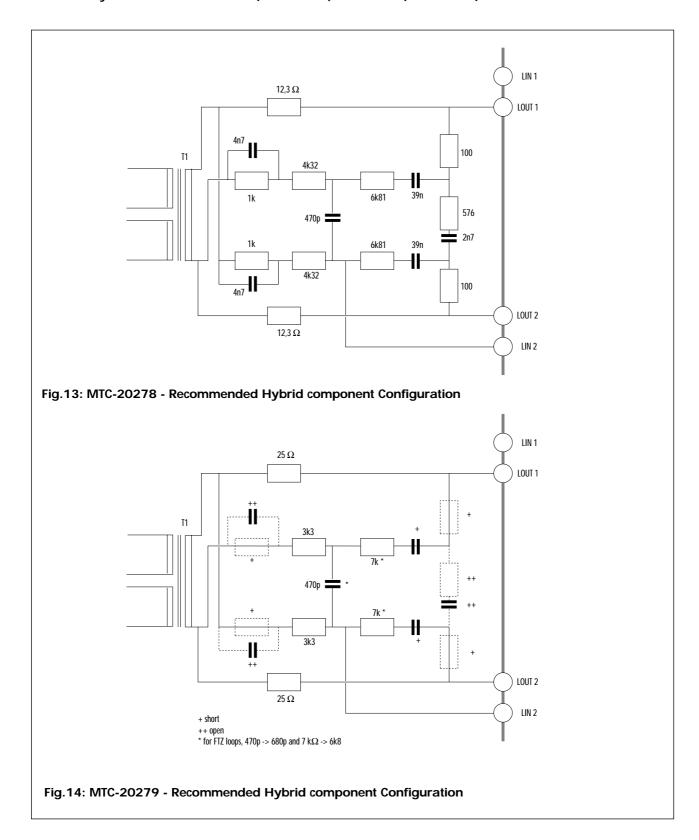

### **Recommended Component Values**

Table 2

| Component | Function                    | Value          | Comment |

|-----------|-----------------------------|----------------|---------|

| Rh        | U feed bridge and hybrid    |                | ±1%     |

|           | resistors                   | see Fig. 13/14 |         |

| R1        | reset delay                 | 100kΩ          | ±5%     |

| C1        | reset delay                 | 100 nF         | ±5%     |

| C2        | Digital supply decoupling   | 100 nF         |         |

| C3        | Analog reference decoupling | 100 nF         |         |

| C4        | Analog supply decoupling    | 100 nF         |         |

| CL        | Line-feed coupling          | 2.2 µF         | 250V    |

| Ch        | Hybrid capacitance          | see Fig. 13/14 | 2%      |

| Z         | overvoltage protection      |                |         |

### Common Hybrid Shematics for 4B3T (MTC-20279) and 2B1Q (MTC-20278)

### MTC-20278

# Logical Characteristics of the U Interface

The quaternary symbol stream crossing the U-interface complies with the following logical characteristics:

### Frame Structure

The information flow across the subscriber line uses frames as shown in Figure 15. The length of such a frame corresponds to 120 quaternary symbols being transmitted within 1.5ms. The frame structure is detailed as follows.

#### B+B+D - Data

108 quaternary symbols represent 216 bits of scrambled and encoded B+B+D data. The 108 quaternary symbols are transmitted in succession. These blocks are assembled as follows:

| Data of:        | B1 + | B2 + | D + | B1 + | B2 + | D |

|-----------------|------|------|-----|------|------|---|

| Number of bits: | 8    | 8    | 2   | 8    | 8    | 2 |

### Synchronizing Word

9 quaternary symbols in each direction represent a non-scrambled synchronizing word. They are used to generate frame clocks. If they are out of position for 60... 200 consecutive frames, the line resynchronization procedure is started. The quaternary values and the frame positions are as follows: From LT to NT or analog loop in LT (loop 1) and from NT to LT.

| Quad<br>Position | 1-9  |      |      | 10-117 |       |      | 1  | 118-120 |    |

|------------------|------|------|------|--------|-------|------|----|---------|----|

| Bit<br>Position  | 1-18 |      |      | 19-234 | 9-234 |      |    | 235-240 |    |

| Frame 1          | ISW  | 2B+D | 2B+D |        | 2B+D  | 2B+D | M1 |         | M6 |

| Frame 2          | SW   | 2B+D | 2B+D |        | 2B+D  | 2B+D | M1 |         | M6 |

| Frame 3          | SW   | 2B+D | 2B+D |        | 2B+D  | 2B+D | M1 |         | M6 |

| Frame 4          | SW   | 2B+D | 2B+D |        | 2B+D  | 2B+D | M1 |         | M6 |

| Frame 5          | SW   | 2B+D | 2B+D |        | 2B+D  | 2B+D | M1 |         | M6 |

| Frame 6          | SW   | 2B+D | 2B+D |        | 2B+D  | 2B+D | M1 |         | M6 |

| Frame 7          | SW   | 2B+D | 2B+D |        | 2B+D  | 2B+D | M1 |         | M6 |

| Frame 8          | SW   | 2B+D | 2B+D |        | 2B+D  | 2B+D | M1 |         | M6 |

Fig.15: Frame and Superframe Structure

### Maintenance and Service Channel

3 quaternary symbols per frame are transmitted to convey maintenance and embedded operations channel information. This information is contained in a superframe consisting of 8 frames (duration: 12ms). The start of a superframe in the up and downstream directions is marked by a single inversion of the synchronisation word. The quaternary symbol sequences represent data that can be transmitted at a rate of 4 kbit/s. They are transmitted immediately before the sync word.

The M symbol is used for various purposes:

Maintenance Channel (control test loops and report frame errors)

Service Channel (carry transparent user data in both directions)

In detail the following convention applies (LT to NT):

| ACT:  | Activation bit (set to ONE during activation)           |

|-------|---------------------------------------------------------|

| AIB:  | Alarm indication bit (set = 0 to indicate interruption) |

| CRC:  | Cyclic Redundancy Check: covers 2B+D & M4:              |

|       | 1 = most significant bit;                               |

|       | 2 = next most significant bit, etc.                     |

| DEA:  | turn-off bit (set = 0 to announce turn-off)             |

| EOC:  | Embedded operations channel:                            |

|       | a = address bit;                                        |

|       | dm = data/message indicator;                            |

|       | i = information (data/message).                         |

| FEBE: | Far end block error bit (ZERO for errored multiframes)  |

| UOA:  | U-only-activation bit                                   |

| 1     |                                                         |

|         | M1     | M2     | M3     | M4  | M5     | M6     |

|---------|--------|--------|--------|-----|--------|--------|

| Frame 1 | EOC a1 | EOC a2 | EOC a3 | ACT | 1      | 1      |

| Frame 2 | EOC dm | EOC i1 | EOC i2 | DEA | 1      | FEBE   |

| Frame 3 | EOC i3 | EOC i4 | EOC i5 | 1   | CRC 1  | CRC 2  |

| Frame 4 | EOC i6 | EOC i7 | EOC i8 | 1   | CRC 3  | CRC 4  |

| Frame 5 | EOC a1 | EOC a2 | EOC a3 | 1   | CRC 5  | CRC 6  |

| Frame 6 | EOC dm | EOC i1 | EOC i2 | 1   | CRC 7  | CRC 8  |

| Frame 7 | EOC i3 | EOC i4 | EOC i5 | UOA | CRC 9  | CRC 10 |

| Frame 8 | EOC i6 | EOC i7 | EOC i8 | AIB | CRC 11 | CRC 12 |

#### Encoding

The encoding of a binary bit stream is made such that 2 binary bits correspond to 1 quaternary symbol. The first symbol of a frame will always contain the information of the first 2 bits of a B1 channel (although these bits are of course scrambled. In the receive direction, the first symbol of the quaternary frame is always converted (after descrambling) into the first two bits of a B1 channel. The exact convertion is done according to the following rules (ANSI specification):

| Quaternary Symbol | First bit (sign) | Second bit (Magnitude) |

|-------------------|------------------|------------------------|

| +3                | 1                | 0                      |

| +1                | 1                | 1                      |

| -1                | 0                | 1                      |

| -3                | 0                | 0                      |

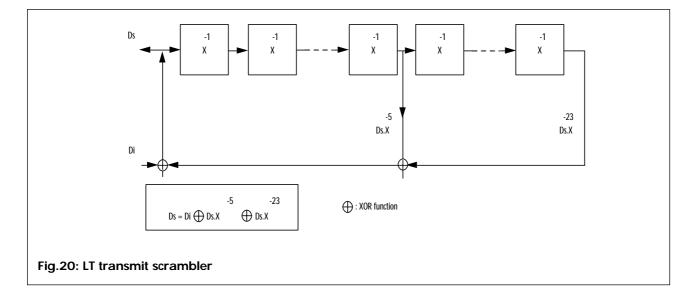

### Scrambling

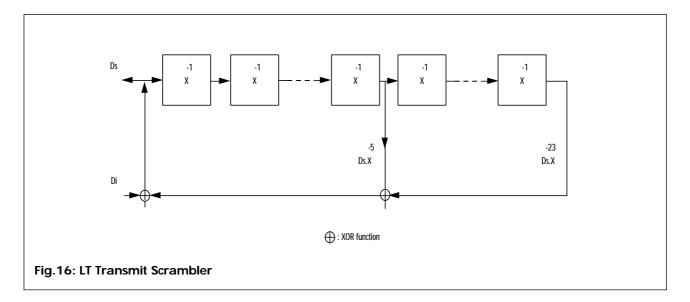

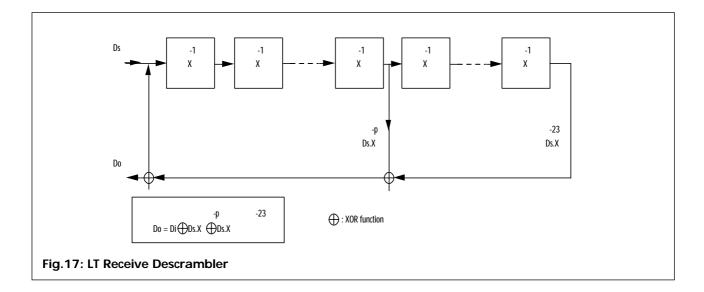

The received binary data stream is divided by generating polynomials.

The scrambler contains supervision circuitry which flags if a continuous series of ones or zeros have been detected at the output for a complete 1ms frame.

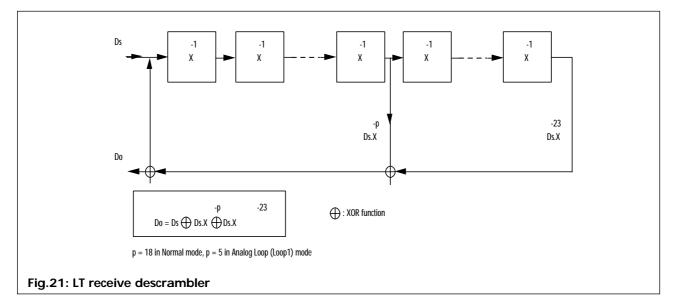

### Descrambling

The quaternary signals received on each side of the subscriber line are converted back into a binary bit stream and multiplied by the generating polynomials in order to recover the original data.

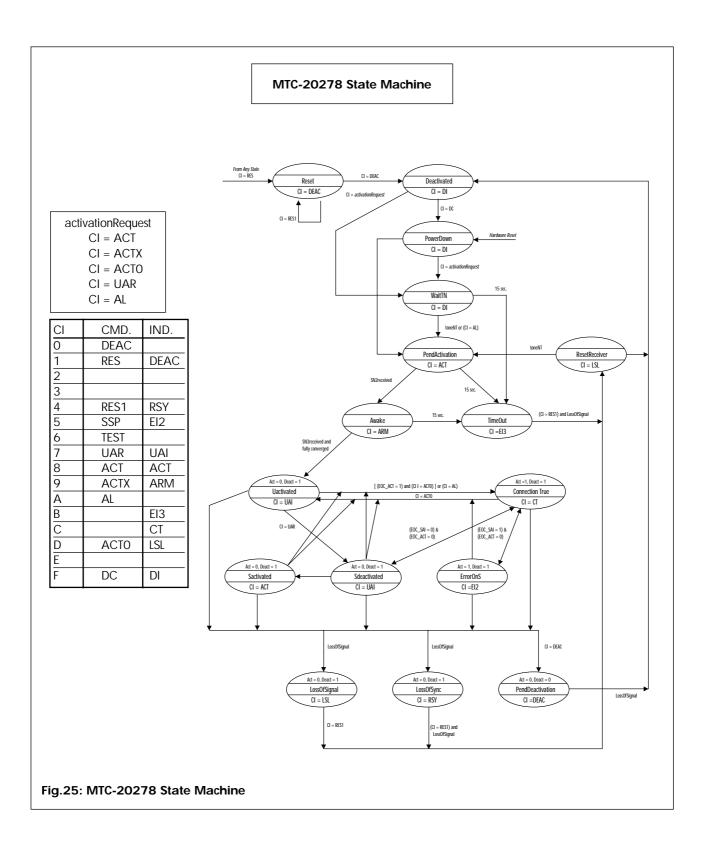

### **Activation and Deactivation**

In order to reduce the power consumption of circuits connected to the subscriber line, ILTQ can be switched to stand-by or powered down during the idle period. The components are powered up again during the line activation procedure. Two states are defined:

- Power-down state

Power consumption of the majority of the functions is reduced by stopping the clocks; maximum power reduction;

Power-up state All functions powered up; GCI interface is activated; exchange of C/I messages possible.

The activation procedure consists of three phases: awake (see the following sections), synchronize, and connect through.

The phases of activation are shown in the following table.

| Phase                | Indication<br>LT |

|----------------------|------------------|

| power-down           | DC               |

| awake<br>synchronize | ACT              |

| connect through      | СТ               |

Conditions for ACT and CT (see table 3 on page 22).

Maximum activation time (from command ACT to indication CT) without repeater for LT +NT:

< 300ms under normal conditions (starting with stored coefficients: See note on DECT synchronisation).

- 15s after reset of the coefficients With repeater, the activation may take twice as long.

Maximum activation time (from command ACT to indication CT) without repeater for LT:

- < 150ms under normal conditions (starting with stored coefficients)

- 10s after reset of the coefficients

The deactivation procedure consists of two phases: line deactivation and power-down (see table 3).

The deactivation can be initiated only by the command DEAC in the LT. The deactivation of the LT can be initiated only by INFO U0. The phases of deactivation are indicated in the following table. Deactivation time (from Command DEAC to Indication DC) is of the order of 4ms.

With repeater the deactivation may take twice as long.

#### Reset

The ILTQ can be reset via an external pin (NRESET = LOW) or via the command RES in the C/I channel. Normally the ILTQ is reset via the pin NRESET (hardware reset).

The ILTQ is initialized such that a "cold start" (resetting of the coefficients) is performed.

Resetting the component affects the status of the driver pins; after HW reset the drivers are switched off (low output level) but not changed after SW reset. (See also the Monitor channel).

#### Loops

For maintenance purposes a loop can be closed by applying the correct command via the M channel or the GCI C/I channel.

| Phase          |         | Indication |

|----------------|---------|------------|

|                |         | LT         |

| power-up       |         | CT         |

| (connected t   | hrough) |            |

| Line deactiv   | ation   | DEAC       |

| power-dowr     | า       | DC         |

| 1 <sup>.</sup> |         |            |

Conditions for DC and DEAC (see table 3 on page 22).

### **Activation signals**

The MTC-20278 can transmit any of the signals shown in Table 3.

### **Table 3: LT Activation Signals**

| Information | Description                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------|

| Station     | Description                                                                                                |

| TL          | A 10 kHz tone consisting of alternating four + 3 quats followed by four - 3 quats for a time period of two |

|             | frames.                                                                                                    |

| SLO         | No signal transmitted.                                                                                     |

| SL1         | Synchronization word present, no superframe synchronization word (ISW), and 2B+D+M = 1.                    |

| SL2         | Synchronization word present, superframe synchronization word (ISW) present, 2B+D = 0, and M =             |

|             | Normal.                                                                                                    |

| SL3         | Synchronization word present, superframe synchronization word (ISW) present. M channel bits active.        |

|             | Transmitted 2B+D data operational when M4 act bit = 1. When M4 act = 0, transmitted 2B+D data = 0.         |

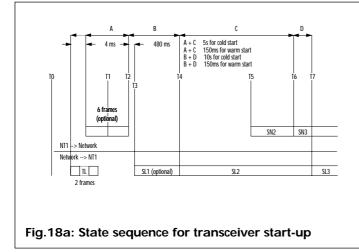

| TO RESET state.<br>11 Network and NT1 are awake.<br>12 NT1 discontinues transmission, indicating that the NT1 is ready to receive signal.<br>13 Network responds to termination of signal and begins transmitting signal towards to NT1.<br>14 Network begins transmitting SU2 towards the network, indicating that the network is ready to receive SU2.<br>15 NT1 begins transmitting SU2 towards the network, indicating that NT1 has acquired FW frame and detected SU2.<br>16 NT1 has acquired multiframe marker and is fully operational.<br>17 Network has acquired multiframe marker and is fully operational.<br>NOTE 1: If the II is repeated due to the persistence of FE 1, the repetition interval shall be > 25ms. At a repetition<br>interval larger than 480ms, the state machine will cause a TL tone if FE 1 remains.<br>NOTE 2: The maximum time between TL tone is defined to be Ams. This requirement is unnecessarily strict.<br>To allow transceivers which cannot meet this the L1 should wait for, and accept the TN tone, for a<br>period of 10ms from the beginning of issuing the TL tone. | Time: D | escription of event or state:                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------|

| <ul> <li>12 NT1 discontinues transmission, indicating that the NT1 is ready to receive signal.</li> <li>13 Network responds to termination of signal and begins transmitting signal towards to NT1.</li> <li>14 Network begins transmitting SU2 towards the network, indicating that the network is ready to receive SN2.</li> <li>15 NT1 begins transmitting SN2 towards the network, indicating that NT1 has acquired FW frame and detected SL2.</li> <li>16 NT1 has acquired multiframe marker and is fully operational.</li> <li>17 Network has acquired multiframe marker and is fully operational.</li> <li>NOTE 1: If the TL is repeated due to the persistence of FE 1, the repetition interval shall be &gt; 25ms. At a repetition interval larger than 480ms, the state machine will cause a TL tone if FE 1 remains.</li> <li>NOTE 2: The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict. To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a</li> </ul>                                                       | TO RESE | T state.                                                                                                         |

| T3 Network responds to termination of signal and begins transmitting signal towards to NT1.     T4 Network begins transmitting SL2 towards the network, indicating that the network is ready to receive SN2.     T5 NT1 begins transmitting SN2 towards the network, indicating that NT1 has acquired FW frame and detected SL2.     T6 NT1 has acquired multiframe marker and is fully operational.     T7 Network has acquired multiframe marker and is fully operational.     NOTE 1: If the TL is repeated due to the persistence of FE 1, the repetition interval shall be > 25ms. At a repetition     interval larger than 490ms, the state machine will cause a TL tone if FE 1 remains.     NOTE 2: The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict.     To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a                                                                                                                                                                                                   | T1 Netv | vork and NT1 are awake.                                                                                          |

| T4 Network begins transmitting SL2 towards the network, indicating that the network is ready to receive SN2.<br>T5 NT1 begins transmitting SN2 towards the network, indicating that NT1 has acquired FW frame and detected SL2.<br>T6 NT1 has acquired multiframe marker and is fully operational.<br>T7 Network has acquired multiframe marker and is fully operational.<br>NOTE 1: If the TL is repeated due to the persistence of FE 1, the repetition interval shall be > 25ms. At a repetition<br>interval larger than 480ms, the state machine will cause a TL tone if FE 1 remains.<br>NOTE 2: The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict.<br>To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a                                                                                                                                                                                                                                                                                                          | T2 NT1  | discontinues transmission, indicating that the NT1 is ready to receive signal.                                   |

| T5 NT1 begins transmitting SN2 towards the network, indicating that NT1 has acquired FW frame and detected SL2.         T6 NT1 has acquired multiframe marker and is fully operational.         T7 Network has acquired multiframe marker and is fully operational.         NOTE 1: If the TL is repeated due to the persistence of FE 1, the repetition interval shall be > 25ms. At a repetition interval arger than 480ms, the state markine will cause a TL tone if FE 1 remains.         NOTE 2: The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict. To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a                                                                                                                                                                                                                                                                                                                                                                                                             | T3 Netv | vork responds to termination of signal and begins transmitting signal towards to NT1.                            |

| T6 NT1 has acquired multiframe marker and is fully operational.<br>T7 Network has acquired multiframe marker and is fully operational.<br>NOTE 1: If the TL is repeated due to the persistence of FE 1, the repetition interval shall be > 25ms. At a repetition<br>interval larger than 480ms, the state machine will cause a TL tone if FE 1 remains.<br>NOTE 2: The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict.<br>To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | T4 Netv | vork begins transmitting SL2 towards the network, indicating that the network is ready to receive SN2.           |

| <ul> <li>177 Network has acquired multiframe marker and is fully operational.</li> <li>NOTE 1: If the TL is repeated due to the persistence of FE 1, the repetition interval shall be &gt; 25ms. At a repetition interval larger than 480ms, the state machine will cause a TL tone if FE 1 remains.</li> <li>NOTE 2: The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict. To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | T5 NT1  | begins transmitting SN2 towards the network, indicating that NT1 has acquired FW frame and detected SL2.         |

| NOTE 1: If the TL is repeated due to the persistence of FE 1, the repetition interval shall be > 25ms. At a repetition<br>interval larger than 480ms, the state machine will cause a TL tone if FE 1 remains.<br>NOTE 2: The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict.<br>To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | T6 NT1  | has acquired multiframe marker and is fully operational.                                                         |

| interval larger than 480ms, the state machine will cause a TL tone if FE 1 remains.<br>NOTE 2: The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict.<br>To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T7 Netv | vork has acquired multiframe marker and is fully operational.                                                    |

| NOTE 2: The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict.<br>To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NOTE 1  | : If the TL is repeated due to the persistence of FE 1, the repetition interval shall be > 25ms. At a repetition |

| To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | interval larger than 480ms, the state machine will cause a TL tone if FE 1 remains.                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NOTE 2  | The maximum time between TL tone is defined to be 4ms. This requirement is unnecessarily strict.                 |

| period of 10ms from the beginning of issuing the TL tone.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | To allow transceivers which cannot meet this the LT should wait for, and accept the TN tone, for a               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | period of 10ms from the beginning of issuing the TL tone.                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                                                                  |

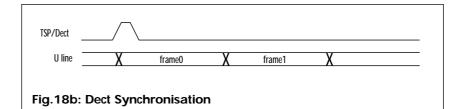

### **DECT Synchronisation**

The 4 U frames and superframes are aligned with the DECT synchronisation signal with a precision of 1 symbol, in the activation procedure. At the rising edge of the DECT signal, bit and frame counters are set to zero. DECT synchronisation needs soft or hard reset, precludes total power-down (that is replaced by partial powerdown), and warm-start may require 2.4 additional seconds. The DECT signal has a periodicity of 2.4 seconds and the width of the pulse can be between 13 and 375 microseconds.

### MTC-20279

# Logical Characteristics of the GCI Interface

The ternary symbol stream crossing the U-interface comply with the following logical characteristics:

### Frame Structure

The information flow across the subscriber line utilizes frames as shown in Figure 9. The length of such a frame corresponds to 120 ternary symbols being transmitted within 1ms. The frame structure is detailed as follows.

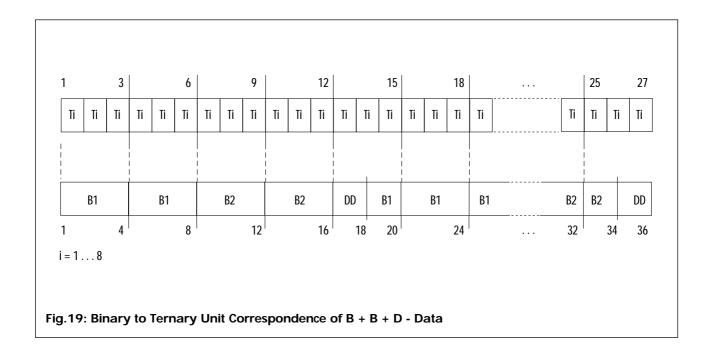

#### B+B+D - Data

Г

108 ternary symbols (T1 . . . T8) represent 144 bits of scrambled and encoded B+B+D data. The 108 ternary symbols are divided into four equally structured groups in which each group of 27 ternary symbols corresponds to a block of 36 binary bits (consult also Figure 9 and Figure 10). These blocks are assembled as follows:

| Data of:        |   |   |   |   |   |   |

|-----------------|---|---|---|---|---|---|

| Number of bits: | 8 | 8 | 2 | 8 | 8 | 2 |

### Synchronizing Word

11 ternary symbols in each direction (SW1, SW2) represent a non-scrambled synchronizing word. They are used to generate frame clocks. If they are out of position for 60 . . . 200 consecutive frames, the line resynchronization procedure is started. The ternary values and the frame positions are as follows:

| From LT to NT or a | analog le | oop in L | T (loop | 1) (LT Tr | ansmit) | :   |     |     |     |     |     |  |

|--------------------|-----------|----------|---------|-----------|---------|-----|-----|-----|-----|-----|-----|--|

| Frame position:    | 110       | 111      | 112     | 113       | 114     | 115 | 116 | 117 | 118 | 119 | 120 |  |

| SW1 Polarity:      | +         | +        | +       | -         | -       | -   | +   | -   | -   | +   | -   |  |

| From NT to LT (L1 | [ Receive) | :  |    |    |    |    |    |    |    |    |    |

|-------------------|------------|----|----|----|----|----|----|----|----|----|----|

| Frame position:   | 50         | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 |

| SW1 Polarity:     | -          | +  | -  | -  | +  | -  | -  | -  | +  | +  | +  |

| 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 |

|----|----|----|----|----|----|----|----|----|----|----|----|

| T1 |

| T1 |

| T1 | T1 | T1 | T2 |

| T2 |

| T2 | T2 | T2 | T2 | T2 | T2 | T3 | T3 | T3 | T3 | T3 | T3 |

| T3 |

| T3 | T4 | T4 | T4 |

| M1 | T4 |

| T4 |

### Table 4: Ternary Frame Structure

### NT -→ LT

| 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | _   |

|----|----|----|----|----|----|----|----|----|----|----|----|-----|

| T5 | 12  |

| T5 | 24  |

| M2 | T5 | T5 | T5 | T6 | 36  |

| T6 | 48  |

| T6 |    |    |    |    |    |    |    |    |    |    |    | 60  |

| T6 | T6 | T6 | T6 | T6 | T6 | T7 | T7 | T7 | T7 | T7 | T7 | 72  |

| T7 | 84  |

| T7 | T8 | T8 | T8 | 96  |

| T8 | 108 |

| T8 | 120 |

Legend:

T1 . . . T8: B + B + D - Data (ternary) M1, M2: Maintenance and Service Data (ternary) SW1, SW2: Synchronizing Word

### Maintenance and Service Channel

The ternary symbols (M1, M2) represent non-scrambled data that can be transmitted at a rate of 1 kBaud. The frame position for M1 is 85 and for M2 it is 25 (see Figure 9). The M symbol is used for various purposes:

Maintenance Channel (control test loops and report frame errors)

Service Channel (carry transparent user data in both directions); this is not supported by the MTC-20279.

In detail the following convention applies:

### Table 5: Service and Maintenance Data Convention

| Meaning          | Encoding                                   | Direction                                                                                     |

|------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------|

| Idle             | 0                                          | Both                                                                                          |

|                  |                                            |                                                                                               |

| Loop 2 in NT (1) | ++++                                       | from LT to NT                                                                                 |

| Loop 4 in RPTR   | +0+0+                                      | from LT to RPTR                                                                               |

| Frame Error (2)  | + (single symbol)                          | from NT to LT                                                                                 |

|                  | Idle<br>Loop 2 in NT (1)<br>Loop 4 in RPTR | Idle         O           Loop 2 in NT (1)         ++++           Loop 4 in RPTR         +O+O+ |

### NOTE 1:

A loop function is performed, if on eight consecutive frames the ternary encoding is recognized.

A loop function is finished if eight consecutive ternary zeros are recognized, or on line deactivation.

### Encoding

The encoding of a binary bit stream is made such that 4 binary bits correspond to 3 symbols of the ternary symbol stream (4B/3T encoding scheme). The encoding follows the rules of modified monitoring state 43 (MMS 43) which contains four alphabets. The left most bit of the binary value in column 1 of Figure 12 represents the first received bit of the binary bit stream. Corresponding to this, the left most indicated symbol of the ternary word is transmitted first.

### Table 6: MMS 43 - Code

#### NOTE 2:

One or more code violations detected by RDS (Running Digital Sum) checks or non-permissible series of 8 0\_polarity symbols within one frame lead to one frame error.

The alphabet used for encoding of a given binary block depends on the digital sum of previous three ternary symbols transmitted. Therefore, the alphabet to be used for encoding of the next binary block is indicated by a suffix number beside each ternary word.

After reset any alphabet can be used. The running digital sum (RDS) is computed in the RDS monitor (RDSM) from the received ternary symbols. When at the end of a ternary block the running digital sum equals zero or five a code violation has occured. The RDS monitor is reset to one at the beginning of each frame. RDS errors which are reported back from the NT to the LT are also accumulated in the RDS monitor.

One or more RDS errors or one or more series of five or more zeros within one frame lead to one frame error.

| Binary<br>Information | Те   | rnary Alphabets (left s | ymbol is transmitted | first) |

|-----------------------|------|-------------------------|----------------------|--------|

|                       | S1   | S2                      | S3                   | S4     |

| 0001                  | 0-+1 | 0-+2                    | 0-+3                 | 0-+4   |

| 0111                  | -0+1 | -0+2                    | -0+3                 | -0+4   |

| 0100                  | -+01 | -+02                    | -+03                 | -+04   |

| 0010                  | +-01 | +-02                    | +-03                 | +-04   |

| 1011                  | +0-1 | +0-2                    | +03                  | +0-4   |

| 1110                  | 0+-1 | 0+-2                    | 0+-3                 | 0+-4   |

| 1001                  | +-+2 | +-+3                    | +-+4                 | 1      |

| 0011                  | 00+2 | 00+3                    | 00+4                 | 02     |

| 1101                  | 0+02 | 0+03                    | 0+04                 | -0-2   |

| 1000                  | +002 | +003                    | +004                 | 02     |

| 0110                  | -++2 | -++3                    | +2                   | +3     |

| 1010                  | ++-2 | ++-3                    | +2                   | +3     |

| 1111                  | ++03 | 00-1                    | 00-2                 | 00-3   |

| 0000                  | +0+3 | 0-01                    | 0-02                 | 0-03   |

| 0101                  | 0++3 | -001                    | -002                 | -003   |

| 1100                  | +++4 | -+-1                    | -+-2                 | -+-3   |

Note that the received 3T-word 000 is transformed into a 4B-word of 0000. This pattern occurs only during deactivation.

24

### Scrambling

The received binary data stream is divided by generating polynomials.

The scrambler contains supervision circuitry which flags if a continuous series of ones or zeros have been detected at the output for a complete 1ms frame.

### Descrambling

The ternary signals received on each side of the subscriber line are converted back into a binary bit stream and multiplied by the generating polynomials in order to recover the original data.

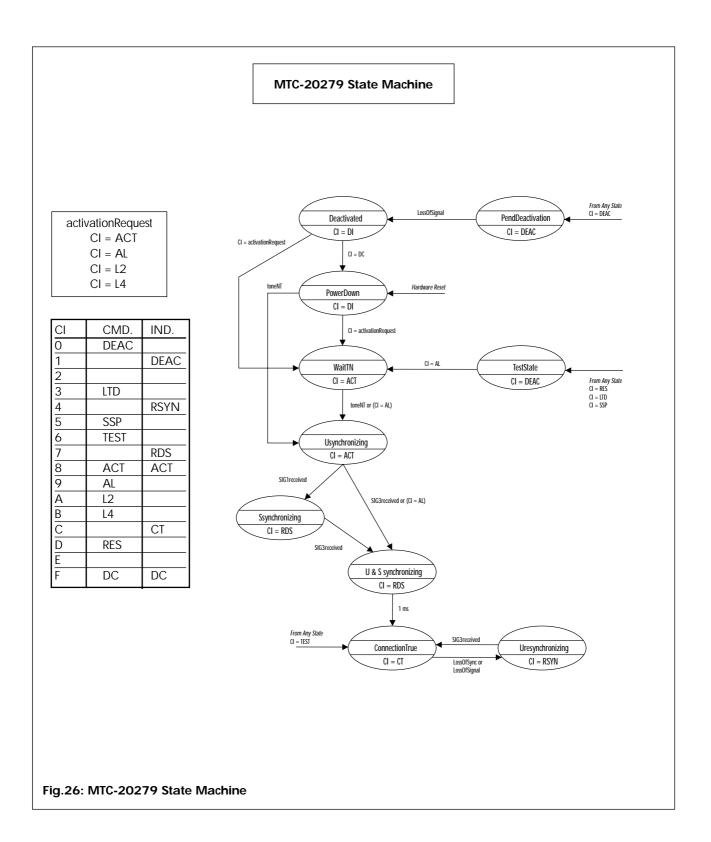

#### **Activation and Deactivation**

In order to reduce the power consumption of circuits connected to the subscriber line, the ILTT is powered down during idle period. The components are powered up again during the line activation procedure. Two states are defined:

- Power-down state

Power consumption of the majority of the functions is reduced by stopping the clocks; maximum power reduction;

- Power-up state All functions powered up.

The activation procedure consists of three phases: awake (see the following sections), synchronize, and connect through.

The phases of activation are indicated according to the following table.

| Phase           | Indication |

|-----------------|------------|

|                 | LT         |

| power-down      | DC         |

| awake           | ACT        |

| synchronize     | RDS        |

| connect through | CT         |

|                 |            |

Conditions for RDS, ACT and CT see 8.2.

Maximum activation time (from command ACT to indication CT) without RPTR:

- ≤ 210ms under normal conditions (starting with stored coefficients)

- 1.5s after reset of the coefficients

The deactivation procedure consists of two phases: line deactivation and power-down (see 8.2).

The deactivation can be initiated only by the command DEAC in the LT. The deactivation of the LT can be initiated only by INFO UO. The phases of deactivation are indicated in the following table.

| Phase               | Indication |

|---------------------|------------|

|                     | LT         |

| power-up            | CT         |

| (connected through) |            |

| Line deactivation   | DEAC       |

| power-down          | DC         |

|                     |            |

Conditions for DC and DEAC see 8.2.

Deactivation time (from Command DEAC to Indication DC) is in the order of 4ms.

With RPTR the deactivation may take twice as long.

#### Note:

When powered down, execution of commands via the M-Channel is not possible. To allow M-Channel commands to be used, issue the DGAC command on the CII bits.

#### Reset

The ILTT can be reset via an external pin (NRESET = LOW) or via the command RES in the C/I channel. Normally the ILTT is reset via the pin NRESET (hardware reset). Both reset requests cause via the activation/deactivation control (ACDECO) and the reset logic a reset for various functional blocks. The ILTT is initialized such that after reset a "cold start" (resetting of the coefficients) is forced. Resetting the component affects the status of the Relay drivers; after HW reset the Relay drivers are switched off (low output level), but after a SW reset the status of the Relay drivers is not modified. See also 8.4.

#### Loop2 (Loop in NT)

For maintenance purposes a loop can be closed by applying the correct command into the M channel or into the GCI C/I channel.

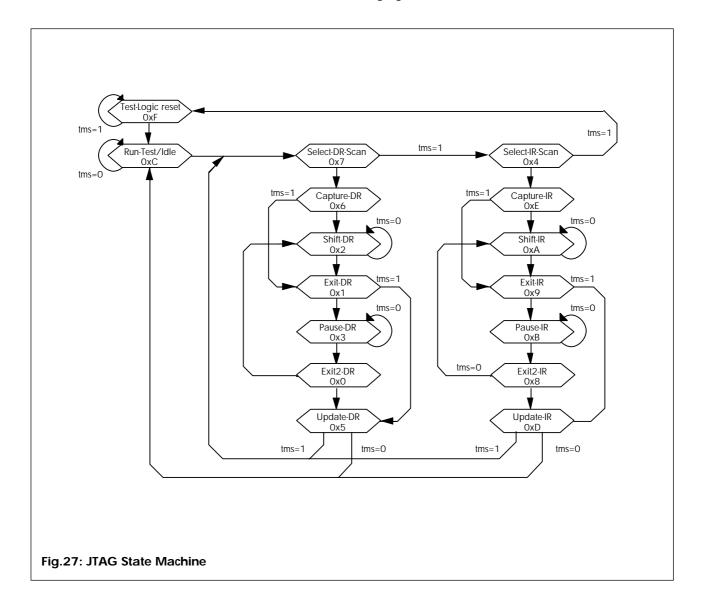

### Logical Characteristics of the GCI Interface

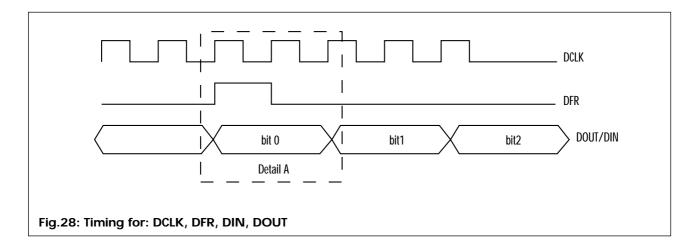

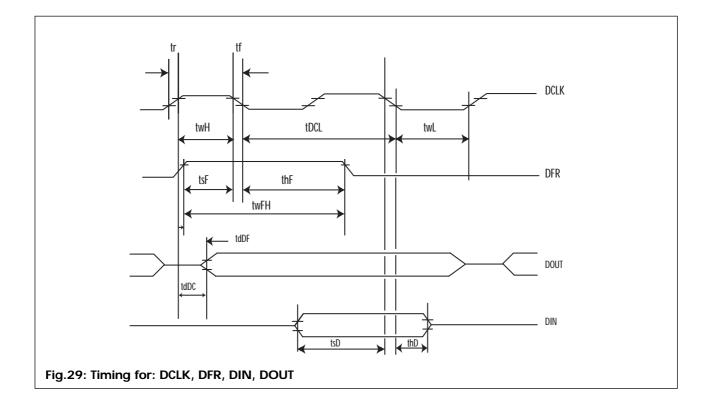

### Data Format and Timing at the GCI Interface (DIN, DOUT, DCLK, DFR)

#### **Continuous Modes**

- Nominal bitrate of data (DIN and DOUT): 2048 kbit/s

- Nominal frequency of clock (DCLK): 4096kHz

- Nominal frequency of frame clock (DFR): 8kHz

The following Figure shows the timing of data and clocks at the digital interface 2048 kbit/s (continuous modes). See the AC characteristics section for details. Transitions of the data occur after even-numbered rising edges of the clock DCLK. The data is valid on the odd-numbered rising edges of the clock DCLK.

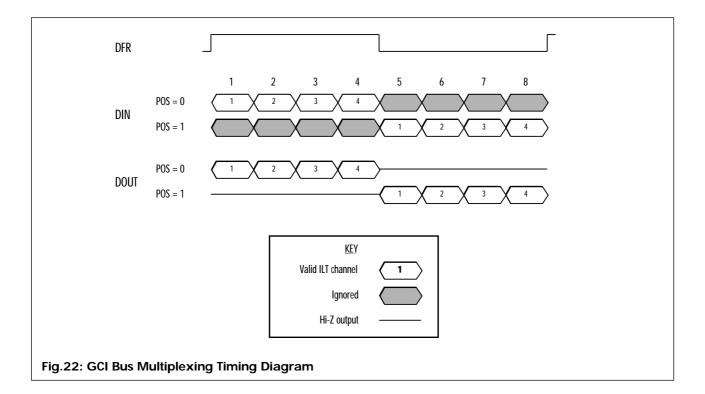

Even-numbered rising edges of the clock are defined as the second rising edge following the rising edge of the frame clock and every second rising edge thereafter. The frame is marked by the rising edge of the frame clock DFR and the data/frames are sampled on falling edge of DCLK. Note that the position of the falling edge of DFR is not important. One frame contains 8 bursts 4 bytes. The data streams at DIN and DOUT consist of 32 bytes per frame. See Figure 13. The input data DIN and the output data DOUT are synchronous and in phase.

Depending on the level of the pin POS. The quad-LT takes the 4 first or the 4 last time-slots.

| Port<br>Signal                         |                                                         |

|----------------------------------------|---------------------------------------------------------|

| DCLK<br>4096 kHz                       | mmmmmmm                                                 |

| DFR<br>8 kHz                           |                                                         |

| DIN<br>2048 kbit/s<br>(burstId-bitId)  | 7-28 7-29 7-30 7-31 0-0 0-1 0-2 0-3 0-4 0-5 0-6 0-7 0-8 |

| DOUT<br>2048 kbit/s<br>(burstId-bitId) | 7-28 7-29 7-30 7-31 0-0 0-1 0-2 0-3 0-4 0-5 0-6 0-7 0-8 |

| Rising<br>edge no.                     | 0 2 4 6 8 10 12 14 16                                   |

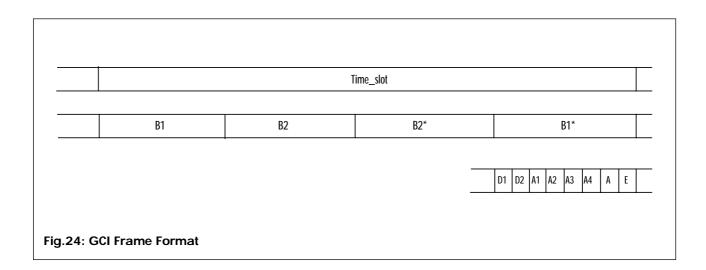

### Frame Format

Within each time-slot, 4 bytes are transmitted:

| 1st byte B1:  | B channel (64 kbit/s data), transparent                                     |

|---------------|-----------------------------------------------------------------------------|

| 2nd byte B2:  | B channel (64 kbit/s data), transparent                                     |

| 3rd byte B2*: | Monitor channel                                                             |

| 4th byte B1*: | 2 bit D channel (16 kbit/s data)                                            |

|               | 4 bit C/I channel A1, A2, A3, A4                                            |

|               | A, E bit used to control the transfer of information on the Monitor channel |

# Command and Indicate (C/I) Channel (A bits), MTC-20278

### Command (DIN)

| Deactivate             | DEACR | 0000 | Request to deactivate UO. The transmitter outputs INFO UO.                |

|------------------------|-------|------|---------------------------------------------------------------------------|

|                        |       |      | After detecting the disappearance of an incoming signal at UO the         |

|                        |       |      | indication DC is transmitted at module interface.                         |

| Reset                  | RESI  | 0001 | Reset of ILTQ to initial state.                                           |

| Reset receiver         | RESR  | 0100 | Reset of the ILTQ receiver only                                           |

| Send Single Pulses     | TXSSP | 0101 | The ILTQ transmits single pulses at 1.5ms time intervals with alternate   |

|                        |       |      | polarity +3/-3.                                                           |

| Test                   | TEST  | 0110 | The ILTQ will be connected through from module interface to line          |

|                        |       |      | interface (transparent) without wake-up procedure.                        |

| U activation request   | ARUO  | 0111 | Activation request of the UO interface only.                              |

| Activate               | ACT   | 1000 | Request to activate. ACT is indicated. The ILTQ is set in power-up state, |

|                        |       |      | executing the complete activation of layer 1: the wake-up procedure is    |

|                        |       |      | executed by transmission of INFO U2W.                                     |

|                        |       |      | After successful wake-up process, the synchronization procedure is        |

|                        |       |      | started by transmission of INFO U2 (in case of LT).                       |

| Activation request 2   | ACTX  | 1001 | Activation request without 15 sec limit.                                  |

| Analog Loop            | AL    | 1010 | ACT is indicated. The analog transmitter output is looped back to the     |

|                        |       |      | receiver input (channels B+B+D), which is disconnected from the UO        |

|                        |       |      | interface.                                                                |

| Activation request 3   | ACT0  | 1101 | Activation request with ACT bit = 0.                                      |

| DeactivateConfirmation | DCON  | 1111 | No signal is transmitted at UO and the ILTQ is powerd down.               |

|                        |       |      | The wake-up detect circuitry remains enabled: thus a detected wake-up     |

|                        |       |      | signal INFO U1W is able to power-up the UIC and to initiate the           |

|                        |       |      | activation procedure, as in case of control ACT applied.                  |

Note that RES or RES1 do not change the driver pins status while a hard reset configures RDi3 as input. Note that at power-up, a DC command has to be given prior to any other command or DIN has to be one.

### Indication (DOUT)

| DEACA | 0001                                                             | The ILTQ is deactivating. Data transmission is impossible.                                                                                                                                                          |  |

|-------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RSYN  | 0100                                                             | Loss of synchronization.                                                                                                                                                                                            |  |

| EIST  | 0101                                                             | Error indication on the S/T interface.                                                                                                                                                                              |  |

| UAIN  | 0111                                                             | U activation indication.                                                                                                                                                                                            |  |

| ACT   | 1000                                                             | The signal INFO U1W has been recognized by the wake-up detect                                                                                                                                                       |  |

|       |                                                                  | circuitry. The ILTQ is powered up and the activation procedure will be                                                                                                                                              |  |

|       |                                                                  | executed.                                                                                                                                                                                                           |  |

| ARMB  | 1001                                                             | Activation request maintenance bits                                                                                                                                                                                 |  |

| EIRTI | 1011                                                             | Error indication for timeout T1 (15s) or error on the UO interface.                                                                                                                                                 |  |

| СТ    | 1100                                                             | The transparent channels are connected through from module to line                                                                                                                                                  |  |

|       |                                                                  | interface (transparent). The activation of Layer 1 up to the terminals is                                                                                                                                           |  |

|       |                                                                  | completed.                                                                                                                                                                                                          |  |

| LSLU  | 1101                                                             | Loss of signal level on U.                                                                                                                                                                                          |  |