CMOS IC

LC8920

FAX Modem

## Preliminary

### **Overview**

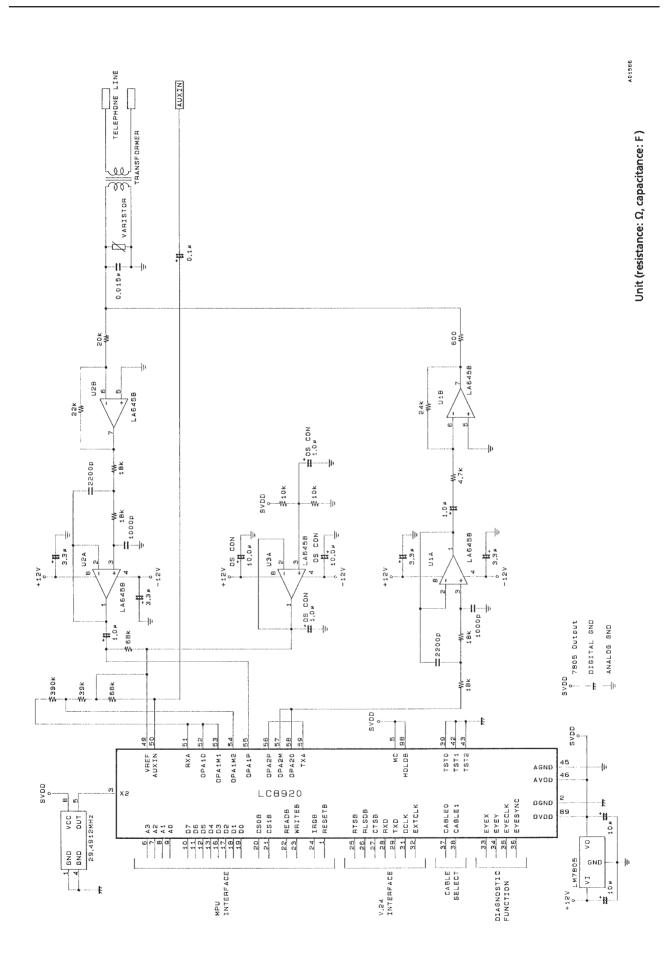

The LC8920 is designed for synchronous, half-duplex, 9,600 bps CMOS single chip modem applications using public telephone networks. This LSI has built-in modulation-demodulation components meeting modem requirements, along with transmitter-receiver filters and V.24 interfacing. In addition, construction of Group 3 and Group 2 facsimile systems has been simplified.

The LC8920 conforms to V.29, V.27ter, T.30, T.4 and T.3 recommendations for telecommunications as set forth by CCITT (CCITT: International Telephone and Telegraph Consultative Committee). Transfer speeds supported by this LSI include 300, 2400, 4800, 7200 and 9600 bps rates. Advanced signal processing functions permit data transmission and reception even under poor line conditions.

## **Features**

• CCITT recommendations

V.29 (9600 bps, 7200 bps and 4800 bps) V.27ter (4800 bps and 2400 bps) V.21ch2 (300 bps) T.30, T.4 and T.3

- Supports high-speed (V.29 and V.27ter) and low-speed (V.21ch2) simultaneous reception

- Half-duplex operation

- Capable of supporting Group 3 and Group 2 facsimiles

- Programmable signal tone generation and detection

- Programmable DTMF (Dual Tone Multi Frequency) generation and detection

- Built-in adaptive automatic equalizer

- Built-in amplitude equalizers (rink amplitude equalizer and cable amplitude equalizer)

- Built-in transmitter-receiver filter (digital filter)

- Supports transmit level adjustment (-0.5 dBm step intervals)

- Dynamic receiving range (-7 dBm to -43 dBm)

- Supports adjustment of transmit-receive sensitivity

- DTE (Data Terminal Equipment) interface Serial interface (conforming to CCITT recommended V.24) and parallel interface

- HDLC (High-level Data Link Control) framing function (during applications of CCITT recommended V.21 ch2)

- Programmable call progress tone detection

- Built-in eye-pattern generator

- Built-in diagnostic function

- Low consumption electric power (typ 250mW) and adopted CMOS (Complementary Metal Oxide Semiconductor)

- +5 V single power supply

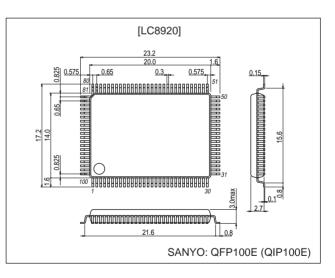

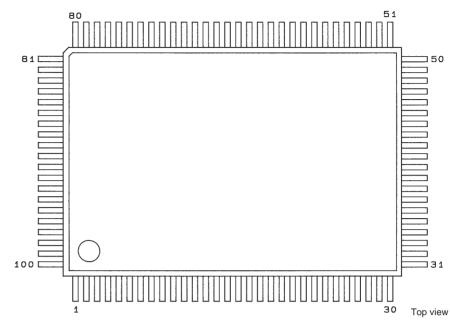

# Package Dimensions

unit : mm 3151-QFP100E

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

# **Specifications**

#### Absolute Maximum Ratings at GND = 0V

|                             | 0              |                                 |            |                              |      |

|-----------------------------|----------------|---------------------------------|------------|------------------------------|------|

| Parameter                   |                | Symbol                          | Conditions | Ratings                      | Unit |

| Maximum supply voltage      |                | V <sub>DD</sub> max             | Ta = 25°C  | -0.3 to +7.0                 | V    |

| I/O voltage                 |                | V <sub>I</sub> , V <sub>O</sub> | Ta = 25°C  | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Allowable power dissipation |                | Pd max                          | Ta≤70°C    | 400                          | mW   |

| Operating temperature range |                | Topr                            |            | -30 to +70                   | °C   |

| Storage temperature range   |                | Tstg                            |            | -55 to +125                  | °C   |

| Solder heat resistance      | Hand soldering |                                 | 3 seconds  | 350                          | °C   |

|                             | Reflow         | ]                               | 10 seconds | 235                          | °C   |

|                             |                |                                 |            |                              |      |

### Allowable Operating Range at $Ta=-30\ to\ +70^{\circ}C,\ GND=0V$

| Parameter           | Symbol          | Conditions | Ratings |     |                 | Unit |

|---------------------|-----------------|------------|---------|-----|-----------------|------|

| Farameter           | Symbol          | Conditions | min     | typ | max             | Onit |

| Supply voltage      | V <sub>DD</sub> |            | 4.5     | 5.0 | 5.5             | V    |

| Input voltage range | V <sub>IN</sub> |            | 0       |     | V <sub>DD</sub> | V    |

### Electrical Characteristics DC Characteristics Input Characteristic at Ta = -30 to +70°C, $V_{DD}$ = 4.5 to 5.5 V, GND = 0 V

| Decementar                     |                  | 0                                |                                                                        |                       | Ratings            |                       | 1.1=34 |  |

|--------------------------------|------------------|----------------------------------|------------------------------------------------------------------------|-----------------------|--------------------|-----------------------|--------|--|

| Parameter                      | Symbol           | Conditions                       | Adaptive Pin                                                           | min                   | typ                | max                   | Unit   |  |

| Input "H" level voltage        | V <sub>IH</sub>  | TTL correspondence               | RESETB, MC, A3 to A0,<br>D7 to D0, CS0B, CS1B,                         | 2.2                   |                    |                       | V      |  |

| Input "L" level voltage        | V <sub>IL</sub>  | TTL correspondence               | READB, WRITEB, RTSB,<br>TXD, CABLE1, CABLE0,<br>TST2 to TST0, PD15 to  |                       |                    | 0.8                   | V      |  |

| Input leakage voltage          | IL.              | $V_{IN} = GND, V_{DD}$           | PD0, HOLDB, EXTCLK                                                     | -1                    |                    | +1                    | μA     |  |

| Output "H" level voltage       | V <sub>OH</sub>  | I <sub>OH</sub> = -3mA: TTL      | WEB, D7 to D0, IRQB,<br>RLSDB, CTSB, RXD, DCLK,<br>EYEX, EYEY, EYECLK, | 2.4                   |                    |                       | V      |  |

| Output "L" level voltage       | V <sub>OL</sub>  | I <sub>OL</sub> = 3mA: TTL       | EYESYNC, PD15 to PD0,<br>PA13 to PA0, MENB,<br>CLKOUT, HOLDACB         |                       |                    | 0.4                   | V      |  |

| Output leakage voltage         | loz              | During high-<br>impedance output | D7 to D0, PD15 to PD0                                                  | -10                   | +10                |                       | μΑ     |  |

| Input frequency                | f <sub>IN</sub>  |                                  | X2                                                                     |                       | 29.4912            |                       | MHz    |  |

| V <sub>REF</sub> input voltage | V <sub>REF</sub> |                                  | V <sub>REF</sub>                                                       |                       | V <sub>DD</sub> /2 |                       | V      |  |

| V <sub>REF</sub> impedance     | R <sub>REF</sub> |                                  |                                                                        | 1                     |                    |                       | MΩ     |  |

| Input voltage range            | VIA              |                                  | RAX                                                                    | V <sub>DD</sub> X 0.2 |                    | V <sub>DD</sub> X 0.8 | V      |  |

| Output voltage range           | V <sub>OA</sub>  |                                  | ТХА                                                                    | V <sub>DD</sub> X 0.2 |                    | V <sub>DD</sub> X 0.8 | V      |  |

| Output impedance               | Ro               |                                  |                                                                        |                       |                    | 7.0                   | kΩ     |  |

| Consumable current             | IDD              | $V_{DD} = 5.5V$                  |                                                                        |                       |                    | 80                    | mA     |  |

|                                | -00              | $V_{DD} = 5.0V$                  |                                                                        |                       | 50                 |                       |        |  |

Note:  $GND = (AGND, DGND), V_{DD} = (AV_{DD}, DV_{DD})$

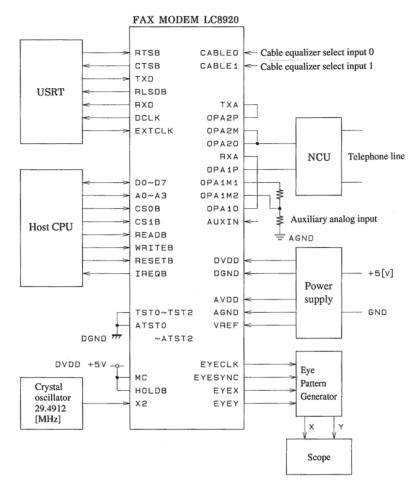

#### System Block Diagram

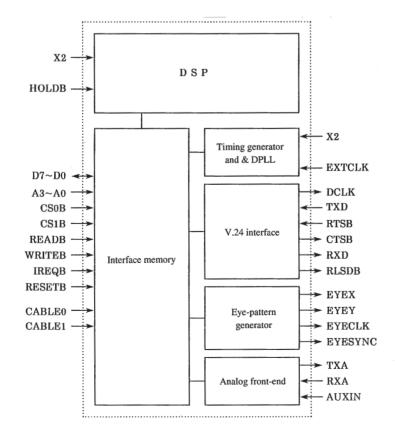

#### **Block Diagram**

A00692

### **Pin Assignment**

- : Input pin Ι

- 0 : Output pin

- В : Bidirectional pin

- Р : Power source pin

- NC : No Connection

A00696

| Number | Nama             |      | North  |                  |      |        |                  |      |

|--------|------------------|------|--------|------------------|------|--------|------------------|------|

| Number | Name             | type | Number | Name             | type | Number | Name             | type |

| 1      | RESETB           |      | 35     | EYECLK           | 0    | 69     | PD10             | В    |

| 2      | DGND             | Р    | 36     | EYESYNC          | 0    | 70     | PD9              | В    |

| 3      | X2               |      | 37     | CABLEO           |      | 71     | DGND             | Р    |

| 4      | WEB              | 0    | 38     | CABLE1           |      | 72     | PD8              | В    |

| 5      | MC               | I    | 39     | TST0             | I    | 73     | PD7              | В    |

| 6      | A3               |      | 40     | DGND             | Р    | 74     | PD6              | В    |

| 7      | A2               | I    | 41     | DV <sub>DD</sub> | Р    | 75     | PD5              | В    |

| 8      | A1               |      | 42     | TST1             |      | 76     | PD4              | В    |

| 9      | A0               | 1    | 43     | TST2             | .    | 77     | PD3              | В    |

| 10     | D7               | В    | 44     | ATST0            | 0    | 78     | PD2              | В    |

| 11     | D6               | В    | 45     | AGND             | Р    | 79     | PD1              | В    |

| 12     | D5               | В    | 46     | AV <sub>DD</sub> | Р    | 80     | PD0              | В    |

| 13     | D4               | В    | 47     | ATST2            | 0    | 81     | PA13             | 0    |

| 14     | DGND             | Р    | 48     | ATST1            | 0    | 82     | PA12             | 0    |

| 15     | DV <sub>DD</sub> | Р    | 49     | V <sub>REF</sub> | I    | 83     | PA11             | 0    |

| 16     | D3               | В    | 50     | AUXIN            |      | 84     | PA10             | 0    |

| 17     | D2               | В    | 51     | RXA              |      | 85     | PA9              | 0    |

| 18     | D1               | В    | 52     | OPA10            | 0    | 86     | PA8              | 0    |

| 19     | D0               | В    | 53     | OPA1M1           | I    | 87     | PA7              | 0    |

| 20     | CSOB             |      | 54     | OPA1M2           | 1    | 88     | PA6              | 0    |

| 21     | CS1B             | I    | 55     | OPA1P            | 1    | 89     | DV <sub>DD</sub> | Р    |

| 22     | READB            |      | 56     | OPA2P            | I    | 90     | DGND             | Р    |

| 23     | WRITEB           |      | 57     | OPA2M            | 1    | 91     | PA5              | 0    |

| 24     | IRQB             | 0    | 58     | OPA20            | 0    | 92     | PA4              | 0    |

| 25     | RTSB             | 1    | 59     | TXA              | 0    | 93     | PA3              | 0    |

| 26     | RLSDB            | 0    | 60     | AGND             | Р    | 94     | PA2              | 0    |

| 27     | CTSB             | 0    | 61     | AV <sub>DD</sub> | Р    | 95     | PA1              | 0    |

| 28     | RXD              | 0    | 62     | DGND             | Р    | 96     | PA0              | 0    |

| 29     | TXD              |      | 63     | DV <sub>DD</sub> | Р    | 97     | HOLDACB          | 0    |

| 30     | DGND             | Р    | 64     | PD15             | В    | 98     | HOLDB            | 1    |

| 31     | DCLK             | 0    | 65     | PD14             | В    | 99     | MENB             | 0    |

| 32     | EXTCLK           |      | 66     | PD13             | В    | 100    | CLKOUT           | 0    |

| 33     | EYEX             | 0    | 67     | PD12             | В    |        |                  |      |

| 34     | EYEY             | 0    | 68     | PD11             | В    |        |                  |      |

## **Pin Description**

## 1. Power Supply, Clock and Test Pins

| Name                    | Pin No.                               | I/O | Functions                                                                        |

|-------------------------|---------------------------------------|-----|----------------------------------------------------------------------------------|

| DV <sub>DD</sub>        | 15<br>41<br>63<br>89                  | Ρ   | These pins are for connecting to the digital power supply (+5 V).                |

| DGND                    | 2<br>14<br>30<br>40<br>62<br>71<br>90 | Ρ   | These pins are for connecting to the digital ground (0 V).                       |

| AV <sub>DD</sub>        | 46<br>61                              | Р   | These pins are for connecting to the analog power supply (+5 V).                 |

| AGND                    | 45<br>60                              | Р   | These pins are for connecting to the analog ground (0 V).                        |

| V <sub>REF</sub>        | 49                                    | Р   | This pin is for connecting to the power supply reference (AV <sub>DD</sub> /2V). |

| X2                      | 3                                     | I   | This pin is for connecting to the master clock (29.4912 MHz).                    |

| CLKOUT                  | 100                                   | 0   | This pin outputs 1/4 of the frequency (7.3728 MHz) of the master clock (X2).     |

| TST0<br>TST1<br>TST2    | 39<br>42<br>43                        | I   | These pins are for use during testing and are connected to the ground (0 V).     |

| ATST0<br>ATST1<br>ATST2 | 44<br>48<br>47                        | 0   | These pins are for use with analog testing.                                      |

## 2. Data Terminal Equipment (DTE) Interface

| Name                                         | Pin No.                                      | I/O | Functions                                                                    |

|----------------------------------------------|----------------------------------------------|-----|------------------------------------------------------------------------------|

| D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | 19<br>18<br>17<br>16<br>13<br>12<br>11<br>10 | I/O | These pins are for host CPU and data bus interfacing.                        |

| A0<br>A1<br>A2<br>A3                         | 9<br>8<br>7<br>6                             | I   | These pins are for host CPU and address bus interfacing.                     |

| CS0B<br>CS1B                                 | 20<br>21                                     | I   | These pins are for chip select signal interfacing.                           |

| READB                                        | 22                                           | Ι   | This pin is for interfacing the interface memory read signal.                |

| WRITEB                                       | 23                                           | I   | This pin is for interfacing the interface memory write signal.               |

| IREQB                                        | 24                                           | 0   | This pin is for interfacing the interruption request signal to the host CPU. |

| RESETB                                       | 1                                            | I   | This pin is for interfacing the system reset signal.                         |

### 3. Diagnosis

| Name    | Pin No. | I/O | Functions                                                                                                                                  |  |  |

|---------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| EYECLK  | 35      | 0   | This pin is for diagnosis of the timing clock for generating eye pattern data. It can be used with an external shift register shift clock. |  |  |

| EYESYNC | 36      | 0   | This pin is for diagnosis of eye pattern synchronization signal.                                                                           |  |  |

| EYEX    | 33      | 0   | These pins are for eye pattern data (8 bit MSB first) serial output.                                                                       |  |  |

| EYEY 34 |         | Ŭ   | mese pins are for eye pattern data (o bit NOB linst) senai output.                                                                         |  |  |

#### 4. V.24 Interface

| Name   | Pin No. | I/O | Functions                                                                                                                                                                                                                   |

|--------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTSB   | 25      | I   | This pin is for interfacing the request to send (RTS) signal. When RTSB sets to an "L" level, transmission begins. When RTSB sets to an "H" level, transmission stops.                                                      |

| СТЅВ   | 27      | 0   | This pin is for interfacing the clear to send (CTS) signal. When CTSB sets to an "L" level, transmission can proceed. When CTSB sets to an "H" level, transmission will not be accepted.                                    |

| RLSDB  | 26      | 0   | This pin is for interfacing received line signal detect (RLSD). When RLSDB sets to an "L" level and transmission is set to proceed, this pin functions as a timing signal for transmitting transmission data to a terminal. |

| TXD    | 29      | I   | This pin is for input of transmit data (TXD).                                                                                                                                                                               |

| RXD    | 28      | 0   | This pin is for output of receive data (RXD).                                                                                                                                                                               |

| DCLK   | 31      | 0   | This pin is for clock output using transmit-receive data.                                                                                                                                                                   |

| EXTCLK | 32      | I   | This is the external input clock pin for use with Group 2.                                                                                                                                                                  |

### 5. Cable Equalizer

| Name   | Pin No. | I/O | Functions                                 |

|--------|---------|-----|-------------------------------------------|

| CABLE0 | 37      | I   | This pin is for cable equalizer sector 0. |

| CABLE1 | 38      | I   | This pin is for cable equalizer sector 1. |

## 6. Analog Signal

| Name   | Pin No. | I/O | Functions                                                                                        |

|--------|---------|-----|--------------------------------------------------------------------------------------------------|

| ТХА    | 59      | 0   | This pin is for transmitter analog output.                                                       |

| RXA    | 51      | I   | This pin is for receiver analog input.                                                           |

| AUXIN  | 50      | Ι   | This pin is for auxiliary analog input.                                                          |

| OPA2P  | 56      | Ι   |                                                                                                  |

| OPA2M  | 57      | I   | This pin is for transmission buffer input and output. (For further details, refer to the circuit |

| OPA20  | 58      | 0   | diagram.)                                                                                        |

| OPA1P  | 55      | I   |                                                                                                  |

| OPA1M1 | 53      | I   | This pin is for receiving buffer input and output. (For further details, refer to the circuit    |

| OPA1M2 | 54      | I   | diagram.)                                                                                        |

| OPA10  | 52      | 0   |                                                                                                  |

# 7. System Signal

| Name  | Pin No. | I/O | Functions                                                                                |

|-------|---------|-----|------------------------------------------------------------------------------------------|

| MC    | 5       | Ι   | This pin is for the program mode control signal and is connected to a +5 V power supply. |

| HOLDB | 98      | Ι   | This pin is for the system hold signal and is connected to a +5 V power supply.          |

Note: Other pins are all left open.

#### 2. AC Characteristics

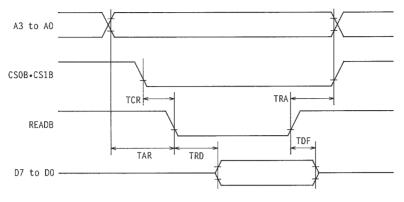

• DTE Interface Timing

#### (a) Read Cycle Timing

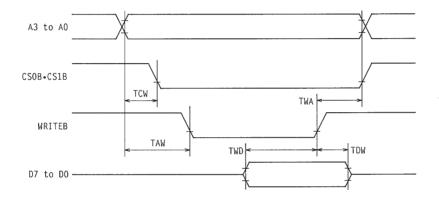

(b) Write Cycle Timing

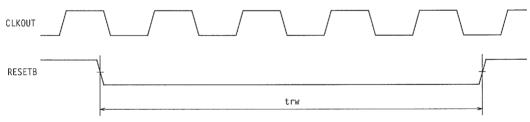

• Reset Timing

| 4 | 0 | 0 | 6 | 9 | 4 |

|---|---|---|---|---|---|

|   |   |   |   |   |   |

| Parameter                                                     | Symbol | Ratings |     | Unit |

|---------------------------------------------------------------|--------|---------|-----|------|

|                                                               |        | min     | max | Unit |

| Address stabilization time (in response to READB signal)      | TAR    | 40      |     | ns   |

| Chip-select stabilization time (in response to READB signal)  | TCR    | 40      |     | ns   |

| Data delay time                                               | TRD    | 30      |     | ns   |

| Data float delay time                                         | TDF    | 10      |     | ns   |

| Address hold time (in response to READB signal)               | TRA    | 10      |     | ns   |

| Address stabilization time (in response to WRITEB signal)     | TAW    | 40      |     | ns   |

| Chip-select stabilization time (in response to WRITEB signal) | TCW    | 40      |     | ns   |

| Data setting time                                             | TDW    | 30      |     | ns   |

| Data hold time                                                | TWD    | 10      |     | ns   |

| Address hold time (in response to WRITEB signal)              | TWA    | 10      |     | ns   |

| Reset pulse width                                             | Trw    | 500     |     | ns   |

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of November, 1999. Specifications and information herein are subject to change without notice.