#### TENTATIVE TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

Lead Free

#### **OVERVIEW**

The Rambus  $XDR^{TM}$  DRAM device is a general purpose high-performance memory device suitable for use in a broad range of applications including computer memory, graphics, video, and any other application where high bandwidth and low latency are required.

The 256Mb Rambus XDR DRAM device is a CMOS DRAM organized as 16M words by 16 bits. The use of Differential Rambus Signaling Level (DRSL) technology permits 4000/3200/2400 Mb/s transfer rates while using conventional system and board design technologies. XDR DRAM devices are capable of sustained data transfers of 8000/6400/4800 MB/s.

XDR DRAM device architecture allows the highest sustained bandwidth for multiple, interleaved randomly addressed memory transactions. The highly efficient protocol yields over 95% utilization while allowing fine access granularity. The device's 8 banks support up to four interleaved transactions.

### **FEATURES**

- Highest pin bandwidth available

- 4000/3200/2400 Mb/s Octal Data Rate (ODR) Signaling

- Bi-directional differential RSL (DRSL)

Flexible read/write bandwidth allocation

Minimum pin count

- Programmable on-chip termination

- Adaptive impedance matching

- Reduced system cost and routing complexity

- · Highest sustained bandwidth per DRAM device

- 8000/6400/4800 MB/s sustained data rate

- 8 banks: bank-interleaved transactions at full bandwidth

- Dynamic request scheduling

- Early-Read-after-Write support for maximum efficiency

- Zero overhead refresh

- Low latency

- 2.0/2.5/3.33 ns request packets

- Point-to-point data interconnect for fastest possible flight time

- Support for low-latency, fast-cycle cores

- Low power

- 1.8V V<sub>DD</sub>

- Programmable small-swing I/O signaling (DRSL)

- Low power PLL/DLL design

- Power Down Self Refresh support

- Per pin I/O Power Down for narrow-width operation

- · Programmable I/O width

- $-\times4/\times8/\times16$  programmable device I/O width

Note: XDR is a trademark or a registered trademark in Japan and/or other countries.

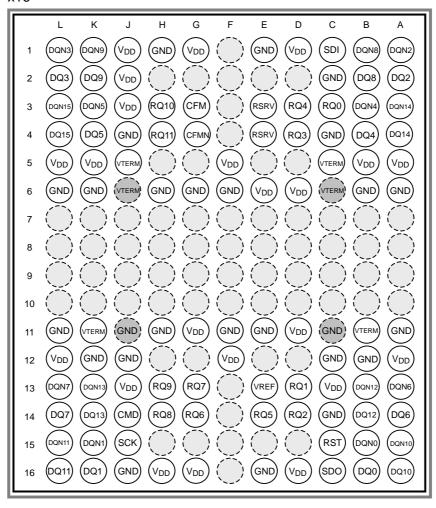

# **PIN ASSIGNMENT (TOP VIEW)**

XDR DRAM CSP x16

Note: • ( ): Optional ball / Depopulated

( ): DepopulatedRSRV: Reserved pin

DQ8...DQ15, DQN8...DQN15 are RSRV's for ×8

DQ4...DQ15, DQN4...DQN15 are RSRV's for ×4

#### **Key Timing Parameters/Part Numbers**

| Organization <sup>a</sup> | Bandwidth (1/t <sub>BIT</sub> ) <sup>b</sup> | Latency (t <sub>RAC</sub> ) <sup>c</sup> | Bin <sup>d</sup> | Part Number     |

|---------------------------|----------------------------------------------|------------------------------------------|------------------|-----------------|

| 8 × 2K × 1K × 16          | 2400                                         | 36                                       | А                | TC59YM816BKG24A |

| 8 × 2K × 1K × 16          | 3200                                         | 27                                       | А                | TC59YM816BKG32A |

| 8 × 2K × 1K × 16          | 3200                                         | 35                                       | В                | TC59YM816BKG32B |

| 8 × 2K × 1K × 16          | 3200                                         | 35                                       | С                | TC59YM816BKG32C |

| 8 × 2K × 1K × 16          | 4000                                         | 28                                       | В                | TC59YM816BKG40B |

| 8 × 2K × 1K × 16          | 4000                                         | 28                                       | С                | TC59YM816BKG40C |

- a.  $Bank \times Row \times Column \times Width$

- b. Data rate measured in Mbit/s per DQ differential pair. See "Timing Conditions" on page 60 and "Timing Characteristics" on page 62. Note that t<sub>BIT</sub> = t<sub>CYCLE</sub> / 8.

- c. Read access time  $t_{RAC}$  (= $t_{RCD-R} + t_{CAC}$ ) measured in ns. See "Timing Parameters" on page 63.

- d. Timing parameter bin. See "Timing Parameters" on page 63. This is a measure of the number of interleaved read transactions needed for maximum efficiency (the value Ceiling (t<sub>RC-R</sub>/t<sub>RR-D</sub>).

For bin A,  $t_{RC-A} / t_{RR-D} = 4$ , and for bin B,  $t_{RC-R} / t_{RR-D} = 5$

### **General Description**

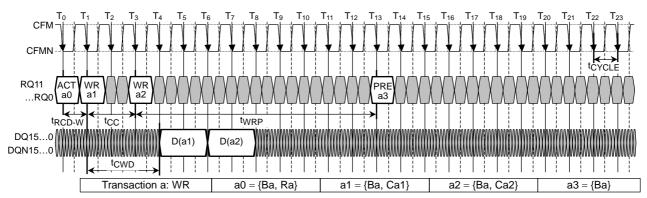

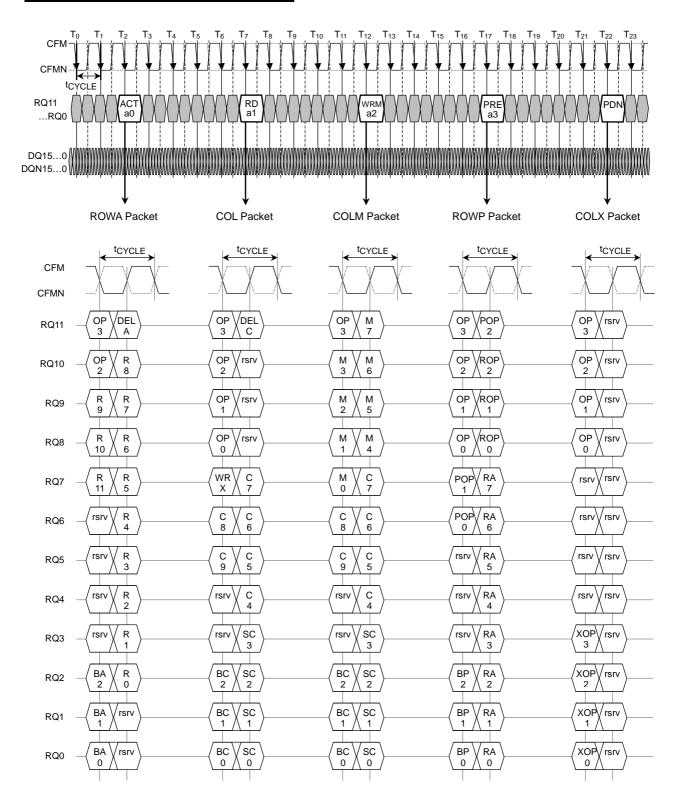

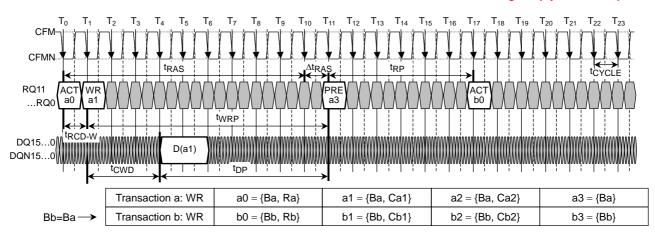

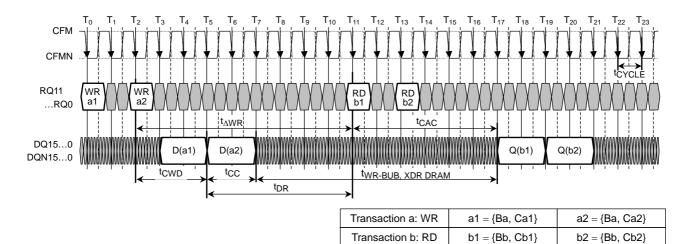

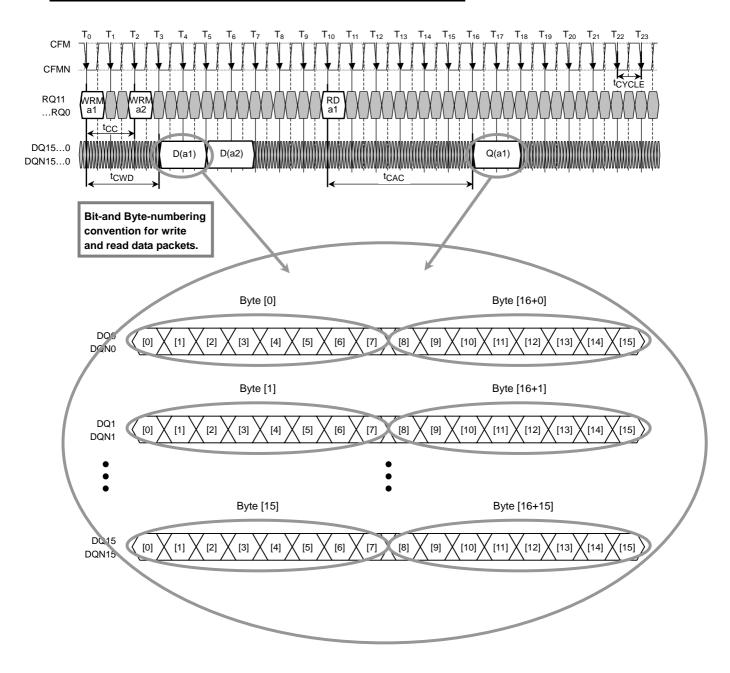

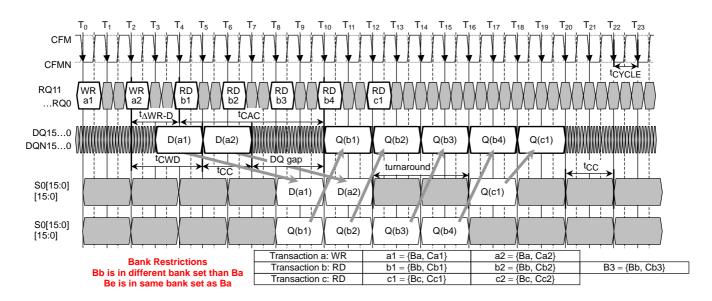

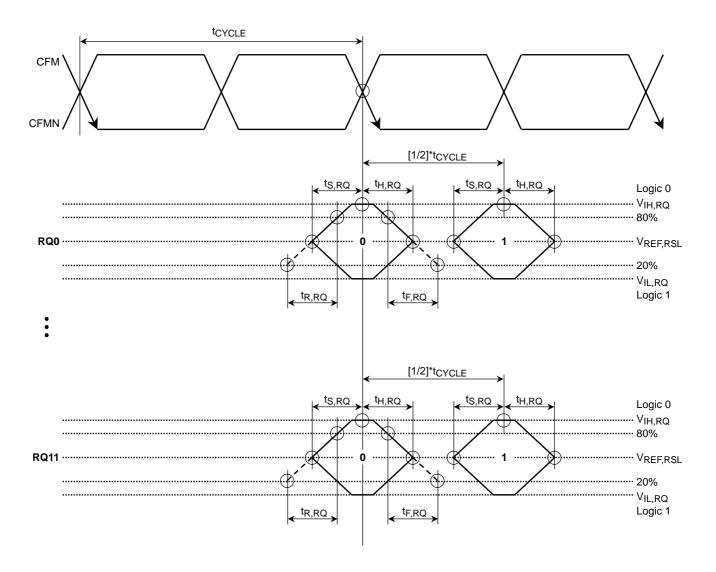

The timing diagrams in Figure 1 illustrate XDR DRAM device write and read transactions. There are three sets of pins used for normal memory access transactions: CFM/CFMN clock pins, RQ11...RQ0 request pins, and DQ15...DQ0/DQN15...DQN0 data pins. The "N" appended to a signal name denotes the complementary signal of a differential pair.

A transaction is a collection of packets needed to complete a memory access. A packet is a set of bit windows on the signals of a bus. There are two buses that carry packets: the RQ bus and DQ bus. Each packet on the RQ bus uses a set of 2 bit-windows on each signal, while the DQ bus uses a set of 16 bit-windows on each signal.

In the write transaction shown in Figure 1, a request packet (on the RQ bus) at clock edge  $T_0$  contains an activate (ACT) command. This causes row Ra of bank Ba in the memory component to be loaded into the sense amp array for the bank. A second request packet at clock edge  $T_1$  contains a write (WR) command. This causes the data packet D (a1) at edge  $T_4$  to be written to column Ca1 of the sense amp array for bank Ba. A third request packet at clock edge  $T_3$  contains another write (WR) command. This causes the data packet D (a2) at edge  $T_6$  to be also be written to column Ca2. A final request packet at clock edge  $T_{13}$  contains a precharge (PRE) command.

The spacing between the request packets are constrained by the following timing parameters in the diagram:  $t_{RCD-W}$ ,  $t_{CC}$ , and  $t_{WRP}$ . In addition, the spacing between the request packets and data packets are constrained by the  $t_{CWRD}$  parameter. The spacing of the CFM/CFMN clock edges is constrained by  $t_{CYCLE}$ .

### Figure 1. XDR DRAM Device Write and Read Transactions

Write Transaction

**Read Transaction**

The read transaction shows a request packet at clock edge  $T_0$  containing an ACT command. This causes row Ra of bank Ba of the memory component to load into the sense amp array for the bank. A second request packet at clock edge  $T_5$  contains a read (RD) command. This causes the data packet Q (a1) at edge  $T_{11}$  to be read from column Ca1 of the sense amp array for bank Ba. A third request packet at clock edge  $T_7$  contains another RD command. This causes the data packet Q (a2) at edge  $T_{13}$  to also be read from column Ca2. A final request packet at clock edge  $T_{10}$  contains a PRE command.

The spacing between the request packets are constrained by the following timing parameters in the diagram: tRCD-R, tCC, and tRDP. In addition, the spacing between the request and data packets is constrained by the tCAC parameter.

# **Table of Contents**

| Overview                                 | 1                                     |

|------------------------------------------|---------------------------------------|

| Features                                 | 1                                     |

| XDR DRAM CSP ×16 Pin Out                 | 1                                     |

| Key Timing Parameters / Part Numbers     | 1                                     |

| Pin Assignment (top view)                | 2                                     |

| Key Timing Parameters/Part Numbers       | 2                                     |

| Related Documentation                    |                                       |

| General Description                      |                                       |

| Table of Contents                        | 4                                     |

| Lift of Tables                           | ·<br>5                                |

| Lift of Figures                          | 6                                     |

| Pin Description                          | 7                                     |

| Block Diagram                            | 88                                    |

| Request Packets                          | 10                                    |

| Request Packet Formats                   | 10                                    |

| Request Field Encoding                   | 12                                    |

| Request Field Interactions               | 14                                    |

| Request Interactions Cases               | 15                                    |

| Dynamic Request Scheduling               | 20                                    |

| Memory Operations                        | 22                                    |

| Write Transactions                       |                                       |

| Read Transactions                        | 22<br>24                              |

| Interleaved Transactions                 |                                       |

| Read/Write Interaction                   |                                       |

| Propagation Delay                        |                                       |

| Register Operations                      | 33                                    |

| Serial Transactions                      | 33                                    |

| Serial Write Transaction                 | 33                                    |

| Serial Read Transaction                  |                                       |

| Register Summary                         |                                       |

| Maintenance Operations                   | 42                                    |

| Refresh Transactions                     | 42                                    |

| Interleaved Refresh Transactions         | 42                                    |

| Calibration Transactions                 | 44                                    |

| Power State Management                   | 45                                    |

| Initialization                           |                                       |

| XDR DRAM Initialization Overview         | 49                                    |

| XDR DRAM Pattern Load with WDSL Register | 50                                    |

| Special Feature Description              | 52                                    |

| Dynamic Width Control                    | 52                                    |

| Write Masking                            | 54                                    |

| Multiple Bank Sets and the ERAW Feature  | 56                                    |

| Simultaneous Precharge                   | 58                                    |

| Operating Conditions                     | 59                                    |

| Electrical Conditions                    |                                       |

| Timing Conditions                        |                                       |

| Operating Characteristics                | 61                                    |

| Electrical Characteristics               |                                       |

| Supply Current Profile                   |                                       |

| Timing Characteristics                   | 62                                    |

| Timing Parameters                        | 63                                    |

| Receive/Transmit Timing                  | 65                                    |

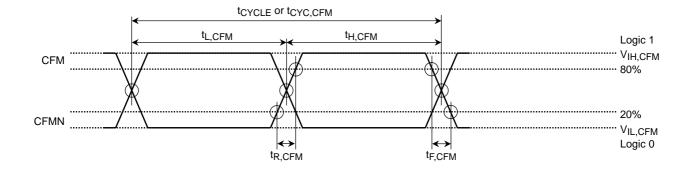

| Clocking                                 | 65<br>65                              |

| RSL RQ Receive Timing                    |                                       |

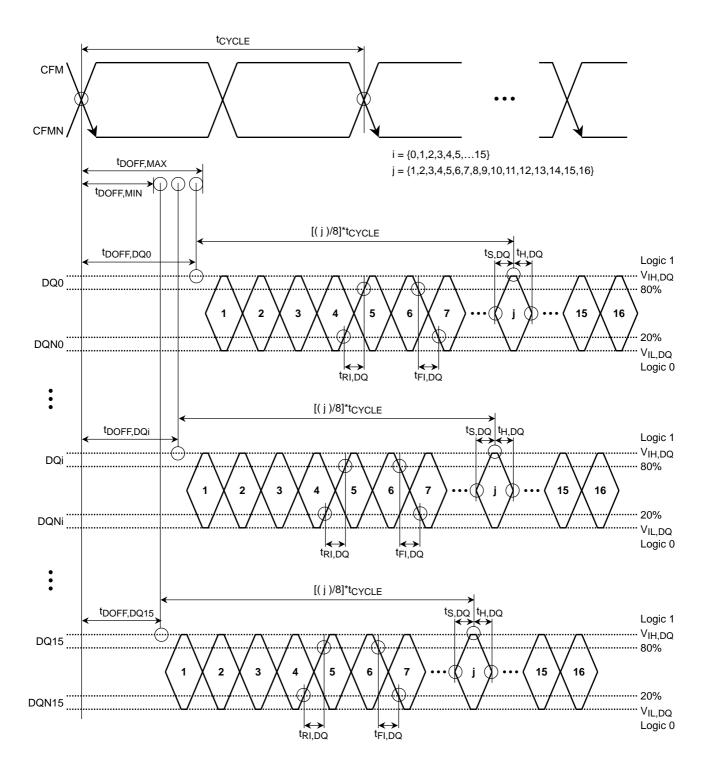

| DRSL DQ Receive Timing                   | 60<br>67                              |

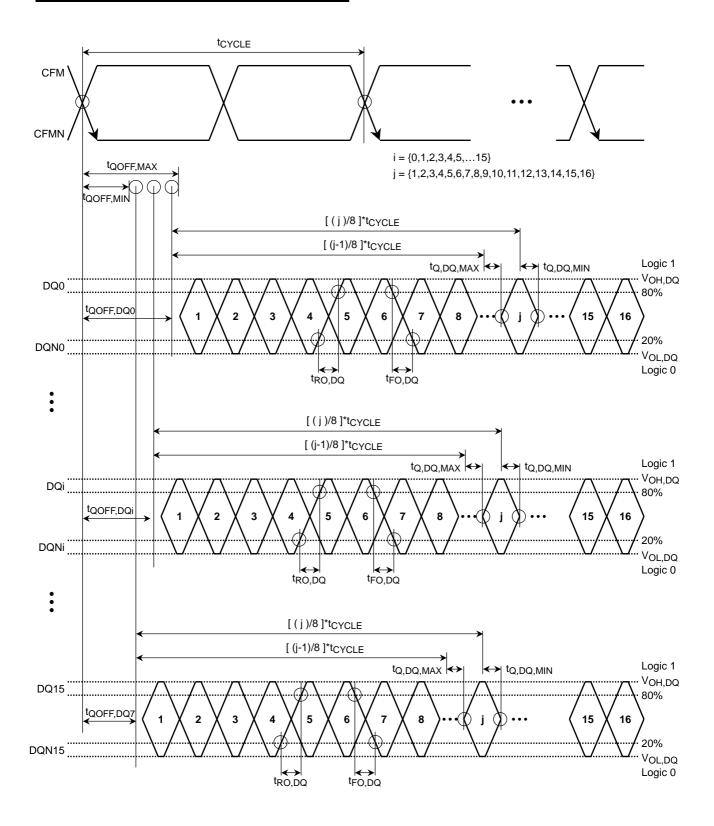

| DRSL DQ Transmit Timing                  |                                       |

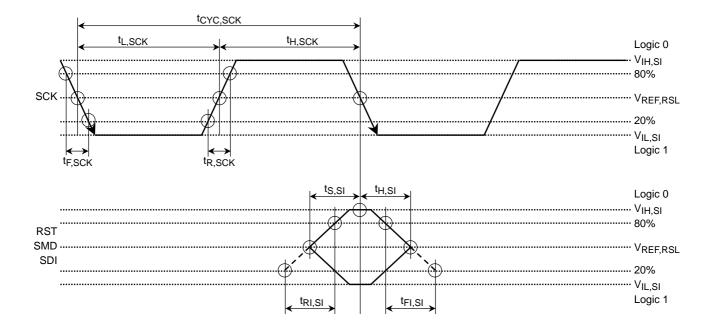

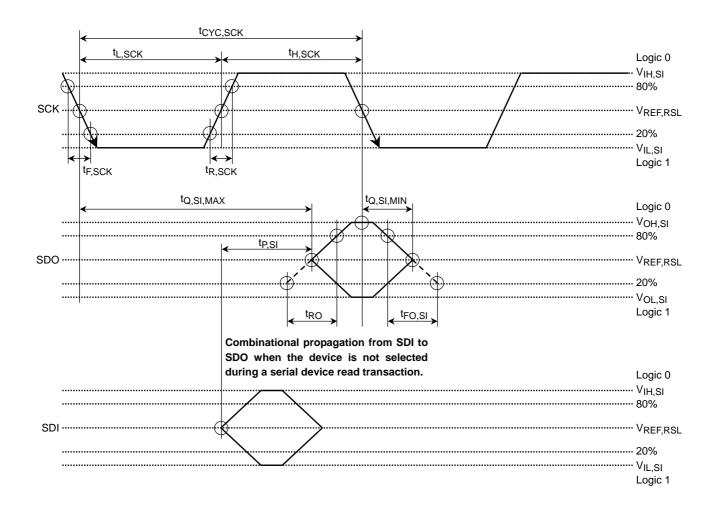

| Serial Interface Receive Timing          | 00<br>71                              |

| Serial Interface Transmit Timing         | 72                                    |

| Package Description                      | 73                                    |

| Package Parasitic Summary                | <br>73                                |

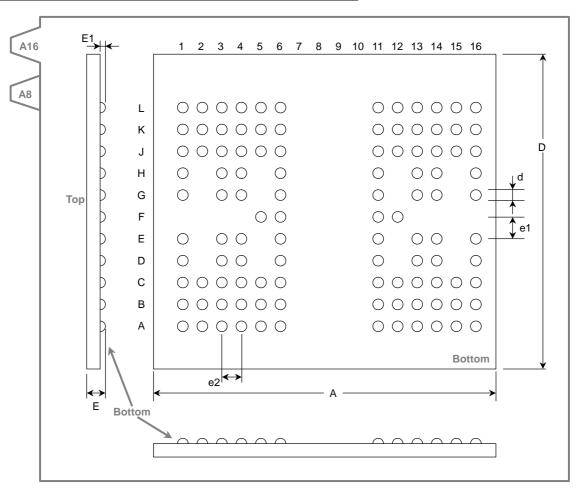

| Package Mechanical Drawing               | 75                                    |

| Package Pin Numbering                    | , , , , , , , , , , , , , , , , , , , |

| . actuage . in transcoming               | 10                                    |

# **Table of Tables**

| Table 1.  | Pin Descriptions                      | 7  |

|-----------|---------------------------------------|----|

| Table 2.  | Request Field Description             |    |

| Table 3.  | OP Field Encoding Summary             | 12 |

| Table 4.  | ROP Field Encoding Summary            | 12 |

| Table 5.  | POP Field Encoding Summary            | 13 |

| Table 6.  | XOP Field Encoding Summary            | 13 |

| Table 7.  | Packet Interaction Summary            |    |

| Table 8.  | SCMD Field Encoding Summary           | 33 |

| Table 9.  | Initialization Timing Parameters      | 48 |

| Table 10. | , , ,                                 |    |

| Table 11. |                                       |    |

| Table 12. | Electrical Conditions                 | 59 |

| Table 13. | Timing Conditions                     | 60 |

| Table 14. | Electrical Characteristics            | 61 |

| Table 15. | Supply Current Profile                | 62 |

| Table 16. | Timing Characteristics                | 62 |

| Table 17. |                                       | •  |

| Table 18. | Package RSL Parasitic Summary         | 73 |

| Table 19. | CSP x16 Package Mechanical Parameters | 75 |

# **Table of Figures**

| Figure 1.                | XDR DRAM Device Write and Read Transactions         | 3          |

|--------------------------|-----------------------------------------------------|------------|

| Figure 2.                | 512Mb (8x4Mx16) XDR DRAM Block Diagram              | 9          |

| Figure 3.                | Request Packet Formats                              | 11         |

| Figure 4.                | ACT-, RD-, WR-, PRE-to-ACT Packet Interactions      | 16         |

|                          | ACT-, RD-, WR-, PRE-to-RD Packet Interactions       | 10<br>17   |

| Figure 5.                | ACT, ND, WD, DDF to WD Poolst Interactions          | 40         |

| Figure 6.                | ACT-, RD-, WR-, PRE-to-WR Packet Interactions       | 18         |

| Figure 7.                | ACT-, RD-, WR-, PRE-to-PRE Packet Interactions      | 19         |

| Figure 8.                | Request Scheduling Examples                         | 21         |

| Figure 9.                | Write Transactions                                  |            |

| Figure 10.               | Read Transactions                                   |            |

| Figure 11.               | Interleaved Transactions                            |            |

| Figure 12.               | Write/Read Interaction                              | 29         |

| Figure 13.               | Propagation Delay                                   | 32         |

| Figure 14.               | Serial Write Transaction                            | 34         |

| Figure 15.               | Serial Read Transaction – Selected DRAM             | 3 <i>1</i> |

| Figure 16.               | Serial Read Transaction – Non-Selected DRAM         | 3 <i>1</i> |

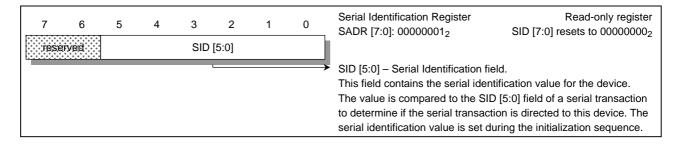

| Figure 17.               | Serial Identification (SID) Register                | 36         |

|                          | Serial Identification (SEC) Register                | 36         |

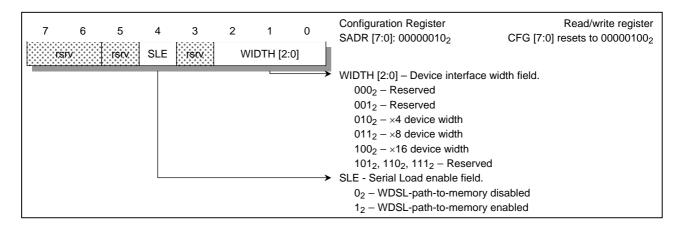

| Figure 18.               | Configuration (CFG) Register                        | 00         |

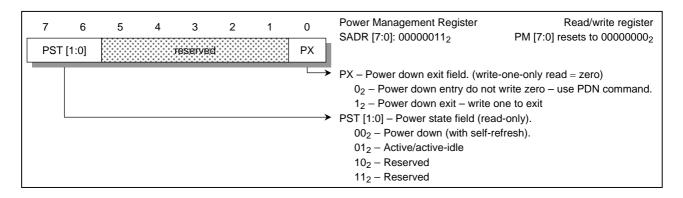

| Figure 19.               | Power Management (PM) Register                      | 36         |

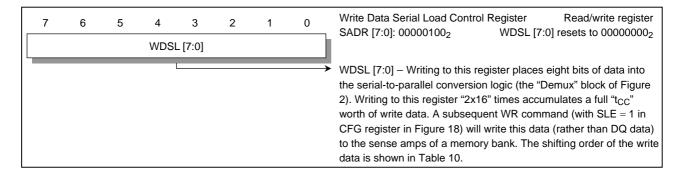

| Figure 20.               | Write Data Serial Load (WDSL) Control Register      | 36         |

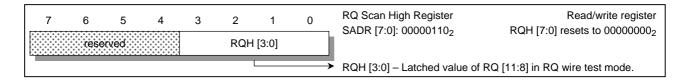

| Figure 21.               | RQ Scan High (RQH) Register                         | 37         |

| Figure 22.               | RQ Scan Low (RQL) Register                          | 37         |

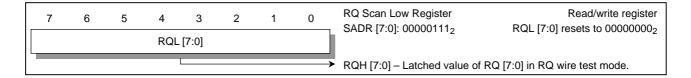

| Figure 23.               | Refresh Bank (REFB) Control Register                | 37         |

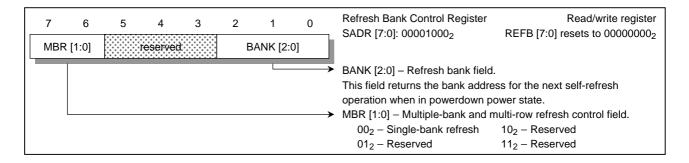

| Figure 24.               | Refresh High (REFH) Row Register                    | 37         |

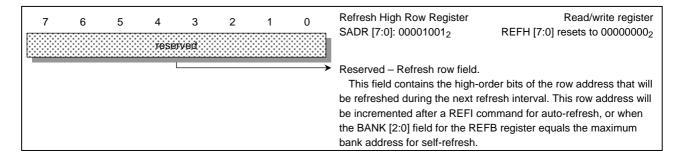

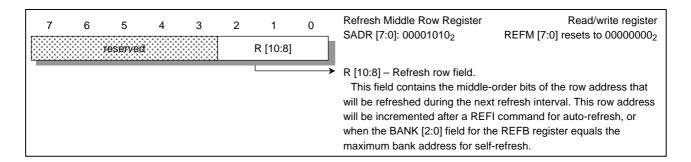

| Figure 25.               | Refresh Middle (REFM) Row Register                  | 37         |

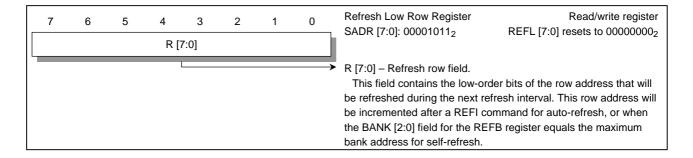

| Figure 26.               | Refresh Low (REFL) Row Register                     | 38         |

| Figure 27.               | IO Configuration (REFL) Register                    | 38         |

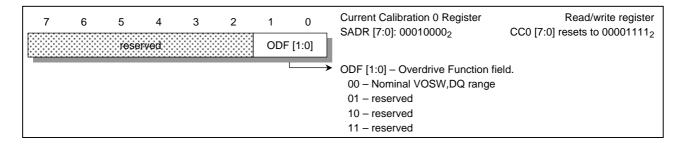

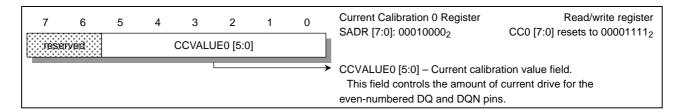

| Figure 28.               | Current Calibration 0 (CC0) Register                | 38         |

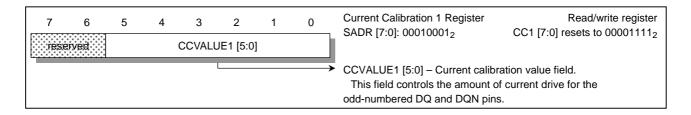

| Figure 29.               | Current Calibration 1 (CC1) Register                | 38         |

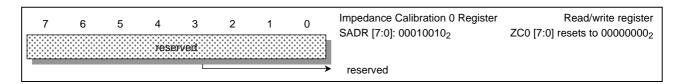

| Figure 30.               | Impedance Calibration 0 (ZC0) Register              | 38         |

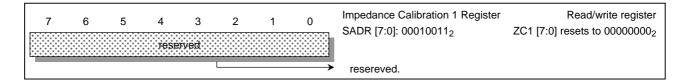

| Figure 31.               | Impedance Calibration 1 (ZC1) Register              | 30         |

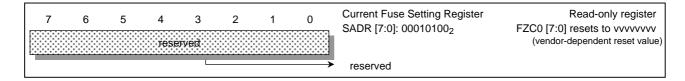

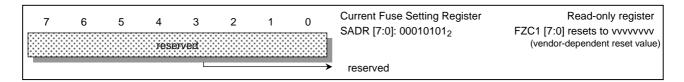

|                          | Current Fuse Setting 0 (FZC0) Register              | 33<br>20   |

| Figure 32.               | Current Fuse Setting 0 (FZC0) Register              | 39<br>30   |

| Figure 33.               | Current ruse Setting 1 (FZC1) Register              | 39         |

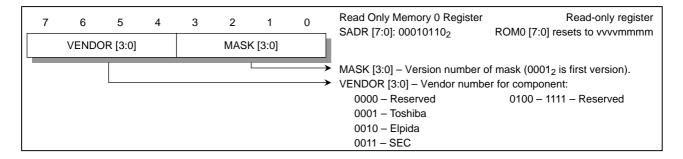

| Figure 34.               | Read Only Memory 0 (ROM0) Register                  | 39         |

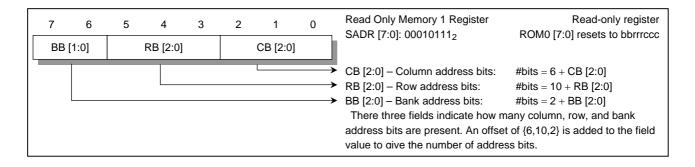

| Figure 35.               | Read Only Memory 1 (ROM1) Register                  | 39         |

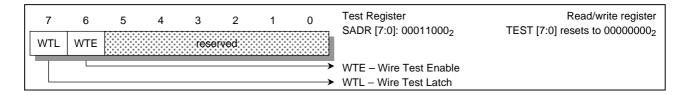

| Figure 36.               | Test Register                                       | 40         |

| Figure 37.               | DLL Register                                        | 40         |

| Figure 38.               | PLL0 Register                                       | 40         |

| Figure 39.               | PLL1 Register                                       | 40         |

| Figure 40.               | IFT Register                                        | 40         |

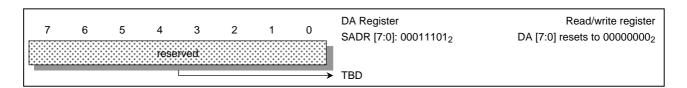

| Figure 41.               | DA Register                                         | 40         |

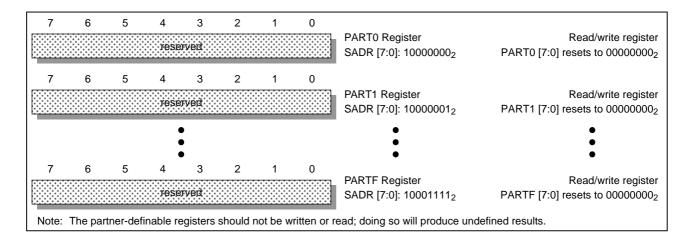

| Figure 42.               | Partner-Definable (PART) Register                   | 41         |

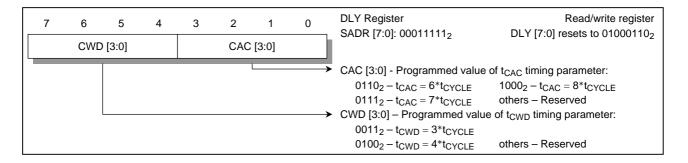

| Figure 43.               | Delay (DLY) Control Register                        | 41         |

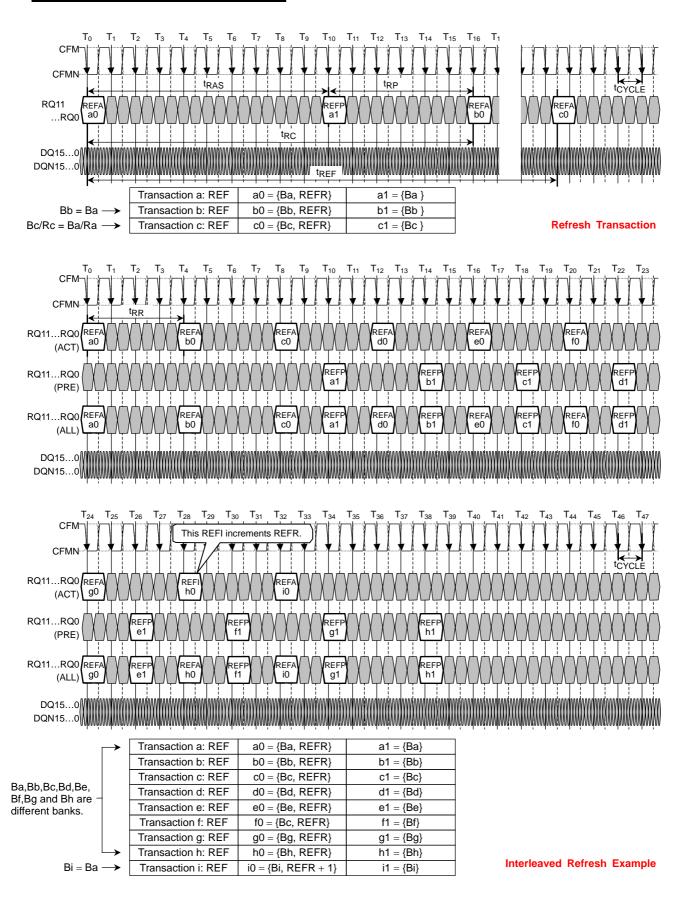

| Figure 44.               | Refresh Transactions                                | 43         |

| Figure 45.               | Calibration Transactions                            | 44         |

| Figure 46.               | Power State Management                              | 46         |

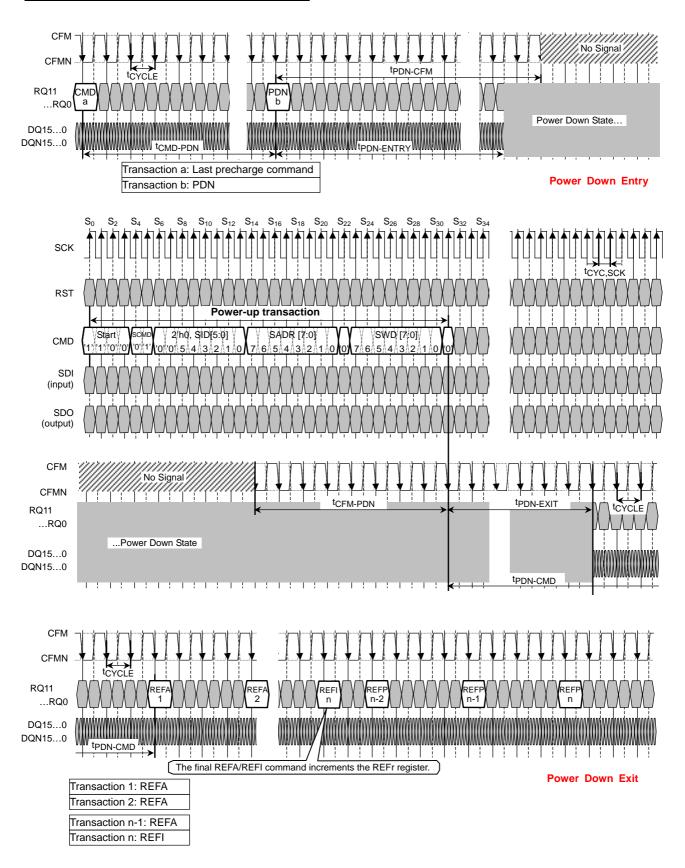

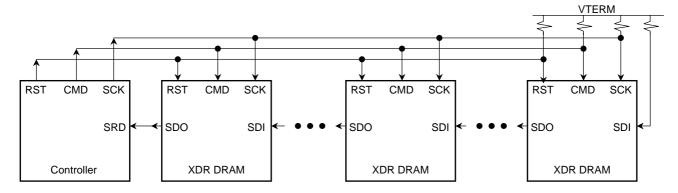

| Figure 47.               | Serial Interface Systems Topology                   | 47         |

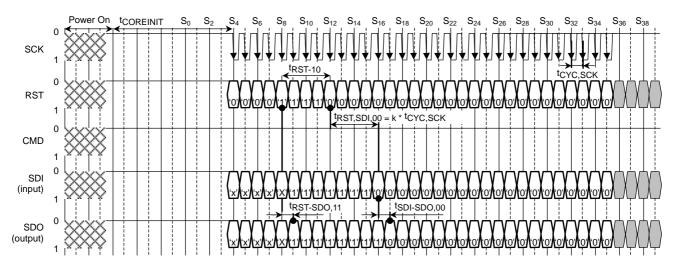

| Figure 48.               | Initialization Timing for XDR DRAM [ k ] Device     | 4 <i>1</i> |

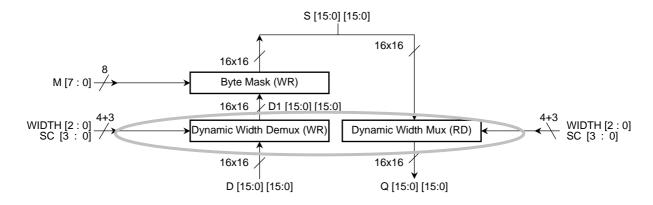

|                          | Multiplexes for Dynamic Width Control               | 4/<br>52   |

| Figure 49.               | Multiplexes for Dynamic witch Control               | 52         |

| Figure 50.               | D-to-S and S-to-Q Mapping for Dynamic Width Control | 53         |

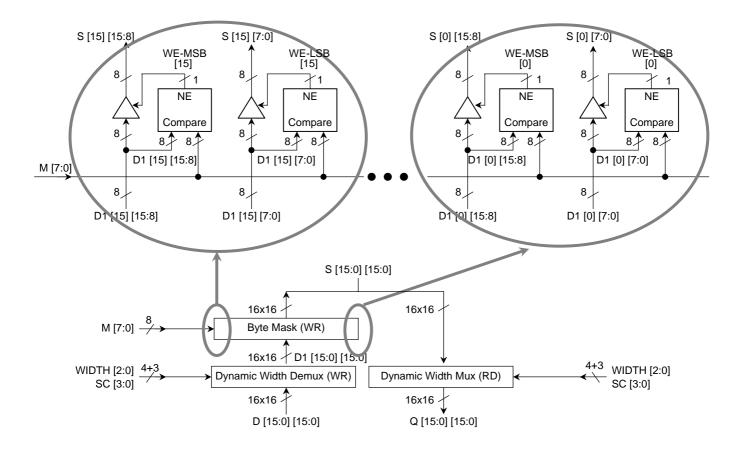

| Figure 51.               | Byte Mask Logic                                     | 54         |

| Figure 52.               | Write-Masked (WRM) Transaction Example              | 55         |

| Figure 53.               | Write/Read Interaction - No ERAW Feature            |            |

| Figure 54.               | Write/Read Interaction – ERAW Feature               | 56         |

| Figure 55.               | XDR DRAM Block Diagram with Bank Sets               | 57         |

| Figure 56.               | Simultaneous Precharge - tPP-D Cases                | 58         |

| Figure 57.               | Clocking Waveforms                                  | 65         |

| Figure 58.               | RSL RQ Receive Waveform                             | 66         |

| Figure 59.               | DRSL DQ Receive Waveform                            | 68         |

| Figure 60.               | RSL DQ Transmit Waveforms                           | 70         |

| Figure 61.               | Serial Interface Receive Waveforms                  | 71         |

| Figure 62.               | Serial Interface Transmit Waveforms                 | 72         |

| Figure 63.               | Equivalent Circuits for Package Parasitic           | 7 <i>1</i> |

| Figure 64.               | CSP x16 Package Mechanical Drawing                  | 7F         |

| Figure 64.<br>Figure 65. |                                                     | 1 J        |

| . Iuule 03.              | ODI A 10 FAURAUC - FIII INUIIIDCI IIIU (LUD VICW)   | /10        |

# **Pin Description**

Table 1 summarizes the pin functionality of the XDR DRAM device. The first group of pins provide the necessary supply voltages. These include VDD and GND for the core and interface logic, VREF for receiving input signals, and VTERM for driving output signals.

The next group of pins is used for high bandwidth memory accesses. These include DQ15...DQ0 and DQN15...DQN0 for carrying read and write data signals, RQ11...RQ0 for carrying request signals, and CFM and CFMN for carrying timing information used by the DQ, DQN, and RQ signals.

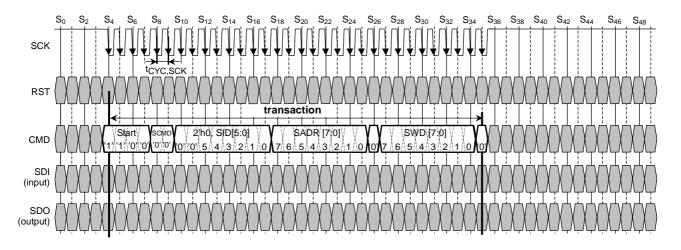

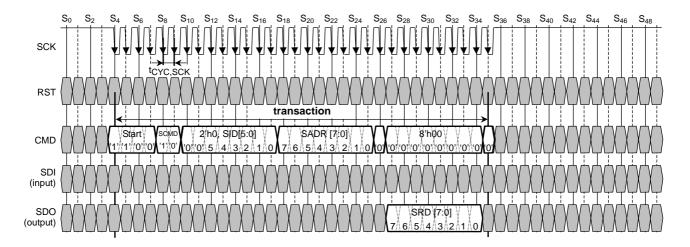

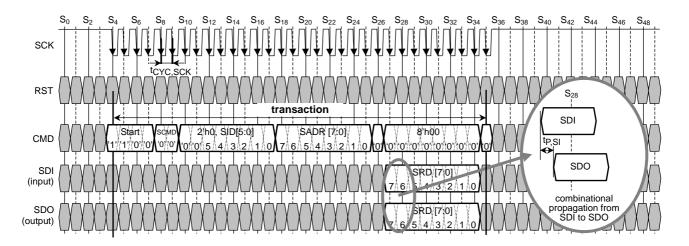

The final set of pins comprises the serial interface that is used for control register accesses. These include RST for initializing the state of the device, CMD for carrying command signals, SDI and SDO for carrying register read data, and SCK for carrying the timing information used by the RST, SDI, SDO, and CMD signals.

Table 1. Pin Descriptions

| Signal          | I/O                         | Туре             | No. of Pins     | Description                                                                                                                                |  |  |

|-----------------|-----------------------------|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>DD</sub> | _                           | _                | 22              | Supply voltage for the core and interface of the device.                                                                                   |  |  |

| GND             | _                           | _                | 26 <sup>a</sup> | Ground reference for the core and interface logic of the device.                                                                           |  |  |

| VREF            | _                           | _                | 1               | Logic threshold reference voltage for RSL signals.                                                                                         |  |  |

| VTERM           | _                           | _                | 6 <sup>a</sup>  | Termination voltage for DRSL signals.                                                                                                      |  |  |

| DQ15DQ0         | I/O                         | DRSL b           | 16              | Positive data signals that carry write or read data to and from the device.                                                                |  |  |

| DQN15DQN0       | I/O                         | DRSL b           | 16              | Negative data signals that carry write or read data to and from the device.                                                                |  |  |

| RQ11RQ0         | ı                           | RSL b            | 12              | Request signals that carry control and address information to the device.                                                                  |  |  |

| CFM             | I                           | DIFFCLK b        | 1               | Clock from master – Positive interface clock used for receiving RSL signals, and receiving and transmitting DRSL signals from the Channel. |  |  |

| CFMN            | I                           | DIFFCLK b        | 1               | Clock from master – Negative interface clock used for receiving RSL signals and receiving and transmitting DRSL signals from the Channel.  |  |  |

| RST             | I                           | RSL b            | 1               | Reset input – This pin is used to initialize the device.                                                                                   |  |  |

| CMD             | ı                           | RSL <sup>b</sup> | 1               | Command input – This pin carries command, address, and control register write data into the device.                                        |  |  |

| SCK             | I                           | RSL b            | 1               | Serial clock input – Clock source used for reading from and writing to the control registers.                                              |  |  |

| SDI             | I                           | RSL b            | 1               | Serial data input – This pin carries control register read data through the device. This pin is also used to initialize the device.        |  |  |

| SDO             | 0                           | CMOS b           | 1               | Serial data output – This pin carries control register read data from the device. This pin also used to initialize the device.             |  |  |

| RSRV            | _                           | _                | 2               | Reserved pins – Follow Rambus XDR system design guidelines for connecting RSRV pins.                                                       |  |  |

| Total pin cou   | Total pin count per package |                  | 108             |                                                                                                                                            |  |  |

a. J6 / J11 / C6 / C11 are optional balls. This table represent a superset across all the generations and densities pf XDR DRAM.

b. All DQ and CFM signals are high-true; low voltage is logic 0 and high voltage is logic 1.

All DQN, CFMN, RQ, RSL and CMOS signals are low-true; high voltage is logic 0 and low voltage is logic 1.

# **Block Diagram**

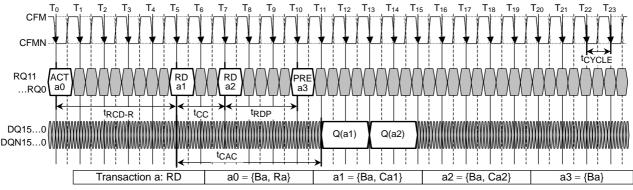

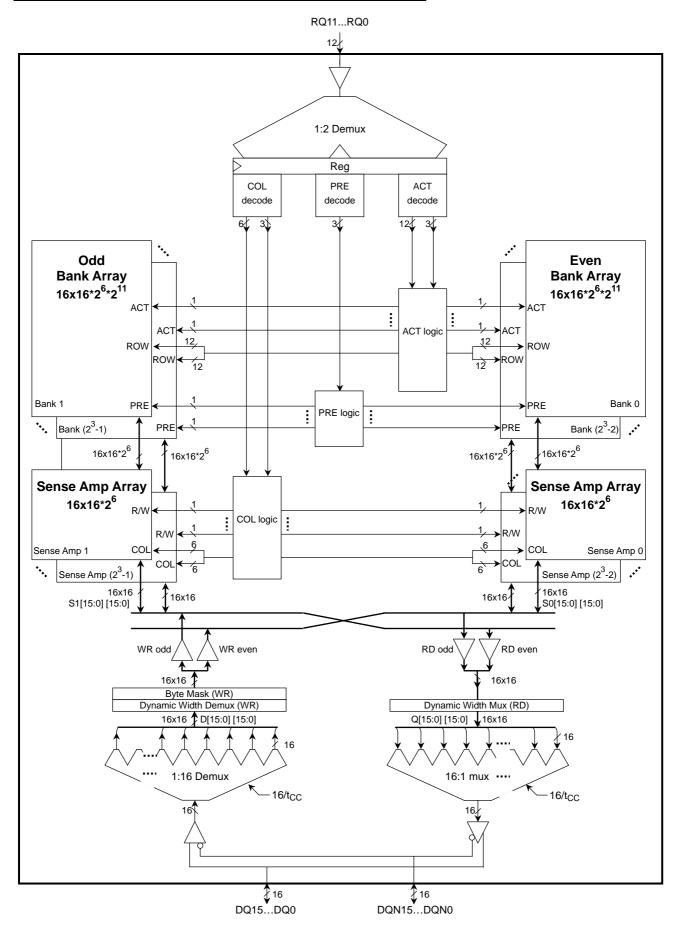

A block diagram of the XDR DRAM device is shown in Figure 2. It shows all interface pins and major internal blocks.

The CFM and CFMN clock signals are received and used by the clock generation logic to produce three virtual clock signals:  $1/t_{CYCLE}$ ,  $2/t_{CYCLE}$ , and  $16/t_{CC}$ . The frequency of these signals are 1x, 2x, and 8x that of the CFM and CFMN signals. These virtual signals show the effective data rate of the logic blocks to which they connect; they are not necessarily present in the actual memory component.

The RQ11...RQ0 pins receive the request packet. Two 12-bit words are received in one tCYCLE interval. This is indicated by the 2/tCYCLE clocking signal connected to the 1: 2 Demux Block that assembles the 24-bit request packet. These 24 bits are loaded into a register (clocked by the 1/tCYCLE clocking signal) and decoded by the Decode Block. The VREF pin supplies a reference voltage used by the RQ receivers.

Three sets of control signals are produced by the Decode Block. These include the bank (BA) and row (R) addresses for an activate (ACT) command, the bank (BR) and row (REFr) addresses for a precharge (PRE) command, the bank (BP) address for a precharge (PRE) command, the bank (BR) address for a refresh precharge (REFP) command, and the bank (BC) and column (C and SC) addresses for a read (RD) or write (WR or WRM) command. In addition, a mask (M) is used for a masked write (WRM) command.

These commands can all be optionally delayed in increments of  $t_{CYCLE}$  under control of delay fields in the request. The control signals of the commands are loaded into registers and presented to the memory core. These registers are clocked at maximum rates determined by core timing parameters, in this case  $1/t_{RR}$ ,  $1/t_{PP}$ , and  $1/t_{CC}$  (1/4, 1/4, and 1/2 the frequency of CFM). These registers may be loaded at any  $t_{CYCLE}$  rising edge. Once loaded, they should not be changed until a  $t_{RR}$ ,  $t_{PP}$ , or  $t_{CC}$  time later because timing paths of the memory core need time to settle.

A bank address is decoded for an ACT command. The indicated row of the selected bank is sensed and placed into the associated sense amp array for the bank. Sensing a row is also referred to as "opening a page" for the bank.

Another bank address is decoded for a PRE command. The indicated bank and associated sense amp array are precharged to a state in which a subsequent ACT command can be applied. Precharging a bank is also called "closing the page" for the bank.

After a bank is given an ACT command and before it is given a PRE command, it may receive read (RD) and write (WR) column commands. These commands permit the data in the bank's associated sense amp array to be accessed.

For a WR command, the bank address is decoded. The indicated column of the associated sense amp array of the selected bank is written with the data received from the DQ15...DQ0 pins.

The bank address is decoded for a RD command. The indicated column of the selected bank's associated sense amp array is read. The data is transmitted onto the DQ15...DQ0 pins.

The DQ15...DQ0 pins receive the write data packet (D) for a write transaction. 16 sixteen-bit words are received in one  $t_{CC}$  interval. This is indicated by the  $16/t_{CC}$  clocking signal connected to the 1:16 Demux Block that assembles the 16x16-bit write data packet. The write data is then driven to the selected Sense Amp Array Bank.

16 sixteen-bit words are accessed in the selected Sense Amp Array Bank for a read transaction. The DQ15...0 pins transmit this read data packet (Q) in one  $t_{CC}$  interval. This is indicated by the  $16/t_{CC}$  clocking signal connected to the 16:1 Mux Block. The VTERM pin supplies a termination voltage for the DQ pins.

The RST, SCK, and CMD pins connect to the Control Register block. These pins supply the data, address and control needed to write the control registers. The read data for these registers is accessed through the SDO/SDI pins. These pins are also used to initialize the device.

The controls registers are used to transition between power modes, and are also used for calibrating the high speed transmit and receive circuits of the device. The control registers also supply bank (REFB) and row (REFr) addresses for refresh operations.

Figure 2. 512Mb (8x4Mx16) XDR DRAM Block Diagram

### **Request Packets**

A request packet carries address and control information to the memory device. This section contains tables and diagrams for packet formats, field encoding and packet interactions.

#### Request Packet Formats

There are five types of request packets:

- 1. ROWA specifies an ACT command

- 2. COL specifies RD and WR commands

- 3. COLM specifies a WRM command

- 4. ROWP specifies PRE and REF commands

- 5. COLX specifies the remaining commands

Table 2 describes fields within different request packet types. Various request packet type formats are illustrated in Figure 3.

Each packet type consists of 24 bits sampled on the RQ11..RQ0 pins on two successive edges of the CFM/CFMN clock. The request packet formats are distinguished by the OP3..OP0 field. This field also specifies the operation code of the desired command.

In the ROWA packet, a bank address (BA), row address (R), and command delay (DELA) are specified for the activate (ACT) command.

In the COL packet, a bank address (BC), column address (C), sub-column address (SC), command delay (DELC), and sub-opcode (WRX) are specified for the read (RD) and write (WR) commands.

In the COLM packet, a bank address (BC), column address (C), sub-column address (SC), command delay (DELC), and mask field (M) are specified for the masked write (WRM) command.

In the ROWP packet, two independent commands may be specified. A bank address (BP) and sub-opcode (POP) are specified for the precharge (PRE) commands. An address field (RA) and sub-opcode (ROP) are specified for the refresh (REF) commands.

In the COLX packet, a sub-operation code field (XOP) is specified for the remaining commands.

Table 2. Request Field Description

| Field    | Packet Types                | Description                                                                                                                                         |

|----------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| OP3OP0   | ROWA/ROWP/CO<br>L/COLM/COLX | 4-bit operation code that specifies packet format.<br>(Encoded commands are in a Table 3 on page 12.)                                               |

| DELA     | ROWA                        | Delay the associated row activate command by 0 or 1 t <sub>CYCLE</sub> .                                                                            |

| BA2BA0   | ROWA                        | 3-bit bank address for row activate command.                                                                                                        |

| R10R0    | ROWA                        | 11-bit row address for row activate command.                                                                                                        |

| WRX      | COL                         | Specifies RD (=0) or WR (=1) command.                                                                                                               |

| DELC     | COL                         | Delay the column read or write command by 0 or 1 t <sub>CYCLE</sub> .                                                                               |

| BC2BC0   | COL/COLM                    | 3-bit bank address for column read or write command.                                                                                                |

| C9C4     | COL/COLM                    | 6-bit column address for column read or write command.                                                                                              |

| SC3SC0   | COL/COLM                    | 4-bit sub-column address for dynamic width (see "Dynamic Width Control" on page 49).                                                                |

| M7M0     | COLM                        | 8-bit mask for masked-write command WRM.                                                                                                            |

| POP2POP0 | ROWP                        | 3-bit operation code that specifies row precharge command with a delay of 0 to 3 t <sub>CYCLE</sub> . (Encoded commands are in Table 5 on page 13). |

| BP2BP0   | ROWP                        | 3-bit bank address for row precharge command.                                                                                                       |

| ROP2ROP0 | ROWP                        | 3-bit operation code that specifies refresh commands. (Encoded commands are in Table 4 on page 12).                                                 |

| RA7RA0   | ROWP                        | 8-bit refresh address field (specifies BR bank address, delay value, and REFr load value)                                                           |

| XOP3XOP0 | COLX                        | 4-bit extended operation code that specifies column preload, calibration and Power Down commands. (Encoded commands are in Table 6 on page13).      |

# Figure 3. Request Packet Formats

### Request Field Encoding

*Operation-code fields* are encoded within different packet types to specify commands. Table 3 through Table 6 provides packet type and encoding summaries.

Table 3 shows the OP field encoding for the five packet types. The COLM and ROWA packets each specify a single command: ACT and WRM. The COL, COLX, and ROWP packets each use additional fields to specify multiple commands: WRX, XOP, and POP/ROP, respectively. The COLM packet specifies the masked write command WRM. This is like the WR unmasked write command, except that a mask field M7...M0 indicates whether each byte of the write data packet is written or not written. The ROWA packet specifies the row activate command ACT. The COL packet uses the WRX field to specify the column read and column write (unmasked) commands

| OP [3:0]             | Packet | Command | Description                                                                                                             |

|----------------------|--------|---------|-------------------------------------------------------------------------------------------------------------------------|

| 0000                 | _      | NOP     | No operation                                                                                                            |

| 0001 COL -           |        | RD      | Column read (WRX = 0). Column C9C4 of sense amp in bank BC2BC0 is read to DQ bus after DELC* $t_{CYCLE}$ .              |

|                      |        | WR      | Column write (WRX = 1). Write DQ bus to column C9C4 of sense amp in bank BC2BC0 after DELC*tCYCLE.                      |

| 0010                 | COLX   | CALy    | XOP3XOP0 specifies a calibrate or Power Down command – see Table 6 on page 13.                                          |

| 0011 ROWP REFy, LRRr |        | PREx    | POP2POP0 specifies a row precharge command – see Table 5 on page 13.                                                    |

|                      |        | ,       | ROP2ROP0 specifies a row refresh command or load REFr register command – see Table 4 on page 12.                        |

| 01xx                 | ROWA   | ACT     | Row activate command. Row R11R0 of bank BA2BA0 is placed into the sense amp of the bank after DELA*t <sub>CYCLE</sub> . |

| 1xxx                 | COLM   | WRM     | Column write command (masked) – mask M7M0 specifies which bytes are written.                                            |

Table 3. OP Field Encoding Summary

Encoding of the ROP field in the ROWP packet is shown in Table 4. The first encoding specifies a NOPR (no operation) command. The REFP command uses the RA field to select a bank to be precharged. The REFA and REFI commands use the RA field and REFH/M/L registers to select a bank and row to be activated for refresh. The REFI command also increments the REFH/M/L register. The REFP, REFA, and REFI commands may also be delayed by up to 3\*tCYCLE using the RA [7:6] field. The LRR0, LRR1, and LRR2 commands load the REFH/M/L registers from the RA [7:0] field.

ROP [2:0] Command Description 000 **NOPR** No operation Refresh precharge command. Bank RA2...RA0 is precharged. REFP 001 This command is delayed by {0, 1, 2, 3}\*tCYCLE (the value is given by the expression (2\*RA [7] + RA [6]). Refresh activate command. Row R [11:0] (from REFH/M/L register) of bank RA2...RA0 is placed into sense 010 **REFA** This command is delayed by  $\{0, 1, 2, 3\}$ \* $t_{CYCLE}$  (the value is given by the expression (2\*RA [7] + RA [6])). Refresh activate command. Row R [11:0] (from REFH/M/L register) of bank RA2...RA0 is placed into sense 011 REFI This command is delayed by {0, 1, 2, 3}\*tCYCLE (the value is given by the expression (2\*RA [7] + RA [6]). R[11:0] field of REFH/M/L register is incremented after the activate command has completed. LRR0 100 Load Refresh Low Row register (REFL). RA [7:0] is stored in R [7:0] field. LRR1 Load Refresh Middle Row register (REFM). RA [3:0] is stored in R [11:8] field. 101 110 LRR2 Load Refresh High Row register - not used with this device Reserved 111

Table 4. ROP Field Encoding Summary

The REFH/M/L registers are also referred to as the REFr registers. Note that only the bits that are needed for specifying the refresh row (12 bits in all) are implemented in the REFr registers - the rest are reserved. Note also that the RA2...RA0 field that specifies the refresh bank address is also referred to as BR2...BR0. See "Refresh Transactions" on page 40.

Table 5 shows the POP field encoding in the ROWP packet. The first encoding specifies a NOPP (no operation) command. There are four variations of PRE (precharge) command. Each uses the BP field to specify the bank to be precharged. Each also specifies a different delay of up to 3\*tCYCLE using the POP [1:0] field. A precharge command may be specified in addition to a refresh command using the ROP field.

Table 5. POP Field Encoding Summary

| POP [2:0] | Command | Description                                                                                           |

|-----------|---------|-------------------------------------------------------------------------------------------------------|

| 000       | NOPP    | No operation                                                                                          |

| 001       | _       | Reserved.                                                                                             |

| 010       | _       | Reserved.                                                                                             |

| 011       | _       | Reserved.                                                                                             |

| 100       | PRE0    | Row precharge command – Bank BP2 BP0 is precharged. This command is delayed by 0*t <sub>CYCLE</sub> . |

| 101       | PRE1    | Row precharge command – Bank BP2 BP0 is precharged. This command is delayed by 1*t <sub>CYCLE</sub> . |

| 110       | PRE2    | Row precharge command – Bank BP2 BP0 is precharged. This command is delayed by 2*t <sub>CYCLE</sub> . |

| 111       | PRE3    | Row precharge command – Bank BP2 BP0 is precharged. This command is delayed by 3*tCYCLE.              |

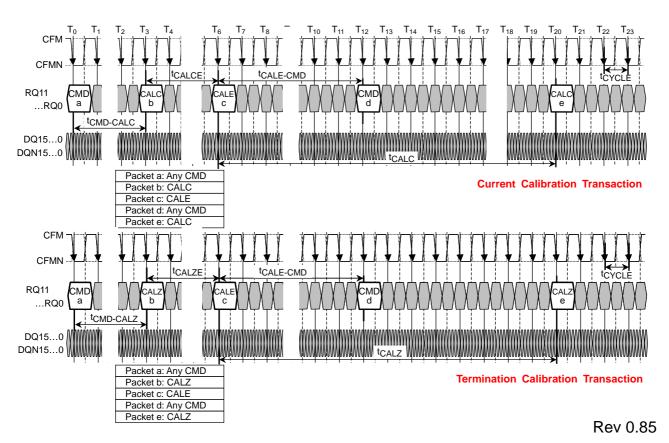

Table 6 shows the XOP field encoding in the COLX packet. This field encodes the remaining commands. The CALC and CALE commands perform calibration operations to ensure signal integrity on the Channel. See "Calibration Transactions" on page 42.

The PDN command causes the device to enter a power-down state. See "Power State Management" on page 43.

Table 6. XOP Field Encoding Summary

| XOP [3:0] | Command | Command and Description | XOP [3:0] | Command | Command and Description         |

|-----------|---------|-------------------------|-----------|---------|---------------------------------|

| 0000      |         | Reserved                | 1000      | CALC    | Current calibration command.    |

| 0001      |         | Reserved.               | 1001      | CALZ    | Impedance calibration command.  |

| 0010      |         | Reserved.               | 1010      | CALE    | End calibration command (CALC). |

| 0011      |         | Reserved.               | 1011      |         | Reserved.                       |

| 0100      |         | Reserved.               | 1100      | PDN     | Enter Power Down power state.   |

| 0101      |         | Reserved.               | 1101      |         | Reserved                        |

| 0110      |         | Reserved                | 1110      |         | Reserved                        |

| 0111      |         | Reserved                | 1111      |         | Reserved.                       |

#### Request Field Interactions

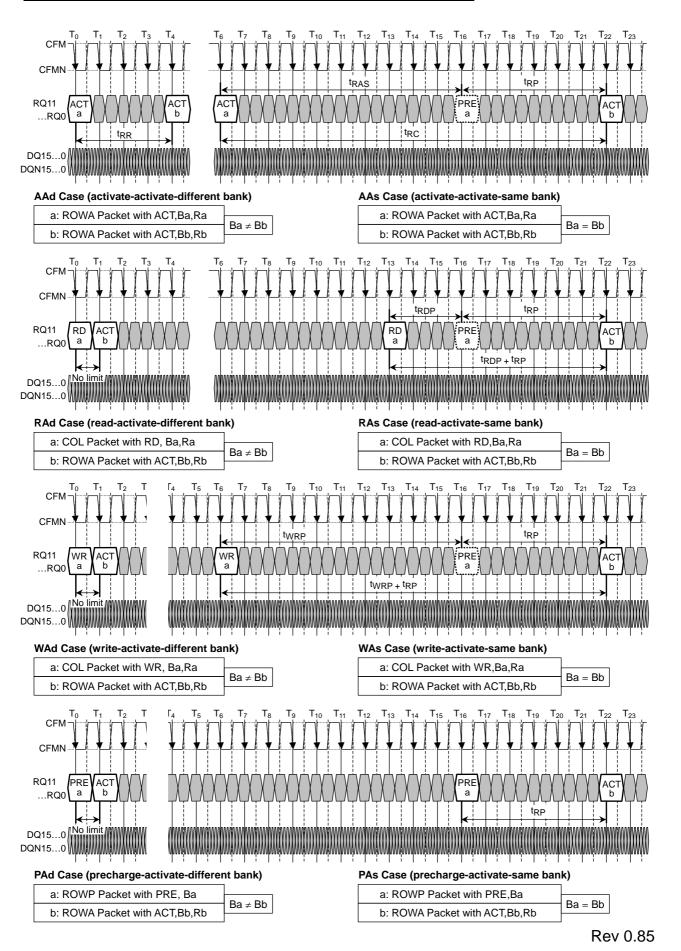

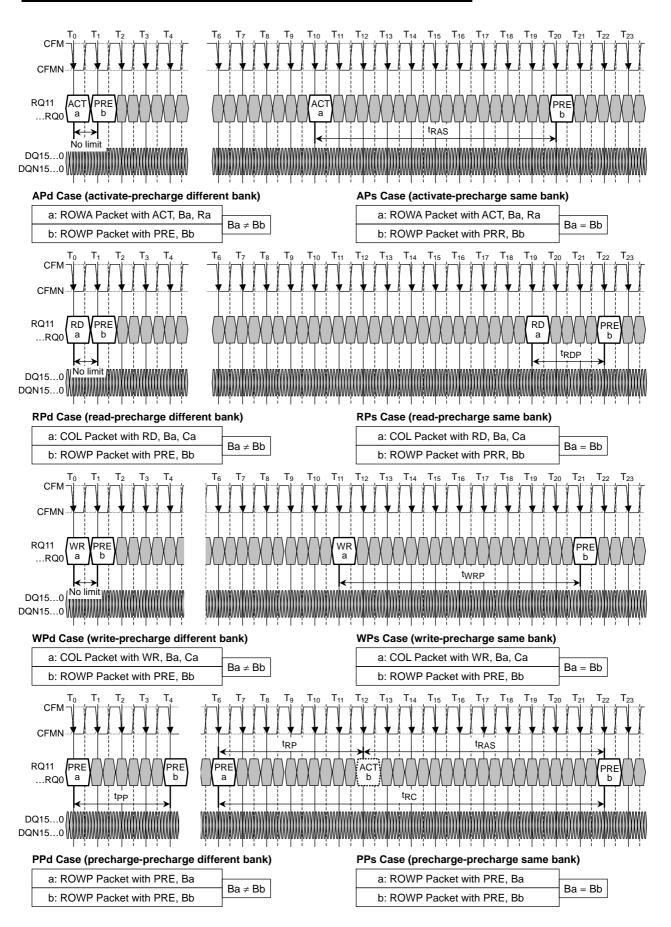

A summary of request packet interactions is shown in Table 7. Each case is limited to request packets with commands that perform memory operations (including refresh commands). This includes all commands in ROWA, ROWP, COL, and COLM packets. The commands in COLX packets are described in later sections. See "Maintenance Operations" on page 40.

Request packet/command "a" is followed by request packet/command "b". The minimum possible spacing between these two packet/commands is  $0*t_{CYCLE}$ . However, a larger time interval may be needed because of a resource interaction between the two packet/commands. If the minimum possible spacing is  $0*t_{CYCLE}$ , then an entry of "No limit" is shown in the table.

Note that the spacing values shown in the table are relative to the *effective* beginning of a packet/command. The use of the delay field with a command will delay the position of the effective packet/command from the position of the actual packet/command. See "Dynamic Request Scheduling" on page 20.

Any of the packet/command encoding under one of the four operation types is equivalent in terms of the resource constraints. Therefore, both the horizontal columns (packet "a") and vertical rows (packet "b") of the interaction table are divided into four major groups.

The four possible operation types for request packets a and b include:

: [A] Activate Row • ROWA/ACT

ROWP/REFA

ROWP/REFI

[R] Read Column • COL/RD

; [W] Write Column • COL/WR

COLM/WRM

[P] Precharge Row • ROWP/PRE

ROWP/REFP

Table 7. Packet Interaction Summary

|                                                      |                    | Second packet/command to bank Bb                          |                                                             |                                                             |                                 |  |

|------------------------------------------------------|--------------------|-----------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|--|

| First packet command to bank<br>Ba                   |                    | Activate Row [A]                                          | Read Column [R]                                             | Write Column [W]                                            | Precharge Row[P]                |  |

|                                                      |                    | ROWA – ACT Bb<br>ROWP – REFA Bb<br>ROWP – REFI Ba         | COL – RD Bb                                                 | COL – WR Bb<br>COLM – WRM Bb                                | ROWP – PRE Bb<br>ROWP – REFP Bb |  |

| Activate Row [A] ROWA – ACT Ba                       | Ba,Bb<br>different | Case AAd: t <sub>RR</sub>                                 | Case ARd: No limit                                          | Case AWd: No limit                                          | Case APd: No limit              |  |

| ROWP – REFA Ba<br>ROWP – REFI Ba                     | Ba,Bb same         | Case AAs: t <sub>RC</sub>                                 | Case ARs: t <sub>RCD-R</sub>                                | Case AWs: t <sub>RCD-W</sub>                                | Case APs: t <sub>RAS</sub>      |  |

| Read Column [R]                                      | Ba,Bb<br>different | Case RAd: No limit                                        | Case RRd: t <sub>CC</sub>                                   | Case RWd <sup>a</sup> : t <sub>∆RW</sub>                    | Case RPd: No limit              |  |

| COL – RD Ba                                          | Ba,Bb same         | Case RAs <sup>b</sup> : t <sub>RDP</sub> +t <sub>RP</sub> | Case RRs: t <sub>CC</sub>                                   | Case RWs <sup>a</sup> : t∆RW                                | Case RRs: t <sub>RDP</sub>      |  |

| Write Column [W] COL – WR Ba                         | Ba,Bb<br>different | Case WAd: No limit                                        | Case WRd <sup>C</sup> : t <sub>∆WR</sub>                    | Case WWd: t <sub>CC</sub>                                   | Case WPd: No limit              |  |

| COLM – WRM Ba                                        | Ba,Bb same         | Case WAs <sup>b</sup> : t <sub>WRP</sub> +t <sub>RP</sub> | Case WRs <sup>C</sup> : t <sub>∆WR</sub>                    | Case WWs: t <sub>CC</sub>                                   | Case WPs: t <sub>WRP</sub>      |  |

| Precharge Row [P]<br>ROWP – PRE Ba<br>ROWP – REFP Ba | Ba,Bb<br>different | Case PAd: No limit                                        | Case PRd: No limit                                          | Case PWd: No limit                                          | Case PPd: t <sub>PP</sub>       |  |

|                                                      | Ba,Bb same         | Case PAs: t <sub>RP</sub>                                 | Case PRs <sup>d</sup> : t <sub>RP</sub> +t <sub>RCD-R</sub> | Case PWs <sup>d</sup> : t <sub>RP</sub> +t <sub>RCD-W</sub> | Case PPs: t <sub>RC</sub>       |  |

| See Examples:                                        |                    | Figure 4                                                  | Figure 5                                                    | Figure 6                                                    | Figure 7                        |  |

a.  $t_{\Delta RW}$  is equal to  $t_{CC}$  +  $t_{RW-BUB,XDR}$   $t_{CAC}$  -  $t_{CWD}$  and is defined in Table 17. This also depends upon propagation delay – See "Propagation Delay" on page 30.

b. A PRE command is needed between the RD and ACT/REFA commands or the WR/WRM and ACT/REFA commands.

c.  $t_{\Delta WR}$  is defined in Table 17.

d. An ACT command is needed between the PRE/REFP and RD commands or the PRE/REFP and WR/WRM commands.

The first request is shown along the vertical axis on the left of the table. The second request is shown along the horizontal axis at the top of the table. Each request includes a bank specification "Ba" and "Bb". The first and second banks may be the same, or they may be different. These two sub cases for each interaction are shown along the vertical axis on the left.

There are 32 possible interaction cases altogether. The table gives each case a label of the form "xyz", where "x" and "y" are one of the four operation types ("A" for Activate, "R" for Read, "W" for Write, or "P" for Precharge) for the first and second request, respectively, and "z" indicates the same bank ("s") or different bank ("d").

Along the horizontal axis at the bottom of the table are cross-references to four figures (Figure 4 through Figure 7). Each figure illustrates the eight cases in the corresponding vertical column. Thus, Figure 4 shows the eight cases when the second request is an activate operation ("A"). In the following discussion of the cases, only those in which the interaction interval is greater than tCYCLE will be described.

### **Request Interactions Cases**

In Figure 4, the interaction interval for the AAd case is transfer is the row-to-row time and is the minimum interval between activate commands to different banks of a device.

The interaction interval for the AAs case is  $t_{RC}$ . This is the row cycle time parameter and is the minimum interval between activate commands to same banks of a device. A precharge operation must be inserted between the two activate operations.

The interaction interval for the RAs case is tWRP + tRP. A precharge operation must be inserted between the read and activate operation. The minimum interval between a read and a precharge operation to a bank is tRDP. The minimum interval between a precharge and an activate operation to a bank is tRP.

The interaction interval for the WAs case is tWRP + tRP. A precharge operation must be inserted between the read and the activate operation. The minimum interval between a write and a precharge operation to a bank is tWRP. The minimum interval between a precharge and an activate operation to a bank is tRP.

The interaction interval for the PAs case is  $t_{RP}$ . The minimum interval between a precharge and an activate operation to a bank is  $t_{RP}$ .

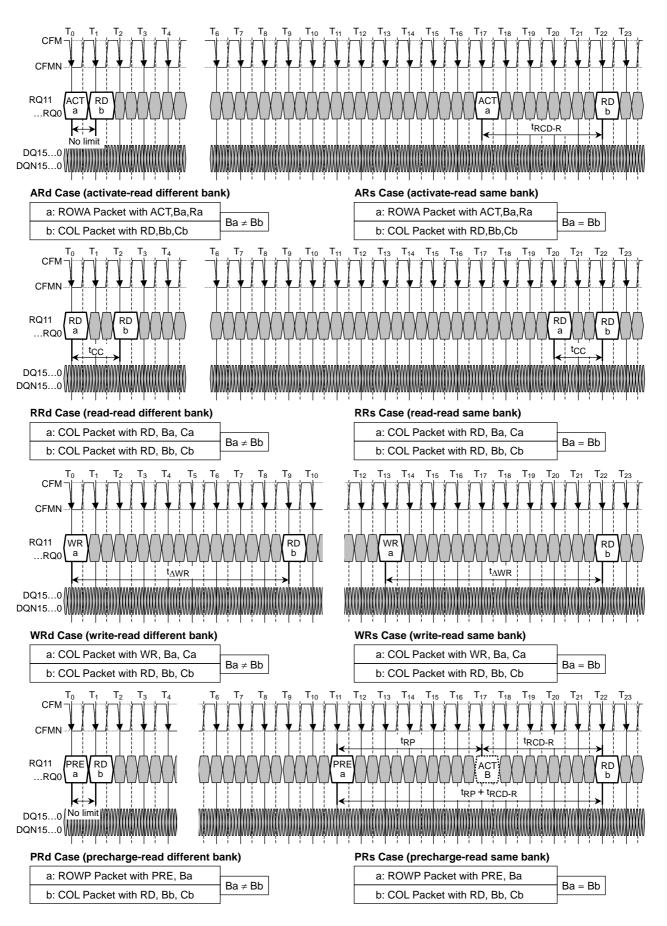

In Figure 5, the interaction interval for the ARs case is  $t_{RCD-R}$ . This is the row-to-column-read time parameter and represents the minimum interval between an activate operation and a read operation to a bank.

The interaction interval for the RRd and RRs cases is  $t_{CC}$ . This is the column-to-column time parameter and represents the minimum interval between two read operations.

The interaction interval for the WRd and WRs cases is  $t\Delta$ WR. This is the write-to-read time parameter and represents the minimum interval between a write and a read operation to any banks. See "Read/Write Interaction" on page 28.

The interaction interval for the PRs case is  $t_{RP} + t_{RCD-R}$ . An activate operation must be inserted between the precharge and the read operation. The minimum interval between a precharge and an activate operation to a bank is  $t_{RCD-R}$ .

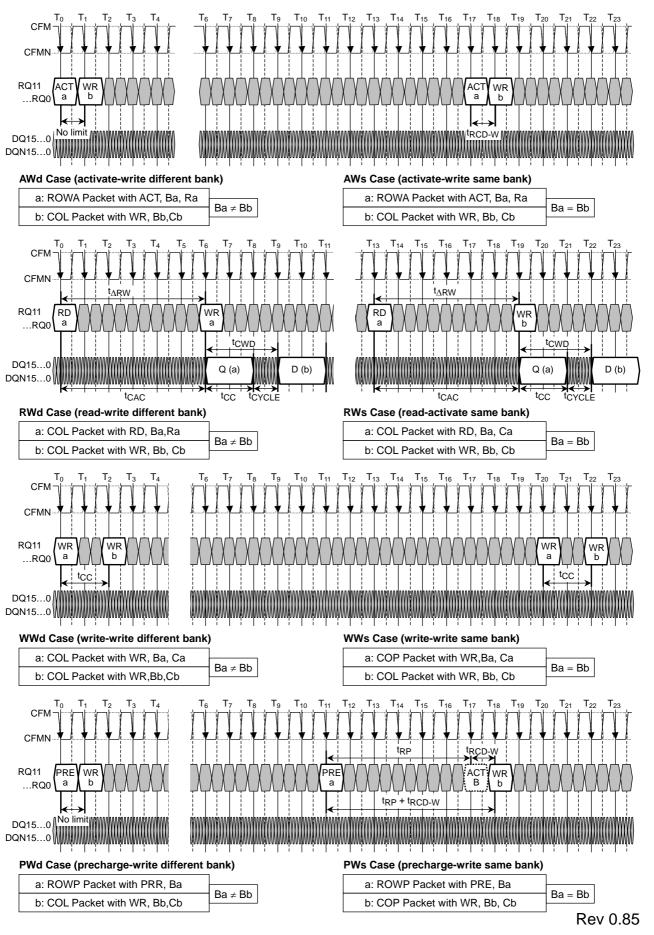

In Figure 6, the interaction interval for the AWs case is  $t_{RCD-W}$ . This is the row-to-column-write timing parameter and represents the minimum interval between an activate operation and a write operation to a bank.

The interaction interval for the RWd and RWs cases is  $t\Delta_{RW}$ . This is the read-to-write time parameter and represents the minimum interval between a read and a write operation to any banks. See "Read/Write Interaction" on page 28.

The interaction interval for the WWd and WWs cases is t<sub>CC</sub>. This is the column-to-column time parameter and represents the minimum interval between two write operations.

The interaction interval for the PWs case is  $t_{RP} + t_{RCD-W}$ . An activate operation must be inserted between the precharge and the write operation. The minimum interval between a precharge and an activate operation to a bank is  $t_{RCD-W}$ .

In Figure 7, the interaction interval for the APs case is  $t_{RAS}$ . This parameter is the minimum activate – to - precharge time to a bank.

The interaction intervals for the RPs and WPs cases are tRDP and tWRD, respectively. These are the read- or write-to-precharge time parameters to a bank.

The interaction interval for the PPd case is tpp. This parameter is the precharge-to-precharge time and the minimum interval between precharge commands to different banks of a device.

The interaction interval for the PPs case is  $t_{RC}$ . This is the row cycle time parameter and the minimum interval between precharge commands to same banks of a device. An activate operation must be inserted between the two activate operations. This activate operation must be placed a time  $t_{RAS}$  before the second precharge.

# Figure 4. ACT-, RD-, WR-, PRE-to-ACT Packet Interactions

Figure 5. ACT-, RD-, WR-, PRE-to-RD Packet Interactions

# Figure 6. ACT-, RD-, WR-, PRE-to-WR Packet Interactions

# Figure 7. ACT-, RD-, WR-, PRE-to-PRE Packet Interactions

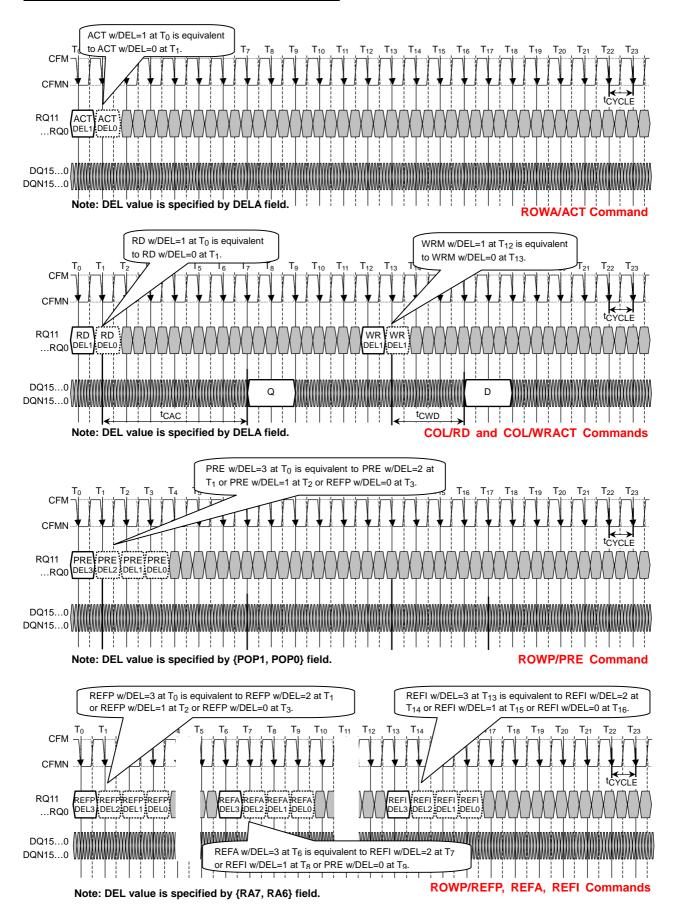

#### Dynamic Request Scheduling

Delay fields are present in the ROWA, COL, and ROWP packets. They permit the associated command to optionally wait for a time of one (or more) tcycle before taking effect. This allows a memory controller more scheduling flexibility when issuing request packets. Figure 8 illustrates the use of the delay fields.

In the first timing diagram, a ROWA packet with an ACT command is present at cycle T<sub>0</sub>. The DELA field is set to "1". This request packet will be equivalent to a ROWA packet with an ACT command at cycle T<sub>1</sub> with the DELA field is set to "0". This equivalence should be used when analyzing request packet interactions.

In the second timing diagram, a COL packet with a RD command is present at cycle  $T_0$ . The DELC field is set to "1". This request packet will be equivalent to a COL packet with an RD command at cycle  $T_1$  with the DELC field is set to "0". This equivalence should be used when analyzing request packet interactions.

In a similar fashion, a COL packet with a WR command is present at cycle  $T_{12}$ . The DELC field is set to "1". This request packet will be equivalent to a COL packet with a WR command at cycle  $T_{13}$  with the DELC field is set to "0". This equivalence should be used when analyzing request packet interactions.

In the COL packet with a RD command example, the read data delay.  $t_{CAC}$  is measured between the Q read data packet and the virtual COL packet at cycle  $T_1$ .

Likewise, for the example with the COL packet with a WR command, the write data delay.  $t_{CWD}$  is measured between the D write data packet and the virtual COL packet at cycle  $T_{13}$ .

In the third timing diagram, a ROWP packet with a PRE command is present at cycle T<sub>0</sub>. The DEL field (POP [1:0]) is set to "11". This request packet will be equivalent to a ROWP packet with a PRE command at cycle T<sub>1</sub> with the DEL field is set to "10", it will be equivalent to a ROWP packet with a PRE command at cycle T<sub>2</sub> with the DEL field is set to "01", and it will be equivalent to a ROWP packet with a PRE command at cycle T<sub>3</sub> with the DEL field is set to "00". This equivalence should be used when analyzing request packet interactions.

In the fourth timing diagram, a ROWP packet with a REFP command is present at cycle  $T_0$ . The DEL field (RA [7:6]) is set to "11". This request packet will be equivalent to a ROWP packet with a REFP command at cycle  $T_1$  with the DEL field is set to "10", it will be equivalent to a ROWP packet with a REFP command at cycle  $T_2$  with the DEL field is set to "01", and it will be equivalent to a ROWP packet with a REFP command at cycle  $T_3$  with the DEL field is set to "00". This equivalence should be used when analyzing request packet interactions.

The two examples for the REFA and REFI commands are identical to the example just described for the REFP command.

The ROWP packet allows two independent operations to be specified. A PRE precharge command uses the POP and BP fields, and the REFP, REFA, or REFI commands uses the ROP and RA fields. Both operations have an optional delay field (the POP field for the PRE command and the RA field with the REFP, REFA, or REFI commands). The two delay mechanisms are independent of one another. The POP field does not affect the timing of the REFP, REFA, or REFI commands, and the RA field does not affect the timing of the PRE command.

When the interactions of a ROWP packet are analyzed, it must be remembered that there are two independent commands specified, both of which may affect how soon the next request packet can be issued. The constraints from both commands in a ROWP packet must be considered, and the one that requires the longer time interval to the next request packet must be used by the memory controller. Furthermore, the two commands within a ROWP packet may not reference the same bank in the BP and RA fields.

# Figure 8. Request Scheduling Examples

# **Memory Operations**

#### Write Transactions

TOSHIBA

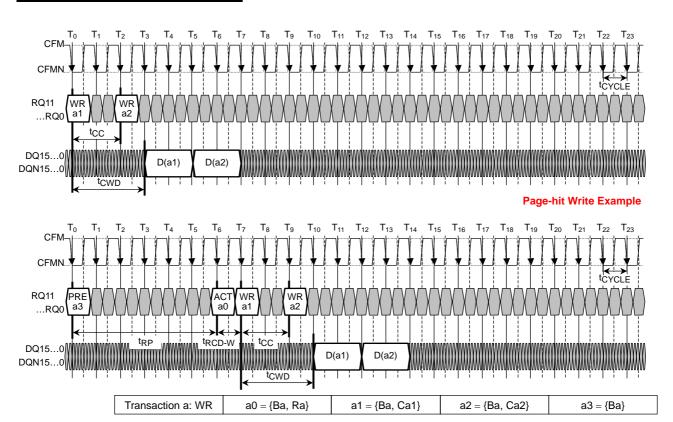

Figure 9 shows four examples of memory write transactions. A transaction is one or more request packets (and the associated data packets) needed to perform a memory access. The state of the memory core and the address of the memory access determine how many request packets are needed to perform the access.

The first timing diagram shows a page-hit write transaction. In this case, the selected bank is already open (a row is already present in the sense amp array for the bank). In addition, the selected row for the memory access matches the address of the row already sensed (a page hit). This comparison must be done in the memory controller. In this example, the access is made to row Ra of bank Ba.

In this case, write data may be directly written into the sense amp array for the bank, and row operations (activate or precharge) are not needed. A COL packet with WR command to column Ca1 of bank Ba is presented on edge  $T_0$ , and a second COL packet with WR command to column Ca2 of bank Ba is presented on edge  $T_2$ . Two write data packets D (a1) and D (a2) follow these COL packets after the write data delay tCWD. The two COL packets are separated by the column-cycle time  $t_{CC}$ . This is also the length of each write data packet.

The second timing diagram shows an example of a page-miss write transaction. In this case, the selected bank is already open (a row is already present in the sense amp array for the bank). However, the selected row for the memory access does not match the address of the row already sensed (a page miss). This comparison must be done in the memory controller. In this example, the access is made to row Ra of bank Ba, and the bank contains a row other than Ra.

In this case, write data may not be directly written into the sense amp array for the bank. It is necessary to close the present row (precharge) and access the requested row (activate). A precharge command (PRE to bank Ba) is presented on edge  $T_0$ . An activate command (ACT to row Ra of bank Ba) is presented on edge  $T_0$  a time  $t_{RCD-W}$  later. A COL packet with WR command to column Ca1 of bank Ba is presented on edge  $T_0$  a time  $t_{RCD-W}$  later. A second COL packet with WR command to column Ca2 of bank Ba is presented on edge  $T_0$ . Two write data packets D (a1) and D (a2) follow these COL packets after the write data delay  $t_{CWD}$ . The two COL packets are separated by the column-cycle time  $t_{CC}$ . This is also the length of each write data packet.

The third timing diagram shows an example of a page-empty write transaction. In this case, the selected bank is already closed (no row is present in the sense amp array for the bank). No row comparison is necessary for this case; however, the memory controller must still remember that bank Ba has been left closed. In this example, the access is made to row Ra of bank Ba.

In this case, write data may not be directly written into the sense amp array for the bank. It is necessary to access the requested row (activate). An activate command (ACT to row Ra of bank Ba) is presented on edge  $T_0$ . A COL packet with WR command to column Ca1 of bank Ba is presented on edge  $T_1$  a time  $t_{RCD-W}$  later. A second COL packet with WR command to column Ca2 of bank Ba is presented on edge  $T_3$ . Two write data packets D (a1) and D (a2) follow these COL packets after the write data delay  $t_{CWD}$ . The two COL packets are separated by the column-cycle time  $t_{CC}$ . This is also the length of each write data packet. After the final write command, it may be necessary to close the present row (precharge). A precharge command (PRE to bank Ba) is presented on edge  $T_{14}$  a time  $t_{WRP}$  after the last COL packet with a WR command. The decision whether to close the bank or leave it open is made by the memory controller and its page policy.

The fourth timing diagram shows another example of a page–empty write transaction. This is similar to the previous example except that only a single write command is presented, rather than two write commands. This example shows that even with a minimum length write transaction, the transaction will not be a constraint. The transactions the minimum time between an activate command and a precharge command to a bank. This time interval is also constrained by the sum transaction will be larger for a write transaction. These two constraints (transaction) will be a function of the memory device's speed bin and the data transfer length (the number of write commands issued between the activate and precharge commands), and the transaction parameter could become a constraint for write transactions for future speed bins. In this example, the sum transaction transactions for future speed bins. In this example, the sum transactions transactions for future speed bins.

# Figure 9. Write Transactions

#### Page-miss Write Example

#### **Page-empty Write Example**

Page-empty Write Example - Core Limited

#### **Read Transactions**

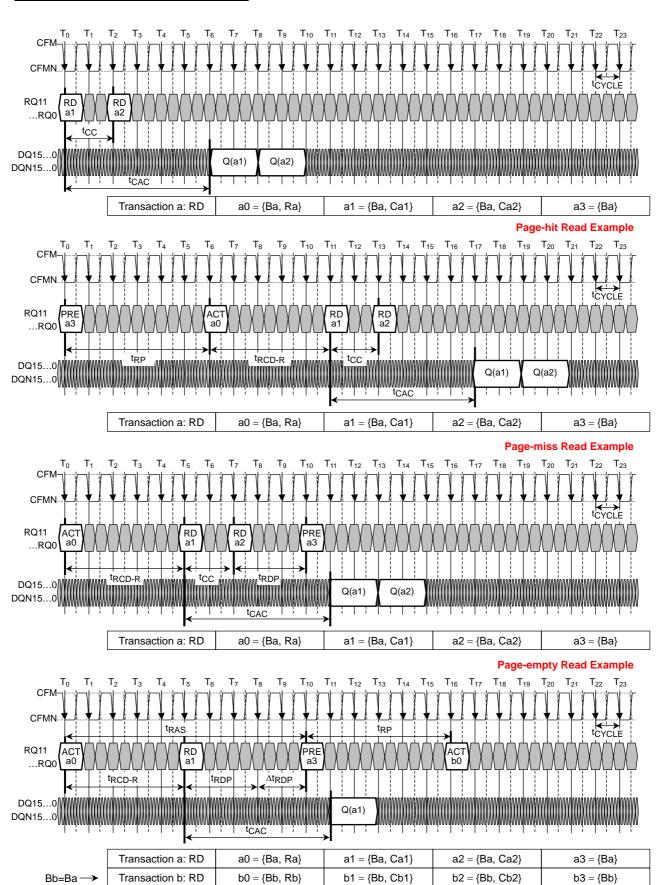

Figure 10 shows four examples of memory read transactions. A transaction is one or more request packets (and the associated data packets) needed to perform a memory access. The state of the memory core and the address of the memory access determine how many request packets are needed to perform the access.

The first timing diagram shows a page-hit read transaction. In this case, the selected bank is already open (a row is already present in the sense amp array for the bank). In addition, the selected row for the memory access matches the address of the row already sensed (a page hit). This comparison must be done in the memory controller. In this example, the access is made to row Ra of bank Ba.

In this case, read data may be directly read from the sense amp array for the bank, and no row operations (activate or precharge) are needed. A COL packet with RD command to column Ca1 of bank Ba is presented on edge  $T_0$ , and a second COL packet with RD command to column Ca2 of bank Ba is presented on edge  $T_2$ . Two read data packets Q (a1) and Q (a2) follow these COL packets after the read data delay tCAC. The two COL packets are separated by the column-cycle time tCC. This is also the length of each read data packet.

The second timing diagram shows an example of a page-miss read transaction. In this case, the selected bank is already open (a row is already present in the sense amp array for the bank). However, the selected row for the memory access does not match the address of the row already sensed (a page miss). This comparison must be done in the memory controller. In this example, the access is made to row Ra of bank Ba, and the bank contains a row other than Ra.

In this case, read data may not be directly read from the sense amp array for the bank. It is necessary to close the present row (precharge) and access the requested row (activate). A precharge command (PRE to bank Ba) is presented on edge  $T_0$ . An activate command (ACT to row Ra of bank Ba) is presented on edge  $T_0$  a time  $t_{RCD-R}$  later. A COL packet with RD command to column Ca1 of bank Ba is presented on edge  $T_{11}$  a time  $t_{RCD-R}$  later. A second COL packet with RD command to column Ca2 of bank Ba is presented on edge  $T_{13}$ . Two read data packets  $Q_0$  and  $Q_0$  follow these COL packets after the read data delay  $t_{CAC}$ . The two COL packets are separated by the column-cycle time  $t_{CC}$ . This is also the length of each read data packet.

The third timing diagram shows an example of a page-empty write transaction. In this case, the selected bank is already closed (no row is present in the sense amp array for the bank). No row comparison is necessary for this case; however, the memory controller must still remember that bank Ba has been left closed. In this example, the access is made to row Ra of bank Ba.

In this case, read data may not be directly read from the sense amp array for the bank. It is necessary to access the requested row (activate). An activate command (ACT to row Ra of bank Ba) is presented on edge  $T_0$ . A COL packet with RD command to column Ca1 of bank Ba is presented on edge  $T_0$  a time  $t_{RCD-R}$  later. A second COL packet with RD command to column Ca2 of bank Ba is presented on edge  $T_0$ . Two read data packets Q (a1) and Q (a2) follow these COL packets after the read data delay  $t_{CAC}$ . The two COL packets are separated by the column-cycle time  $t_{CC}$ . This is also the length of each read data packet. After the final read command, it may be necessary to close the present row (precharge). A precharge command — PRE to bank Ba — is presented on edge  $t_{T0}$  a time  $t_{RDP}$  after the last COL packet with a RD command. Whether the bank is closed or left open depends on the memory controller and its page policy.

The fourth timing diagram shows another example of a page-empty read transaction. This is similar to the previous example except that it uses one read command instead of two read commands. In this case, the core parameter transmit may also be a constraint upon when the precharge command may be issued.

The  $t_{RAS}$  measures the minimum time between an activate command and a precharge command to a bank. This time interval is also constrained by the sum  $t_{RCD-R} + t_{RDP}$  and must be set to whichever is larger. These two constraints ( $t_{RAS}$  and  $t_{RCD-R} + t_{RDP}$ ) will be a function of the memory device's speed bin and the data transfer length (the number of read commands issued between the activate and precharge commands). In this example, the  $t_{RAS}$  is greater than the sum  $t_{RCD-R} + t_{RDP}$  by the amount  $\Delta t_{RDP}$ .

# Figure 10. Read Transactions

Page-empty Read Example - Core Limited

#### **Interleaved Transactions**

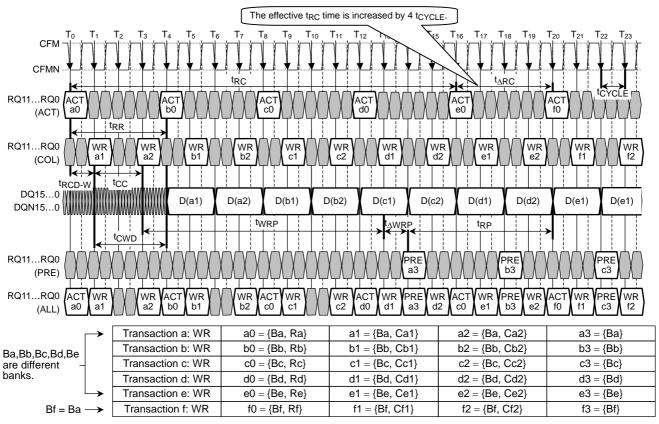

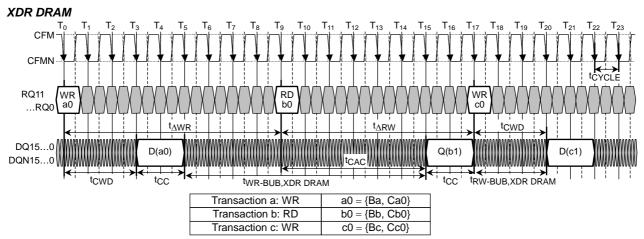

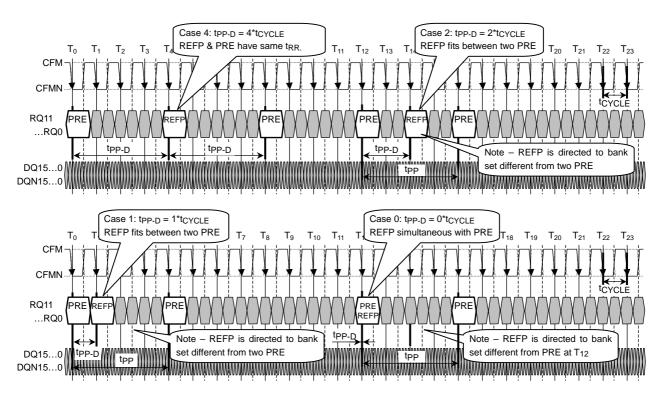

Figure 11 shows two examples of interleaved transactions. Interleaved transactions are overlapped with one another; a transaction is started before an earlier one is completed.

The timing diagram at the top of the figure shows interleaved write transactions. Each transaction assumes a page-empty access; that is, a bank is in a closed state prior to an access, and is precharged after the access. With this assumption, each transaction requires the same number of request packets at the same relative positions. If banks were allowed to be in an open state, then each transaction would require a different number of request packets depending upon whether the transaction was page-empty, page-hit, or page-miss. This situation is more complicated for the memory controller, and will not be analyzed in this document.

In the interleaved page-empty write example, there are four sets of request pins RQ11...RQ0 shown along the left side of the timing diagram. The first three show the timing slots used by each of the three requests packet types (ACT, COL and PRE), and the fourth set (ALL) shows the previous three merged together. This allows the pattern used for allocating request slots for the different packets to be seen more clearly.

The slots at  $\{T_0, T_4, T_8, T_{12}, ...\}$  are used for ROWA packets with ACT commands. This spacing is determined by the tRR parameter. There should not be interference between the interleaved transactions due to resource conflicts because each bank address — Ba, Bb, Bc, Bd, and Be — is assumed to be different from another. If two of the bank addresses are the same, the later transaction would need to wait until the earlier transaction had completed its precharge operation. Five different banks are needed because the effective tRC (tRC +  $\Delta$ tRC) is 20 × tCYCLE.

The slots at  $\{T_1, T_3, T_5, T_7, T_9, T_{11}, ...\}$  are used for COL packets with WR commands. This frequency of the COL packet spacing is determined by the t<sub>CC</sub> parameter and by the fact that there are two column accesses per row access. The phasing of the COL packet spacing is determined by the t<sub>RCD-W</sub> parameter. If the value of t<sub>RCD-W</sub> required the COL packets to occupy the same request slots as the ROWA packets (this case is not shown), the DELC field in the COL packet could be used to place the COL packet one t<sub>CYCLE</sub> earlier.

The DQ bus slots at  $\{T7, T9, T11, T13, ...\}$  carry the write data packets  $\{D(a1), D(a2), D(b1), D(b2), ....\}$ . Two write data packets are written to a bank in each transaction. The DQ bus is completely filled with write data; no idle cycles need to be introduced because there are no resource conflicts in this example.

The slots at  $\{T_{14}, T_{18}, T_{22}, ...\}$  are used for ROWP packets with PRE commands. This frequency of ROWP packet spacing is determined by the tpp parameter. The phasing of the ROWP packet spacing is determined by the twrp parameter. If the value of twrp required the ROWP packets to occupy the same request slots as the ROWA or COL packets already assigned (this case is not shown), the delay field in the ROWP packet could be used to place the ROWP packet one or more tcycle earlier.

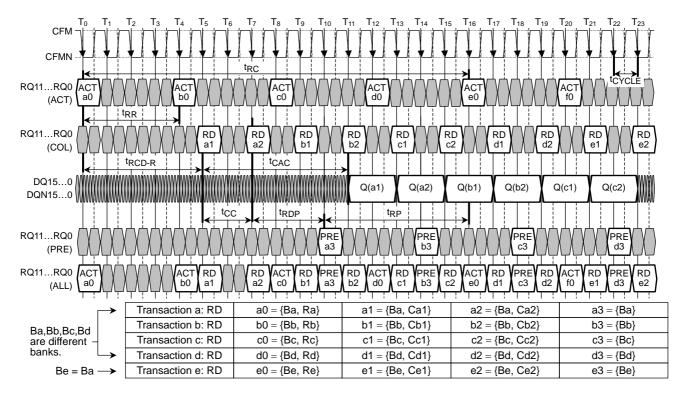

There is an example of an interleaved page-empty read at the bottom of the figure. As before, there are four sets of request pins RQ11...RQ0 shown along the left side of the timing diagram, allowing the pattern used for allocating request slots for the different packets to be seen more clearly.

The slots at  $\{T_0, T_4, T_8, T_{12}, ...\}$  are used for ROWA packets with ACT commands. This spacing is determined by the  $t_{RR}$  parameter. There should not be interference between the interleaved transactions due to resource conflicts because each bank address — Ba, Bb, Bc, and Bd — is assumed to be different from another. Four different banks are needed because the effective  $t_{RC}$  is  $16 \times t_{CYCLE}$ .

The slots at  $\{T_5, T_7, T_9, T_{11}, ...\}$  are used for COL packets with RD commands. This frequency of the COL packet spacing is determined by the  $t_{CC}$  parameter and by the fact that there are two column accesses per row access. The phasing of the COL packet spacing is determined by the  $t_{RCD-R}$  parameter. If the value of  $t_{RCD-R}$  required the COL packets to occupy the same request slots as the ROWA packets (this case is not shown), the DELC field in the COL packet could be used to place the packet one  $t_{CYCLE}$  earlier.

The DQ bus slots at  $\{T_{11}, T_{13}, T_{15}, T_{17}, ...\}$  carry the read data packets  $\{Q(a1), Q(a2), Q(b1), Q(b2), ...\}$ . Two read data packets are read from a bank in each transaction. The DQ bus is completely filled with read data — that is, no idle cycles need to be introduced because there are no resource conflicts in this example.

The slots at  $\{T_{10}, T_{14}, T_{18}, T_{22}, ...\}$  are used for ROWP packets with PRE commands. This frequency of the ROWP packet spacing is determined by the tpp parameter. The phasing of the ROWP packet spacing is determined by the tpp parameter. If the value of tpp required the ROWP packets to occupy the same request slots as the ROWA or COL packets already assigned (this case is not shown), the delay field in the ROWP packet could be used to place the ROWP packet one or more tcycle earlier.

Figure 11. Interleaved Transactions

Interleaved Page-empty Write Example

Interleaved Page-empty Read Example

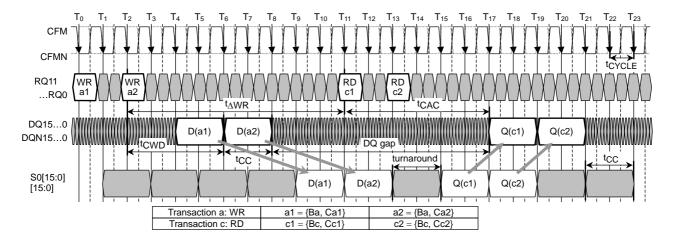

#### Read/Write Interaction

The previous section described overlapped read transactions and overlapped write transactions in isolation. This section will describe the interaction of read and write transactions and the spacing required to avoid channel and core resource conflicts.

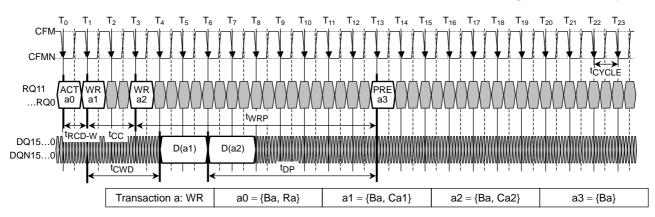

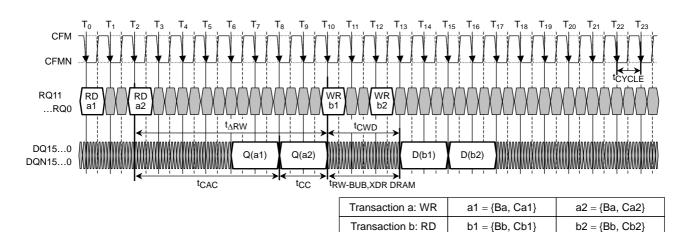

Figure 12 shows a timing diagram (top) for the first case, a write transaction followed by a read transaction. Two COL packets with WR commands are presented on cycles  $T_0$  and  $T_2$ . The write data packets are presented a time  $t_{CWD}$  later on cycles  $T_4$  and  $T_6$ . The device requires a time  $t_{\Delta WR}$  after the second COL packet with a WR command before a COL packet with a RD command may be presented. Two COL packets with RD commands are presented on cycles  $T_{11}$  and  $T_{13}$ . The read data packets are returned a time  $t_{CAC}$  later on cycles  $T_{17}$  and  $T_{19}$ . The time  $t_{\Delta WR}$  is required for turning around internal bi-directional interconnections (inside the device). This time must be observed regardless of whether the write and read commands are directed to the same bank or different banks. A gap  $t_{WR-BUB}$ ,  $t_{XDR}$  different banks and  $t_{YR-BUB}$ ,  $t_{YR-BUB$

```

tWR-BUB,XDRDRAM = t_{\Delta}WR + tCAC - tCWD - tCC

```

In this example, the value of twr-bub, xdr dram is greater than its minimum value of twr-bub, xdr dram, min. The values of  $t_{\Delta}$ Wr and  $t_{CAC}$  are equal to their minimum values.

In the second case, the timing diagram displayed at the bottom of Figure 12 illustrates a read transaction followed by a write transaction. Two COL packets with RD commands are presented on cycles  $T_0$  and  $T_2$ . The read data packets are returned a time  $t_{CAC}$  later on cycles  $T_0$  and  $T_0$ . The device requires a time  $t_{ARW}$  after the second COL packet with a RD command before a COL packet with a WR command may be presented. Two COL packets with WR commands are presented on cycles  $T_{10}$  and  $T_{12}$ . The write data packets are presented a time  $t_{CWD}$  later on cycles  $T_{13}$  and  $T_{15}$ . The time  $t_{ARW}$  is required for turning around the external DQ bi-directional interconnections (outside the device). This time must be observed regardless whether the read and write commands are directed to the same bank or different banks. The time  $t_{ARW}$  depends upon four timing parameters, and may be evaluated by calculating the difference between cycles  $T_2$  and  $T_{13}$  using the two timing paths:

```

t_{\Delta RW} + t_{CWD} = t_{CAC} + t_{CC} + t_{RW-BUB,XDRDRAM} or t_{\Delta RW} = (t_{CAC} - t_{CWD}) + t_{CC} + t_{RW-BUB,XDRDRAM}

```

In this example, the values of  $t_{\Delta}RW$ ,  $t_{CAC}$ ,  $t_{CWD}$ ,  $t_{CC}$ , and  $t_{RW-BUB,XDR}$  DRAM are equal to their minimum values.

# Figure 12. Write/Read Interaction

Write/Read Turnaround Example

Read/Write Turnaround Example

# **Propagation Delay**

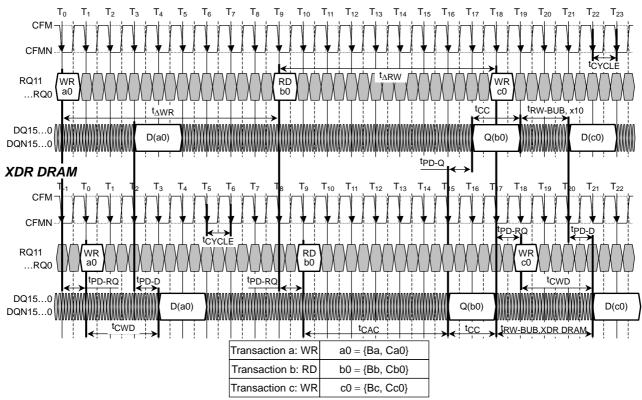

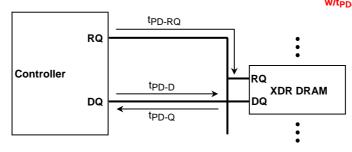

Figure 13 shows two timing diagrams that display the system-level timing relationships between the memory component and the memory controller.

The timing diagram at the top of the figure shows the case of a write-read-write command and data at the memory component. In this case, the timing will be identical to what has already been shown in the previous sections; i.e. with all timing measured at the pins of the memory component. This timing diagram was produced by merging portions of the top and bottom timing diagrams in Figure 12.

The example shown is that of a single COL packet with a write command, followed by a single COL packet with a read command, followed by a second COL packet with a write command. These accesses all assume a page-hit to an open bank.