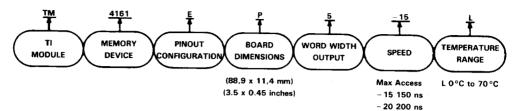

# TM4161EP5 65.536 BY 5-BIT MULTIPORT VIDEO RAM MODULE

P SINGLE-IN-LINE PACKAGE

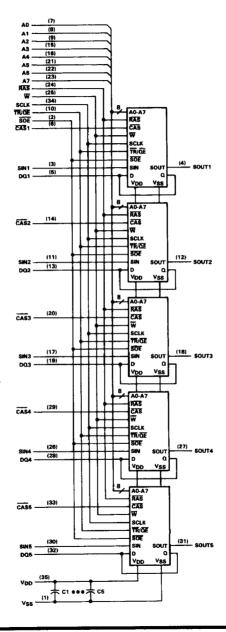

(TOP VIEW)

JULY 1984 - REVISED NOVEMBER 1985

- 65,536 X 5 Organization

- Single 5-V Supply (10% Tolerance)

- 35-Pin Single-in-Line Package (SIP)

- Utilizes Five Multiport Video RAMs in Plastic Chip Carriers

- Serial In/Serial Out Capability

- Dual Accessibility One Port Sequential Access, One Port Random Access

- Five Serial Shift Registers for Sequential Access Applications, Each Comprised of Four Cascaded 64-Bit Segments

- Designed for both Video and Non-Video Applications

- Fast Serial Port . . . Can Be Configured for Video Data Rates in Excess of 150 MHz

- TR/QE as Output Enable Allows Direct Connection of DQ and Address Lines to Simplify System Design

- Separate Serial In and Serial Out to Allow Simultaneous Shift In and Out

- Supported by TI's TMS34061 Video System Controller (VSC)

- SOE Simplifies Multiplexing of Serial Data Streams

- Long Refresh Period . . . 4 ms (256 Cycles)

- All Inputs, Outputs, Clocks Fully TTL Compatible

- 3-State Outputs

- Performance Ranges:

|              | _              |                |            |

|--------------|----------------|----------------|------------|

|              | ACCESS<br>TIME | ACCESS<br>TIME | READ<br>OR |

|              | ROW            | COLUMN         | WRITE      |

|              | ADDRESS        | ADDRESS        | CYCLE      |

|              | (MAX)          | (MAX)          | (MIN)      |

| TM4161EP5-15 | 150 ns         | 100 ns         | 240 ns     |

| TM4161EP5-20 | 200 ns         | 135 ns         | 315 ns     |

- Separate CAS Control with Common Data-In and Data-Out Lines

- Low Power Dissipation:

- -Operating . . . 1250 mW (Typ)

- -Standby . . . 400 mW (Typ)

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Operating Free-Air Temperature . . . 0 °C to 70 °C

| V <sub>SS</sub><br>SOE    | (1)                            | 1             |

|---------------------------|--------------------------------|---------------|

| SIN1                      | (3)                            |               |

| SOUT1                     | (4)                            |               |

| 50011<br>DQ1              | (5)                            |               |

| CAS1                      | (6)                            |               |

| AO                        |                                | -             |

| A1                        | (8)                            |               |

| A2                        | (9)                            |               |

| TR/QE                     | (10)                           |               |

| SIN2                      | (11)                           | 1             |

| SOUT2                     | (12)                           |               |

| DQ2                       | (13)                           | $\Box$        |

| CAS2                      | (14)                           |               |

| A3                        | (15)                           | ᆜ             |

| A4                        | $(16) \longrightarrow \square$ | [ ]           |

| SIN3                      | (17)                           | 1             |

| SOUT3                     | (18)                           | ļ             |

| DQ3                       | (19)                           | لما           |

| CAS3<br>A5                | (20)                           | $\overline{}$ |

| A6                        | (22)                           |               |

| A7                        | (23)                           |               |

| RAS                       | (24)                           |               |

| $\overline{\overline{w}}$ | (25)                           |               |

| SIN4                      | (26)                           | ا ا           |

| SOUT4                     | (27)                           |               |

| DQ4                       | (28)                           | u             |

| CAS4                      | (29)                           | $\overline{}$ |

| SIN5                      | (30)                           |               |

| SOUT5                     | (31)                           | 1 1           |

| <u>DQ</u> 5               | (32)                           |               |

| CAS5                      | (33)                           | $\prod$       |

| SCLK                      | (34)                           |               |

| $V_{DD}$                  | (35)                           |               |

|                           |                                |               |

| PII         | NOMENCLATURE                      |

|-------------|-----------------------------------|

| A0-A7       | Address Inputs                    |

| CAS1-CAS5   | Column-Address Strobes            |

| DQ1-DQ5     | Random-Access Data In/Data Out    |

| RAS         | Row-Address Strobe                |

| SCLK        | Serial Data Clock                 |

| SIN1-SIN5   | Serial Data In                    |

| SOE         | Serial Output Enable              |

| SOUT1-SOUT5 | Serial Data Out                   |

| TR/QE       | Register Transfer/Q Output Enable |

| VDD         | 5-V Supply                        |

| Vss         | Ground                            |

| w           | Write Enable                      |

# description

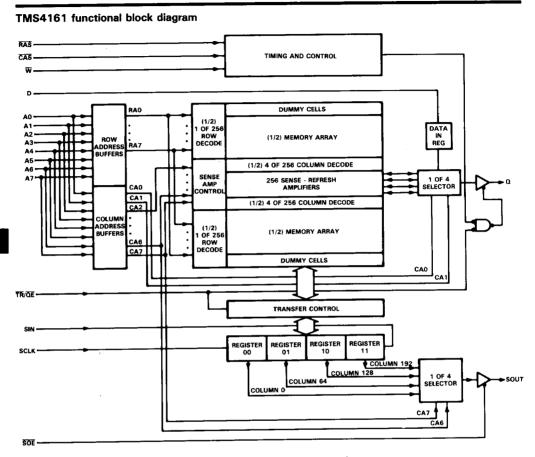

The TM4161EP5 is a 320K dual-access dynamic random-access memory module organized as 65,536 imes 5-bits in a 35-pin single-in-line package comprising five TMS4161FML, 65,536 imes 1-bit Multiport Video RAMs in 22-lead plastic chip carriers mounted on top of a substrate together with five decoupling capacitors. The random-access port makes the module look like it is organized as 65,536 words of five bits each. The sequential-access port is interfaced to five internal 256-bit dynamic shift registers each organized as four cascaded 64-bit shift register segments which are accessed serially. One, two, three, or four 64-bit shift register segments can be sequentially read out after a transfer cycle depending on a two-bit code applied to the two most significant column address inputs.

The TM4161EP5 features full asynchronous dual access capability except when transferring data between the shift registers and the memory array.

Refresh period is extended to 4 milliseconds, and during this period each of the 256 rows must be strobed with RAS in order to retain data. CAS can remain high during the refresh sequence to conserve power. Note that the transfer of a row of data from the memory array to the shift registers also refreshes that row.

All inputs and outputs, including clocks, are compatible with Series 74 TTL. All address lines and data in are latched on chip to simplify system design. Data out is unlatched to allow greater system flexibility.

The TM4161EP5 is guaranteed for operation from 0°C to 70°C.

# functional block diagram

# random-access address space to sequential address space mapping

The TM4161EP5 is designed with each row divided into four, 64-column sections which map directly onto the four segments of each shift register (see TMS4161 functional block diagram). The first column section to be shifted out is selected by the two most-significant column-address bits. If the two bits represent binary 00, then one to four register segments can be shifted out in order. If the two bits represent binary 01, then only 1 to 3 (the most significant) register segments can be shifted out in order. If the two bits represent 10, then one to two of the most-significant register segments can be shifted out in order. Finally, if the two bits represent 11 only the most-significant register segment can be shifted out. All register segments are shifted out with the least-significant bit (bit 0) first and the most-significant bit (bit 63) last. Note that if the two column-address bits equal 00 during the last register transfer cycle (TR/QE at logic level "O" as RAS falls) a total of 256 bits can be sequentially read out of each serial output pin.

# 1M4161EP5 65,536 BY 5-BIT MULTIPORT VIDEO RAM MODULE

# random-access operation

## TR/QE

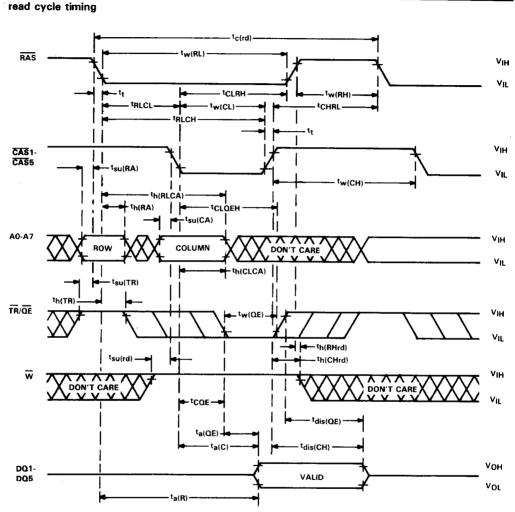

The  $\overline{TR}/\overline{QE}$  pin has two functions. First, it selects either register transfer or random-access operation as  $\overline{RAS}$  falls, and second, during a random-access operation, it functions as an output enable after  $\overline{CAS}$  falls.

To use the TM4161EP5 in the random-access mode,  $\overline{TR}/\overline{QE}$  must be high as  $\overline{RAS}$  falls. Holding  $\overline{TR}/\overline{QE}$  high as  $\overline{RAS}$  falls keeps the 256 elements of the shift registers disconnected from the corresponding 256 bit lines of the memory array. If data is to be shifted, the shift registers must be disconnected from the bit lines. Holding  $\overline{TR}/\overline{QE}$  low as  $\overline{RAS}$  falls enables the 256 switches that connect the shift registers to the bit lines and indicates that a transfer will occur between the shift registers and one of the memory rows.

During random-access operation, once  $\overline{CAS}$  has been pulled low,  $\overline{TR}/\overline{QE}$  controls when the data will appear at the Q output (if this is a read cycle). Whenever  $\overline{TR}/\overline{QE}$  is held high during random-access operation, the Q output will be in the high-impedance state. This feature removes the possibility of an overlap between data on the address lines and data appearing on the Q output making it possible to connect the address lines to the Q and D lines (Use of this organization prohibits the use of the early write cycle.).

# address (A0 through A7)

Sixteen address bits are required to decode 1 of 65,536 storage cell locations. Eight row-address bits are set up on pins A0 through A7 and latched onto the chip by the row-address strobe (RAS). Then the eight column-address bits are set up on pins A0 through A7 and latched onto the chip by the column-address strobe (CAS). All addresses must be stable on or before the falling edges of RAS and CAS. RAS is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder. CAS is used as a chip select activating the column decoder and the input and outputs buffers.

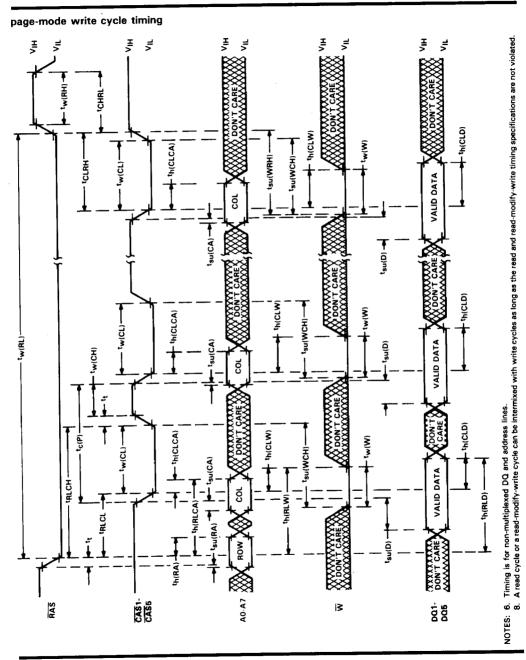

### write enable (W)

The read or write mode is selected through the write-enable  $\{\overline{W}\}$  input. A logic high on the  $\overline{W}$  input selects the read mode and a logic low selects the write mode. The write-enable terminal can be driven from standard TTL circuits without a pull-up resistor. The data inputs are disabled when the read mode is selected. The common I/O feature of the TM4161EP5 dictates the use of early write cycles to prevent contention on DQ. When  $\overline{W}$  goes low prior to  $\overline{CAS}$ , the data outputs will remain in the high-impedance state for the entire cycle permitting common I/O operation.

# data in (DQ1-DQ5)

Data is written during a write or read-modify-write cycle. The falling edge of  $\overline{\text{CAS}}$  or  $\overline{\text{W}}$  strobes data into the on-chip data latch. This latch can be driven from standard TTL circuits without a pull-up resistor. In an early write cycle,  $\overline{\text{W}}$  is brought low prior to  $\overline{\text{CAS}}$  and the data is strobed in by  $\overline{\text{CAS}}$  with setup and hold times referenced to this signal.

## data out (DQ1-DQ5)

The three-state output buffer provides direct TTL compatibility (no pull-up resistor required) with a fan out of two Series 74 TTL loads. Data out is the same polarity as data in. The output is in the high-impedance (floating) state as long as  $\overline{CAS}$  or  $\overline{TR}/\overline{QE}$  is held high. Data will not appear on the output until after both  $\overline{CAS}$  and  $\overline{TR}/\overline{QE}$  have been brought low. In a read cycle, the guaranteed maximum output enable access time is valid only if tCQE is greater than tCQE MAX, and tRLCL is greater than tRLCL MAX. Likewise, ta(C) MAX is valid only if tRLCL is greater than tRLCL MAX. Once the output is valid, it will remain valid while  $\overline{CAS}$  and  $\overline{TR}/\overline{QE}$  are both low;  $\overline{CAS}$  or  $\overline{TR}/\overline{QE}$  going high will return the output to a high-impedance state. In an early write cycle, the output is always in a high-impedance state. In a register transfer cycle, the output will always be in a high-impedance state.

5

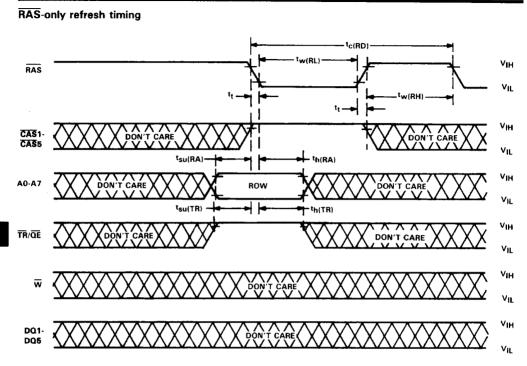

# refresh

A refresh operation must be performed at least every four milliseconds to retain data. Since the output buffer is in high-impedance state unless  $\overline{CAS}$  is applied, the  $\overline{RAS}$ -only refresh sequence avoids any output during refresh. Strobing each of the 256 row addresses (A0 through A7) with  $\overline{RAS}$  causes all bits in each row to be refreshed. CAS can remain high (inactive) for this refresh sequence to conserve power.

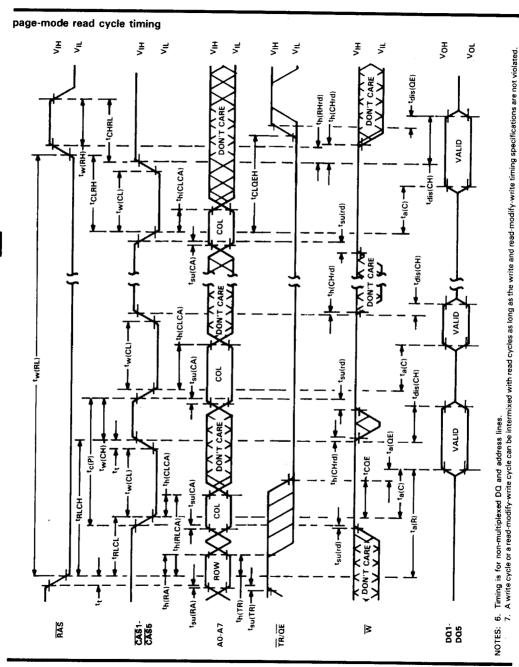

#### page mode

Page-mode operation allows effectively faster memory access by keeping the same row address and strobing successive column addresses onto the module. Thus, the time required to setup and strobe sequential row addresses for the same page is eliminated. To extend beyond the 256 column locations on M1-M5, the row address and RAS are applied to multiple modules. CAS is then decoded to select the proper module.

#### power up

After power up, the power supply must remain at its steady-state value for 1 ms. In addition,  $\overline{RAS}$  must remain high for 100  $\mu$ s immediately prior to initialization. Initialization consists of performing eight  $\overline{RAS}$  cycles before proper device operation is achieved.

### sequential-access operation

### TR/QE

Memory transfer operations involving parallel use of the shift registers are first indicated by bringing  $\overline{TR}/\overline{QE}$  low before  $\overline{RAS}$  falls low. This enables the switches connecting the 256 elements of the shift registers to the 256 bit lines of the memory array. The  $\overline{W}$  line determines whether the data will be transferred from or to the shift registers.

#### write enable (W)

In the sequential-access mode,  $\overline{W}$  determines whether a transfer will occur from the shift registers to the memory array, or from the memory array to the shift registers. To transfer from the shift registers to the memory array,  $\overline{W}$  is held low as  $\overline{RAS}$  falls, and, to transfer from the memory array to the shift registers,  $\overline{W}$  is held high as  $\overline{RAS}$  falls. Thus, reads and writes are always with respect to the memory array. The write setup and hold times are referenced to the falling edge of  $\overline{RAS}$  for this mode of operation.

#### row address (A0 through A7)

Eight address bits are required to select one of the 256 possible rows involved in the transfer of data to or from the shift registers. A0-A7,  $\overline{W}$ , and  $\overline{TR}/\overline{QE}$  are latched on the falling edge of  $\overline{RAS}$ .

## register column address (A7, A6)

To select one of the four shift register segments within each shift register (transfer from memory to register only), the appropriate 2-bit column address (A7, A6) must be valid when  $\overline{CAS}$  falls. However, the  $\overline{CAS}$  and segment address signals need not be supplied every transfer cycle, only when it is desired to change or select a new segment.

#### **SCLK**

Data is shifted in and out on the rising edge of SCLK. This makes it possible to view each shift register as though it were made of 256 rising edge D flip-flops connected D to Q. The TM4161EP5 is designed to work with a wide range duty cycle clock to simplify system design. Note that data will appear at the SOUT pins not only on the rising edge of SCLK but also after an access time of ta(RSO) from RAS high during a parallel load of the shift registers.

#### SIN and SOUT

Data is shifted in through the SIN pins and is shifted out through the SOUT pins. The TM4161EP5 is designed such that it requires 3 ns hold time on SIN as SCLK rises. SOUT is guaranteed not to change for at least

# TM4161EP5 65.536 BY 5-BIT MULTIPORT VIDEO RAM MODULE

8 ns after SCLK rises. When loading data into the shift registers from the serial inputs in preparation for a shift register to memory transfer operation, the serial clock must be clocked an even number of times. To guarantee proper serial clock sequence after power up, a transfer cycle must be initiated before a serial data stream is applied at SIN.

#### SOF

The serial output enable pin controls the impedance of the serial outputs, allowing multiplexing of more than one bank of TM4161EP5 memories into the same external video circuitry. When  $\overline{SOE}$  is at a logic low level, the SOUTs will be enabled and the proper data read out. When  $\overline{SOE}$  is at a logic high level, the SOUTs will be disabled and be in the high-impedance state.

#### refresh

The shift registers are also dynamic storage elements. The data held in the registers will be lost unless SCLK goes high to shift the data one bit position, a transfer write operation is invoked, or the data is reloaded from the memory array. See specifications for maximum register data retention times. Important: If the shift registers have remained idle for a time period which exceeds the maximum SCLK high or SCLK low time, the dynamic clock circuits will lose charge. Under these conditions, the shift register clocks must be re-enabled by performing any transfer cycle before data can be shifted into or out of the shift registers.

### single-in-line package and components

PC substrate: 0,79 mm (0.031 inch) minimum thickness

Bypass capacitors: Multilayer ceramic

Leads: Tin/lead solder coated over phosphor-bronze

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Voltage range on any pin except VDD and data out (see Note 1) | -1.5 V to 10 V |

|---------------------------------------------------------------|----------------|

| Voltage range on VDD supply and data out with respect to VSS  | $-1$ V to 6 V  |

| Short circuit output current                                  | 50 mA          |

| Power dissipation                                             |                |

| Operating free-air temperature range                          | 0°C to 70°C    |

| Storage temperature range                                     | -65°C to 150°C |

<sup>†</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values in this data sheet are with respect to VSS.

## recommended operating conditions

| -               |                                             | MIN  | NOM | MAX                 | UNIT |

|-----------------|---------------------------------------------|------|-----|---------------------|------|

| V <sub>DD</sub> | Supply voltage                              | 4.5  | 5   | 5.5                 | ٧    |

| VSS             | Supply voltage                              |      | 0   |                     | V    |

| VIH             | High-level input voltage                    | 2.4  |     | V <sub>DD+0.3</sub> | V    |

| VIL             | Low-level input voltage (see Notes 2 and 3) | -0.6 |     | 0.8                 | V    |

| TA              | Operating free-air temperature              | 0    |     | 70                  | °C   |

- NOTES: 2. The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

- Due to input protection circuitry, the applied voltage may begin to clamp at -0.6 V; test conditions must comprehend this

occurrence.

- 4. See application report entitled "TMS4164A and TMS4416 Input Protection Diode" on page 9-5.

# electrical characteristics over full range of recommended operating conditions (unless otherwise noted)

|                   | PARAMETER                                                   | TEST CONDITIONS                                                                                                                                                                                                                                                        | TM4161EP5-15 |                  | TM   | 4161EP | 5-20             | UNIT |      |

|-------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|------|--------|------------------|------|------|

|                   | TAIGHETEN                                                   | Test delibritions                                                                                                                                                                                                                                                      | MIN          | TYP <sup>†</sup> | MAX  | MIN    | TYP <sup>†</sup> | MAX  | UNII |

| ∨он               | High-level output voltage (DQ1-DQ5, SOUT1-SOUT5)            | I <sub>OH</sub> = -5 mA                                                                                                                                                                                                                                                | 2.4          |                  |      | 2.4    |                  | ٠    | ٧    |

| VOL               | Low-level output voltage (DQ1-DQ5, SOUT1-SOUT5)             | I <sub>OL</sub> = 4.2 mA                                                                                                                                                                                                                                               |              |                  | 0.4  |        |                  | 0.4  | ٧    |

| ΙĮ                | Input current (leakage)                                     | V <sub>I</sub> = 0 V to 5.8 V,<br>V <sub>DD</sub> = 5 V,<br>All other pins = 0 V                                                                                                                                                                                       |              |                  | ± 10 |        |                  | ± 10 | μΑ   |

| ю                 | Output current (leakage)<br>(DQ1-DQ5, SOUT1-SOUT5)          | V <sub>O</sub> = 0.4 V to 5.5 V,<br>V <sub>DD</sub> = 5 V                                                                                                                                                                                                              |              |                  | ±10  |        |                  | ± 10 | μА   |

| IDD1              | Average operating current during read or write cycle        | t <sub>C(rd)</sub> = minimum cycle time,<br>TR/QE low after RAS falls, <sup>‡</sup><br>SCLK and SIN low, SOE high,<br>No load on DQ1-DQ5<br>and SOUT1-SOUT5                                                                                                            |              | 250              | 350  |        | 250              | 350  | mA   |

| lDD2 <sup>§</sup> | Standby current                                             | After 1 RAS cycle, RAS and CAS high, SCLK and SIN low, SOE high, No load on DQ1-DQ5 and SOUT1-SOUT5                                                                                                                                                                    |              | 80               | 100  |        | 80               | 100  | mA   |

| IDD3              | Average refresh current                                     | t <sub>C(rd)</sub> = minimum cycle time, CAS high, FIAS cycling, SCLK and SIN low, SOE high, TR/QE high, No load on DQ1-DQ5 and SOUT1-SOUT5                                                                                                                            |              | 210              | 275  |        | 185              | 250  | mA   |

| I <sub>DD4</sub>  | Average page-mode current                                   | t <sub>C(P)</sub> = minimum cycle time, RAS low, CAS cycling, TR/QE low after RAS falls, SCLK and SIN low, SOE high, No load on DQ1-DQ5 and SOUT1-SOUT5                                                                                                                |              | 225              | 275  |        | 200              | 250  | mA   |

| I <sub>DD5</sub>  | Average shift register current (includes I <sub>DD2</sub> ) | RAS and $\overline{\text{CAS}}$ high,<br>$t_{\text{C}(\text{SCLK})} = t_{\text{C}(\text{SCLK})}$ min,<br>No load on DQ1-DQ5<br>and SOUT1-SOUT5                                                                                                                         |              | 150              | 200  |        | 150              | 200  | mA   |

| IDD6              | Worst case average<br>DRAM and shift<br>register current    | $\begin{split} t_{\text{C}\{\text{rd}\}} &= \text{minimum cycle time,} \\ t_{\text{C}\{\text{SCLK}\}} &= \text{minimum cycle time,} \\ \overline{\text{TR}/\text{QE}} &\text{low after RAS falls,} \\ \text{No load on DQ1-DQ5} \\ \text{and SOUT1-SOUT5} \end{split}$ |              | 425              | 475  |        | 400              | 450  | mA   |

$<sup>^{\</sup>dagger}All$  typical values are at  $T_{\mbox{\scriptsize A}}=25\,^{\circ}\mbox{\scriptsize C}$  and nominal supply voltages. ‡See appropriate timing diagram.

<sup>§</sup>VIL > -0.6 V

# 65.536 BY 5-BIT MULTIPORT VIDEO RAM MODULE

# capacitance over recommended supply voltage and operating free-air temperature range, f = 1 MHz

|                       | PARAMETER                                  | MAX | UNIT     |

|-----------------------|--------------------------------------------|-----|----------|

| C <sub>i(A)</sub>     | Input capacitance, address inputs          | 35  |          |

| C <sub>i(DQ)</sub>    | Input capacitance, data inputs             | 25  |          |

| C <sub>i(RC)</sub>    | Input capacitance, strobe inputs           | 50  |          |

| C <sub>i(W)</sub>     | Input capacitance, write enable input      | 50  | pF       |

| C <sub>i(CK)</sub>    | Input capacitance, serial clock            | 50  | ] "      |

| C <sub>i(SI)</sub>    | Input capacitance, serial in               | 25  |          |

| C <sub>i</sub> (SOE)  | Input capacitance, serial output enable    | 30  | 1        |

| C <sub>i(TR)</sub>    | Input capacitance, register transfer input | 35  | ]        |

| C <sub>O</sub> (SOUT) | Output capacitance, serial out             | 35  | <u> </u> |

$<sup>^{\</sup>dagger}$ All typical values are at T<sub>A</sub> = 25 °C and nominal supply voltages.

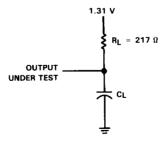

# switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 1)

|                                   |                                          |                             | ALT.   | TM4161EP | 5-15 | TM4161 | EP5-20 | UNIT |

|-----------------------------------|------------------------------------------|-----------------------------|--------|----------|------|--------|--------|------|

| PARAMETER                         |                                          | TEST CONDITIONS†            | SYMBOL | MIN I    | MAX  | MIN    | MAX    | UNIT |

| ta(C)                             | Access time from CAS                     | C <sub>L</sub> = 100 pF     | tCAC   |          | 100  |        | 135    |      |

| ta(QE)                            | Access time of Q from                    | C <sub>L</sub> = 100 pF     |        |          | 40   |        | 50     |      |

| a(R)                              | Access time from RAS                     | trice = MAX,<br>CL = 100 pF | tRAC   |          | 150  |        | 200    |      |

| ta(RSO)                           | SOUT access time from RAS high           | C <sub>L</sub> = 30 pF      |        |          | 65   |        | 85     |      |

| t <sub>a</sub> (SOE)              | Access time from SOE                     | C <sub>L</sub> = 30 pF      |        |          | 30   |        | 30     | ns   |

| ta(SO)                            | Access time from SCLK                    | C <sub>L</sub> = 30 pF      |        |          | 45   |        | 50     |      |

| t <sub>dis(CH)</sub> ‡            | Q output disable time from CAS high      | C <sub>L</sub> = 100 pF     | tOFF   |          | 40   |        | 40     |      |

| <sup>t</sup> dis(QE) <sup>‡</sup> | Q output disable time from TR/QE high    | C <sub>L</sub> = 100 pF     |        |          | 40   |        | 40     |      |

| t <sub>dis</sub> (SOE)            | Serial output disable time from SOE high | C <sub>L</sub> = 30 pF      |        |          | 30   |        | 30     |      |

<sup>†</sup>Figure 1 shows the load circuit.

<sup>&</sup>lt;sup>‡</sup>The maximum values for t<sub>dis(CH)</sub>, <sup>†</sup>dis(QE), and t<sub>dis(SOE)</sub> define the time at which the output achieves the open circuit condition and are not referenced to VOH or VOL.

# timing requirements over recommended supply voltage range and operating free-air temperature range

|                       |                                               | ALT.             | TM416 | 1EP5-15 | 5-15 TM4161EP5-20 |        |      |

|-----------------------|-----------------------------------------------|------------------|-------|---------|-------------------|--------|------|

|                       |                                               | SYMBOL           | MIN   | MAX     | MIN               | MAX    | UNIT |

| t <sub>C</sub> (P)    | Page-mode cycle time                          | <sup>t</sup> PC  | 160   |         | 225               |        | ns   |

| tc(rd)                | Read cycle time <sup>†</sup>                  | tRC              | 240   |         | 315               |        | ns   |

| t <sub>c(W)</sub>     | Write cycle time                              | twc              | 240   |         | 315               |        | ns   |

| tc(TW)                | Transfer write cycle time <sup>‡</sup>        |                  | 240   |         | 315               |        | ns   |

| <sup>t</sup> c(Trd)   | Transfer read cycle time                      |                  | 240   |         | 315               |        | ns   |

| t <sub>c</sub> (SCLK) | Serial-clock cycle time                       | tscc             | 45    | 50,000  | 50                | 50,000 | ns   |

| tw(CH)                | Pulse duration, CAS high (precharge time) §   | tCP              | 50    |         | 80                |        | ns   |

| tw(CL)                | Pulse duration, CAS low                       | tCAS             | 100   | 10,000  | 135               | 10,000 | ns   |

| tw(RH)                | Pulse duration, RAS high (precharge time)     | tRP              | 80    |         | 105               |        | ns   |

| tw(RL)                | Pulse duration, RAS low                       | tRAS             | 150   | 10,000  | 200               | 10,000 | ns   |

| tw(W)                 | Write pulse duration                          | tWP              | 45    |         | 45                |        | ns   |

| tw(CKL)               | Pulse duration, SCLK low                      |                  | 10    |         | 10                |        | ns   |

| tw(CKH)               | Pulse duration, SCLK high                     |                  | 12    |         | 12                |        | ns   |

| tw(QE)                | TR/QE pulse duration low time (read cycle)    |                  | 40    |         | 40                |        | ns   |

| tę                    | Transition times (rise and fall)              | +-               | 3     | 50      |                   |        |      |

| ٠٢                    | RAS, CAS, and SCLK                            | t <sub>T</sub>   |       | 50      | 3                 | 50     | ns   |

| t <sub>su(CA)</sub>   | Column-address setup time                     | t <sub>ASC</sub> | 0     |         | 0                 |        | ns   |

| <sup>t</sup> su(RA)   | Row-address setup time                        | <sup>t</sup> ASR | 0     |         | 0                 |        | ns   |

| t <sub>su(RW)</sub>   | W setup time before RAS low                   |                  | 0     |         | 0                 |        |      |

|                       | with TR/QE low                                |                  |       |         |                   |        | ns   |

| t <sub>su(D)</sub>    | Data setup time                               | t <sub>DS</sub>  | 0     |         | 0                 |        | ns   |

| t <sub>su(rd)</sub>   | Read-command setup time                       | tRCS             | 0     |         | 0                 |        | ns   |

| tsu(WCL)              | Early write-command setup time before CAS low | twcs             | - 5   |         | - 5               |        | ns   |

| t <sub>su</sub> (WCH) | Write-command setup time before CAS high      | tCWL             | 40    |         | 60                |        | ns   |

| t <sub>su(WRH)</sub>  | Write-command setup time before RAS high      | *RWL             | 40    |         | 60                | _      | ns   |

| t <sub>su(TR)</sub>   | TR/QE setup time before RAS low               |                  | 0     |         | 0                 |        | ns   |

| t <sub>su(St)</sub>   | Serial-data setup time before SCLK high       |                  | 6     |         | 6                 |        | ns   |

| th(SI)                | Serial-data-in hold time after SCLK high      |                  | 3     |         | 3                 |        | ns   |

| th(CLCA)              | Column-address hold time after CAS low        | <sup>t</sup> CAH | 45    |         | 55                |        | ns   |

| th(RA)                | Row-address hold time                         | tRAH             | 20    |         | 25                |        | ns   |

| th(RW)                | W hold time after RAS low with TR/QE low      |                  | 20    |         | 20                |        | ns   |

| th(RLCA)              | Column-address hold time after RAS low        | †AR              | 95    |         | 120               |        | ns   |

| th(CLD)               | Data hold time after CAS low                  | tDH              | 60    |         | 80                |        | ns   |

| th(RLD)               | Data hold time after RAS low                  | tDHR             | 110   |         | 145               |        | ns   |

| th(WLD)               | Data hold time after W low                    | tDH.             | 45    |         | 55                | +      | ns   |

| th(CHrd)              | Read-command hold time after CAS high         | tRCH             | 0     |         | 0                 |        |      |

(Continued next page.)

NOTE 5: Timing measurements are made at the 10% and 90% points of input and clock transitions. In addition, VIL max and VIH min must be met at the 10% and 90% points.

<sup>&</sup>lt;sup>†</sup>All cycle times assume  $t_t = 5$  ns except  $t_{C(SCLK)}$  which assumes  $t_t = 3$  ns.

<sup>\*</sup>Multiple transfer write cycles require separation by either a 500-ns RAS-precharge interval or any other active RAS-cycle.

<sup>§</sup>Page-mode only.

# timing requirements over recommended supply voltage range and operating free-air temperature range (concluded)

|                     |                                                                                                                | ALT.              | TM416 | IEP5-15 | TM4161   | EP5-20 | UNIT |

|---------------------|----------------------------------------------------------------------------------------------------------------|-------------------|-------|---------|----------|--------|------|

|                     |                                                                                                                | SYMBOL            | MIN   | MAX     | MIN      | MAX    | ONIT |

| th(RHrd)            | Read-command hold time after RAS high                                                                          | tRRH              | 5     |         | 5        |        | ns   |

| th(CLW)             | Write-command hold time after CAS low                                                                          | twch              | 60    |         | 80       |        | ns   |

| th(RLW)             | Write-command hold time after RAS low                                                                          | twcn              | 110   |         | 145      |        | ns   |

| th(RSO)             | Serial-data-out hold time after RAS low with TR/QE low                                                         |                   | 30    |         | 30       |        | ns   |

| th(SO)              | Serial-data-out hold time after SCLK high                                                                      |                   | 8     |         | 8        |        | ns   |

| th(TR)              | TR/QE hold time after RAS low (transfer)                                                                       |                   | 20    |         | 20       |        | ns   |

| †RLCH               | Delay time, RAS low to CAS high                                                                                | <sup>†</sup> CSH  | 150   |         | 200      |        | ns   |

| tCHRL               | Delay time, CAS high to RAS low                                                                                | tCRP              | 0     |         | 0        |        | ns   |

| tCLQEH              | Delay time, CAS low to QE high                                                                                 |                   | 100   |         | 135      |        | ns   |

| tCLRH               | Delay time, CAS low to RAS high                                                                                | tRSH              | 100   |         | 135      |        | ns   |

| †CQE                | Delay time, CAS low to QE low<br>(maximum value specified only<br>to guarantee t <sub>a(QE)</sub> access time) |                   |       | 60      |          | 85     | กร   |

| tRHSC               | Delay time, RAS high to SCLK high                                                                              |                   | 80    | 50,000  | 80       | 50,000 | ns   |

| †RLCL               | Delay time, RAS low to CAS low (maximum value specified only to guarantee access time)                         | †RCD              | 25    | 50      | 30       | 65     | ns   |

| <sup>t</sup> CKRL   | Delay time, SCLK high before  RAS low with TR/QE low                                                           |                   | 10    | 50,000  | 10       | 50,000 | ns   |

| t <sub>rf(MA)</sub> | Refresh time interval, memory array                                                                            | <sup>†</sup> REF1 |       | 4       | <b> </b> | 4      | ms   |

| trf(SR)             | Refresh time interval, shift register#                                                                         | tREF2             |       | 50,000  |          | 50,000 | ns   |

NOTE 5: Timing measurements are made at the 10% and 90% points of input and clock transitions. In addition, V<sub>IL</sub> max and V<sub>IH</sub> min must be met at the 10% and 90% points.

SCLK may be high or low during tw(RL). but there can not be any positive edge transitions on SCLK for a minimum of 10 ns prior to RAS going low with TR/QE low (i.e., before a transfer cycle).

#See "refresh" on page 5-9.

# PARAMETER MEASUREMENT INFORMATION

FIGURE 1. LOAD CIRCUIT

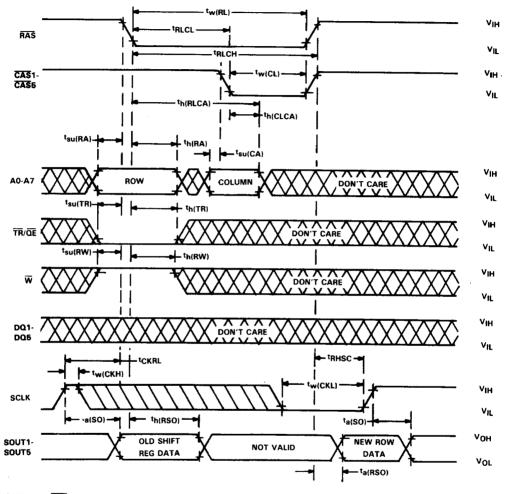

# tc(W) · tw(RL) ٧н RAS ٧ıL tCLRH w(RH) <sup>t</sup>CHRL tw(CL)-RLCL <sup>t</sup>RLCH VIH CAS1-CAS5 $v_{\text{IL}}$ t<sub>su(RA)</sub> th(RLCA) th(RA) t<sub>su(CA)</sub> V<sub>IH</sub> DON'T CARE A0-A7 th(CLCA) t<sub>su(WCH)</sub> t<sub>su(TR)</sub> 1 1 tsu(WRH) ۷ін TR/QE $v_{\text{IL}}$ ⊦<sup>t</sup>h(RLW) VIH $\overline{\mathbf{w}}$ tw(W) th(WLD) -th(CLD) th(RLD) ٧н DQ1-VALID DATA DQ5 --- t<sub>su(D)</sub>

early write cycle timing

Texas VI

#### shift register to memory timing tw(RL) νн **TRLCL** RAS VIL **tRLCH** V<sub>IH</sub> CAS1- $V_{IL}$ CAS<sub>5</sub> th(RLCA) th(CLCA) th(RA) tsu(RA) 1su(CA) ٧щ DON'T CARE ROW A0-A7 VIH TR/QE -th(RW) ٧<sub>IH</sub> ٧н ヘ ハ ハ ノ DON'T CARE DQ1-DQ5 tRHSC-<sup>t</sup>CKRL tw(CKL) tw(CKH) $V_{\text{IH}}$ SCLK ٧ıL ta(SO) ta(RSO)-- th(RSO) -+ ta(SO)-۷он SAME AS OLD SHIFT REG DATA OLD SHIFT REGISTER OLD SHIFT SOUT1-DATA NOT VALID REG DATA VOL **SOUT5**

NOTES: 9. The shift register to memory cycle is used to transfer data from the shift registers to the memory array. Every one of the 256 locations in each shift register is written into the 256 columns of the selected row. Note that the data that was in the shift registers may have resulted, either from a serial shift in or from a parallel load of the shift registers from one of the memory array rows.

- 10. SOE assumed low.

- 11. SCLK may be high or low during tw(RL)-

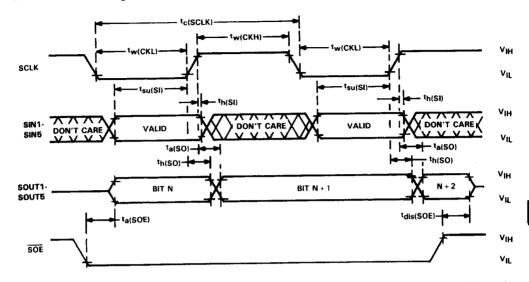

# memory to shift register timing

NOTES: 10. SOE assumed low.

- 11. SCLK may be high or low during  $t_{W(RL)}$ .

- 12. The memory to shift register cycle is used to load the shift registers in parallel from the memory array. Every one of the 256 locations in each shift register are written into from the 256 columns of the selected row. Note that the data that is loaded into the shift registers may be either shifted out or written back into another row.

# serial data shift timing

- NOTES: 13. When loading data into the shift registers from the serial input in preparation for a shift register to memory transfer operation, the serial clock must be clocked an even number of times.

- 14. While shifting data through the serial shift registers, the state of TR/QE is a don't care as long as TR/QE is held high when RAS goes low and t<sub>Su(TR)</sub> and t<sub>h(TR)</sub> timings are observed. This requirement avoids the initiation of a register-to-memory or memory-to-register data transfer operation. The serial data transfer cycle is used to shift data in and/or out of the shift registers.

5

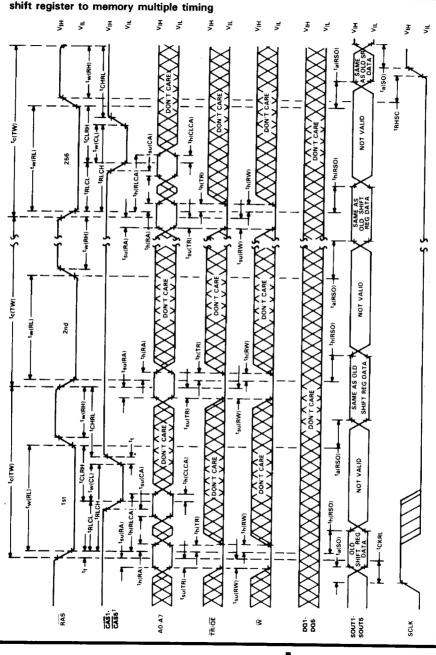

CAS and register address need not be supplied every cycle, only when it is desired to change or select a new register length.

SOE assumed low. 9 NOTES:

The shift register to memory multiple cycle is used to write the shift register data to more than one row of the memory array. An application of this could be clearing all memory. To do this, the SiN lines would be held at 0 to fill all locations in the shift registers with 0's. The shift registers would then be written into all 256 rows of the memory array in 256 cycles. The random output ports (DQ1-DQ5) will be in a high-impedance state as long as register SCLK is a don't care except that no positive transitions on SCLK can occur for a period equal to tCKRL prior to RAS falling with TR/OE low transfer cycles are selected. 9

INSTRUMENTS

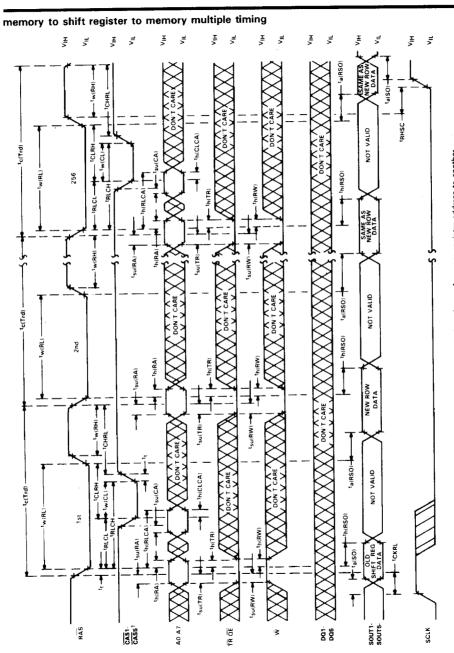

TCAS and register address need not be supplied every cycle, only when it is desired to change from one register address to another. SOE assumed low. ō. NOTES:

the shift register and then it is written into other selected rows. The random output port Q will be in a high-impedance state as long as register transfer cycles are selected. The memory to shift register to memory multiple cycle is used to reorder the rows within the memory array itself. First, the data in a row is stored in SCLK is a don't care except that no positive transitions on SCLK can occur for a period equal to tCKRL prior to RAS falling with TR/QE low. 9

TI single-in-line package nomenclature