### Advance Information

This document contains information on a product under development. The parametric information contains target parameters that are subject to change.

## **CN8380**

## Quad T1/E1 Line Interface

The CN8380 is a fully integrated quad line interface unit for both 1.544 Mbps (T1) and 2.048 Mbps (E1) applications. It is designed to complement T1/E1 framers or operate as a stand-alone line interface to synchronous or plesiochronous mappers and multiplexers. The device can be controlled through a host mode serial port or by hardware mode operation, where device control and status are obtained through non-multiplexed dedicated pins. Many of these pins are also dedicated to individual channels for maximum flexibility and for use in redundant systems. Integrated in the CN8380 device is a clock rate adapter (CLAD), which provides various low-jitter programmable system clock outputs. The receive section of the CN8380 is designed to recover encoded signals from lines having up to 12 dB of attenuation. The transmit section consists of a programmable, precision pulse shaper.

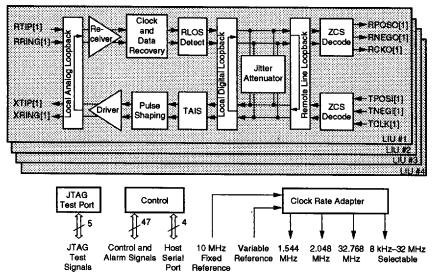

### **Functional Block Diagram**

8380\_001

### **Distinguishing Features**

- Four T1/E1 short haul line interfaces in a single chip

- On-chip CLAD /system synchronizer

- Digital (crystal-less) jitter attenuators selectable for transmitter/receiver on each line interface

- Meets AT&T pub 62411 jitter specs

- Meets ITU G.703, ETS 300 011 (PSTNX) Connections

- AMI/B8ZS/HDB3 line codes

- Host serial port or hardware only control modes

- On-chip receive clock recovery

- Common transformers for 120/75  $\Omega$  E1 and 100  $\Omega$  T1

- Low-power 3.3 V power supply

- · Transmitter performance monitor

- Compatible with latest ANSI, ITU-T, and ETSI standards

- 128-pin MQFP package

- · Remote and local loopbacks

### Applications

- SONET/SDH multiplexers

- T3 and E3/E4 (PDH) multiplexers

- ATM multiplexers

- Voice compression and voice processing equipment

- WAN routers and bridges

- · Digital loop carrier terminals (DLC)

- HDSL terminal units

- · Remote concentrators

- Central office equipment

- PBXs and rural switches

- PCM/voice channel banks

- Digital access and cross-connect systems (DACS)

## **Ordering Information**

| Model Number | Package       | Operating Temperature |  |  |

|--------------|---------------|-----------------------|--|--|

| CN8380EPF    | 128-pin MQFP  | 40 ℃ to +85 ℃         |  |  |

| CN8398EVM    | BT00-D660-001 |                       |  |  |

## **Revision History**

| Revision | Level   |                | Description |

|----------|---------|----------------|-------------|

| Α        | Advance | April 26, 1999 | Created     |

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

Conexant and "What's Next in Communications Technologies" are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc. Printed in U.S.A. All Rights Reserved

Reader Response: To improve the quality of our publications, we welcome your feedback. Please send comments or suggestions via e-mail to Conexant Reader Response@conexant.com. Sorry, we can't answer your technical questions at this address. Please contact your local Conexant sales office or local field applications engineer if you have technical questions.

N8380DSA

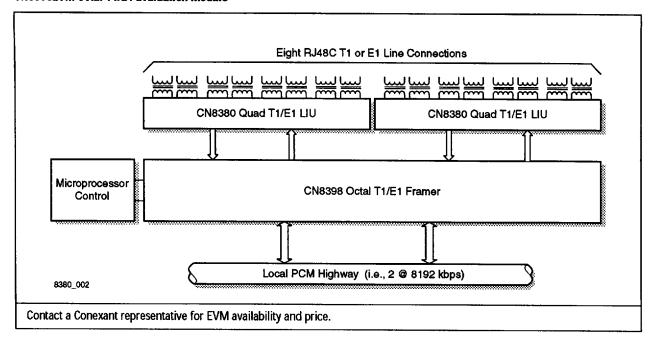

### CN8398EVM Octal T1/E1 Evaluation Module

### **Detailed Feature Summary**

### Interface Compatibility

- T1.102–1993

- G.703 at 1.544 or 2.048 Mbps

- ITU-T Recommendation 1.431

### Receive Line Interface

- · External Termination

- Equalizer compensation for 20 dB bridged monitor levels

- + 3 dB to -12 dB receiver sensitivity

#### **Transmit Line Interface**

- Pulse shapes for 0–655 ft., in 133 ft. steps (T1 DSX-1)

- External termination for improved return loss

- Line driver enable/disable for protection switching

- Output short circuit protection (for BABT applications)

#### **Jitter Attenuator Elastic Store**

- Receive or transmit direction

- · 8-, 16-, 32-, 64-, or 128-bit depth

- · Automatic and manual centering

### **Line Codes**

- Bipolar alternate mark inversion line coding

- Optional zero code suppression:

- Independent transmit and receive

- T1: B8ZS

- E1: HDB3

#### Loopbacks

- Remote loopback towards line

- With or without JAT

- Retains BPV transparency

- Local loopback towards system

- Analog line loopback

- Local digital loopback

- Simultaneous local and remote line loopbacks

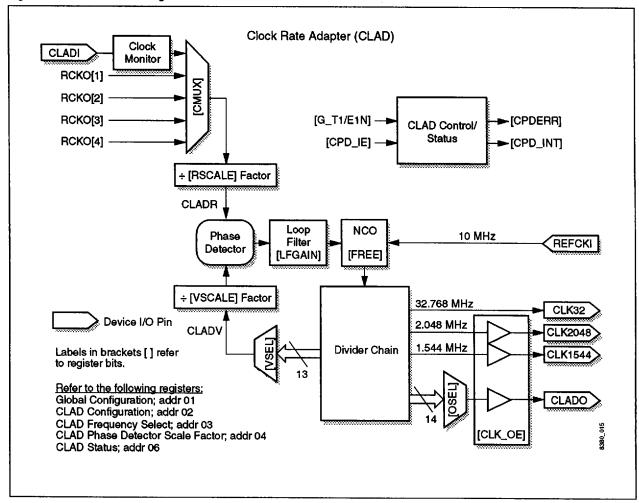

### **Clock Rate Adapter**

- Outputs jitter attenuated line rate clock

- CLK1544 = 1544 k (T1)

- CLK2048 = 2048 k (E1)

- CLAD output supports 14 output clock frequencies: 8 kHz to 32,768 kHz

- Programmable input timing reference:

- Receive recovered clock from any channel

- Internal clock (REFCKI)

- CLADI

- Subrate CLADI timing reference:

- Line rate  $\pm 2^N$ , N = 0 to 7

- References as low as 8 kHz

### **Host Serial Interface**

- Compatible with existing framers

- Compatible with microprocessor serial ports

- · Bit rates up to 8 Mbps

### In-Service Performance Monitoring

- Transmit alarm detectors:

- Loss of Transmit Clock (TLOC)

- Transmit Short Circuit (TSHORT)

- Receive alarm detectors:

- Loss of Signal (RLOS)

- Loss of Analog Input (RALOS)

- Bipolar/Line Code Violations

- Automatic and on-demand transmit alarms;

- AIS following TLOC

- Automatic AIS clock switching

## **Table of Contents**

| List o | f Figu  | res     |           | ix                         |

|--------|---------|---------|-----------|----------------------------|

| List o | f Table | es      |           | xi                         |

| 1.0    | Pin     | Descrip | otions    |                            |

| 2.0    | Circ    | uit Des | cription  |                            |

|        | 2.1     | Overvi  | ew        | ····· 2-1                  |

|        | 2.2     |         |           | Control                    |

|        | ~       | 2.2.1   |           | Mode                       |

|        |         | 2.2.2   |           | de                         |

|        |         | 2.2.3   |           | al Control Interface       |

|        |         | 2.2.4   |           | 2-4                        |

|        |         |         | 2.2.4.1   | Power-on Reset             |

|        |         |         | 2.2.4.2   | Hard Reset                 |

|        |         |         | 2.2.4.3   | Soft Reset                 |

|        | 2.3     | Receiv  | er        |                            |

|        |         | 2.3.1   |           | overy                      |

|        |         |         | 2.3.1.1   | Raw Receive Mode           |

|        |         |         | 2.3.1.2   | Sensitivity2-7             |

|        |         |         | 2.3.1.3   | Bridge Mode                |

|        |         |         | 2.3.1.4   | Loss Of Signal Detector2-8 |

|        |         | 2.3.2   | Clock Re  | covery                     |

|        |         |         | 2.3.2.1   | Phase Lock Loop            |

|        |         |         | 2.3.2.2   | Jitter Tolerance           |

|        |         | 2.3.3   | Receive . | Jitter Attenuator          |

|        |         | 2.3.4   | RZCS De   | coder                      |

|        |         | 2.3.5   | Receive ( | Digital Interface          |

|        |         |         | 2.3.5.1   | Bipolar Mode               |

|        |         |         | 2.3.5.2   | Unipolar Mode              |

|     | 2.4 | Transm    | itter                                        | 2-10 |

|-----|-----|-----------|----------------------------------------------|------|

|     |     | 2.4.1     | Transmit Digital Interface                   | 2-10 |

|     |     |           | 2.4.1.1 Bipolar Mode                         | 2-10 |

|     |     |           | 2.4.1.2 Unipolar Mode                        | 2-11 |

|     |     | 2.4.2     | TZCS Encoder                                 | 2-11 |

|     |     | 2.4.3     | Transmit Jitter Attenuator                   | 2-11 |

|     |     | 2.4.4     | All 1s AlS Generator                         | 2-11 |

|     |     | 2.4.5     | Pulse Shaper                                 | 2-13 |

|     |     | 2.4.6     | Driver                                       | 2-14 |

|     |     |           | 2.4.6.1 Transmit Termination Options         | 2-14 |

|     |     |           | 2.4.6.2 Output Disable                       | 2-18 |

|     |     | 2.4.7     | Transmitter Output Monitoring                | 2-19 |

|     |     |           | 2.4.7.1 Short Circuit Detect                 | 2-19 |

|     |     |           | 2.4.7.2 Driver Performance Monitor           | 2-19 |

|     | 2.5 | Loopba    | cks                                          | 2-20 |

|     |     | 2.5.1     | Local Analog Loopback                        |      |

|     |     | 2.5.2     | Local Digital Loopback                       |      |

|     |     | 2.5.3     | Remote Line Loopback                         |      |

|     | 2.6 | Jitter At | tenuator                                     | 2-22 |

|     | 2.7 |           | ate Adapter                                  |      |

|     | ,   | 2.7.1     | Inputs                                       |      |

|     |     | 2.7.2     | Outputs                                      |      |

|     |     | 2.7.3     | Configuration Options                        |      |

|     | 2.8 |           | cess Port (JTAG)                             |      |

|     | 2.0 | 2.8.1     | Instructions                                 |      |

|     |     | 2.8.2     | Device Identification Register               |      |

|     |     |           | ·                                            |      |

| 3.0 | Reg |           | ••••••                                       |      |

|     | 3.1 | Address   | ы Мары мары мары мары мар                    | 3-1  |

|     | 3.2 | Global (  | Control and Status Registers                 | 3-3  |

|     |     |           | 00—Device Identification (DID)               | 3-3  |

|     |     |           | 01—Global Configuration (GCR)                | 3-3  |

|     |     |           | 02—CLAD Configuration (CLAD_CR)              | 3-4  |

|     |     |           | 03—CLAD Frequency Select (CSEL)              | 3-5  |

|     |     |           | 04—CLAD Phase Detector Scale Factor (CPHASE) | 3-6  |

|     |     |           | 05—CLAD Test (CTEST)                         | 3-7  |

|     |     |           | 06—CLAD Status (CSTAT)                       | 3-7  |

|     |     |           | 07—(FREG)                                    | 3-7  |

|     |     |           | 08—(TESTA1)                                  | 3-7  |

|     |     |           | 09—(TESTA2)                                  | 3-7  |

|     |     |           | 0A—(FUSE_CH1)                                |      |

|     |     |           | 0B—(FUSE_CH2)                                |      |

|     |     |           | 0C—(FUSE_CH3)                                |      |

|     |     |           | 0D—(FUSE_CH4)                                |      |

|     |     |           | 0E—(FUSE_RES)                                |      |

|     |     |           | OF—(TESTD)                                   |      |

|     |     |           |                                              |      |

|      | 3.3    | Per Channel Registers                                   | 3-10          |

|------|--------|---------------------------------------------------------|---------------|

|      |        | 10, 20, 30, 40—Jitter Attenuator Configuration (JAT_CR) | 3-10          |

|      |        | 11, 21, 31, 41—Receiver Configuration (RLIU_CR)         | 3-11          |

|      |        | 12, 22, 32, 42 —Transmitter Configuration (TLIU_CR)     |               |

|      |        | 13, 23, 33, 43—LIU Control (LIU_CTL)                    | 3-13          |

|      |        | 15, 25, 35, 45—Alarm Status (ALARM)                     | 3-15          |

|      |        | 16, 26, 36, 46—Interrupt Status Register (ISR)          | 3-16          |

|      |        | 17, 27, 37, 47—Interrupt Enable Register (IER)          | 3-16          |

|      | 3.4    | Transmitter Shape Registers                             | 3-17          |

|      |        | 18 - 1F—Transmit PULSE Shape CONFIGURATION (SHAPE1)     | 3-17          |

|      |        | 28 - 2FTransmit PULSE Shape CONFIGURATION (SHAPE2)      | 3-17          |

|      |        | 38 - 3F—Transmit PULSE Shape CONFIGURATION (SHAPE3)     | 3-17          |

|      |        | 48 - 4F—Transmit PULSE Shape CONFIGURATION (SHAPE4)     |               |

|      |        | 50—(TESTA3)                                             | 3-17          |

|      |        | 51—(TESTA4)                                             | . 3-18        |

| 4.0  | Elec   | ctrical/Mechanical Specifications                       | 4-1           |

|      | 4.1    | Absolute Maximum Ratings                                | . 4-1         |

|      | 4.2    | Recommended Operating Conditions                        |               |

|      | 4.3    | DC Characteristics                                      | 4-3           |

|      | 4.4    | Performance Characteristics                             | . 4-4         |

|      | 4.5    | AC Characteristics                                      | . 4-5         |

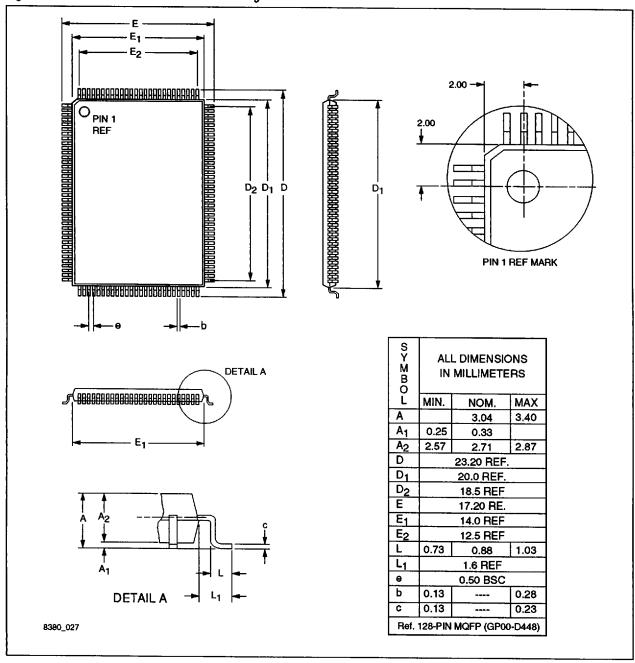

|      | 4.6    | Packaging                                               | 4-13          |

| Appe | ndix A | : Applicable Standards                                  | . <b>A-</b> 1 |

| Appe | ndix B | : External Component Specifications                     | . B-1         |

| Appe | ndix C | : Acronym List                                          | . C-1         |

## **List of Tables**

| Table 1-1.  | Hardware Signal Definitions                           | 1-5   |

|-------------|-------------------------------------------------------|-------|

| Table 2-1.  | Line Compatible Modes                                 |       |

| Table 2-2.  | Transmitter Operating Modes                           | 2-12  |

| Table 2-3.  | Transmit Pulse Configurations                         |       |

| Table 2-4.  | Transmit Termination Option A                         |       |

| Table 2-5.  | Transmit Termination Option B                         |       |

| Table 2-6.  | Transmit Termination Option C                         | 2-17  |

| Table 2-7.  | Transmit Termination Option D                         |       |

| Table 2-8.  | Transmit Termination Option E                         |       |

| Table 2-9.  | Loopback Controls                                     | 2-20  |

| Table 2-10. | CLAD Outputs and Frequencies                          |       |

| Table 2-11. | CLAD Reference Frequencies and Configuration Examples | 2-27  |

| Table 2-12. | Sample Alternate Configuration                        | 2-28  |

| Table 2-13. | JTAG Instructions                                     |       |

| Table 2-14. | Device Identification JTAG Register                   | 2-29  |

| Table 3-1.  | Address Map                                           | . 3-1 |

| Table 3-2.  | Transmitter Operating Modes                           |       |

| Table 4-1.  | Absolute Maximum Ratings                              |       |

| Table 4-2.  | Recommended Operating Conditions                      |       |

| Table 4-3.  | DC Characteristics                                    | . 4-2 |

| Table 4-4.  | Performance Characteristics                           | . 4-3 |

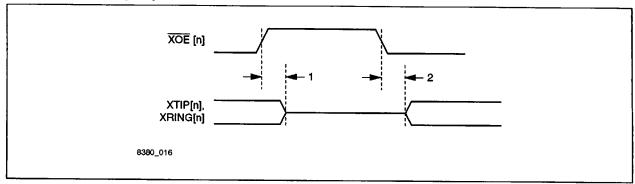

| Table 4-5.  | XOE Timing Parameters                                 |       |

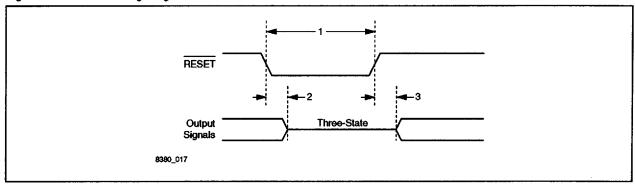

| Table 4-6.  | RESET Timing Parameters                               |       |

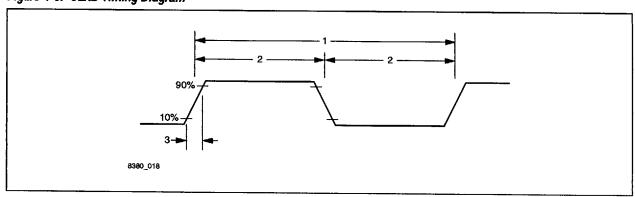

| Table 4-7.  | CLAD Timing Parameters                                | . 4-7 |

| Table 4-8.  | Receiver Signals Timing Parameters                    |       |

| Table 4-9.  | Transmitter Signals Timing Parameters                 | . 4-9 |

| Table 4-10. | Host Serial Port Timing Parameters                    |       |

| Table 4-11. | JTAG Interface Timing Parameters                      | 4-12  |

| Table A-1.  | Applicable Standards                                  | . A-1 |

| Table B-1.  | Transformer Specifications                            |       |

| Table B-2.  | REFCKI (10 MHz) Crystal Oscillator Specifications     |       |

## **List of Figures**

| Figure 1-1.  | CN8380 Pinout Diagram                                       | 1-2          |

|--------------|-------------------------------------------------------------|--------------|

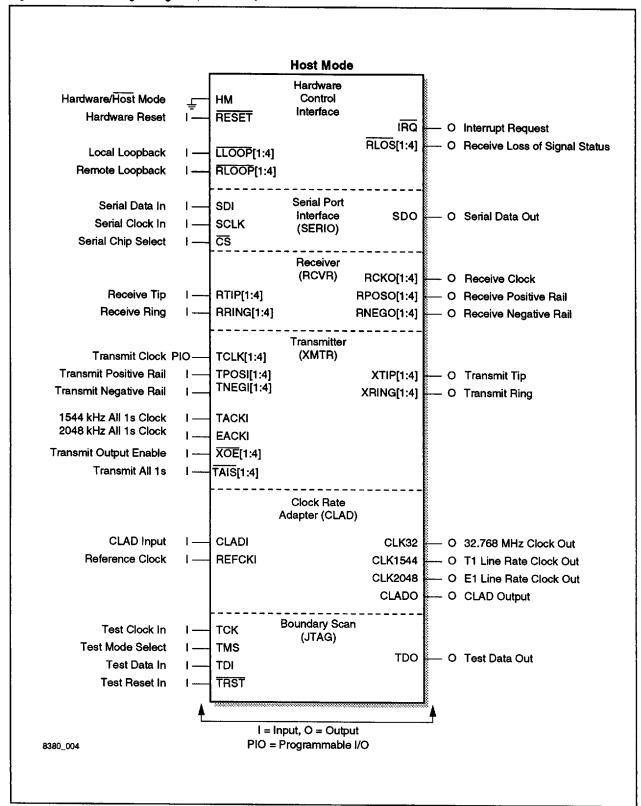

| Figure 1-2.  | CN8380 Logic Diagram (Host Mode)                            | 1-3          |

| Figure 1-3.  | CN8380 Logic Diagram (Hardware Mode)                        |              |

| Figure 2-1.  | Detailed Block Diagram                                      | 2-2          |

| Figure 2-2.  | Host Serial Port Signals                                    | 2-4          |

| Figure 2-3.  | Receiver Signals                                            | 2-6          |

| Figure 2-4.  | Raw Mode Receiver Signals                                   | 2-7          |

| Figure 2-5.  | Transmitter Signals                                         | 2-10         |

| Figure 2-6.  | Transmit Pulse Shape                                        | 2-14         |

| Figure 2-7.  | Transmit Termination Components                             | 2-15         |

| Figure 2-8.  | Receiver Input Jitter Tolerance                             | 2-23         |

| Figure 2-9.  | Typical JAT Transfer Characteristics with Various JAT Sizes | 2-24         |

| Figure 2-10. | CLAD Block Diagram                                          | 2-25         |

| Figure 4-1.  | XOE Timing Diagram                                          | 4-5          |

| Figure 4-2.  | RESET Timing Diagram                                        | 4 <b>-</b> 6 |

| Figure 4-3.  | CLAD Timing Diagram                                         | 4-7          |

| Figure 4-4.  | Receiver Signals Timing Diagram                             | 4-8          |

| Figure 4-5.  | Transmitter Signals Timing Diagram                          | 4-9          |

| Figure 4-6.  | Host Serial Port Timing Diagram                             | 4-10         |

| Figure 4-7.  | Host Serial Port Write Timing                               | 4-11         |

| Figure 4-8.  | Host Serial Port Read Timing                                | 4-11         |

| Figure 4-9.  | JTAG Interface Timing Diagram                               | 4-12         |

| Figure 4-10. | 128-Pin MQFP Mechanical Drawing                             | 4-13         |

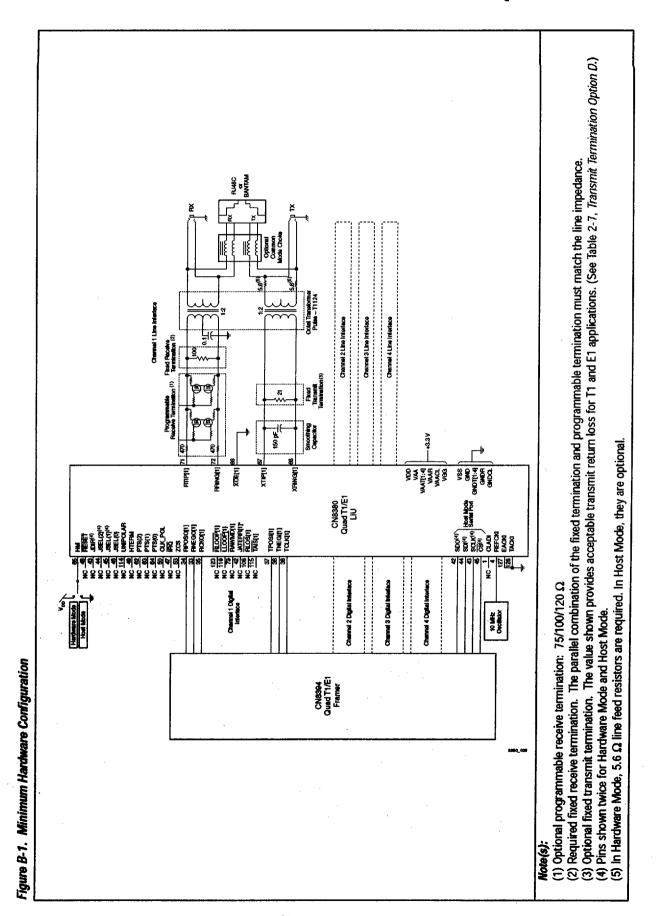

| Figure B-1.  | Minimum Hardware Configuration                              | B-2          |

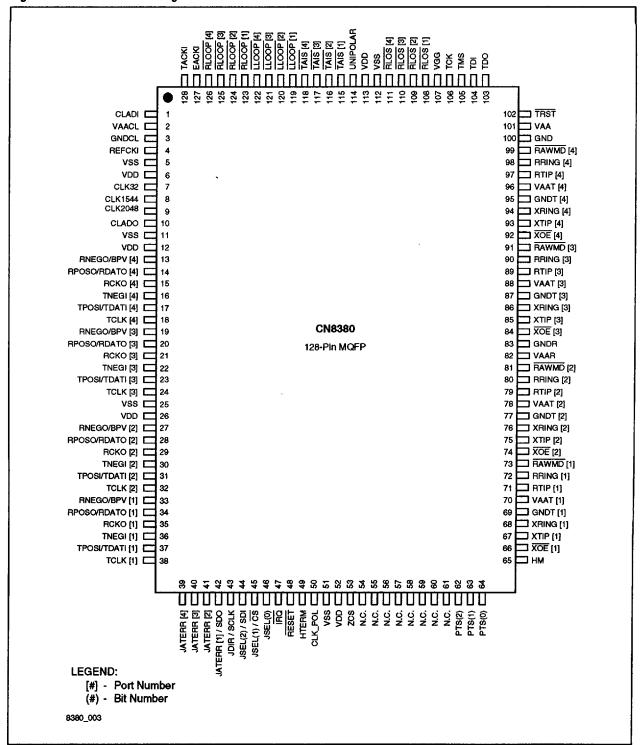

## 1.0 Pin Descriptions

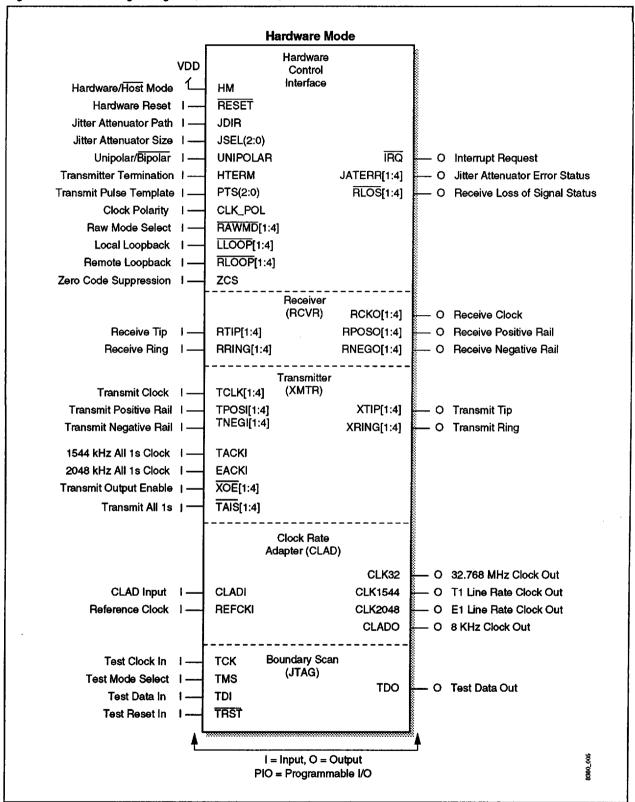

The CN8380 is packaged in a 128-pin metric quad flat pack (MQFP). A pinout diagram is illustrated in Figure 1-1. Logic diagrams are illustrated in Figure 1-2 and Figure 1-3. Pin labels and numbers, input/output functions, and descriptions are provided in Table 1-1.

The following input pins contain an internal pull-up resistor (> 50 k $\Omega$ ) and may remain unconnected if unused or if the active high input state is desired:

```

XOE [1:4]

TAIS [1:4]

RAWMD [1:4]

RLOOP [1:4]

LLOOP [1:4]

HM

UNIPOLAR

JDIR/SCLK

JSEL(2)/SDI

JSEL(1)/CS

JSEL(0)

RESET

HTERM

CLK_POL

PTS(2:0)

TDI

(Unused if JTAG not connected)

TMS

(Disables JTAG if not connected)

TCK

(Unused if JTAG not connected)

TRST

(Unused if JTAG not connected)

```

Figure 1-1. CN8380 Pinout Diagram

Figure 1-2. CN8380 Logic Diagram (Host Mode)

Figure 1-3. CN8380 Logic Diagram (Hardware Mode)

**Table 1-1. Hardware Signal Definitions** (1 of 5)

| Pin Label                | Signal Name                                                                | 1/0            | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------|----------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                                                                            |                | Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RPOSO[1:4]<br>RDATO[1:4] | RX Positive Rail<br>(Bipolar Mode)<br>RX Data (Unipolar<br>Mode)           | 0              | Line rate data output on the rising or falling edge of RCKO. The clock edge is determined by the CLK_POL pin in Hardware Mode or the CLK_POL register bit [RLIU_CR; addr n1] in Host Mode. In bipolar mode, a high signal indicates receipt of a positive AMI pulse on RTIP/RRING inputs. In unipolar mode, RPOSO is redefined as RDATO and a high signal indicates either a positive or negative AMI pulse on RTIP/RRING inputs. RPOSO/RDATO is three-stated during device reset.   |

| RNEGO[1:4]<br>BPV[1:4]   | RX Negative Rail<br>(Bipolar Mode)<br>Bipolar Violation<br>(Unipolar Mode) | 0              | Line rate data output on rising or falling edge of RCKO. The clock edge is determined by the CLK_POL pin in Hardware Mode or the CLK_POL register bit [RLIU_CR; addr n1] in Host Mode. In bipolar mode, a high signal indicates receipt of a negative AMI pulse on RTIP/RRING inputs. In unipolar mode, RNEGO is redefined as BPV, and a high signal indicates the reception of a BPV which is not part of a ZCS code (B8ZS or HDB3). RNEGO/BPV is three-stated during device reset. |

| RCKO[1:4]                | RX Clock Output                                                            | 0              | Receive clock output. RCKO is the RPLL recovered line rate clock or jitter attenuated clock output, based on the programmed jitter attenuator selection. RCKO is three-stated during device reset.                                                                                                                                                                                                                                                                                   |

| RTIP[1:4]                | Receive Tip                                                                | I              | Differential AMI data inputs for direct connection to receive transformer.                                                                                                                                                                                                                                                                                                                                                                                                           |

| RRING[1:4]               | Receive Ring                                                               |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                          |                                                                            |                | Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TPOSI[1:4] TDATI[1:4]    | Tx Positive Rail<br>(Bipolar Mode)<br>Tx Data (Unipolar<br>Mode)           | ı              | Positive rail, line rate data source for transmitted XTIP/XRING output pulses. Data is sampled on the falling edge of TCLK. In bipolar mode, a high on TPOSI causes a positive output pulse on XTIP/XRING; and a high on TNEGI causes a negative output pulse. In unipolar mode, TPOSI is redefined as TDATI and accepts single-rail NRZ data. TNEGI is not used in unipolar mode.                                                                                                   |

| TNEGI[1:4]               | Tx Negative Rail<br>Input                                                  | I              | Negative rail, line rate data input on TCLK falling edge. Refer to TPOSI signal definition.                                                                                                                                                                                                                                                                                                                                                                                          |

| TCLK[1:4]                | TX Clock Input                                                             | 1/0            | Transmit line rate clock. TCLK is the transmit clock for TPOSI and TNEGI data inputs and for transmitter timing. Normally, TCLK is an input and samples TPOSI/TNEGI on the falling edge. In Host Mode, TCLK can be configured as an output to supply a line rate transmit clock from the CLAD. The timing reference for the TCLK output (and CLAD) can be selected from six sources.                                                                                                 |

| TACKI                    | T1 AIS Clock E1 AIS Clock                                                  | l              | Alternate T1 and E1 transmit clock used to transmit AIS (all 1s alarm signal) when the primary transmit clock source, TCLK, fails. TACKI (T1) or EACKI (E1) is either manually or automatically switched to replace TCLK [LIU_CTL; addr n3]. Systems without an AIS clock should connect TACKI and EACKI to ground.                                                                                                                                                                  |

| XOE[1:4]                 | Transmit Output<br>Enable                                                  | ĮΡ             | A low signal enables XTIP and XRING output drivers. Otherwise outputs are high impedance.                                                                                                                                                                                                                                                                                                                                                                                            |

| TAIS[1:4]                | Transmit AIS<br>Alarm                                                      | I <sup>P</sup> | In Hardware Mode, a low signal causes AIS (unframed all 1s) transmission on XTIP/XRING outputs. In Host Mode, these pins can be enabled or disabled [LIU_CTL; addr n3]. If disabled, they are not used and may be left unconnected.                                                                                                                                                                                                                                                  |

Table 1-1. Hardware Signal Definitions (2 of 5)

| Pin Label            | Signal Name                | 1/0 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTIP[1:4] XRING[1:4] | Transmit Tip Transmit Ring | 0   | Complementary AMI transmitter line outputs for direct connection to transmit transformer. Optionally, both outputs are three-stated when XOE is high.                                                                                                                                                                                                                                                                                                                              |

| ARING[1:4]           | Transmit Ring              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      |                            | - U | ock Rate Adapter (CLAD)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLADI                | CLAD input                 |     | CLAD input timing reference used to phase/frequency lock the CLAD outputs to an input clock frequency selected in the range of 8 kHz to 32,768 kHz [CLAD_CR; addr 02]. Systems which do not use CLADI should connect CLADI to ground. In Hardware Mode, the CLAD timing reference automatically switches to internal free-run operation if clock edges are not detected on CLADI pin.                                                                                              |

| REFCKI               | Reference Clock            | _   | System must apply a 10 MHz ± 50 ppm (E1) or ± 32 ppm (T1) clock signal to act as the frequency reference for the internal numerically controlled oscillator (NCO). REFCKI determines the frequency accuracy and stability of the CLAD output clocks when operating in free-run mode [CLAD_CR; addr 02]. REFCKI is the baseband reference for all CLAD/JAT functions and is used internally to generate clocks of various frequency locked to a selected receive or external clock. |

|                      |                            |     | Note: REFCKI is always required.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLK32                | 32 MHz Clock<br>Output     | 0   | Fixed rate 32.768 MHz clock output provided by the CLAD. May be used by framers, such as the CN8398 octal T1/E1 framer, to provide system timing reference.                                                                                                                                                                                                                                                                                                                        |

| CLK1544              | T1 Clock Output            | 0   | Fixed rate 1.544 MHz T1 line rate clock output provided by the CLAD. May be used for TCLK or TACKI clock sources. This clock is locked to the selected CLAD timing reference.                                                                                                                                                                                                                                                                                                      |

| CLK2048              | E1 Clock Output            | 0   | Fixed rate 2.048 MHz E1 line rate clock output provided by the CLAD. May be used for TCLK or EACKI clock sources. This clock is locked to the selected CLAD timing reference.                                                                                                                                                                                                                                                                                                      |

| CLADO                | CLAD Output                | 0   | In Hardware Mode, CLADO is a fixed rate 8 kHz clock output provided by the CLAD. In Host Mode, CLADO may be configured to operate at one of 14 different clock frequencies [CSEL; addr 03] that include T1 or E1 line rates. CLADO is typically programmed to supply system clocks that are phase-locked to the selected receive or CLAD timing reference [CLAD_CR; addr 02].                                                                                                      |

| •                    | ,                          | Н   | ardware Control Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| НМ                   | Hardware Mode              | IP  | A high on HM places the device in Hardware Mode, enabling all hardware control pin functions. A low on HM places the device in Host Mode, disabling some hardware-mode-only pin functions and enabling the serial port signals on the dual function pins listed below. The serial port signals allow serial host access to the device registers. Refer to the Host Serial Control Signals section of this table.                                                                   |

|                      |                            |     | JSEL(1) / CS JSEL(2) / SDI JDIR / SCLK JATERR(1) / SDO                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RAWMD[1:4]           | Raw Mode                   | ľΡ  | Low selects receiver Raw mode. Applicable only in Hardware Mode. In Raw mode, RPOSO and RNEGO represent the data slicer outputs and RCKO is the logical OR of RPOSO and RNEGO.                                                                                                                                                                                                                                                                                                     |

Table 1-1. Hardware Signal Definitions (3 of 5)

| Pin Label   | Signal Name                            | 1/0            | Definition                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|----------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET       | Hardware Reset                         | P              | Active low asynchronous hardware reset. A falling edge forces registers to their default, power-up state. Output pins are forced to the high impedance state while RESET is asserted. RESET is not mandatory at power-up because an internal power-on reset circuit performs an identical function.                                                                                        |

| UNIPOLAR    | Unipolar Mode<br>Select                | Ι <sup>P</sup> | Applicable only in Hardware Mode. A high signal on UNIPOLAR configures all RPOSO outputs and TPOSI inputs to operate with unipolar, NRZ-formatted data. In this mode, RNEGO reports non-ZCS BPVs and TNEGI is not used. A low signal on UNIPOLAR configures all channels' RPOSO/RNEGO and TPOSI/TNEGI interfaces to operate with bipolar, dual-rail, NRZ formatted data.                   |

| zcs         | Zero Code<br>Suppression<br>Select     | Ι <sup>Ρ</sup> | Applicable only in Hardware Mode. A high signal on ZCS enables the transmit ZCS encoder and the receive ZCS decoder if unipolar mode is enabled (UNIPOLAR = 1). In Bipolar Mode (UNIPOLAR = 0), the ZCS encoder and decoder are disabled and ZCS is ignored.                                                                                                                               |

| CLK_POL     | Rx Clock Polarity<br>Select            | Ι <sup>P</sup> | Applicable only in Hardware Mode. High sets RPOSO/RNEGO to be output on the falling edge of RCKO. Low sets RPOSO/RNEGO to be output on the rising edge of RCKO                                                                                                                                                                                                                             |

| PTS(2:0)    | Transmit Pulse<br>Template Select      | ΙP             | Applicable only in Hardware Mode. The PTS(2:0) control bus selects the transmit pulse template and the line rate (T1 or E1) globally for all channels. Refer to the description of HTERM in this table and to the transmit pulse configurations in Table 2-3.                                                                                                                              |

| HTERM       | Transmitter<br>Hardware<br>Termination | Ι <sup>P</sup> | Applicable only in Hardware Mode. If an external transmit termination resistor is used to meet return loss specifications; a transformer with a 1:2 turns ratio is used, and HTERM is set high to allow the transmitter to compensate for the increased load. Refer to the Transmitter section of this table and Tables 2-4 through 2-8 for transmitter termination configuration options. |

| ĪRQ         | Interrupt Request                      | OD             | Active low, open drain output. In Host Mode, IRQ indicates one or more pending interrupt requests ([ISR; addr n6] and [CSTAT; addr 06]). In Hardware Mode, IRQ is the logical NOR of the four internal transmitter driver performance monitor outputs.                                                                                                                                     |

| JSEL(2:0)   | Jitter Attenuator<br>Select            | I <sup>P</sup> | Applicable only in Hardware Mode. The JSEL and JDIR pins determine the JAT configuration. JSEL(2:0) enables and selects the JAT depth as shown in the table below. SDI/JSEL(2) and CS /JSEL(1) are dual function pins.  JSEL(2:0) JAT Mode 000 8 bits 001 16 bits 010 32 bits 011 64 bits 100 128 bits 111 Disable JAT                                                                     |

| JDIR        | Jitter Attenuator<br>Direction         | ΙP             | Applicable only in Hardware Mode. JDIR determines the path in which the JAT is inserted. If JDIR is low, the JAT (if enabled) is placed in the receive path; if high, the JAT (if enabled) is placed in the transmit path. Refer to the description for JSEL(2:0). SCLK/JDIR is a dual function pin.                                                                                       |

| JATERR[1:4] | Jitter Attenuator<br>Error             | 0              | Applicable only in Hardware Mode. A high on JATERR indicates an overflow or underflow error in the jitter attenuator elastic store.  JATERR(1) / SDO is a dual function pin.                                                                                                                                                                                                               |

**Table 1-1. Hardware Signal Definitions** (4 of 5)

| Pin Label   | Signal Name               | 1/0            | Definition                                                                                                                                                                                                              |

|-------------|---------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLOS [1:4]  | Receive Loss of<br>Signal | 0              | RLOS is asserted low when 100 (T1) or 32 (E1) consecutive 0s (no pulses) are received at the line interface or when the received signal level is approximately 18 dB below nominal for at least 1 ms.                   |

| LLOOP [1:4] | Local Loop                | ΙP             | These pins are always enabled in Hardware Mode and may be enabled or disabled in Host Mode [LIU_CTL; addr n3]. A low on LLOOP initiates Local                                                                           |

| RLOOP [1:4] | Remote Loop               | IP             | Analog Loopback and a low on RLOOP initiates Remote Line Loopback.  Local Digital Loopback is initiated if both signals are asserted together.                                                                          |

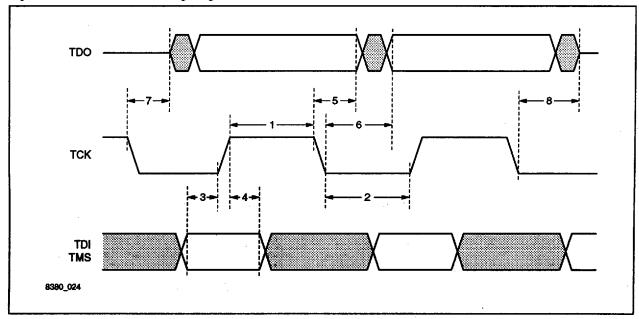

|             |                           | Bou            | ndary Scan Signals (JTAG)                                                                                                                                                                                               |

| TDO         | Test Data Output          | 0              | Test data output per IEEE Std. 1149.1-1990. Three-state output used for reading all serial configuration and test data from internal test logic. Updated on the falling edge of TCK.                                    |

| TDI         | Test Data Input           | I <sup>P</sup> | Test data input per IEEE Std. 1149.1-1990. Used for loading all serial instructions and data into internal test logic. Sampled on the rising edge of TCK. TDI may be left unconnected if not used.                      |

| TMS         | Test Mode Select          | l <sup>P</sup> | Active-low test mode select input per IEEE Std 1149.1-1990. Internally pulled-up input signal used to control the test logic state machine. Sampled on the rising edge of TCK. TMS may be left unconnected if not used. |

| тск         | Test Clock                | iΡ             | Test clock input per IEEE Std. 1149.1-1990. Used for all test interface and internal test-logic operations. If not used, TCK should be pulled low.                                                                      |

| TRST        | Reset                     | I <sup>P</sup> | Active low reset. $\overline{\text{TRST}}$ is pulled up internally and may be left unconnected if not used.                                                                                                             |

|             |                           | Ho             | est Serial Control Signals                                                                                                                                                                                              |

| <u>cs</u>   | Chip Select               | ΙP             | In Host Mode, $\overline{\text{CS}}$ is an active low input used to enable read/write access with the host serial control port. $\overline{\text{CS}}$ /JSEL(1) is a dual function pin.                                 |

| SDI         | Serial Data In            | Ι <sup>P</sup> | In Host Mode, SDI is the serial data input for the host serial control port. SDI/JSEL(2) is a dual function pin.                                                                                                        |

| SDO         | Serial Data Out           | 0              | In Host Mode, SDO is the serial data output for the host serial control port. SDO/JATERR[1] is a dual function pin.                                                                                                     |

| SCLK        | Serial Clock              | Ι <sup>P</sup> | In Host Mode, SCLK is the serial clock input for the host serial control port. SCLK/JDIR is a dual function pin.                                                                                                        |

| 1           | P                         | ower Su        | pply Pins and No-Connect Pins                                                                                                                                                                                           |

| VAA         | Analog Supply             |                | +3.3 V $\pm$ 5%. Power supply pair for the analog circuitry.                                                                                                                                                            |

| GND         | Ground                    |                |                                                                                                                                                                                                                         |

| VAAT[1:4]   | Tx Driver Supply          | l              | $+3.3 \text{ V} \pm 5\%$ . Power supply pairs for the transmitter driver circuitry. These pin pairs should each be bypassed with a tantalum capacitor value of at                                                       |

| GNDT[1:4]   | Ground                    |                | least 10 μF.                                                                                                                                                                                                            |

| VAAR        | Rx Analog Supply          | 1              | + 3.3 V $\pm$ 5%. Power supply pair for the analog receiver circuitry.                                                                                                                                                  |

| GNDR        | Ground                    |                |                                                                                                                                                                                                                         |

**Table 1-1. Hardware Signal Definitions** (5 of 5)

| Pin Label | Signal Name    | 1/0 | Definition                                                                                                                                                                                        |

|-----------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAACL     | CLAD Supply    | ı   | + 3.3 V $\pm$ 5%. Power supply pair for the CLAD PLL circuitry.                                                                                                                                   |

| GNDCL     | Ground         |     |                                                                                                                                                                                                   |

| VDD       | Digital Supply | ı   | + 3.3 V + 5%. Power supply pairs for the digital circuitry.                                                                                                                                       |

| VSS       | Ground         |     |                                                                                                                                                                                                   |

| VGG       | ESD Rail       | ı   | To insure 5 V tolerance in mixed + 5 V / + 3.3 V systems, this input must be connected to + 5 V. If all logic input signals are 3.3 V levels, then this pin may be connected to the 3.3 V supply. |

| N.C.      | No Connect     | _   | No-connect pins are reserved for future device compatibility and should be left unconnected.                                                                                                      |

### NOTE(S):

- 1. I/O Types:

- i = Standard input

- I<sup>P</sup> = Input with internal pull-up resister O = Standard output

- OD = Output with open drain

- 2. Legend:

- [#] = Port number

- (#) = Bit number

## 2.0 Circuit Description

### 2.1 Overview

The CN8380 includes four identical T1/E1 transceiver channels and a common CLAD packaged in a 128-pin MQFP carrier. It is designed to interface T1/E1 framers, or to operate as a stand-alone line interface for synchronous or plesiochronous mappers and multiplexers. The CN8380 is ideal for high line density, short-haul applications that require low power (3.3 V supply) operation. The configurable T1/E1 operation and common line interface design allows support for single-board T1 and E1 designs.

Customer premise applications are supported by an on-chip JAT which conforms to AT&T PUB 62411 and a selectable transmit pulse shape which conforms to FCC Part 68, Pulse Option A. Selectable unipolar or bipolar interface options and internal ZCS encoding and decoding are useful in many multiplexer and mapper applications.

In the most simple configuration, Hardware Mode, the device is controlled using dedicated hardware control pins. In this mode, the four channels are configured globally to identical operating modes (T1, E1, transmit termination, jitter attenuators, and so on). Each channel has device pins dedicated for channel control and status, such as loopback controls, bipolar/unipolar interface modes, and loss of signal indicators. Hardware Mode is selected by pulling the HM pin high.

Host Mode allows control of the device through a 4-line serial port. In this mode, all control and status functions can be accessed using internal registers. Several additional features are also available in Host Mode, such as individual channel operating mode configuration (T1/E1, transmit termination, jitter attenuators, etc.) and programmable CLAD output frequencies. Host Mode is selected by grounding the HM pin.

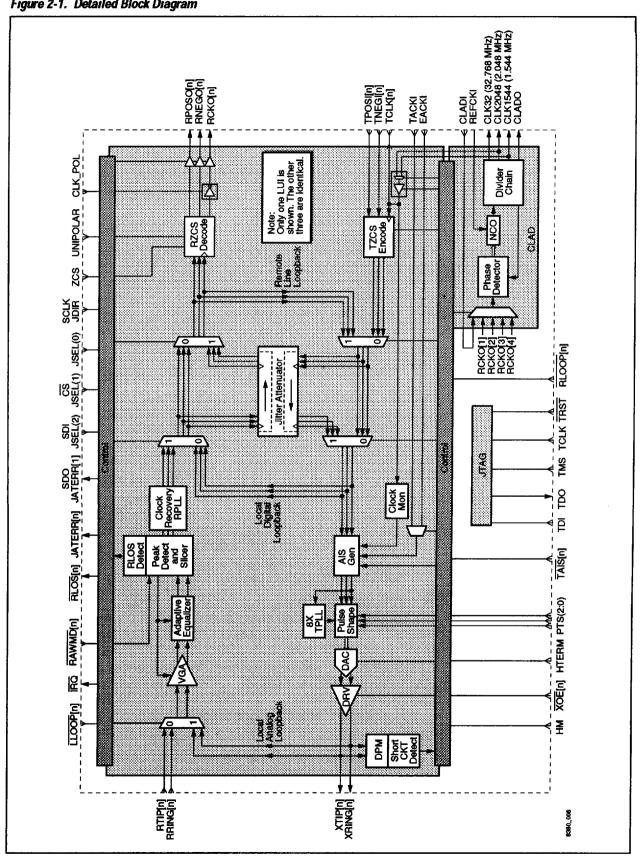

The CN8380 incorporates printed circuit board testability circuits in compliance with IEEE Std P1149.1a–1993, IEEE Standard Test Access Port and Boundary–Scan Architecture, commonly known as JTAG (Joint Test Action Group). A detailed block diagram is displayed in Figure 2-1.

Figure 2-1. Detailed Block Diagram

2.2 Configuration and Control

## 2.2 Configuration and Control

### 2.2.1 Hardware Mode

In Hardware Mode, the device is controlled using dedicated hardware control pins. In this mode, the four channels are configured globally to identical operating modes (T1, E1, transmit termination, jitter attenuators, and so on). Each channel has device pins dedicated for channel control and status, such as loopback controls, bipolar/unipolar interface modes, and loss of signal indicators. Refer to Table 1-1. *Hardware Signal Definitions*, for a description of all hardware pins. Hardware Mode is selected by pulling the HM pin high.

### 2.2.2 Host Mode

In Host Mode, control of the device is through a four-line serial port. In this mode, all control and status functions can be accessed using internal registers. Refer to Chapter 3.0, *Registers*, for a description of each register. Host Mode is selected by grounding the HM pin.

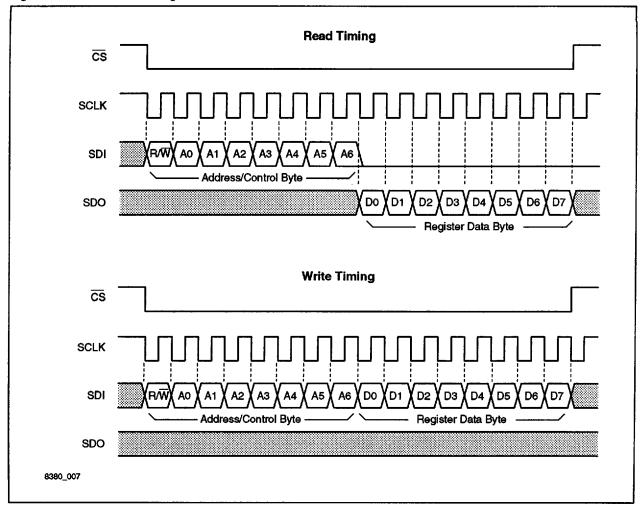

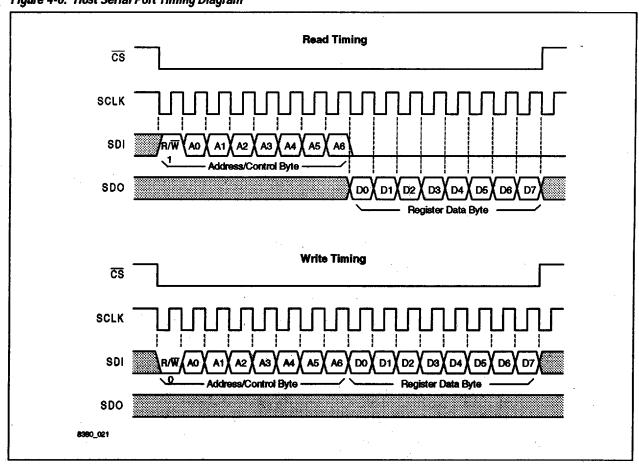

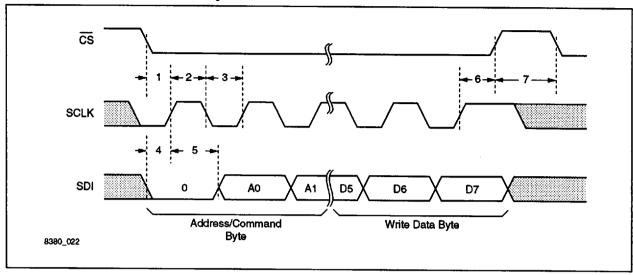

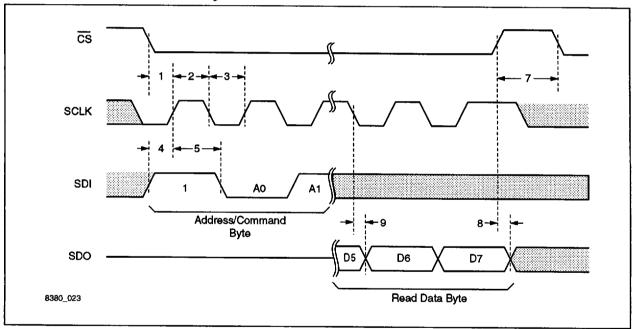

### 2.2.3 Host Serial Control Interface

The CN8380 serial interface is a four-wire, slave interface which allows a host processor or framer with a compatible master serial port to communicate with the LIU. This interface allows the host to control and query the CN8380 status by writing and reading internal registers. One 8-bit register in the LIU can be written via the SDI pin or read from the SDO pin at the clock rate determined by SCLK. The serial port is enabled by pulling the chip select pin,  $\overline{\text{CS}}$ , active (low) during the read and write cycles. Refer to Figure 2-2 for host serial port signals.

The serial interface uses a 16-bit process for each write or read operation. During a write or read operation, an 8-bit control word, consisting of a read/write control bit (R/W) and a 7-bit LIU register address (A[6:0]) is transmitted to the LIU using the SDI pin. If the operation is a write operation (R/W = 0), an 8-bit register data (D[7:0]) byte follows the address on the SDI pin. This data is received by the CN8380 and stored in the addressed register. If the operation is a read operation (R/W = 1), the CN8380 outputs the addressed register contents on the SDO pin. The signal input on SDI is sampled on the SCLK falling edge, and data output on SDO changes on the SCLK rising edge.

### 2.2 Configuration and Control

Figure 2-2. Host Serial Port Signals

### 2.2.4 Reset

The CN8380 supports three reset methods: power-on reset, hard reset initiated by the RESET pin, and soft reset initiated by the RESET bit in the Global Configuration Register [GCR; addr 01]. In Host Mode, all three reset methods produce the same results as listed below. In Hardware Mode, power-on reset and hard reset produce the same results as shown; and soft reset is not applicable. After RESET is complete, the following is true:

### Hardware Mode

Digital receiver outputs (RPOSO[1:4] and RNEGO[1:4], RCKO[1:4]) are enabled.

Transmitter line outputs (XTIP[1:4] and XRING[1:4]) are enabled (controlled by XOE).

### **Host Mode**

Digital receiver outputs (RPOSO[1:4] and RNEGO[1:4], RCKO[1:4]) are three-stated.

Transmitter line outputs (XTIP[1:4] and XRING[1:4]) are three-stated.

2.2 Configuration and Control

### Hardware Mode

CLK1544, CLK2048, and CLADO clock outputs are enabled.

Host Mode

CLK1544, CLK2048, and CLADO clock outputs are three-stated.

Transmitter clocks, TCLK[1:4], are configured as inputs.

Transmitter clocks, TCLK[1:4], are configured as inputs.

The IRQ pin is enabled (controlled by DPM).

The IRQ pin is three-stated.

All interrupt sources are disabled.

All configuration registers are set to default values as listed in Section 3.1, *Address Map.*

### 2.2.4.1 Power-on Reset

An internal power-on reset process is initiated during power-up. When VDD has reached approximately 2.6 V, the internal reset process begins and continues for 300 ms maximum if REFCLK is applied. If REFCLK is not present, the CN8380 remains in the reset state.

#### 2.2.4.2 Hard Reset

Hard reset is initiated by bringing the RESET pin active (low). Once initiated, the internal reset process completes in 5  $\mu$ s maximum. If the RESET pin is held active continuously, the clock and data outputs and the  $\overline{IRQ}$  pin remain three-stated. The following output pins are forced to high impedance while RESET is held active:

| RPOSO[1:4]  | CLADO       |

|-------------|-------------|

| RNEGO[1:4]  | TCLK[1:4]   |

| RCKO[1:4]   | ĪRQ         |

| XTIP[1:4]   | RLOS[1:4]   |

| XRING[1:4:] | JATERR[1:4] |

| CLK1544     | SDO         |

| CLK2048     | TDO         |

### 2.2.4.3 Soft Reset

In Host Mode, soft reset is initiated by writing a one to the RESET bit in the Global Configuration register [addr 01]. The RESET bit is self-clearing. Once initiated, the internal reset process completes in 5  $\mu$ s maximum and the device enters normal operation.

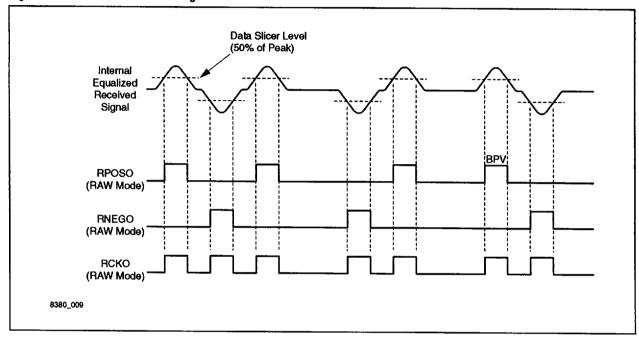

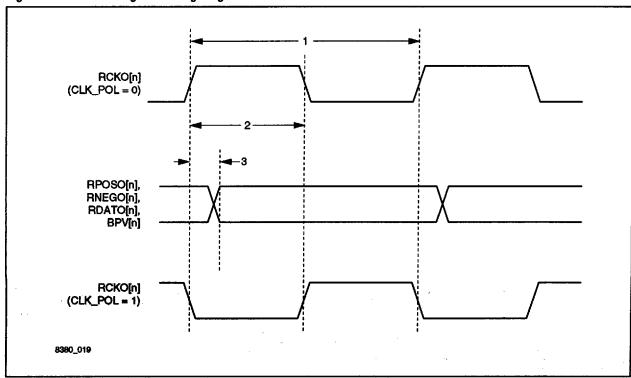

### 2.3 Receiver

Bipolar AMI pulses are input on the receiver input pins, RTIP[n] and RRING[n]. The receiver recovers clock and data from the AMI signal which has been attenuated and distorted due to the line characteristics. The AMI pulses are converted into bipolar or unipolar, NRZ data and output on RPOSO[n] and RNEGO[n], along with the recovered clock on RCKO[n]. Figure 2-3 illustrates the relationship between the AMI received signal, the recovered clock, and the data outputs. This section discusses each receiver block from the line input to the digital outputs.

Data Slicer Level (50% of Peak) Internal Equalized Received Signal **RCKO BPV RPOSO** (Bipolar) **RNEGO** (Bipolar) **RDATO** (Unipolar) 0 0 1 BPV (Unipolar)

Figure 2-3. Receiver Signals

## 2.3.1 Data Recovery

The receiver recovers data by normalizing the input signal with an automatic gain control (AGC) circuit, removing distortion with an equalizer, and extracting the data using a data slicer. The transfer function of the equalizer is adjusted based on the average peak value of the input signal. The AGC maintains the equalizer's average peak output level to a constant value. The data slicer compares the equalizer output to a threshold value equal to 50% of the average peak equalizer output level and produces both positive and negative pulse detect signals. The data slicer outputs are re-timed using the recovered clock and routed to the RZCS decoder (or to the JAT).

2.3 Receiver

## 2.3.1.1 Raw Receive

Optionally, the data slicer outputs, before re-timing, can be routed directly to the RPOSO and RNEGO digital output pins. This option (raw receive mode) is selected by asserting the RAWMD[n] pin in Hardware Mode or by asserting the RAWMD register bit [RLIU\_CR; addr n1] in Host Mode. In raw receive mode, RCKO is replaced by the logical OR of the RPOSO and RNEGO output signals.

This mode is useful in applications which provide external clock and data recovery. Figure 2-4 illustrates the raw mode receiver signals.

Figure 2-4. Raw Mode Receiver Signals

### 2.3.1.2 Sensitivity

The receiver is capable of recovering signals with cable attenuation in the range of +3 to -12 dB in E1 and T1 modes. The receiver is configured by setting register bits appropriately in Host Mode or by setting configuration pins in Hardware Mode. See Table 2-1for line compatible modes.

Table 2-1. Line Compatible Modes

| Mode                  | Receiver Sensitivity | RALOS<br>Threshold | Squeich<br>Threshold | RLOS<br>Detect |

|-----------------------|----------------------|--------------------|----------------------|----------------|

| T1                    | +3 dB to -12 dB      | -18 dB             | –18 dB               | 100 zeros      |

| T1/E1 20 dB<br>Bridge | -17 dB to -26 dB     | NA                 | NA                   | 100 zeros      |

| E1                    | +3 dB to -12 dB      | -18 dB             | –18 dB               | 32 zeros       |

### 2.3.1.3 Bridge Mode

In Host Mode, the receiver allows interfacing to network test (MON) points which are resistively attenuated with resisters in series with transmit and receive Tip and Ring signals. The Bridge Monitor Level is -20 dB. Bridge operation is enabled by setting register bit ATTEN [addr n1] to 1. In this mode, RALOS detection and squelch operation are disabled.

#### 2.3 Receiver

## 2.3.1.4 Loss Of Signal Detector

The Receive Loss of Signal (RLOS) Detector monitors both consecutive 0s and signal level. Receive Analog Loss Of Signal (RALOS) is declared when RTIP/RRING input signal amplitude is a certain level (RALOS level) below the nominal receive level for at least 1 ms (2 ms maximum). RALOS status is cleared as soon as pulses above the RALOS level are detected.

In Host Mode, the received data can be replaced with all 0s (squelched) if the receive level is also below the SQUELCH level. Squelch is enabled in register RLIU\_CR [addr n1]. In Host Mode, RALOS real time status is reported in the ALARM [addr n5] register; and an interrupt status bit is available in the ISR [addr n6] register. Also, RALOS is indicated on the  $\overline{RLOS}[n]$  pin, which is the logical NOR of the RLOS[n] status and RALOS[n] status.

RLOS is declared when 100 (T1) or 32 (E1) consecutive bits with no pulses are detected. RLOS status is cleared when pulses are received with at least 12.5% pulse density (during a period of 192 bits starting with the receipt of a pulse) and where no occurrences of 100 or 32 consecutive bits with no pulses are detected. In Host Mode, RLOS real time status is reported in the ALARM register [addr n5]; and an interrupt status bit is available in the ISR register [addr n6]. Also, RLOS is indicated by a 0 level on the  $\overline{\text{RLOS}}$ [n] pin, which is the logical NOR of the RLOS[n] status and RALOS[n] status.

## 2.3.2 Clock Recovery

### 2.3.2.1 Phase Lock Loop

The Receive Phase Lock Loop (RPLL) recovers the line rate clock from the data slicer dual-rail outputs. The RPLL generates a recovered clock that tracks jitter in the data and sustains the data-to-clock phase relationship in the absence of incoming pulses. The RPLL is a digital PLL which adjusts its output phase in 1/16 unit interval (UI) steps. Consequently, the RPLL adds approximately 0.12 UI peak-to-peak jitter to the recovered receive clock.

During loss of signal (RLOS or RALOS), the RPLL maintains an output clock signal and smoothly transitions to a nominal line rate frequency determined by the CLAD input reference (selected by CMUX [GCR; addr 01] or FREE [CLAD\_CR; addr 02]). If the CLAD reference is the recovered received clock from a channel which has detected RLOS, the CLAD outputs and the recovered received clock enter a "hold-over" state to maintain the average frequency that was present just before the RLOS was detected.

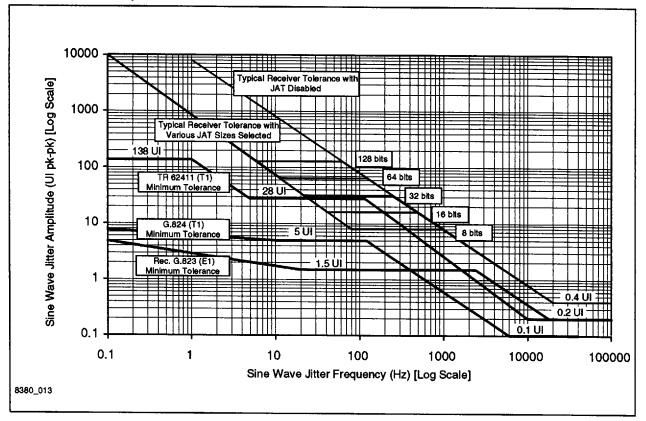

### 2.3.2.2 Jitter Tolerance

Figure 2-8, Receiver Input Jitter Tolerance, illustrates the receiver's jitter tolerance for all jitter attenuator (JAT) configurations: JAT disabled and JAT enabled in the receive path with each JAT elastic store size. The jitter tolerance of the clock and data recovery circuit alone (not including the JAT) is illustrated by the curve labeled with "JAT Disabled." The receiver meets jitter tolerance specifications TR62411, G.823, and G.824. In addition, the receiver meets jitter tolerance tests defined in ETS300 011: ISDN; Primary Rate User-Network Interface Layer 1 Specification and Test Principles.

### 2.3.3 Receive Jitter Attenuator

The data slicer outputs can be routed to the JAT before going to the RZCS decoder. The JAT attenuates clock and data jitter introduced by the line or added by the clock recovery circuit. The JAT can be placed in the receive path or transmit path, but not in both simultaneously. If the JAT is placed in the receive

2.3 Receiver

path, RCKO is replaced with the jitter attenuated clock. The JAT performance is discussed in Section 2.6, *Jitter Attenuator*.

In Host Mode, the JAT is configured for each channel independently and is put in the receive path by setting JEN and JDIR register bits to 1 [JAT\_CR; addr n0]. In Hardware Mode, the JAT is configured for all channels globally using the JSEL(2:0) and JDIR pins. Refer to Chapter 1.0, *Pin Descriptions* for details.

### 2.3.4 RZCS Decoder

The RZCS decoder decodes the dual-rail data from the data slicer or from the JAT. In T1 mode, the RZCS decoder replaces received B8ZS codes with eight 0s. In E1 mode, HDB3 codes are replaced with four 0s. The B8ZS code is 000VB0VB and the HDB3 code is X00V; where B is a normal AMI pulse, V is a bipolar violation, and X is a don't-care.

ZCS decoding (and encoding) can be enabled only if the digital interface mode is unipolar. In Host Mode, RZCS decoding (and TZCS encoding) is enabled for each channel by setting the ZCS [RLIU\_CR; addr n1] register bit to 1. In Hardware Mode, ZCS encoding/decoding is controlled globally for all channels by pulling the ZCS pin high. For the Hardware Mode pin definition, see Table 1-1.

## 2.3.5 Receive Digital Interface

The digital receiver outputs are provided on the RPOSO[n], RNEGO[n], and RCKO[n] pins, where [n] is channel number 1 to 4. The receiver outputs can be configured to operate in two modes: Bipolar NRZ format or unipolar NRZ format. In both modes, RPOSO[n] and RNEGO[n] outputs are clocked by RCKO[n], the recovered line rate clock, or the jitter attenuated clock if the JAT is enabled in the receive path. RCKO[n] polarity is configurable by the CLK\_POL pin in Hardware Mode or register bit CLK\_POL [RLIU\_CR; addr n1] in Host Mode. RPOSO[n], RNEGO[n], and RCKO[n] are three-stated during device reset.

#### 2.3.5.1 Bipolar Mode

In bipolar mode, RPOSO/RNEGO signals output received data in bipolar dual-rail format, where a high level on RPOSO indicates receipt of a positive AMI pulse, and a high level on RNEGO indicates receipt of a negative AMI pulse on RTIP/RING inputs. In bipolar mode, the RZCS decoder is not available. In Hardware Mode, bipolar operation is enabled globally for all channels by pulling the UNIPOLAR pin low. In Host Mode, bipolar operation is enabled per channel by writing a 0 to register bit UNIPOLAR [RLIU\_CR; addr n1].

### 2.3.5.2 Unipolar Mode

In unipolar mode, RPOSO/RNEGO signals are replaced by RDATO/BPV signals. AMI encoded received data is decoded and output on RDATO in NRZ format, and BPV indicates that the currently received bit is a bipolar violation. If the RZCS decoder is enabled, the BPV pin indicates only bipolar violations which are not part of a ZCS code (B8ZS or HDB3). In Hardware Mode, unipolar operation is enabled by pulling the UNIPOLAR pin high. In Host Mode, unipolar operation is enabled by writing a 1 to register bit UNIPOLAR [RLIU\_CR; addr n1].

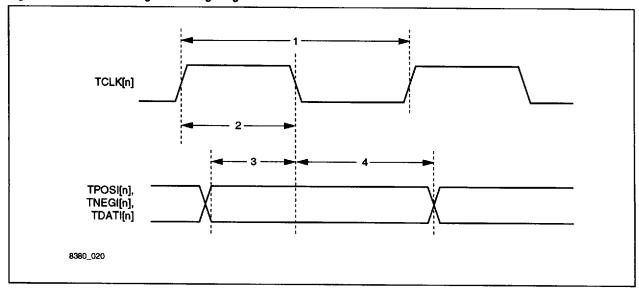

### 2.4 Transmitter

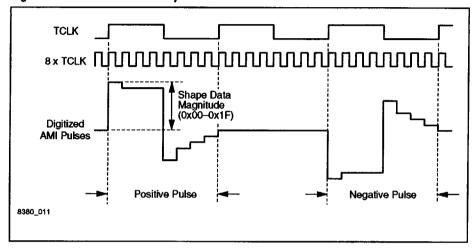

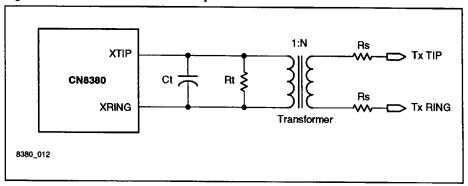

Bipolar or unipolar, NRZ digital transmit data are input on TPOSI and TNEGI using the transmit clock TCLK. Data are converted into AMI pulses, shaped according to required standards, and transmitted to the line. Figure 2-5 illustrates the relationship between the AMI transmitted signal, the transmit clock, and the data inputs. This section discusses each transmitter block, from the digital inputs to the line output.

Figure 2-5. Transmitter Signals

## 2.4.1 Transmit Digital Interface

The digital transmitter inputs, TPOSI[n] and TNEGI[n], accept bipolar or unipolar NRZ formatted data for transmission and are sampled by the falling edge of TCLK[n], where [n] is channel number 1 to 4. TCLK[n] is the line rate transmit clock and is normally supplied externally from a line rate source, but can also be sourced internally (only in Host Mode) from the CLAD. If sourced internally, TCLK[n] is configured as an output to provide the line rate clock to external circuitry. TCLK[n] direction is configured globally for all channels by writing to register bit TCLK\_I/O [GCR; addr 01].

### 2.4.1.1 Bipolar Mode

In bipolar mode, TPOSI/TNEGI inputs accept bipolar dual-rail transmit data where a high on TPOSI causes a positive output pulse and a high on TNEGI causes a negative output pulse on XTIP/XRING. In this mode, the TZCS encoder is not available. In Hardware Mode, bipolar operation is enabled globally for all channels by pulling the UNIPOLAR pin low. In Host Mode, bipolar operation is

2.4 Transmitter

enabled per channel by writing a 0 to register bit UNIPOLAR [RLIU\_CR; addr n1].

### 2.4.1.2 Unipolar Mode

In unipolar mode, TPOSI is replaced with TDATI and accepts unipolar NRZ-formatted transmit data. TNEGI is not used in this mode. A high on TDATI causes an AMI pulse to be transmitted to the line. In this mode, the TZCS encoder can be enabled to provide B8ZS or HDB3 zero code suppression. In Hardware Mode, unipolar operation is enabled globally for all channels by pulling the UNIPOLAR pin high. In Host Mode, unipolar operation is enabled per channel by writing a 1 to register bit UNIPOLAR [RLIU\_CR; addr n1].

### 2.4.2 TZCS Encoder

If enabled, the TZCS encoder encodes unipolar transmit data on TDATI with B8ZS (T1) or HDB3 (E1) line coding. In T1 mode, eight consecutive 0s are replaced with 000VB0VB; and in E1 mode, four consecutive 0s are replaced with X00V; where B is a normal AMI pulse, V is a bipolar violation, and X is a Don't Care. These are standard T1 and E1 line code options.

ZCS encoding (and decoding) can be enabled only if the digital interface mode is unipolar. In Host Mode, TZCS encoding (and RZCS decoding) is enabled for each channel by setting the ZCS [RLIU\_CR; addr n1] register bit to 1. In Hardware Mode, ZCS encoding/decoding is controlled globally for all channels by pulling the ZCS pin high. For the Hardware Mode pin definition, refer to Table 1-1.

### 2.4.3 Transmit Jitter Attenuator

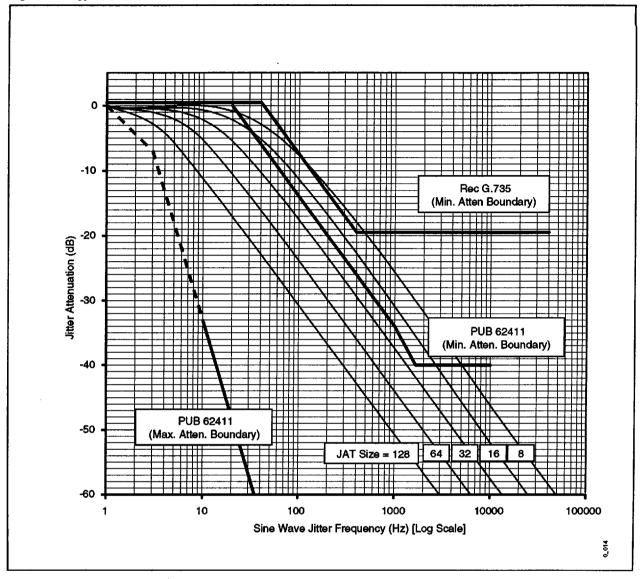

Transmit data from the TZCS encoder can be routed to the JAT before going to the AIS Generator. The JAT attenuates clock and data jitter from the transmit inputs or from the receiver if Remote Line Loopback (RLL) is active. The JAT can be placed in the receive path or transmit path, but not both simultaneously. If the JAT is placed in the transmit path, the jitter attenuated clock becomes the transmit clock for downstream circuits.

In Host Mode, the JAT is configured for each channel independently and is put in the transmit path by setting the JEN register bit to 1 and the JDIR register bit to 0 [JAT\_CR; addr n0]. In Hardware Mode, the JAT is configured for all channels globally using the JSEL(2:0) and JDIR pins. For pin definitions, refer to Chapter 1.0, *Pin Descriptions*; for JAT transfer characteristics, refer to Figure 2-9; and for more information on loopbacks, refer to Section 2.5, *Loopbacks*.

### 2.4.4 All 1s AIS Generator

The transmit data can be replaced with unframed all 1s for transmitting the alarm indication signal (AIS). This includes replacing data supplied from TPOSI[n]/TNEGI[n] pins and from the receiver during RLL. AIS transmission does not affect transmit data that is looped back to the receiver during Local Digital Loopback (LDL). This allows LDL to be active simultaneously with the transmission of AIS. AIS is used to maintain a valid signal on the line and to inform downstream equipment that the transmit data source has been lost. AIS transmission can be done manually or automatically when loss of transmit clock is detected. A clock monitor circuit allows manual or automatic switching of the transmit clock to an alternate AIS clock.

2.4 Transmitter

In Hardware Mode, AIS can be controlled only manually by pulling the TAIS[n] hardware pin low. If TCLK[n] is present, then it is used to transmit AIS. If TCLK[n] is not present (for two clock periods), the alternate AIS clock on either TACKI (T1 Mode) or EACKI (E1 Mode) is used. The AIS transmit clock switches back to TCLK[n] when the TCLK[n] signal returns.

In Host Mode, AIS can be transmitted using the TAIS[n] hardware pins or the TAIS register bit, or automatically by enabling the AUTO\_AIS register bit. AIS clock switching can be enabled by using the AISCLK register bit. Setting AISCLK to 1 forces the use of the alternate AIS clock on either TACKI (T1 Mode) or EACKI (E1 Mode) pins when transmitting AIS. If AUTO\_AIS is set to 1, AIS is automatically transmitted when the clock monitor detects loss of clock on TCLK[n]. When using automatic AIS transmission, the user should also enable the AISCLK bit and provide an alternate clock source to insure that AIS will be transmitted. CLAD output clocks CLK2048 and CLK1544 can be connected externally to EACKI and TACKI alternate AIS clock inputs for this purpose. Setting register bit TAIS\_PE to 1 disables the TAIS register bit and allows manual transmission of AIS using the TAIS[n] hardware pins. Refer to LIU\_CTL [addr n3] in Chapter 3.0, Registers, and to Table 1-1, Hardware Signal Definitions.

If TAIS is activated when Remote Line Loopback is active, AIS is transmitted using the received clock (or JCLK if the JAT is enabled in the receive direction). Table 2-2 lists transmitter operating modes resulting from various configuration settings and input conditions.

Table 2-2. Transmitter Operating Modes

| Configuration and Input Status |      |      |          | Transmitter Mode |                  |                   |

|--------------------------------|------|------|----------|------------------|------------------|-------------------|

| REOOP<br>W/LLOOP=0)            | TLOC | TAIS | AUTO_AIS | AISCLK           | Transmit<br>Data | Transmit<br>Clock |

| 0                              | Х    | 0    | 0        | Х                | Tx Data          | TCLK              |

| 0                              | Х    | 1    | х        | 0                | AIS              | TCLK              |

| 0                              | Х    | 1    | Х        | 1                | AIS              | TACKI/EACKI       |

| 0                              | 0    | 0    | 1        | Х                | Tx Data          | TCLK              |

| 0                              | 1    | 0    | 1        | 0                | AIS              | TCLK              |

| 0                              | 1    | 0    | 1        | 1                | AIS              | TACKI/EACKI       |

| 1                              | Х    | 0    | X        | х                | Rx Data          | RCLK              |

| 1                              | Х    | 1    | х        | Х                | AIS              | RCLK              |

2.4 Transmitter

## 2.4.5 Pulse Shaper

All transmit pulse shaping to meet E1 and T1 transmission standards is done internally, eliminating the need for external shaping circuitry. The pulse shape block receives bipolar NRZ transmit data, produces a set of eight 5-bit values which define the pulse shape, and converts the shape values into an analog pulse using a DAC. Table 2-3 lists the transmit pulse template selections and applications.

Table 2-3. Transmit Pulse Configurations

| Application                                      | Line Rate | Line Length | Hardware Mode<br>Configuration<br>PTS(2:0) | Host Mode Configuration [TLIU_CR; addr n2] PULSE(2:0) |

|--------------------------------------------------|-----------|-------------|--------------------------------------------|-------------------------------------------------------|

| DOV 4                                            | T1        | 0–133 ft.   | 000                                        | 000                                                   |