### Data Separator with Buit-in Read Pulse Detector and (1, 7) Encoder/Decoder

The HD153014RF is a data separator with built-in read pulse detector and (1, 7) run-length-limit encoder/decoder developed for use in magnetic disk drives. In read mode it decodes the readback waveform output from the read/write amplifier to an NRZ signal. In write mode it encodes an NRZ signal from the controller to (1, 7) RLL coded data.

#### **Features**

- Data transfer rate: 10 to 24 Mbps.

- Data transfer clock frequency: 1.5 × data transfer rate.

- Built-in AGC amplifier for stable reproduction despite varying media and head characteristics.

- Gate generator enables incorrect read pulse problems that occur with time-domain filtering to be avoided by appropriate level setting. Head resolution can be increased without incorrect read pulse worries.

- AGC amplifier gain can be set to zero during writing.

- Servo signal full wave rectification. Circuitry for two sample and hold channels built in.

- Dual-mode phase detector compares both phase and frequency to ensure a wide capture range.

- High-speed acquisition can be combined with highly stable reproduction by switching between normal-gain and high-gain modes, and by switching loop filter constants.

- VCO oscillation timing capacitor is built in for excellent noise immunity.

- PLL characteristic frequency and damping rate are defined without (1, 7) RLL signal cycle (2T to 8T).

- Encoding and decoding: IBM (1, 7) RLL code.

- Built-in write precompensation with programmable delay.

- Decode window centering adjustment and monitoring functions

- Single 5 V power supply.

- QFP-80 package suitable for compact surface mounting (resin size: 14 mm × 14 mm).

- TTL compatible logic inputs and outputs.

- BiCMOS process achieves high speed with low power dissipation (475 mW).

### **Ordering Information**

| Type No.    | Package                  |

|-------------|--------------------------|

| HD153014RF  | 80 pin QFP (FP-80A)      |

| HD153014RTF | 80 pin Thin QFP (TFP-80) |

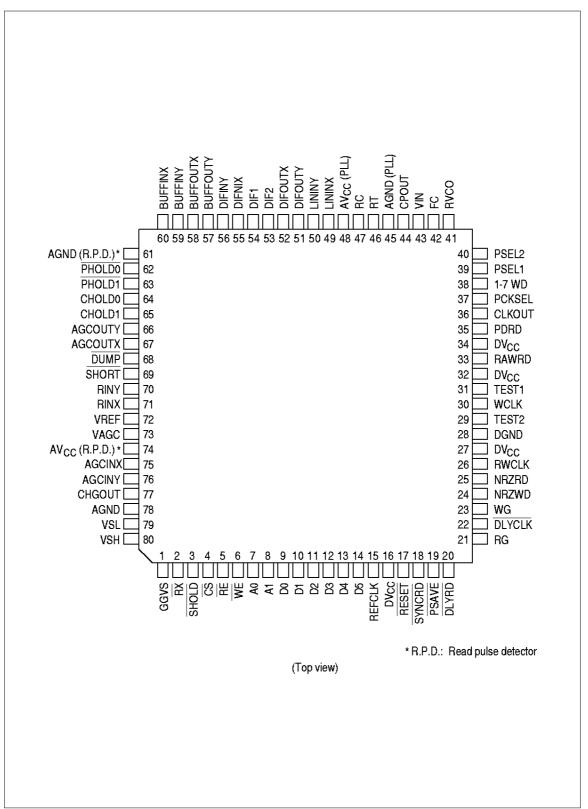

### Pin Arrangement

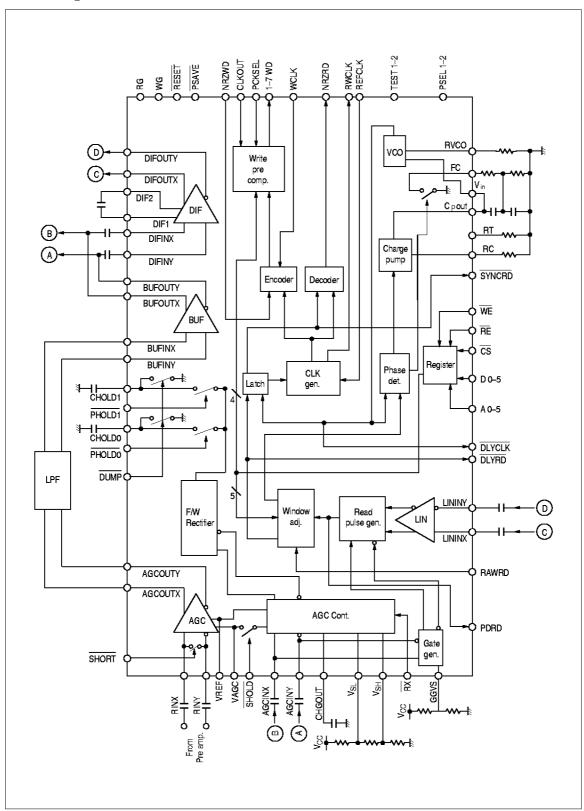

### **Block Diagram**

# HD153014RF/RTF

## Specifications

| No. | Item                               | Specification                                        |

|-----|------------------------------------|------------------------------------------------------|

| 1   | Data transfer rate                 | 24 Mbps max.                                         |

| 2   | Encoding and decoding              | (1, 7) RLL code                                      |

| 3   | Read pulse detector                | On-chip                                              |

| 4   | Phase-lock acquisition time        | 6 Bytes or less                                      |

| 5   | Disk format support                | Hard sectoring                                       |

| 6   | Write precompensation              | On-chip (programmable)                               |

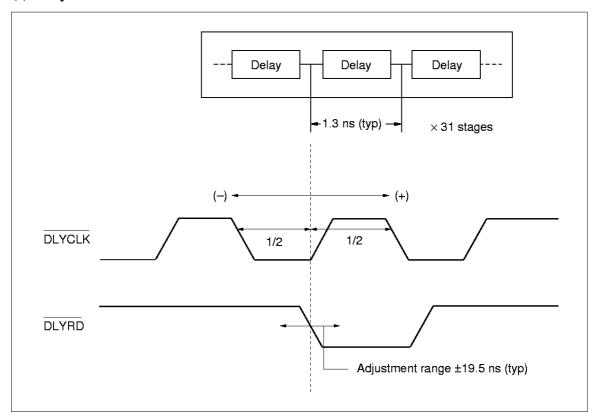

| 7   | Decode window centering adjustment | Digital selection: 5 bits, 32 settings, 1.3 ns steps |

| 8   | Power dissipation                  | 475 mW during operation                              |

| 9   | Inputs and outputs                 | TTL compatible                                       |

| 10  | Power supply                       | Single 5 V supply                                    |

## **Pin Functions**

| Pin name | Pin No. | Туре | Function                                                                                                                                                                                                                                                                                                                 |

|----------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAWRD    | 33      | In   | Input line for (1, 7) encoded pulses when only the HD153014 RF's VFO and encoder/decoder are used, or for checking data separator operation. The leading edge of the input pulse indicates magnetic reversal. The PLL is phase-synchronized with this leading edge. The polarity of this input can be selected by PSEL2. |

| WG       | 23      | ln   | High input selects write mode, in which the NRZ write data signal is converted to (1, 7) code and output.                                                                                                                                                                                                                |

| RG       | 21      | ln   | High input selects read mode, in which (1, 7) encoded data read from disk are converted to an NRZ signal and output. This signal switches the clock for counters and internal circuits, enables NRZ signal output, and begins phase synchronization of the VFO with the (1, 7) coded data.                               |

| CS       | 4       | ln   | Control input for the HD153014RF's internal registers. HD153014RF registers connected to the microcontroller's bus are selected when this line is driven low.                                                                                                                                                            |

# HD153014RF/RTF

| Pin name       | Pin No. | Туре   | Function                                                                                                                                                                                                                                               |

|----------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WE             | 6       | ln     | Control input for the HD153014RF's internal registers. Data on the microcontroller's bus are written on the rising edge of WE to the HD153014RF register selected by address input. CS must be low.                                                    |

| RE             | 5       | ln     | Control input for the HD153014RF's internal registers. While this line is low, contents of the HD153014RF register selected by address input are output on the microcontroller's bus, permitting register contents to be verified. CS must be low.     |

| D0 to D5       | 9 – 14  | In/Out | Data lines for the HD153014RF's internal registers, normally connected to the microcontroller's data bus. Input lines when RE is high. Output lines when RE is low.                                                                                    |

| A0 to A1       | 7 – 8   | ln     | Address input lines for the HD153014RF's internal registers, normally connected to the microcontroller's address bus.                                                                                                                                  |

| PSAVE          | 19      | ln     | Low input halts operation of logic circuits to reduce power dissipation. The read pulse detector continues to operate, and servo information can be read out. Keep this line high during normal operation.                                             |

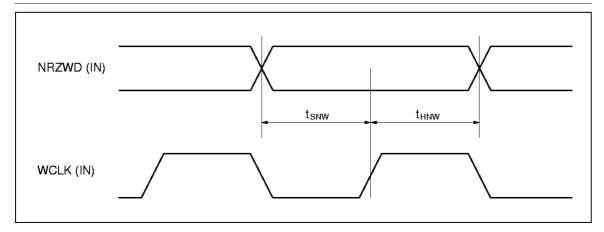

| WCLK           | 30      | ln     | Apply a clock signal synchronized with the NRZ write data input to NRZWD. Connect this input line to the HD153014RF's RWCLK output line. The input to NRZWD must then be synchronized with the RWCLK output.                                           |

| NRZ <b>W</b> D | 24      | ln     | Input line for the NRZ signal to be written to disk. Must be synchronized with the clock signal input to WCLK. The HD153014RF inverts the input on this line, then converts it to (1, 7) code.                                                         |

| RESET          | 17      | ln     | Low input initializes internal circuits, and locks the built-in VCO to its center frequency. Drive this line low at power-up.  Also, the AGC loop is set to the off state.  Keep this line high during normal operation.                               |

| REFCLK         | 15      | ln     | Input line for the HD153014RF's reference clock. When not reading data, the VCO is synchronized with this reference clock. Data writing is also clocked by this reference clock. Apply a clock signal with frequency 1.5 times the data transfer rate. |

| PCKSEL         | 37      | ln     | Control input line for the CLKOUT line used for external write precompensation. The CLKOUT line is enabled when PCKSEL is driven high.  Also, when low, internal precompensation is performed.                                                         |

# HD153014RF/RTF

| Pin name | Pin No. | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

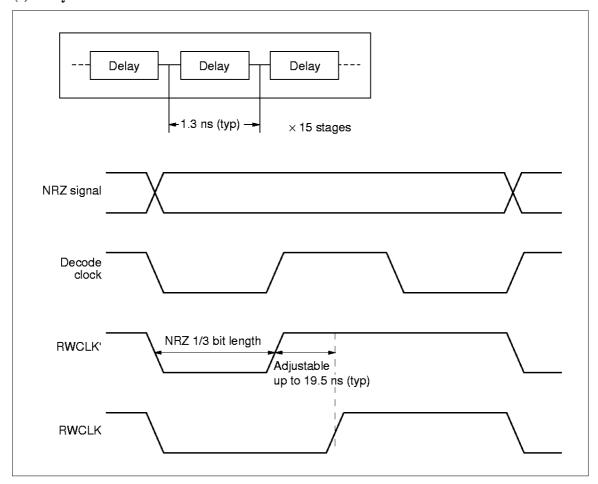

| DLYRD    | 20      | Out  | Decode window adjustment monitor output. Low output on this line corresponds to 1s in (1, 7) code read from disk. During decode window adjustment, set the falling edge of this pin's output to be in between one falling edge and the next of the DLYCLK output (i.e., in the center of a single cycle). DLYRD output is enabled by low input on the TEST2 test mode selection line. See 1. Test Mode Settings on page 10 for details.                                                                                                                  |

| DLYCLK   | 22      | Out  | Decode window adjustment monitor output. Provides clock output synchronized with the (1, 7) codes read from disk. The (1, 7) codes can be latched on this clock. During decode window adjustment, set the falling edge of this pin's output to be in between one falling edge and the next of the DLYRD output (i.e., in the center of a single cycle).  DLYCLK output is enabled by low input on the TEST2 test mode selection line. See 1. Test Mode Settings on page 10 for details.                                                                  |

| SYNCRD   | 18      | Out  | Decode window adjustment monitor output. (1, 7) codes read from the disk are latched on the decode clock and output on this line. SYNCRD output is equivalent to capturing the (1, 7) codes output from DLYRD on the DLYCLK output. Use this line to monitor window margin tests. SYNCRD output is enabled by low input on the TEST2 test mode selection line. See 1. Test Mode Settings on page 10 for details.                                                                                                                                         |

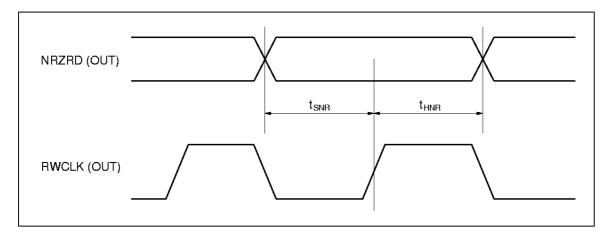

| NRZRD    | 25      | Out  | (1, 7) codes read from the disk are converted to an NRZ signal and output on this line. The NRZRD signal is synchronized with the RWCLK signal.                                                                                                                                                                                                                                                                                                                                                                                                          |

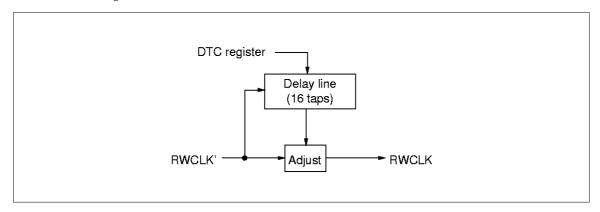

| RWCLK    | 26      | Out  | In read mode, a clock signal synchronized with the converted NRZ read data is output on this line. At other times, a reference clock is output for input by the disk controller. In read mode, the disk controller should latch the NRZ read data on the RWCLK output. Connect RWCLK to the HD153014RF's WCLK line. The signal input at NRZWD must then be synchronized with the RWCLK output. RWCLK output is free of glitches at clock switchover. The duty cycle of the RWCLK output can be selected by bits 0 to 3 in the HD153014RF's DTC register. |

| CLKOUT   | 36      | Out  | Clock output used in write mode for external write precompensation. The clock signal output on this line is synchronized with the 1, 7WD output. Output on this line is enabled when PCKSEL input is high.                                                                                                                                                                                                                                                                                                                                               |

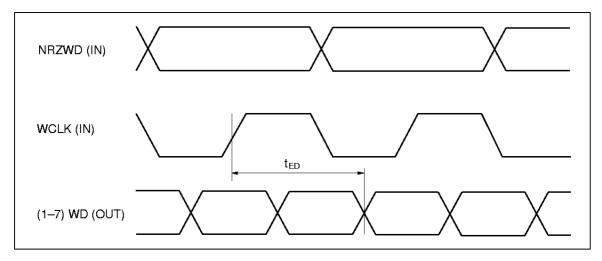

| 1–7WD    | 38      | Out  | Output signal to be written to disk, consisting of (1, 7) codes obtained by encoding the NRZ signal. The polarity of the output on this line can be selected by PSEL1 input. For external write precompensation, output on the CLKOUT line is synchronized with the 1, 7WD output.                                                                                                                                                                                                                                                                       |

# HD153014RF/RTF

| Pin name       | Pin No.  | Туре                                | Function                                                                                                                                                                                                                                      |                                                                                                   |

|----------------|----------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| PSEL1          | 39       | ln                                  | Input on this line selects the polarity                                                                                                                                                                                                       | of 1-7WD.                                                                                         |

|                |          |                                     | 1,7WD output polarity                                                                                                                                                                                                                         | PSEL1                                                                                             |

|                |          |                                     | Active high                                                                                                                                                                                                                                   | High                                                                                              |

|                |          |                                     | Active low                                                                                                                                                                                                                                    | Low                                                                                               |

|                |          |                                     | Note: Drive lines 27 and 32 high, or                                                                                                                                                                                                          | leave them unconnected.                                                                           |

| PSEL2          | 40       | In                                  | Input on this line selects the input po                                                                                                                                                                                                       | plarity on RAWRD of (1, 7)                                                                        |

|                |          |                                     | RAWRD input polarity                                                                                                                                                                                                                          | PSEL2                                                                                             |

|                |          |                                     | Active high                                                                                                                                                                                                                                   | High                                                                                              |

|                |          |                                     | Active low                                                                                                                                                                                                                                    | Low                                                                                               |

|                |          |                                     | Note: RAWRD input is active when lines 27 and 32 high, or leave them                                                                                                                                                                          |                                                                                                   |

| TEST1<br>TEST2 | 31<br>29 | ln                                  | Input lines for selecting decode wind adjustment mode and other test mode Registers, 1. Test Mode Settings".                                                                                                                                  |                                                                                                   |

| PDRD           | 35       | Out                                 | Output line for the data read from dis                                                                                                                                                                                                        | sk as reshaped into digital                                                                       |

| RVCO           | 41       | External component connection       | Connect a resistor to set the center to The resistance value depends on the                                                                                                                                                                   |                                                                                                   |

| FC             | 42       | External<br>component<br>connection | Used to adapt the loop filter attenuation independent settings of the attenuation normal gain.  High gain: The internal transistor congrounding this line.  Normal gain: The internal transistor off, placing this line in the high-imperior. | ion for high gain and nnected to this line saturates connected to this line cuts                  |

| VIN            | 43       | External component connection       | Voltage input controlling the built-in vapplied to this line varies the VCO's Low input on the RESET line causes generated on-chip to be applied to Vmaking the VCO oscillate at its centerine should be connected to CPOUT                   | oscillation frequency.  a VCO bias voltage  IN through an analog switch, frequency. Normally this |

# HD153014RF/RTF

| Pin name             | Pin No.  | Туре                          | Function                                                                                       |                             |  |  |  |

|----------------------|----------|-------------------------------|------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|

| CPOUT                | 44       | External component connection | Current output to an external loo<br>should be connected to VIN as v                           |                             |  |  |  |

| RT                   | 46       | External component connection | Connect a resistor to set the T/I feedback gain to 1 (nominal). The on the data transfer rate. |                             |  |  |  |

| RC                   | 47       | External component connection | Connect a resistor to set the chafor high gain. The resistance valuathe charge pump.           |                             |  |  |  |

| RINX<br>RINY         | 71<br>70 | Differen-<br>tial input       | Differential input lines for the sign recording medium.                                        | nal read from the           |  |  |  |

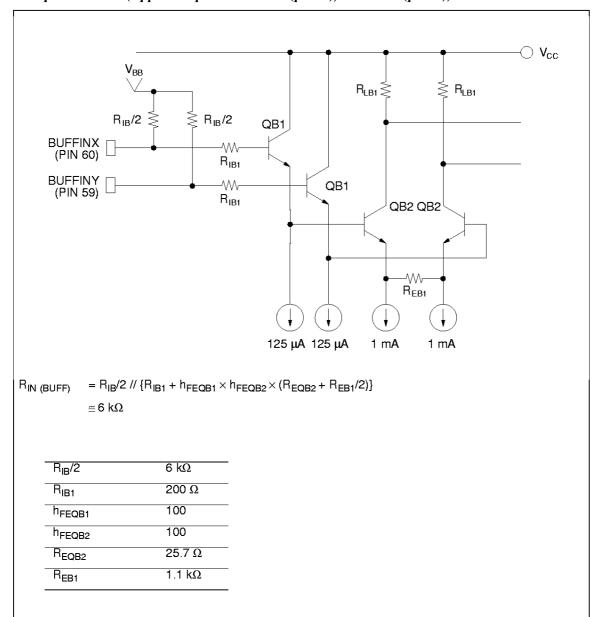

| BUFFINX<br>BUFFINY   | 60<br>59 | Differen-<br>tial input       | Differential input lines for the low-pass filter (LPF) buffer amplifier.                       |                             |  |  |  |

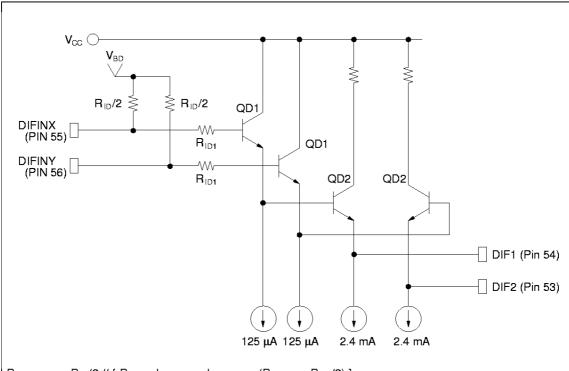

| DIFINX<br>DIFINY     | 55<br>56 | Differen-<br>tial input       | Differential input lines for the differentiating amplifier.                                    |                             |  |  |  |

| LININX<br>LININY     | 49<br>50 | Differen-<br>tial input       | Differential input lines for the zer                                                           | o-crossing comparator.      |  |  |  |

| AGCINX<br>AGCINY     | 75<br>76 | Differen-<br>tial input       | Differential input lines for the AGC output amplitude detector.                                |                             |  |  |  |

| RX                   | 2        | In                            | TTL-level input that switches the                                                              | AGC loop on or off.         |  |  |  |

|                      |          |                               | RX input                                                                                       | AGC loop                    |  |  |  |

|                      |          |                               | High                                                                                           | AGC loop on                 |  |  |  |

|                      |          |                               | Low                                                                                            | AGC loop off                |  |  |  |

| SHOLD                | 3        | ln                            | TTL-level input that locks the AG goes low, the gain is locked at its                          |                             |  |  |  |

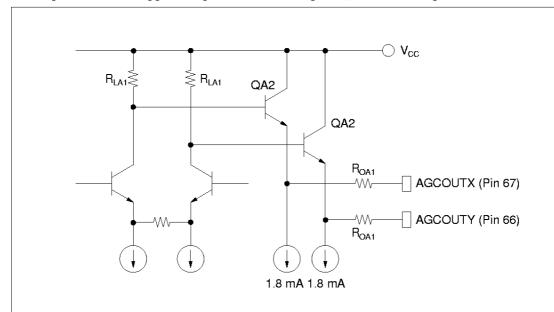

| AGCOUTX<br>AGCOUTY   | 67<br>66 | Differen-<br>tial output      | Differential output lines for emitted the AGC amplifier.                                       | er-follower output from     |  |  |  |

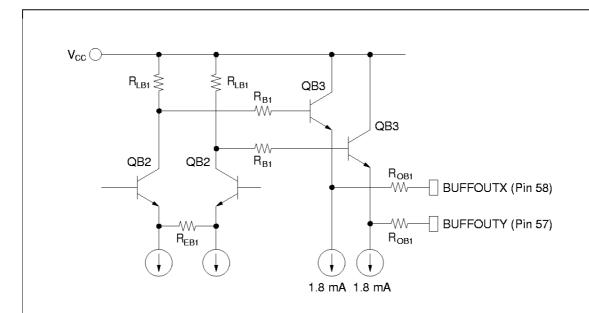

| BUFFOUTX<br>BUFFOUTY | 58<br>57 | Differen-<br>tial output      | Differential output lines for emitte low-pass filter buffer amplifier.                         | er-follower output from the |  |  |  |

| DIFOUTX<br>DIFOUTY   | 52<br>51 | Differen-<br>tial output      | Differential output lines for emitte<br>the differentiating amplifier.                         | er-follower output from     |  |  |  |

| DIF1<br>DIF2         | 54<br>53 | External component connection | Connect a resistor and capacitor frequency and voltage gain of the                             |                             |  |  |  |

| HD153014                  | IRF/RT               | F                             | HD153014RF/RTI                                                                                                                                                                                                            |  |  |  |

|---------------------------|----------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Functio<br>Pin name   | ns (cont)<br>Pin No. | Туре                          | Function                                                                                                                                                                                                                  |  |  |  |

| VSL                       | 79                   | External component connection | Voltage input line for setting the slice voltage of the AGC output amplitude detector. Corresponds to the discharge current threshold.                                                                                    |  |  |  |

| VSH                       | 80                   | External component connection | Voltage input line for setting the slice voltage of the AGC output amplitude detector. Corresponds to the charge current threshold.                                                                                       |  |  |  |

| CHGOUT                    | 77                   | External component connection | Current output line for the AGC output amplitude detector.                                                                                                                                                                |  |  |  |

| GGVS                      | 1                    | External component connection | Voltage input line for setting the gate generator's slice level.                                                                                                                                                          |  |  |  |

| <b>V</b> REF              | 72                   | Monitor<br>line               | Monitor line for the AGC amplifier reference voltage.                                                                                                                                                                     |  |  |  |

| VAGC                      | 73                   | Monitor<br>line               | Monitor line for the AGC amplifier gain setting voltage.                                                                                                                                                                  |  |  |  |

| PHOLD0<br>PHOLD1          | 62<br>63             | IN                            | Peak voltage sample and hold timimg control pin used during servo information read out.  When a TTL low level signal is input to this pin, the full-wave rectified output voltage sampled when this pin was high is held. |  |  |  |

| CHOLD0<br>CHOLD1          | 64<br>65             | External component connection | External capacitors are attached to these pins and used to hold the peak voltage.                                                                                                                                         |  |  |  |

| DUMP                      | 68                   | IN                            | The TTL level input signal pin for initialization of the (hold pin's) peak voltage hold circuit. Initialization is performed when this pin is pulled low.                                                                 |  |  |  |

| SHORT                     | 69                   | IN                            | Control pin for shorting AGC amp input pin through the analog switch. When this pin is pulled low, the AGC amp input will be shorted.                                                                                     |  |  |  |

| DV <sub>CC</sub>          | 16                   | Power                         | Digital V <sub>CC</sub> power supply.                                                                                                                                                                                     |  |  |  |

| DGND                      | 28                   | Power                         | Digital ground.                                                                                                                                                                                                           |  |  |  |

| AV <sub>CC</sub> (PLL)    | 48                   | Power                         | Analog V <sub>CC</sub> power supply. Powers the built-in PLL.                                                                                                                                                             |  |  |  |

| AGND (PLL)                | 45                   | Power                         | Analog ground. Powers the built-in PLL.                                                                                                                                                                                   |  |  |  |

| AV <sub>CC</sub> (R.P.D.) | 74                   | Power                         | Analog V <sub>CC</sub> power supply. Powers the built-in read pulse detector.                                                                                                                                             |  |  |  |

### HD153014RF/RTF

| Pin Function Pin name | ns (cont)<br>Pin No. | Туре  | Function                                                |   |

|-----------------------|----------------------|-------|---------------------------------------------------------|---|

| AGND (R.P.D.)         | 61                   | Power | Analog ground. Powers the built-in read pulse detector. | _ |

| AGND                  | 78                   | Power | Analog ground.                                          | _ |

### **Absolute Maximum Ratings** (Ta = 25°C)

| Description           | Symbol          | Ratings     | Unit | Notes                               |

|-----------------------|-----------------|-------------|------|-------------------------------------|

| Supply voltage        | V <sub>CC</sub> | 7           | V    | AV <sub>CC</sub> , DV <sub>CC</sub> |

| Input voltage         | V <sub>I</sub>  | -0.3 to 5.5 | V    | *1                                  |

| Output voltage        | Vo              | 5.5         | V    | *2                                  |

| Operating temperature | Topr            | 0 to +70    | °C   |                                     |

| Storage temperature   | Tstg            | -55 to +125 | °C   |                                     |

Notes:1. SHOLD, RX, RAWRD, WG, RG, CS, WE, RE, D0, D1 to D5, A0, A1, PSAVE, WCLK, NRZWD, RESET, REFCLK, PCKSEL, PSEL1, PSEL2, TEST1, TEST2, PHOLD0, PHOLD1, DUMP, SHORT

DC Characteristics (Ta = 0 to +70°C) ( $V_{CC}$  = 5.0 V ±5% unless otherwise noted)

| Item<br>Pin                      | Symbol          | Min  | Тур             | Мах              | Unit | Test conditions                                                |

|----------------------------------|-----------------|------|-----------------|------------------|------|----------------------------------------------------------------|

| Supply voltage                   | v <sub>cc</sub> | 4.75 | 5.0             | 5.25             | V    | DV <sub>CC</sub><br>AV <sub>CC</sub>                           |

| Input voltage                    | V <sub>IH</sub> | 2.2  | _               | 5.5              | V    | * 1                                                            |

|                                  | V <sub>IL</sub> | -0.3 | _               | 0.8              | V    | * 1                                                            |

| Input current                    | I <sub>IH</sub> | _    | _               | 20               | μА   | V <sub>CC</sub> = 5.25 V * 1<br>V <sub>I</sub> = 2.7 V         |

|                                  | IIL             | _    | _               | <del>-4</del> 00 | μА   | V <sub>CC</sub> = 5.25 V * 1<br>V <sub>I</sub> = 0.4 V         |

| Output voltage                   | V <sub>OH</sub> | 2.7  | _               | _                | V    | $V_{CC} = 4.75 \text{ V }^* 2$<br>$I_{OH} = -400  \mu\text{A}$ |

|                                  | V <sub>OL</sub> | _    | _               | 0.5              | V    | V <sub>CC</sub> = 4.75 V * 2<br>I <sub>OL</sub> = 8 mA         |

| Output short-circuit c<br>5.25 V | urrent<br>* 2   | los  | <del>-</del> 20 | _                | -120 | mA V <sub>CC</sub> =                                           |

| Input clamp voltage              | V <sub>IK</sub> | _    | _               | <b>–</b> 1 .5    | ٧    | V <sub>CC</sub> = 4.75 V * 1                                   |

<sup>2.</sup> DLYRD, DLYCLK, SYNCRD, NRZRD, RWCLK, CLKOUT, 1, 7WD, PDRD

## HD153014RF/RTF

$I_{IN} = -18 \text{ mA}$

DC Characteristics (Ta = 0 to +70°C) ( $V_{CC}$  = 5.0 V  $\pm 5\%$  unless otherwise noted) (cont)

| Item                                              | Sy mbol         | Min             | Тур | Мах             | Unit | Test conditions                                                                   | Pin                   |

|---------------------------------------------------|-----------------|-----------------|-----|-----------------|------|-----------------------------------------------------------------------------------|-----------------------|

| Off-state output current                          | lozh            | _               | _   | 20              | μА   | V <sub>CC</sub> = 5.25 V<br>V <sub>O</sub> = 2.7 V                                | NRZRD                 |

|                                                   | OZL             | _               | _   | <del>-</del> 20 | μА   | V <sub>CC</sub> = 5.25 V<br>V <sub>O</sub> = 0.4 V                                | NRZRD                 |

| Current consumption                               | I <sub>CC</sub> | _               | 95  | 145             | mA   | V <sub>CC</sub> = 5.25 V, at 24                                                   | Mbps                  |

| DV <sub>cc</sub>                                  |                 |                 |     |                 |      |                                                                                   | $AV_{CC}$             |

| Charge pump output curr                           | ent<br>CPOUT    | I <sub>Cl</sub> | _   | <b>–1</b> .9    | _    | m <b>A</b>                                                                        | V <sub>CC</sub> = 5.0 |

| V, $R_C = 470 \Omega$                             | CFCCT           |                 |     |                 |      | $V_{CPOUT} = 2.15 V$                                                              |                       |

|                                                   | I <sub>CD</sub> | _               | 1.9 | _               | mA   |                                                                                   |                       |

| T/ I converter output cur V, V <sub>CPOUT</sub> = | r ent<br>CPOUT  | I <sub>TI</sub> | _   | <del>-</del> 20 | _    | μΑ                                                                                | V <sub>CC</sub> = 5.0 |

| 0.001                                             |                 |                 |     |                 |      | 2.15 V, input signa phase offset $+\pi/2$ R <sub>T</sub> = 8.2 k $\Omega$ , at 24 | (rad),                |

| CPOUT                                             | I <sub>TD</sub> | _               | 20  | _               | μА   | V <sub>CC</sub> = 5.0 V, V <sub>CPOL</sub>                                        | л =                   |

| Crcoi                                             |                 |                 |     |                 |      | 2.15 V, input signal offset $-\pi/2$ (rad), $R_T = 8.2 \text{ k}\Omega$ , at 24   |                       |

| ODOLIT                                            | I <sub>TO</sub> | _               | 0   | _               | μА   | V <sub>CC</sub> = 5.0 V, V <sub>CPOL</sub>                                        | л =                   |

| CPOUT                                             |                 |                 |     |                 |      | 2.15 V, input signa<br>offset 0 (rad), R <sub>T</sub> =<br>at 24 Mbps             |                       |

Notes:1. SHOLD, RX, RAWRD, WG, RG, CS, WE, RE, D0 to D5, A0, A1, PSAVE, WCLK, NRZWD, RESET, REFCLK, PCKSEL, PSEL1, PSEL2, TEST1, TEST2, PHOLD0, PHOLD1, DUMP, SHORT

2. DLYRD, DLYCLK, SYNCRD, NRZRD, RWCLK, CLKOUT, 1-7WD, PDRD

# HD153014RF/RTF

AC Characteristics (Ta = 25°C,  $V_{CC}$  = 5.0 V)

| Item<br>Pin                | Sy m be<br>Not es           | ol                   | Mir         | тур | Мах  | Unit                       | Test con       | ditions  |

|----------------------------|-----------------------------|----------------------|-------------|-----|------|----------------------------|----------------|----------|

| Data transfar rate         |                             | _                    | _           | 24  | Mbps |                            |                |          |

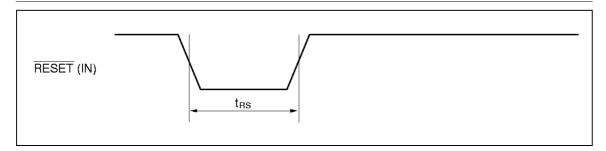

| RESET time                 | t <sub>RS</sub>             | 50                   | _           | _   | ns   |                            |                | Figure   |

| NRZRD set up time<br>NRZRD | t <sub>SNR</sub><br>Figur e | 15<br>2              | _           | _   | ns   | With DUTY adjusted, 24 M   | bps            |          |

|                            |                             | 10                   | _           | _   | ns   | With DUTY not adjusted, 2  | 4 Mbps         |          |

| NRZRD hold time            | t <sub>HNR</sub>            | 15                   | _           | _   | ns   | With DUTY adjusted, 24 M   | bps            |          |

|                            |                             | 15                   | _           | _   | ns   | With DUTY not adjusted, 2  | 4 Mbps         |          |

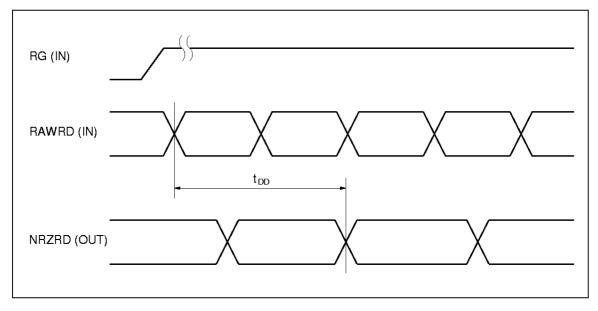

| Decode time                | t <sub>DD</sub>             | _                    | 10          | _   | VCO  |                            | NRZRD          | Figure   |

|                            |                             |                      |             |     | CLK  |                            |                |          |

| NRZWD set up time 4        | t <sub>SNW</sub>            | 10                   | _           | _   | ns   |                            | NRZWD          | Figur e  |

| NRZWD hold time            | t <sub>HNW</sub>            | 5                    | _           | _   | ns   |                            | _              |          |

| Encode time                | t <sub>ED</sub>             | _                    | 13          | _   | REF  | No write precompensation   | 1-7 <b>W</b> D | Figur e  |

| 5                          |                             | _                    | 16          | _   | CLK  | With write precompensation | on             |          |

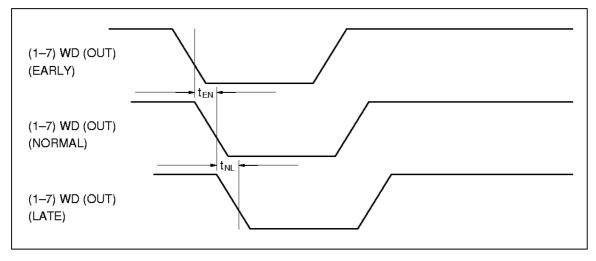

| Write precompens           | ation<br>Figure             | t <sub>EN</sub><br>6 | _           | 0   | _    | ns                         | Minimun de     | lay time |

| delay time                 |                             | _                    | <b>-9</b> . | 1 — | ns   | Maximum delay time         |                |          |

|                            | $t_{NL}$                    | _                    | 0           | _   | ns   | Minimun delay time         |                |          |

|                            |                             | _                    | 9.1         | _   | ns   | Maximum delay time         |                |          |

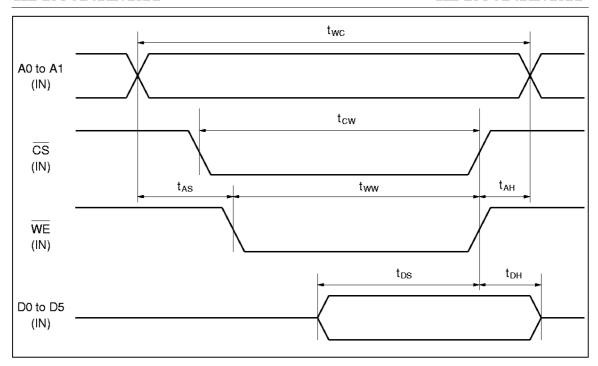

| Register write cycle 7     | twc                         | 50                   | _           | _   | ns   |                            | A0 to A1       | Figure   |

| Address set up time        | t <sub>AS</sub>             | 5                    | _           | _   | ns   |                            | WE             |          |

| Address hold time          | t <sub>AH</sub>             | 0                    | _           | _   | ns   |                            | WE             |          |

| Write chip select          | t <sub>CW</sub>             | 30                   | _           | _   | ns   |                            | CS             |          |

| Write enable time          | t <sub>ww</sub>             | 20                   | _           | _   | ns   |                            | WE             |          |

| Write data set up t        | time                        | t <sub>DS</sub>      | 10          | _   | _    | ns                         |                | D0 to    |

| HD153014RF/RTF                       |   | HD153014RF/RTF |    |          |

|--------------------------------------|---|----------------|----|----------|

| Write data hold time t <sub>DH</sub> | 5 |                | ns | D0 to D5 |

## HD153014RF/RTF

AC Characteristics (Ta = 25°C,  $V_{CC} = 5.0 \text{ V}$ ) (cont)

| Item<br>Pin                   | Sy m<br>Not e   |                 | Min | Тур | Max | Unit | Test condit | ions    |

|-------------------------------|-----------------|-----------------|-----|-----|-----|------|-------------|---------|

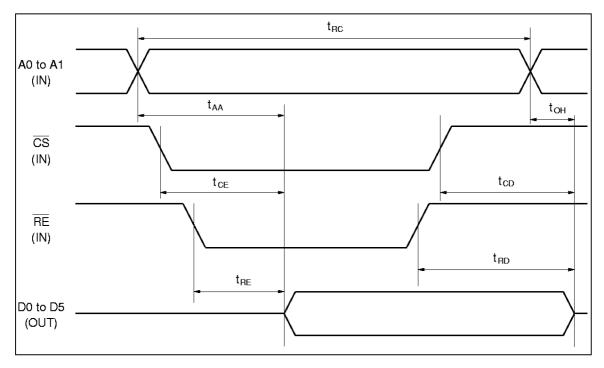

| Register read cycle<br>8      | t <sub>RC</sub> | 50              | _   | _   | ns  |      | A0 to A1    | Figur e |

| Address access ti<br>A5       | me              | t <sub>AA</sub> | _   | _   | 50  | ns   |             | D0 to   |

| Output hold time              | tон             | 5               | _   | _   | ns  |      | D0 to A5    |         |

| Read chip select t            | ime             | t <sub>CE</sub> |     | _   | 30  | ns   |             | CS      |

| Read enable time              | t <sub>RE</sub> | _               | _   | 30  | ns  |      | RE          |         |

| Read disable time             | t <sub>RD</sub> | 0               | _   | 30  | ns  |      | RE          |         |

| Read chip select disable time | t <sub>CD</sub> | 0               | _   | 30  | ns  |      | CS          |         |

### **VFO AC Characteristics** (Ta = 25°C, $V_{CC} = 5.0 \text{ V}$ )

| Item                            | Symbol Min | Тур  | Мах | Unit         | Test conditions                            | Notes      |

|---------------------------------|------------|------|-----|--------------|--------------------------------------------|------------|

| VCO center frequency            | y          | 34.2 | 36  | 37.8         | MHz                                        | At 24 Mbps |

| VCO maximum clamp<br>fr equency | _          | 54   | _   | MHz          | At 24 Mbps                                 |            |

| VCO minimum clamp<br>frequency  | _          | 18   | _   | MHz          | At 24 Mbps                                 |            |

| VCO Gain                        | _          | 208  | _   | Mrad/<br>S•V | At 24 Mbps                                 |            |

| Phase pull-in time              | taq —      | _    | 6   | Byte         | At 24 Mbps, with recommended constants set |            |

| Capture range                   | ±15        | _    | _   | %            | At 24 Mbps, with recommended               |            |

| Locking range                   | ±15        | _    | _   | %            | constants set                              |            |

| Window margin loss              | _          | _    | 3.0 | ns           | During window adjust                       | ment       |

Note: At 24 Mbps the recommended constants are:  $R_{VCO}$  = 2.5 k $\Omega$ ,  $R_{C}$  = 470  $\Omega$ ,  $R_{T}$  = 8.2 k $\Omega$   $C_{1}$  = 2000 pF,  $C_{2}$  = 82 pF,  $R_{1}$  = 910  $\Omega$ ,  $R_{2}$  = 330  $\Omega$

#### **HD153014RF/RTF** HD153014RF/RTF **R.P.D.** DC Characteristics (Ta = 25°C, V<sub>CC</sub> = 5.0 V) Symbol Item Min Typ Max Unit Test conditions Notes Pin Differential input $R_{IA}$ 2.1 3.0 3.9 $k\Omega$ RINX RINY resistance Input bias voltage $V_{BA}$ 2.3 2.5 2.7 ٧ Differential output 0 mV **AGCOUTX** $V_{OFA}$ offset voltage **AGCOUTY** ٧ In-phase output $V_{\text{OCA}}$ 2.4 voltage Output sink current 1.8 mΑ Iosa Differential input 15.6 $k\Omega$ BUFFINX $R_{IB}$ 8.4 12 resistance **BUFFINY** Input bias voltage $V_{BB}$ 3.5 ٧ Differential output BUFFOUTX $V_{OFB}$ 0 mV offset voltage **BUFFOUTY** In-phase output 3.0 — ٧ $V_{OCB}$ voltage Output sink current 1.9 mΑ losa **DIFINX** Differential input 8.4 15.6 k $\Omega$ $R_{ID}$ 12 resistance **DIFINY** Input bias voltage 3.5 ٧ $V_{BD}$ DIF sink current 2.4 mΑ DIF 1 IDSD DIF 2 Differential output $V_{OFD}$ mV DIFOUTX offset voltage **DIFOUTY** In-phase output 3.0 — ٧ $V_{OCD}$ voltage Output sink current 1.9 mΑ losp Differntial input 8.4 12 15.6 k $\Omega$ **AGCINX** $R_{IC}$ resistance **AGCINY** Input bias voltage ٧ $V_{BC}$ 3.5 Input bias current 3.0 μΑ VSL, VSH IBS

## HD153014RF/RTF

Figure 1 Reset Input

Figure 2 NRZ Read Data Output

Figure 3 Decode

## HD153014RF/RTF

Figure 4 NRZ Write Data Output

Figure 5 Encode and (1, 7) Code Write Data Output

Figure 6 White Precompensation Delay

## HD153014RF/RTF

Figure 7 Register Write

Figure 8 Register Read

| HD1                                          | 153014RF                  | /RTF                                              |                     |                                      | HD153014RF/RTF                  |

|----------------------------------------------|---------------------------|---------------------------------------------------|---------------------|--------------------------------------|---------------------------------|

| Differential voltage f <sub>IN</sub> = 1 MHz |                           | A <sub>VA</sub> —<br>AGCOUTX                      | 40.8 — dB           | f <sub>IN</sub> = 1 MHz              | DIFOUTY                         |

| gain                                         |                           | AGCOUTY                                           |                     | Bandwidth<br>MHz                     | B <sub>WD</sub> — 40 —<br>-3 dB |

| Bandw<br>MHz                                 | vidth                     | B <sub>WA</sub> —<br>–3 dB                        | 40 —                | PDRD                                 | t <sub>WPD</sub> — 22.7 ns      |

| TEST2                                        | 2 TEST                    | 1 RAWF                                            | RD input*1          | DLYRD, DLYCLK, a<br>SYNCRD outputs*2 | and<br>Operating mode           |

| High                                         | High                      | Don't                                             | care                | Always high                          | Normal mode                     |

| High                                         | Low                       | Active                                            | (input)             | Always high                          | Test modes                      |

| Low                                          | High                      | Don't d                                           | care                | Output lines                         | _                               |

| Low                                          | Low                       | Active                                            | (input)             | Output lines                         | _                               |

|                                              | on ratio<br>egister Names | s and Functio                                     | ns                  |                                      |                                 |

| A1<br>———                                    | A0 Ac                     | ldress                                            | Name                | Function                             |                                 |

| 0                                            | 0 0                       |                                                   | WAJ register        | Decode window adjus                  | stment                          |

| 0                                            | 1 1                       |                                                   | DTC register        | RWCLK duty adjustm                   | nent                            |

| 1                                            | 0 2                       |                                                   | WPC register        | Write precompensation                | on delay adjustment             |

| Note:                                        | The register              | s are initialized                                 | l to 0 by a low inp | out on the RESET line at             | power-up.                       |

| dB<br>gain                                   | –Differential vo          | oltage A <sub>VB</sub><br>f <sub>IN</sub> = 1 MHz | — 6.4 —<br>BUFFOUTX |                                      |                                 |

|                                              |                           | BUFFOUTY                                          |                     |                                      |                                 |

| Bandw<br>MHz                                 | vidth                     | B <sub>WB</sub> —<br>–3 dB                        | 40 —                |                                      |                                 |

| dB                                           | —Differential vo          | oltage A <sub>VD</sub><br>R <sub>E</sub> = 680 Ω  | — 1.1 — DIFOUTX     |                                      |                                 |

gain

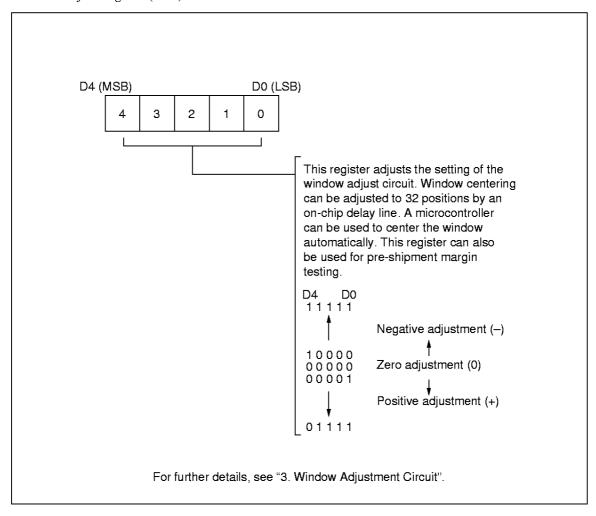

### (2) Register Descriptions

Window Adjust Register (WAJ)

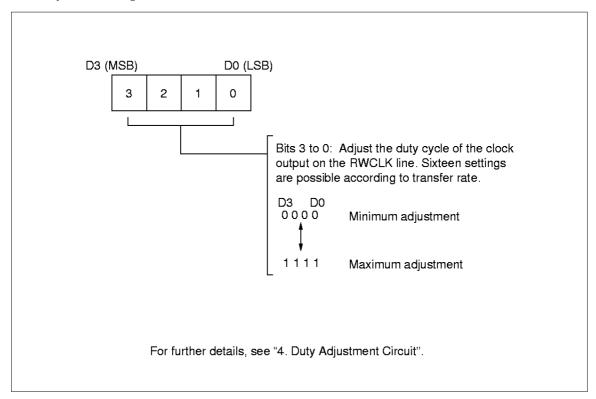

### (3) Duty Control Register (DTC)

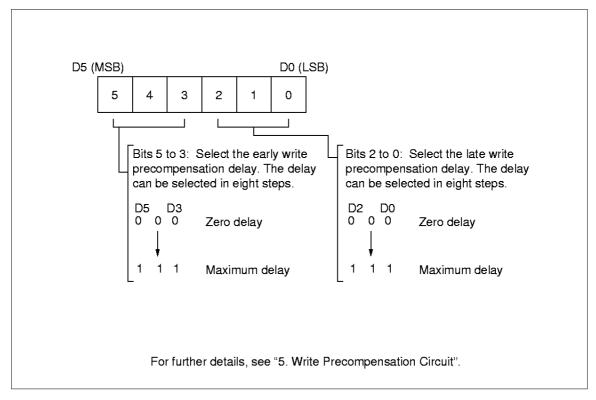

### (4) Write Precompensation Control Register (WPC)

### 3. Window Adjustment Circuit

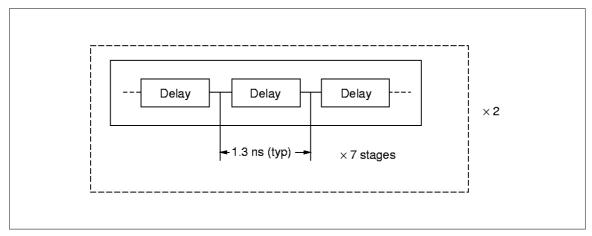

The HD153014RF has an on-chip delay line for centering the decode window. The delay line has 32 taps that can be selected by register WAJ.

Centering adjustment can be performed automatically by a microcontroller. This adjustment function can also be used for pre-shipment margin tests.

### (1) Circuit Configuration

## HD153014RF/RTF

### (2) Delay Line

**WAJ Register**

### **WAJ Register**

| 5 | 4 | 3    | 2 | 1 | 0 | Delay line tap No. |

|---|---|------|---|---|---|--------------------|

| _ | 1 | 1    | 1 | 1 | 1 | <b>–</b> 16        |

|   |   | <br> |   |   |   |                    |

| _ | 1 | 0    | 0 | 0 | 1 | <b>-</b> 2         |

| _ | 1 | 0    | 0 | 0 | 0 | -1                 |

| _ | 0 | 0    | 0 | 0 | 0 | 0                  |

| _ | 0 | 0    | 0 | 0 | 1 | +1                 |

| _ | 0 | 0    | 0 | 1 | 0 | +2                 |

|   |   |      |   |   |   | <br>               |

| _ | 0 | 1    | 1 | 1 | 1 | +15                |

### 4. Duty Adjustment Circuit

The duty cycle of the clock output to the disk controller on the RWCLK line can be adjusted by setting the DTC register.

### (1) Circuit Configuration

### (2) Delay Line

|                        |   |            | _  |    |   |     |    |

|------------------------|---|------------|----|----|---|-----|----|

| $\mathbf{H}\mathbf{D}$ | 1 | <b>5</b> 3 | Λ1 | 4D | F | /DΩ | ГБ |

|                        |   |            |    |    |   |     |    |

### (2) Register Descriptions

Window Adjust Register (WAJ)

### 5. Write Precompensation Circuit

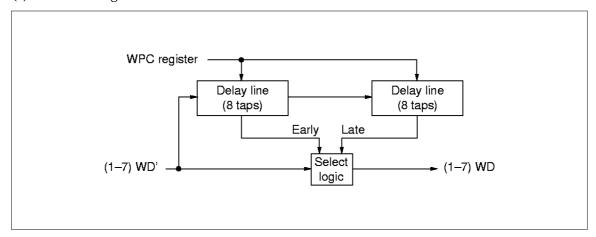

The HD153014RF has a built-in write precompensation circuit and a built-in WPC register that can be used to select independent early and late write precompensation delays. Write precompensation

can also be performed externally, using a clock signal output on the CLKOUT line in synchronization with the output on the 1-7WD line.

### (1) Circuit Configuration

### (2) Programmable Delay Line

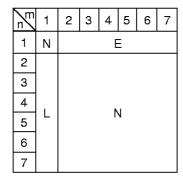

### (3) Table

E: Early

N: Normal (no precompensation)

L: Late E≤N≤L

> n m 10 ··· 010 ··· 01 Last This Next

n: Number of 0s between this 1 bit and last 1 bit.

m: Number of 0s between this 1 bit and next 1 bit.

The early and late precompensation delays can be selected independently in the WPC register (8 selections for each).

### (4) External Write Precompensation Mode

For external write precompensation, drive the PCKSEL line high and use the clock signal output on the CLKOUT line, which is synchronized with the 1, 7WD output.

### 4. Duty Adjustment Circuit

The duty cycle of the clock output to the disk controller on the RWCLK line can be adjusted by setting the DTC register.

### (1) Circuit Configuration

### (2) Delay Line

### **Conversion Table**

NRZ data bits

|     |                                  | Current |   |     |      |   |        |      |  |

|-----|----------------------------------|---------|---|-----|------|---|--------|------|--|

| No. | Last bit of previous (1, 7) code |         |   | Nex | Next |   | ) Code | bits |  |

| 1   | 0                                | 1       | 0 | 0   | х    | 1 | 0      | 1    |  |

| 2   | 0                                | 1       | 0 | 1   | х    | 0 | 1      | 0    |  |

| 3   | 0                                | 1       | 1 | 0   | 0    | 0 | 1      | 0    |  |

| 4   | 0                                | 1       | 1 | 0   | 0    | 1 | 0      | 0    |  |

| 5   | 0                                | 0       | 0 | 0   | х    | 0 | 0      | 1    |  |

| 6   | 0                                | 0       | 0 | 1   | х    | 0 | 0      | 0    |  |

| 7   | 0                                | 0       | 1 | 0   | х    | 0 | 0      | 1    |  |

| 8   | 0                                | 0       | 1 | 1   | х    | 0 | 0      | 0    |  |

| 9   | 1                                | 0       | 0 | 0   | х    | 0 | 0      | 1    |  |

| 10  | 1                                | 0       | 0 | 1   | х    | 0 | 1      | 0    |  |

| 11  | 1                                | 0       | 1 | 0   | 0    | 0 | 1      | 0    |  |

| 12  | 1                                | 0       | 1 | 0   | 0    | 0 | 0      | 0    |  |

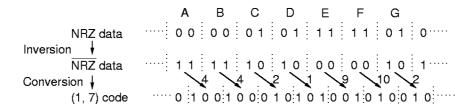

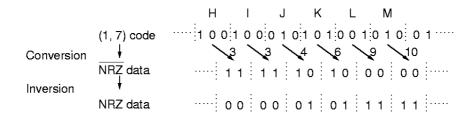

0 0: Not 0 0 x: Don't care An example of the conversion of an NRZ signal to (1, 7) coded data is given below.

The NRZ data is inverted before it is converted into (1, 7) code. For example, when the above NRZ B data ('00') is converted, it is first inverted to give the NRZ data '11', then the last bit ('0') of

the resultof converting A ('100') and the next NRZ data status C '01' (C = '10') dictate that 4 is selected from the conversion table, so that the B data '00' is converted into the (1, 7) code '100'.

### Conversion Table ((1, 7) code $\rightarrow N R Z$ )

### 1, 7 code bits

| No. | Previous | Current | Next         | —<br>NRZ <b>data bits</b> |

|-----|----------|---------|--------------|---------------------------|

| 1   | X 1 0    | 0 0 0   | XXX          | 0 0                       |

| 2   | X 0 0    | 0 0 0   | XXX          | 0 1                       |

| 3   | XXX      | 1 0 0   | XXX          | 11                        |

| 4   | X X 0    | 0 1 0   | 0 0 <b>X</b> | 1 0                       |

| 5   | X X 0    | 0 1 0   | 0 0 X        | 11                        |

| 6   | XXX      | 1 0 1   | XXX          | 1 0                       |

| 7   | X 0 0    | 0 0 1   | XXX          | 0 1                       |

| 8   | X 1 0    | 0 0 1   | XXX          | 0 0                       |

| 9   | X X 1    | 0 0 1   | XXX          | 0 0                       |

| 10  | X X 1    | 0 1 0   | 0 0 <b>X</b> | 0 0                       |

| 11  | X X 1    | 0 1 0   | 0 0 X        | 0 1                       |

| 12  | X X 1    | 0 0 0   | XXX          | 0 1                       |

x: Don't care 0 0: Not 0 0

An example of the conversion of (1, 7) coded data to an NRZ signal is given below.

For example, when the above (1, 7) coded I = '100' data is converted into NRZ data, the previous status H = '100' and the next status J = '010'

dictate that 3 is selected from the conversion table, so the data is converted into the NRZ data '11'. This is inverted and output as the NRZ data '00'

### **HD153014RF/RTF**

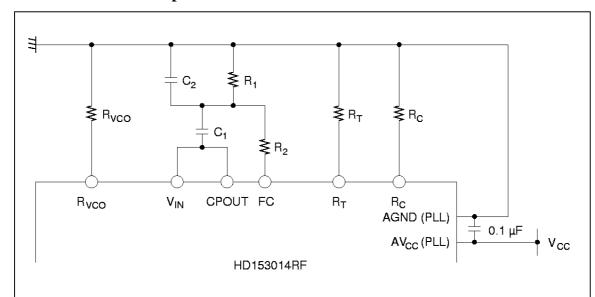

### **HD153014RF PLL Constant Determination Procedure**

This section uses 24 Mbps as an example to describe the procedure for determining the HD153014RF PLL constants.

#### 1. Phase Pull-in Time

The HD153014RF high gain period is 6 bytes. Therefore, the phase pull-in time Taq must be set to be less than that.

Example: If the data transfer rate is 24 Mbps, phase pull-in within 5 bytes requires that:

Taq =

$$1/24$$

Mbps  $\times$  8 bits  $\times$  5 bytes =  $1.67$   $\mu$ s (1-1)

### 2. High Gain on (H)

From the formula for computing the PLL phase step response, the phase pull-in completion time is given by the formula 2-1:

$$\omega_{n}T = 5.4$$

(2-1)

Substituting formula 1-1 gives the high gain  $\omega$ n(H):

$$\omega_n(H) = 3.2 \text{ Mrad/s}$$

(2-2)

#### 3. VCO Constants

The VCO center frequency  $f_{VCO}$  is:

$$f_{VCO}$$

= transfer rate  $\times 1.5 = 24 \text{ Mbps} \times 1.5 = 36 \text{ MHz}$  (3-1)

The external resistance  $R_{VCO}$  is given by:

$$R_{VCO} = K1/f_{VCO}$$

(Hz)  $(K1 = 9.0 \times 10^{10})$  (3-2)

Therefore at 24 Mbps:

$$R_{VCO} = 2.5 \text{ k}\Omega \tag{3-3}$$

Also, at this time the VCO gain K0 will be:

$$K0 = K2/\sqrt{R_{VCO}}$$

(K2 = 1.04 × 10<sup>10</sup>) (3-4)

Therefore at 24 Mbps:

$$K0 = 208 \operatorname{Mrad/S} \cdot V \tag{3-5}$$

#### 4. T/I Conversion Circuit Constants

Next, we derive the T/I conversion circuit external resistance  $R_T$  and the phase detector gain Kd(N) (normal gain).

$$R_T = K3/f_{VCO}$$

(K3 = 3.0 × 10<sup>10</sup>) (4-1)

### **HD153014RF/RTF**

Therefore, at 24 Mbps:

$$R_{T} = 8.33 \text{ k}\Omega \rightarrow 8.2 \text{ k}\Omega \tag{4-2}$$

Also, Kd(N) is given by:

$$Kd(N) = K4/\pi \cdot R_T$$

(K4 = 0.28) (4-3)

Therefore, at 24 Mbps:

$$Kd(N) = 34/\pi \,\mu A/rad$$

(4-4)

#### 5. Charge Pump Circuit Constants

Next, we derive the external resistance  $R_C$  which determines the charge pump circuit's output current and the phase detector gain Kd(H) (high gain).

$R_C$  should be in the range 250  $\Omega \le R_C \le 1$  k $\Omega$ . We recommend initially setting  $R_C$  to:

$$R_C = 470 \Omega \tag{5-1}$$

Next we derive the phase detector gain Kd(H) (high gain).

$$Kd (H) = \frac{0.9}{6\pi \cdot Rc}$$

(5-2)

Therefore, when  $R_C = 470 \Omega$ ,

$$Kd(H) = 319/\pi \cdot \mu A/rad$$

(5-3)

### 6. Loop Filter Constants [1]

First we derive the loop filter C1 capacitance:

$$C1 = \frac{K0 \cdot Kd (H)}{\omega n^2 (H)}$$

(6-1)

Substituting the values from formulas (2-2), (3-5), and (5-3) gives:

$$C1 = 2062 \text{ pF} \rightarrow 2000 \text{ pF}$$

(6-2)

#### 7. Normal Gain $\omega$ n(N)

$$\omega_{\rm II}(N) = \sqrt{\frac{K0 \cdot Kd(N)}{C1}}$$

(7-1)

Substituting the values from formulas (3-5), (4-4), and (6-2) gives:

$$\omega_n(N) = 1.06 \text{ Mrad/s}$$

(7-2)

### 8. Loop Filter Constants [2]

We derive the values for the external resistances R1 and R2, setting the high gain attenuation factor  $\zeta(H) = 0.8$ , and the low gain attenuation factor  $\zeta(L) = 1.0$ .

$$R1 = \frac{2 \zeta \cdot (N)}{C1 \cdot \omega_n(N)}$$

(8-1)

Substituting the values from formulas (6-2) and (7-2) gives:

$$R1 = 943 \Omega \rightarrow 910 \Omega \tag{8-2}$$

Also, R2 is given by:

$$R1 = \left(\frac{C1 \cdot \omega_n(H)}{2 \cdot \zeta(H)} - \frac{1}{P1}\right)^{-1} \tag{8-3}$$

Substituting the values from formulas (6-2), (2-2), and (8-2) gives:

$$R2 = 344 \ \Omega \rightarrow 330 \ \Omega \tag{8-4}$$

### 9. Loop Filter Constants (3)

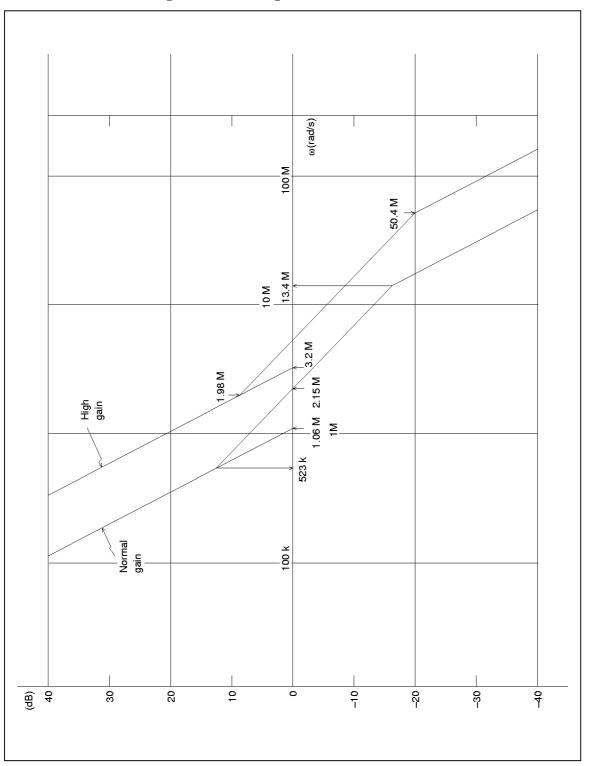

Next we construct the Bode diagram and derive the loop filter C2 capacitance.

The system open loop transfer function G(S) is given by:

$$G(S) = \frac{K0 \cdot Kd}{C1} - \frac{1}{S^2} \frac{1 + S \cdot (C1 + C2) \cdot R}{1 + S \cdot C2 \cdot R}$$

(9-1)

Therefore, the Bode diagram can be constructed by the following procedure.

- a. Draw a straight line of -40~dB/dec through ( $\omega n,~0$ ).

- b. Proceed at -20 dB/dec from  $\omega = \frac{1}{(C1 + C2) \cdot R}$

Here, temporarily substitute a value of about 1/20 C1 for C2.

c. Read off the unity gain frequency  $\omega O(N)$  and  $\omega O(H)$  from the graph.

Next, we derive the loop filter C2 capacitance. C2 performs the function of reducing the system gain in the high frequency region. The break frequency  $\omega$ 2 which is delayed by -40 dB/dec is expressed by:

$$\omega 2 = \frac{1}{\text{C2} \cdot \text{R}} \tag{9-2}$$

When  $\omega 2$  is large, it is easy to follow high frequency components such as jitter, and when it is small the system phase margin is reduced, and furthermore, the second order approximation error is increased. Therefore, set C2 near the value in the formula below as a first approximation.

$$C2 = \frac{0.65}{C1 + R1^2 \cdot \omega_0(N)^2}$$

(9-3)

ω0(N): Unity gain frequency at normal gain.

Example: When  $\omega 0(N)$  is 2.15 Mrad/s:

$$C2 = \frac{0.65}{2000 \text{pF} \times 910^2 \times (2.15 \times 10^6)^2} = 84.9 \text{ pF} \rightarrow 82 \text{ pF}$$

(9-4)

Next, we continue with the construction of the Bode diagram.

d. With

$$\omega = \frac{1}{C2 \cdot R}$$

, it is delayed by – 40 dB/dec. (9-5)

This means that the formulas in b, (9-2), and d above which include R have different values at high gain and normal gain settings.

$$R = \left\{ \begin{array}{ll} R1 & : \text{Normal Gain} \\ R1 \text{ } / \! / \, R2 & : \text{High Gain} \rightarrow \left( \frac{1}{R1} + \frac{1}{R2} \right)^{-1} \end{array} \right.$$

The Bode diagram derived by the above procedure is shown below.

# HD153014RF/RTF

## HD153014RF Bode Diagram for 24 Mbps

## **External Circuit Example**

| Transfer rate | R <sub>C</sub> | $R_T$  | R <sub>VCO</sub>       | C <sub>1</sub> | C <sub>2</sub> | R <sub>1</sub> | $R_2$ |

|---------------|----------------|--------|------------------------|----------------|----------------|----------------|-------|

| 24 Mbps       | 470 Ω          | 8.2 kΩ | $2.5~\mathrm{k}\Omega$ | 2000 pF        | 82 pF          | 910 Ω          | 330 Ω |

| 20 Mbps       | 470 Ω          | 10 kΩ  | 3 kΩ                   | 2700 pF        | 120 pF         | 910 Ω          | 270 Ω |

| 15 Mbps       | 470 Ω          | 13 kΩ  | 4 kΩ                   | 4300 pF        | 160 pF         | 910 Ω          | 240 Ω |

| 12 Mbps       | 470 Ω          | 16 kΩ  | 5 kΩ                   | 5600 pF        | 240 pF         | 910 Ω          | 220 Ω |

| 10 Mbps       | 470 Ω          | 20 kΩ  | 6 kΩ                   | 7500 pF        | 330 pF         | 910 Ω          | 200 Ω |

|               |                |        |                        |                |                |                |       |

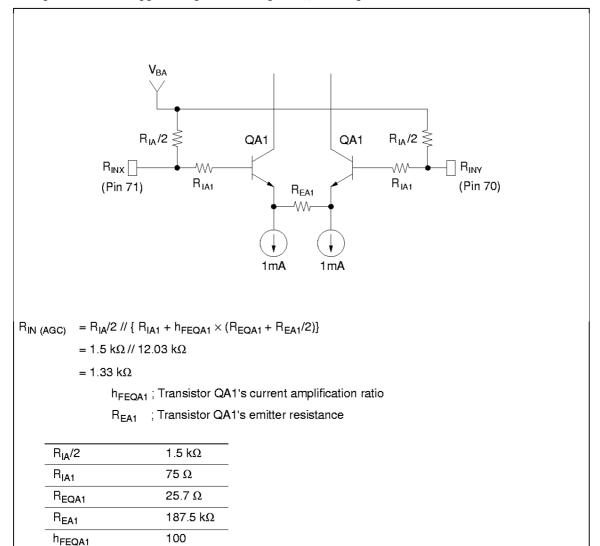

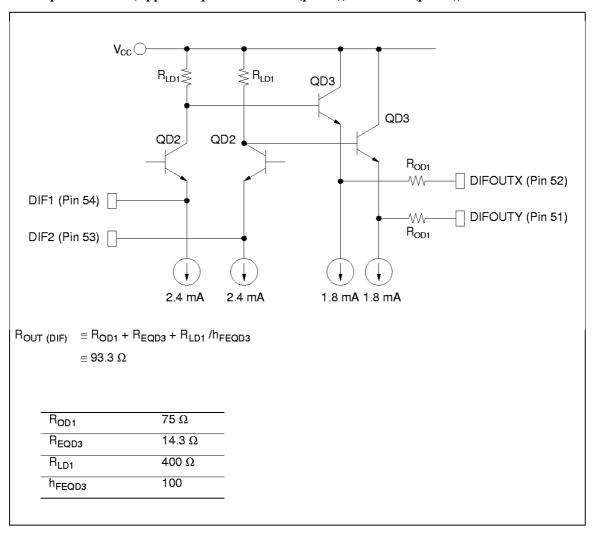

# HD153014RF R.P.D. Amplifier Input Output Impedance

- 1. AGC Amplifier

- a. Input resistance (Applicable pins: RINX (pin 71), RINY (pin 70))

# b. Output resistance (Applicable pins: AGCOUTX (pin 67), AGCOUTY (pin 66))

$$R_{OUT (AGC)} = R_{OA1} + R_{EQA2} + R_{LA1}/h_{FEQA2}$$

$\cong 59 \Omega$

| R <sub>OA1</sub>   | 20 Ω   |

|--------------------|--------|

| R <sub>EQA2</sub>  | 14.3 Ω |

| R <sub>LA1</sub>   | 2.5 kΩ |

| h <sub>FEQA2</sub> | 100    |

## 2. Buffer Amplifier

## a. Input resistance (Applicable pins: BUFFINX (pin 60), BUFFINY (pin 59))

# b. Output resistance (Applicable pins: BUFFOUTX (pin 58), BUFFOUTY (pin 57))

$$R_{OUT (BUFF)} = R_{OB1} + R_{EQB3} + (R_{B1} + R_{LB1}) / h_{FEQB3}$$

$\cong 102 \Omega$

| R <sub>OB1</sub>   | 75 Ω   |

|--------------------|--------|

| R <sub>EQB3</sub>  | 14.3 Ω |

| R <sub>B1</sub>    | 100 Ω  |

| R <sub>LB1</sub>   | 1.2 kΩ |

| h <sub>FEQB3</sub> | 100    |

- 3. Differential Amplifier

- a. Input resistance (Applicable pins: DIFINX (pin 55), DIFINY (pin 56))

$$\begin{split} R_{\text{IN (DIF)}} & \cong R_{\text{ID}}/2 \, / \! / \, \{ \, R_{\text{ID1}} + h_{\text{FEQD1}} \times h_{\text{FEQD2}} \times (R_{\text{EQD2}} + R_{\text{EX}}/2) \, \} \\ & \cong 6 \, k\Omega \, / \! / \, \{ \, 107.28 \, \Omega + 5000 \times \, R_{\text{EX}} \, \} \\ & \cong 6 \, k\Omega \end{split}$$

R<sub>EX</sub>: External resistance between DIF1 and DIF2.

| R <sub>ID</sub> /2 | 6 kΩ   |

|--------------------|--------|

| R <sub>ID1</sub>   | 200 Ω  |

| h <sub>FEQD1</sub> | 100    |

| h <sub>FEQD2</sub> | 100    |

| R <sub>EQD2</sub>  | 10.7 Ω |

# b. Output resistance (Applicable pins: DIFOUTX (pin 52), DIFOUTY (pin 51))

# HD153014RF/RTF

# HD153014RF/RTF

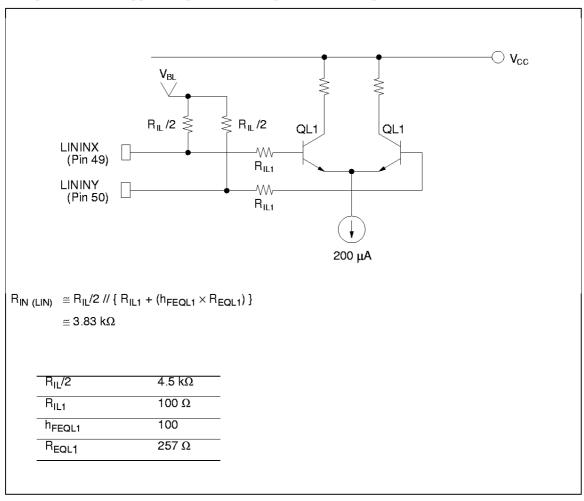

- 4. Line Amplifier

- a. Input resistance (Applicable pins: LININX (pin 49, LININY (pin 50))

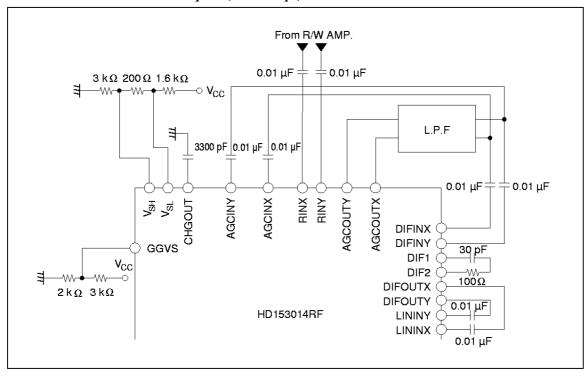

## b. External R.P.D. Circuit Example 1 (At 24 Mbps)

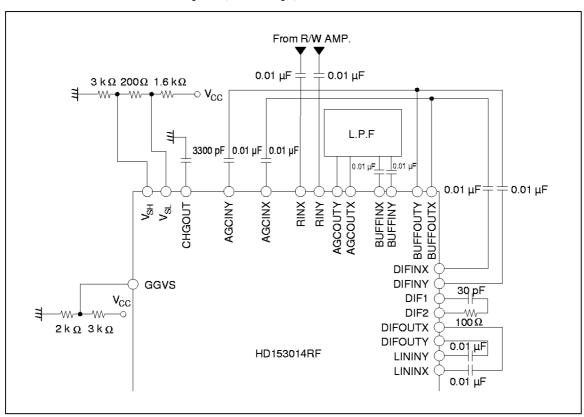

#### c. External R.P.D. Circuit Example 2 (At 24 Mbps)

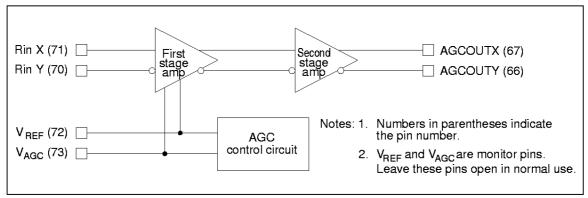

#### 5. AGC (Automatic Gain Control) Amplifier Circuit

The HD153014RF AGC amplifier is constructed from two differential amplifier stages, with the first stage gain variable, and the second stage gain fixed. The AGC amplifier gain is determined by the difference between  $V_{REF}$  and the AGC control circuit output  $V_{AGC}$ . Figure 5-1 shows the structure of the AGC amplifier.

Figure 5-1 The AGC Amplifier Structure

#### (1) The AGC Amplifier Gain

The AGC amplifier gain is determined by the difference between  $V_{REF}$  and the AGC control circuit output  $V_{AGC}$ , and is expressed by the equations (5-1) below.

$$A_{V(V/V)} = K_1 \times \left(\frac{1}{1 + \exp{(qV_C/kT)}}\right)$$

(5-1)

$$K_1 = 110 \text{ V/V} (= 40.8 \text{ dB})$$

$$: AGC \text{ Full Gain}$$

$$V_C = V_{AGC} - V_{REF}$$

$$q: \text{ elementary}$$

$$k: \text{ Boltzman's constant}$$

$$T: \text{ absolute temperature } (KT/q \approx 26 \text{ mV})$$

#### 6. Differential Amplifier Circuit

The current flowing in the collector due to the external capacitance  $C_{EX}$  connected between pins Dif.1 and 2, can be expressed by the following formula.

ic (t) =

$$C_{EX} \times \frac{dVin}{dt}$$

Taking the differentiation circuit input voltage Vin(t) to be  $Vp \times \sin \omega t$  gives:

ic (t) =

$$C_{EX} \times Vp \times \omega \times \cos \omega t$$

Here, the value of the external capacitor  $C_{EX}$  should be chosen so that the ic(t) current slew rate is as large as possible, so the waveform will not be distorted. Here, the maximum value of ic(t) (i.e., ic (t) max) can be expressed by the following formula.

ic max =

$$C_{EX} \times Vp \times \omega$$

## **HD153014RF/RTF**

## **HD153014RF/RTF**

Set ic max to be less than the fixed current  $I_{DSD}$  (2.4 mA (typ): the dif. sink current). If ic max is grater than  $I_{DSD}$ , waveform distortion will occur.

Therefore, it is necessary for  $C_{\text{EX}}$  to fulfill the following condition.

$$C_{EX} < I_{DSD}/Vp \times \omega$$

The frequency characteristics of ic(t) are determined by the sum of the internal transistor emitter resistance ( $R_{EOD2}$ ) and the external resistance  $R_{EX}$ .

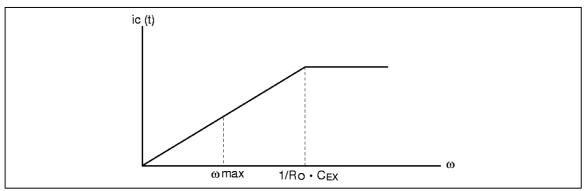

A pole is generated at  $1/R_O \cdot C_{EX}$  by the output resistance  $R_O$ , and as a result, the frequency characteristics of ic(t) are as shown in the figure below.

Figure 6-1 Frequency Characteristics due to CEX

Note: The frequency characteristics for  $C_{EX}$  in figure 6-1 are for an ideal substrate, and in actual use the position of the pole may not agree with the computation due to parasitic C, L, and R from the substrate. We therefore recommend confirmation of the frequency characteristics in the actual circuit.

$$R_{O} = \frac{1}{n \cdot C_{EX} \cdot \omega_{max}}$$

(n = 1.5 to 3.0)

When  $R_O$  is larger than the right hand side of the above formula, connect a resistance  $R_{EX}$  in series with  $C_{EX}$ . In this case the formula becomes:

$$R_{O} + R_{D} = \frac{1}{n \cdot C_{EX} \cdot \omega_{max}}$$

(n = 1.5 to 3.0)

In this case, the gain (A<sub>VD</sub>) of the differential amplifier will be:

$$A_{VD} = \frac{R_{LD1}}{R_{EQD2} + (R_{EX} + \frac{1}{j\omega C_{EX}})/2}$$

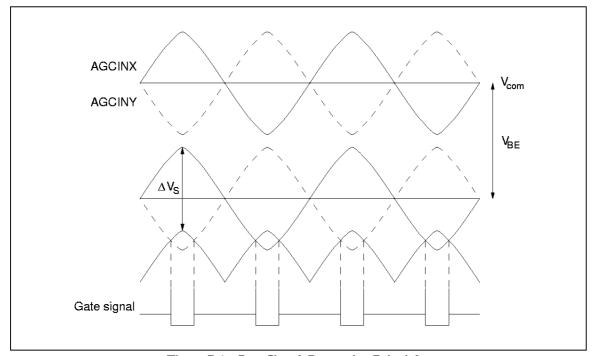

## 7. Gate Generator Circuit

A gate signal is applied at positions corresponding to read signal peaks, and it is the gate signal which is used to exclude source and other noise. The HD153014RF has functions for generating this gate signal. In principle, the method adopted for generating the gate signal, is to compare a signal shifted by  $\Delta V_S$  only, with a signal produced by rectifying the signal input to the AGCINX and AGCINY pins.

Here,  $\Delta V_S$  is:

$$\Delta V_{S} = \frac{V_{GGVS}}{3}$$

Where  $V_{GGVS}$  is the voltage on the GGVS pin.

Figure 7-1 Gate Signal Generation Principles

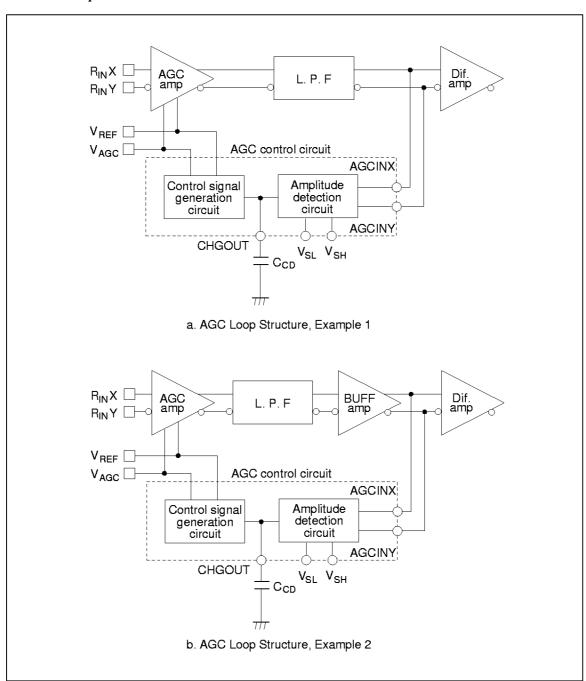

## 8. AGC Loop

Figure 8-1 AGC Loop Structures

## **HD153014RF/RTF**

## **HD153014RF/RTF**

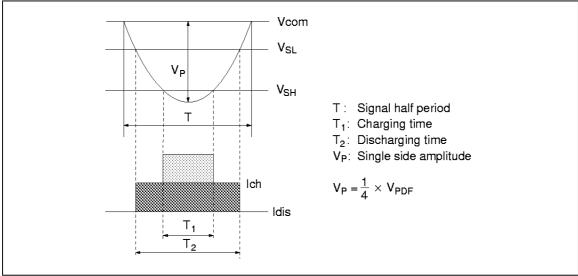

Figure 8-1 shows examples of AGC loop structures. Example 1 is an example where there is no attenuation in the L.P.F., and example 2 is an example where the type of L.P.F. with a -6 dB loss is used. However, even when an attenuating L.P.F. is used, if an adequate signal amplitude can be obtained with the AGC amplifier gain, then we recommend using the circuit structure in example 1. Here, the AGC amplifier gain control is handled by the AGC control circuit shown in figure 8-1. In the AGC control circuit, the signals input from the AGCINX, and AGCINY pins are compared with the externally set reference voltages ( $V_{SL}$  and  $V_{SH}$ ), and an external capacitor is charges and discharged. The AGC amplifier gain is controlled by the changes in the control signal VAGC which are due to the charge and discharge of this external capacitor.

The final amplitude Vp (the waveform at the pins AGCINX and AGCINY) in the above control system, can be derived from the following formulas, assuming that the signals are sine waves.

$$T_1 \times Ich = T_2 \times Idis$$

(8-1)

$$T_1 = (1 - \frac{2}{\Pi} \sin^{-1} \frac{V \cos - V_{SH}}{V_p}) \times T$$

(8-2)

$$T_{1} = \left(1 - \frac{2}{\Pi} \sin^{-1} \frac{V \operatorname{com} - V_{SH}}{Vp}\right) \times T$$

$$T_{2} = \left(1 - \frac{2}{\Pi} \sin^{-1} \frac{V \operatorname{com} - V_{SL}}{Vp}\right) \times T$$

(8-2)

(8-3)

From formulas (8-1), (8-2), and (8-3) we have:

$$\sin^{-1}\frac{V\text{com} - V_{\text{SH}}}{Vp} - \frac{I\text{dis}}{I\text{ch}} \sin^{-1}\frac{V\text{com} - V_{\text{SL}}}{Vp} = \frac{\Pi}{2} \left(1 - \frac{I\text{dis}}{I\text{ch}}\right)$$

(8-4)

Here, since the final amplitude of the AGC loop is mainly determined by V<sub>SH</sub>, the above formulas give the final differential peak voltage V<sub>PDF</sub> to be:

$$V_{PDF} = 4 (V_{com} - V_{SH}) \times m$$

(8-5)

m = 1.02 to 1.04

$V_{com} = 0.824 \times (V_{CC} - V_{BF})$

$V_{BE} = 0.75 \text{ V}$

Figure 8-2 Amplitude Detection

Although the  $V_{PDF}$  mentioned above is determined from the I/O dynamic range and other parameters of the various amplifiers, A  $V_{PDF}$  of about 1.5 V is appropriate. Therefore, (Vcom –  $V_{SH}$ ) will be in the 0.36 to 0.37 V range. Also, although a  $V_{SL}$  level of about

$$Vcom - V_{SL} = \frac{1}{2} (Vcom - V_{SH})$$

(8-6)

is usually acceptable, it is necessary to determine it according to the discrimination specifications. That is, determine  $V_{SH}$  an  $V_{P}$  from formula (8-4), and  $V_{SL}$  based on an Ich of 0.55 mA and an Idis of 0.13 mA. Here, attenuation of signal amplitude within the disk with respect to external amplitudes must be considered.

When the input amplitude at this time is attenuated instantaneously from the previous levels, if that attenuated amplitude is not larger than  $(Vcom-V_{SL})$ , then the time to recover to a fixed voltage will become extremely long.

#### 9. Application Hints

When the AGC amplifier inputs (RINX and RINY) are attenuated to 50% of their prior values, since the AGC amplifier will continue to amplify at the previous gain for the period of a single cycle, the signals on AGCINX and AGCINY (the AGC control circuit inputs) will also be attenuated by 50%. Next, to increase these to the amplitude determined by  $V_{SH}$ , the charge/discharge capacitor will be gin to discharge. Since this discharge must take a 50% amplitude to 100%, the amount of the discharge will correspond to the VAGC potential for increasing the gain by a factor of 2. Here, the AGC amplifier gain is given by formula (5-1), and since the required discharge should double this, taking

$$V_2 = \frac{1}{a} (V_{AGC2} - V_{REF})$$

to be the voltage to double the amplification at  $V_1 = \frac{1}{a} (V_{AGC2} - V_{REF})$ , the

formula

$$[1/\{1 + \exp(qV_1/kT)\}] \times 2 = 1/\{1 + \exp(qV_2/kT)\}$$

(9-1)

is established. Also, since the amount of the voltage drop due to this discharge is  $V_1 - V_2 = \frac{1}{a}$  ( $V_{AGC1} - V_{AGC2}$ ), the time required for this drop is:

$$t = \frac{C_{CD} (V_1 - V_2)}{Idis} = \frac{C_{CD} \frac{1}{a} (V_{AGC1} - V_{AGC2})}{Idis}$$

(9-2)

Inversely, if the AGC amplifier input is suddenly doubled, the time required is:

$$t = \frac{C_{CD} (V_1 - V_2)}{Ich} = \frac{C_{CD} \frac{1}{a} (V_{AGC1} - V_{AGC2})}{Ich}$$

(9-3)

Note that if the AGC amplifier input is attenuated, it is necessary that the attenuated amplitude be grater than  $(Vcom-V_{SL})$ . If it is smaller than  $(Vcom-V_{SL})$ , the recovery will be extremely slow.