LSH33

#### FEATURES

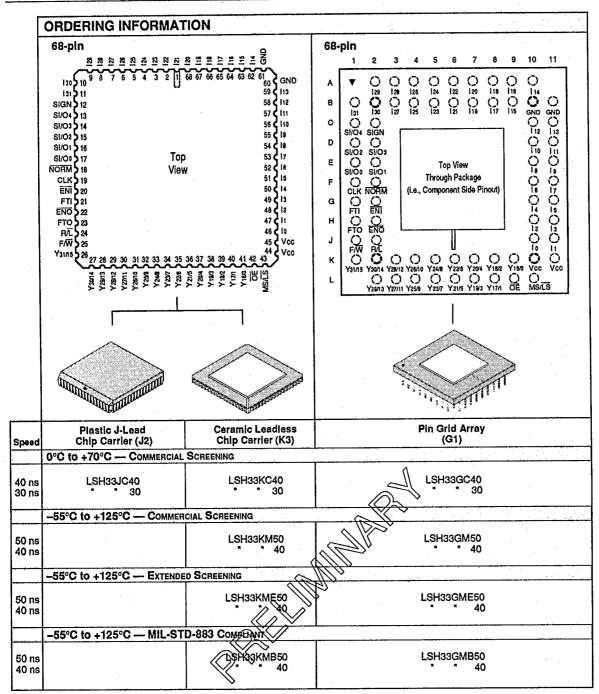

- ☐ 32-bit Input, 32-bit Output Multiplexed to 16 Lines

- ☐ Full 0-31 Position Barrel Shift Capability

- ☐ Integral Priority Encoder for 32-bit Floating Point Normalization

- ☐ Sign-Magnitude or Two's Complement Mantissa Representation

- 32-bit Linear Shifts with Sign or Zero Fill

- ☐ Fully Registered Input/Output with Independent Bypass Paths

- Package Styles Available:

- 68-pin Plastic LCC, J-Lead

- 68-pin Ceramic LCC (Type C)

- 68-pin Pin Grid Array

#### DESCRIPTION

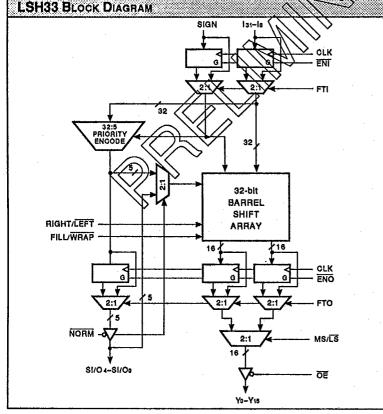

The LSH33 is a 32-bit high speed shifter designed for use in floating point normalization, word pack/unpack, field extraction, and similar applications. It has 32 data inputs, and 16 output lines. Any shift configuration of the 32 inputs, including circular (barrel) shifting, left shifts with zero fill, and right shift with sign extend are possible. In addition, a built-in priority encoder is provided to aid floating point normalization.

Input/Output registers provide complete pipelined operation. Both have independent bypass paths to complete flexibility.

#### **Shift Array**

The 32 registered inputs to the LSH33 are applied to a 32-bit shift array. The 32 outputs of this array can be registered, then are multiplexed down to 16 lines for presentation at the device outputs. The array may be configured such that any contiguous 16-bit field (including wraparound of the 32 inputs) may be presented to the output pinsunder control of the shift code field (Wrap mode). Alternatively, the wrap feature may be disabled, resulting in zero or sign bit fill, as appropriate (fill mode). The shift code control assignments and the resulting input to output mapping for the wrap mode are shown in Table 1.

Essentially the LSH33 is configured as a left shift device. That is, a shift code of 000002 results in no shift of the input field. A code of 000012 provides an effective left shift of 1 position, etc. When viewed as a right shift, the shift code corresponds to the two's complement of the shift distance, i.e., a shift code of 111112 (-110) results in a right shift of one position, etc.

When not in the wrap mode, the LSH33 fills bit positions for which there is no corresponding input bit. The fill value and the positions filled depend on the Right/Left (R/L) direction pin. This pin is a don't care input when in wrap mode. For left shifts in fill mode, lower bits are filled with zero as shown in Table 2. For right shifts, however, the SIGN input is used as the fill value. Table 3 depicts the bits to be filled as a function of shift code for the right shift case. Note that the R/L input changes only the fill convention, and does not affect the definition of the shift code.

LOGIC

DEVICES INCORPORATED

LSH33

T-46-09-09

| TABLE 1. V | **** | NOUE S      |             | OU.S | Perini | ********* | ******* | *******    |            |                  |

|------------|------|-------------|-------------|------|--------|-----------|---------|------------|------------|------------------|

| Shift Code | Y31  | Y30         | •           | •    | Y16    | Y15       | •       | •          | Y1         | Yo               |

| 00000      | 131  | 130         | . •         | •    | 116    | 115       | •       | •          | ft         | lo               |

| 00001      | 130  | 129         | •           | •    | 115    | l14       | •       | •          | 10         | 131              |

| 00010      | 129  | 128         | •           | •    | 114    | 113       | •       | •          | 129        | 130              |

| 00011      | 128  | 127         | • .         | •    | 113    | 112       | •       | •          | 130        | 129              |

| •          |      | •           | •           | •    | •      | •         | •       | •          | •          | •                |

| •          | •    | •           | •           | •    | •      | •         | •       | •          | •          | •                |

| •          | •    | •           | •           | •    | •      | •         | . •     | •          | •          | •                |

| 01111      | 116  | 115         | <b>l</b> 14 | ٠    | li ·   | lo        | •       | •          | 118        | 117              |

| 10000      | 115  | <b>l</b> 14 | 113         | •    | lo     | 131       | . •     | •          | 117        | 116              |

| 10001      | 114  | 113         | 112         | •    | 131    | 130       | •       | •          | 116        | 115              |

| 10010      | 113  | 112         | <b>i</b> 11 | •    | 130    | 129       | •       | •          | 115        | 114              |

| •          | •    | •           | •           | ٠    | •      | •         | •       | •          | •          | •                |

| •          | •    | •           | •           | •    | •      | •         | •       | •          |            | *<               |

| •          | •    | •           | •           | •    | •      | •         | •.      | •          | •          | ~·               |

| 11100      | 113  | 112         | 11          | •    | 120    | 119       | •       | •          | is (       | 174              |

| 11101      | 12   | l1          | lo          | •    | 119    | 118       | •       | •          | (A)        | Ya               |

| 11110      | l1   | lo          | 131         | •    | 118    | 117       | •       | <b>(</b> - | <u>12/</u> |                  |

| 11111      | lo   | [31         | 130         |      | 117    | 116       | •       | 11         | 12         | $\gamma_{\rm h}$ |

| TABLE 2. F | ILL Mo | DE SH | IFT Col            | DE DE      | FINITIO  | из (Це                                 | T SHIP   | KK. | <u> </u> |    |

|------------|--------|-------|--------------------|------------|----------|----------------------------------------|----------|-----|----------|----|

| Shift Code | Y31    | Y30   | •                  | •          | Y16      | Y15                                    | [:/]     | •   | Yı       | Yo |

| 00000      | 131    | 130   | •                  | •          | Ŷ16      | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | <u>ر</u> | •   | 11       | lo |

| 00001      | 130    | 129   | •                  | •<         | ( Jyg/   | ) No                                   | •        | •   | lo       | 0  |

| 00010      | 129    | 128   | • ,                |            | XK4 /    | <b>/</b> 113                           | •        | •   | 0        | 0  |

| 00011      | 128    | 127   | •//                | ار<br>ا    | <u> </u> | <b>l</b> 12                            | •        | •   | 0        | 0  |

| •          | •      | •     | $\mathfrak{S}_{I}$ | <b>X</b> ( | V,       | • .                                    | •        | •   | •        | •  |

| •          | •      | •<<   | (                  | 17)        | •        | •                                      | • .      | •   | • .      | •  |

| •          | • -    | • `   | <b>X</b>           | •          | •        | •                                      | •        | •   | •        | •  |

| 01111      | 116    | 15    | 112                | •          | 11       | lo                                     | •        | ٠.  | 0        | 0  |

| 10000      | 115    | 114   | 113                | •          | lo       | 0                                      | •        | •   | 0        | 0  |

| 10001      | 114    | · l13 | 112                | •          | 0        | 0                                      | •        | •   | 0        | 0  |

| 10010      | 113    | 112   | 111                | •          | 0        | 0                                      | •        | •   | 0        | 0  |

| •          | •      | •     | •                  | •          | •        | •                                      | •        | •   |          | •  |

| •          | •      | •     | •                  | •          | •        | •                                      | •        | •   | •        | •  |

| •          | •      | •     | •                  | •          | •        | •                                      | •        | •   | •        | •  |

| 11100      | lз     | 12    | lı                 | •          | 0        | 0                                      | •        | •   | 0        | 0  |

| 11101      | 12     | lı .  | lo                 | •          | 0        | 0                                      | •        | •   | 0        | 0  |

| 11110      | lı     | lo    | 0                  | •          | 0        | 0                                      | •        | •   | 0        | 0  |

| 11111      | lo     | 0     | 0                  |            | 0        | 0                                      | •        | •   | 0        | Ó  |

In fill mode, as in wrap mode, the shift code input represents the number of shift positions directly for left shifts, but the two's complement of the shift code results in the equivalent right shift. However, for fill mode the R/L input can be viewed as the most significant bit of a 6-bit two's complement shift code, comprised of R/L concatenated with the SI4-SI0 lines. Thus a positive shift code (R/L = 0)results in a left shift of 0-31 positions, and a negative code (R/L = 1) a right shift of up to 32 positions. The LSH33 can thus effectively select any contiguous 32-bit field out of a (sign extended and zero Alled) 96-bit "input."

#### Output Multiplexer

The shift array outputs can be registered and then applied to a 2:1 multiplexer controlled by the MS/LS select line. This multiplexer makes available at the output pins either the most significant or least significant 16 outputs of the shift array.

#### **Priority Encoder**

The 32-bit input bus drives a priority encoder which is used to determine the first significant position for purposes of normalization. The priority encoder produces a five-bit code representing the location of the first non-zero bit in the input word. Code assignment is such that the priority encoder output represents the number of shift positions required to left align the first non-zero bit of the input word. Prior to the priority encoder, the input bits are individually exclusive OR'ed with the SIGN input. This allows normalization in floating point systems using two's complement mantissa representation. A negative value in two's complement representation will cause the exclusive OR gates to invert the input data to the encoder. As a result the leading significant digit will always be "1." This affects only the encoder inputs;

DEVICES INCORPORATED

T-46-09-09

| 2-bit | Barrel | Shifter wil | h Registers |             |

|-------|--------|-------------|-------------|-------------|

|       |        |             |             | <del></del> |

| TABLE 3. F | 200 200 200 | 3,317,262,467.0 |     |    | eznange zerese | er grante, merganiy | ********** | 0000000- <b>8</b> 0000 | ********    | ***               |

|------------|-------------|-----------------|-----|----|----------------|---------------------|------------|------------------------|-------------|-------------------|

| Shift Code | Y31         | Y30             | •   | •  | Y16            | Y15                 | •          | •                      | Y1          | Yo                |

| 00000      | s           | S               | •   | •  | s              | s                   | •          | •                      | S           | S                 |

| 00001      | S           | S               | •   | •  | s              | S                   | •          | •                      | S           | 131               |

| 00010      | s           | S               | •   | •  | S              | S                   | •          | •                      | 131         | 130               |

| 00011      | S           | S               | •   | ٠  | S              | S                   | •          | •                      | 130         | 129               |

| •          | •           | •               | •   | •  | •              | •                   | ٠          | •                      | •           | •                 |

| •          | •           | •               | •   | •  | •              | •                   | •          | •                      | •           | ٠                 |

| •          | •           | •               | •   | •  | •              | •                   | •          | •                      | •           | •                 |

| 01111      | S           | S               | S   | •  | S              | S                   | •          | •                      | <b>l</b> 18 | 117               |

| 10000      | S           | S               | s   | •  | S              | l31                 | •          | •                      | 117         | <b>l</b> 16       |

| 10001      | S           | s               | s   | •. | 131            | 130                 | •          | •                      | 116         | lt5               |

| 10010      | S           | S               | S   | •  | 130            | 129                 | •          | •                      | 115         | 114               |

| •          | •           | •               | •   | •  | . •            | •                   | •          | •                      | •           | •                 |

| •          | •           | ٠               | •   | •  | •              | •                   | •          | •                      | •           | •<                |

| •          | •           | •               | •   | •  | •              | •                   | •          | •                      | •           | ~:                |

| 11100      | S           | S               | S   | •  | 120            | 119                 | •          | •                      | ls          | 14                |

| 11101      | S           | S               | S   | •  | l19            | 118                 | •          | •                      | (A)         | \\ <del>\</del> \ |

| 11110      | S           | S               | l31 | •  | <b>i</b> 18    | 117                 | •          | . <                    | <u>—13/</u> | 7/18/             |

| 11111      | S           | 131             | 130 | •  | <b>l</b> 17    | 116                 | • ,        | (1)                    | 1/12        | <b>-</b> /1       |

| 131 | 130 | 129 | •••   | <b>l</b> 18 | 115           | 194          | •••             | ∕⁄lo, | Shift Code |

|-----|-----|-----|-------|-------------|---------------|--------------|-----------------|-------|------------|

| 1   | Х   | Х   | •••   | Х           | *//           | \ <u>\</u>   | \ <b>,</b>      | X     | 00000      |

| 0   | 1   | X   | •••   | X,          | /k_           | /x /         | > <del>``</del> | X     | 00001      |

| 0   | 0   | 1   | •••   | X/          | $\mathcal{K}$ | \ <b>%</b> / | •••             | X     | 00010      |

| •   | •   | . • | •••   | //          | //·`          | > <b>`</b>   | •••             | •     | • ,        |

| •   | •   | •   | 1/1   | )) <i>`</i> | //•           | •            | ***             | •     |            |

| 0   | Ŏ   | 0   | .//   | //1         | X             | X            | •••             | X     | 01111      |

| 0   | 0   | 0   | ••• ` | 1/20        | 1             | X            | ***             | X     | 10000      |

| 0   | 0   | 0   | ***   | Ô           | 0             | 1            | •••             | X     | 10001      |

| . • | •   | •   | •••   | •           | •             | •            | ***             | •     | •          |

| •   | •   | •   | ***   | •           | •             | •            | ***             | •     | •,         |

| Ö   | 0   | 0   | ***   | 0           | 0             | 0            | •••             | 1     | 11111      |

| 0   | 0   | 0   | 446   | 0           | 0             | 0            | ***             | Ò     | 11111      |

the shift array always operates on the raw input data. The priority encoder function table is shown in Table 4.

#### Normalize Multiplexer

The NORM input, when asserted, results in the priority encoder output driving the internal shift code inputs directly. When using the NORM function, the LSH33 should be placed in fill mode, with the R/L input low.

When NORM is high (not asserted), the SI/O4-SI/O0 port acts as the shift code input to the shifter.

### **Applications** Examples

Normalization of mantissas up to 32 bits can be accomplished directly by a single LSH33. The NORM input is asserted, and fill mode and left shift are selected. The normalized mantissa is then available at the device output in two 16-bit segments, under the control of the output data multiplexer select, the MS/LS.

If it is desirable to avoid the necessity of multiplexing output data in 16-bit segments, two LSH33 devices can be used in parallel. Both devices receive the same input word, with the MS/LS select line of one wired high, and the other low. Each device will then independently determine the shift distance required for normalization, and the full 32 bits of output data will be available simultaneously.

5-153

.

T-46-09-09

| Storage temperature                       |                  |

|-------------------------------------------|------------------|

| Operating ambient temperature             |                  |

| Vcc supply voltage with respect to ground |                  |

| Input signal with respect to ground       | _3.0 V to +7.0 V |

| Signal applied to high impedance output   |                  |

| Output current into low outputs           |                  |

| OPERATING COND |  |  |  |

|----------------|--|--|--|

|                |  |  |  |

|                |  |  |  |

|                |  |  |  |

|                |  |  |  |

Mode

Temperature Range (Ambient

Supply Voltage

Active Operation, Commercial Active Operation, Military

0.0 to +x0.0

4.75 V ≤ Vcc ≤ 5.25 V 4.50 V ≤ Vcc ≤ 5.50 V

| ELECTRI     | cal Characteristics O  | ver Operating Conditions              |     |          |      |      |

|-------------|------------------------|---------------------------------------|-----|----------|------|------|

| Symbol      | Parameter              | Test Condition.                       | Min | Тур      | Max  | Unit |

| <b>V</b> он | Output High Voltage    | 10H 9 - 28 MA                         | 2.4 |          |      | ٧    |

| <b>V</b> OL | Output Low Voltage     | lob.⇒9.0 mA                           |     |          | 0.5  | ٧    |

| ۷н          | Input High Voltage     | <b>→</b>                              | 2.0 |          | Vcc  | ٧    |

| ViL         | Input Low Voltage      | (Note 3)                              |     |          | 0.8  | ٧    |

| lix         | Input Current          | Ground ≤ VIN ≤ VCC                    |     |          | ±20  | μΑ   |

| loz         | Output Leakage Current | Ground ≤ Vο∪τ ≤ Vcc                   |     |          | ±20  | μΑ   |

| los         | Output Short Current   | Vout = Ground, Vcc = Max (Notes 4, 8) |     |          | -250 | mA   |

| ICC1        | Vcc Current, Dynamic   | (Notes 5, 6)                          | 1   | 10       | 30   | mA   |

| loc2        | Vcc Current, Quiescent | (Note 7)                              |     | <u> </u> | 1.0  | mA   |

T-46-09-09

LSH3

## SWITCHING CHARACTERISTICS - COMMERCIAL OPERATING RANGE (0°C to +70°C) Notes 9, 10

| GUARANTEED MAXIMUI                                       | u Combinatii | ONAL DELAYS (F   | s)     |                     |  |

|----------------------------------------------------------|--------------|------------------|--------|---------------------|--|

| To Output                                                | LS           | 133-40           | LS     | H33-30              |  |

| From Input                                               | Y15-Y0       | SO4-SO0          | Y15-Y0 | SO4-SO <sub>0</sub> |  |

| FTI = 0, FTO = 0<br>CLK<br>MS/LS                         |              |                  |        |                     |  |

| FTI = 0, FTO = 1  CLK  SI4-SI0  R/L, F/W  MS/LS          |              |                  |        |                     |  |

| FTI = 1, FTO = 0<br>CLK<br>MS/LS                         |              |                  |        |                     |  |

| FTI = 1, FTO = 1  131-10, SIGN  SI4-SI0  R/L, F/W  MS/LS |              | _<br>_<br>_<br>_ |        |                     |  |

|                          | l     | LSH            | 33-40/ | /) · | 1     | LSH3 | 3-30  |      |             |   |   |

|--------------------------|-------|----------------|--------|------|-------|------|-------|------|-------------|---|---|

| Input                    | FTI   | <del>7</del> 9 | N FT   | =1   | Fil   | = 0  | FTI   | = 1  |             | 1 |   |

|                          | Setup | HÓH            | Setup  | Hold | Setup | Hold | Setup | Hold |             |   |   |

| 1-lo, SIGN               |       |                | }      |      |       |      |       |      |             |   |   |

| 14-SI0                   | 1     |                |        |      |       |      |       |      |             |   | 4 |

| / <b>L</b> , F/ <b>W</b> |       | <b>V</b>       |        |      |       |      | -     |      | <del></del> |   |   |

| /Ľ, F/W<br>NI. ENO       |       | ·              |        |      |       |      | -     |      | <br>        |   |   |

| HREE S | TATE <b>E</b> NABLE/ | DISABLE TIM | E\$ (ns) Note |

|--------|----------------------|-------------|---------------|

|        | LSH33-40             | LSH33-30    |               |

| ten    |                      |             |               |

| tDIS   |                      |             |               |

| CLOCK CYCLE TIME AN | ID PULSE WID | TH (ns)  |  |

|---------------------|--------------|----------|--|

|                     | LSH33-40     | LSH33-30 |  |

| Minimum Cycle Time  |              |          |  |

| Highgoing Pulse     |              |          |  |

| Lowgoing Pulse      |              |          |  |

| _ | _   | _ |    | _  |

|---|-----|---|----|----|

| _ | _   |   |    | _  |

|   | _ = |   | == | _  |

| = | = = |   |    | _  |

|   |     |   |    | _= |

|   | =   | = | == | _  |

DEVICES INCORPORATED

= Logic Products

5-155

5/15/90

T-46-09-09

# SWITCHING CHARACTERISTICS - MILITARY OPERATING RANGE (-55°C to +120°C) Notes 9, 10

| GUAHANTEED MAXIMUN                                               | u Combinatio | ONAL DELAYS (N | 5)     |                  |          |

|------------------------------------------------------------------|--------------|----------------|--------|------------------|----------|

| To Output                                                        | LSI          | 133-50         | LS     | H33-40           |          |

| From Input                                                       | Y15-Y0       | SO4-SO0        | Y15-Y0 | SO4-SO0          |          |

| FTI = 0, FTO = 0<br>CLK<br>MS/LS                                 |              |                |        | -                |          |

| FTI = 0, FTO = 1  CLK  SI4-SI0  R/L, F/W  MS/LS                  |              | _<br>_<br>_    |        | -<br>-<br>-<br>- |          |

| FTI = 1, FTO = 0<br>CLK<br>MS/LS                                 |              |                |        |                  | <b>*</b> |

| FTI = 1, FTO = 1<br>131-lo, SIGN<br>SI4-SIO<br>R/L, F/W<br>MS/LS |              | _<br>_<br>_    |        |                  |          |

|              |       | LSH            | 33-50 | /)`  |       | LSH3       | 3-40  | ·    | <br> | <br> |

|--------------|-------|----------------|-------|------|-------|------------|-------|------|------|------|

| input        | FIL   | <del>7</del> 9 | FT    | =1   | FII   | <b>=</b> 0 | FTI   | =1   |      |      |

|              | Setup | HOHE           | Setup | Hold | Setup | Hold       | Setup | Hold |      |      |

| la1-lo, SIGN |       |                | }     |      |       |            |       |      |      |      |

| SI4-SI0      | 13    | 2              |       |      |       |            |       |      |      |      |

| R/L, F/W     |       | <b>Y</b>       |       |      |       |            |       |      |      |      |

| Three S | TATE ENABLE | DISABLE TIM | ES (ns) Note 11 |

|---------|-------------|-------------|-----------------|

|         | LSH33-50    | LSH33-40    |                 |

| ten     |             |             |                 |

| tois    |             |             |                 |

| CLOCK CYCLE TIME AND PULSE WIDTH (NS) |          |          |  |  |  |  |

|---------------------------------------|----------|----------|--|--|--|--|

|                                       | LSH33-50 | LSH33-40 |  |  |  |  |

| Minimum Cycle Time                    |          |          |  |  |  |  |

| Highgoing Pulse                       |          |          |  |  |  |  |

| Lowgoing Pulse                        |          |          |  |  |  |  |

| LVuit | ≘ | 0 | == | Ξ | = | Ξ |

|-------|---|---|----|---|---|---|

|-------|---|---|----|---|---|---|

DEVICES INCORPORATED

T-46-09-09

## NOTES

- 1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied, Exposure to maximum rating conditions for extended periods may affect reliability.

- 2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

- 3. This device provides hard clamping of transient undershoot and overshoot Input levels below ground or above VCC will be clamped beginning at -0.6 V and VCC + 0.6 V. The device our withstand indefinite operation with inputs in the range of -3.0 V to -7.0 V. Device operation will not be adversely affected, however, input current levels will be well in excess of 100 mA.

- 4. Duration of the output short circuit should not exceed 30 seconds.

5. Supply current for a given application can be accurately approximated by:

NCV<sup>2</sup>F

where

N = total number of device outputs

C = capacitive load per output

V = suppy voltage

F = clock frequency

- 6. Tested with all outputs changing every cycle and no load at a 5 MHz clock rate.

- 7. Tested with all inputs within 0.1 V of VCC or Ground no load.

- 8. These parameters are guaranteed but not 100% tested.

- 9.AC specifications tested with input transition times less than 3 ns, output reference levels of 1.5 V (except tEN/ tols test) and input levels of nominally 0 to 3.0 V. Output loading is a resistive divider which provides for specified IOL and IOH plus 30 pF capacitance.

This device has high speed outputs capable of large instantaneous current pulses and fast turn-on/turn-off times. As a result, care must be exercised in the testing of this device. The following measures are recommended:

- a. A 0.1 µF ceramic capacitor should be installed between VCC and Ground leads as close to the Device Under Test (DUT)\as possible. Similar capacitors should be installed between device VCC and the tester common, and device ground and tester common.

- Ground and VCC supply planes must be brought directly to the DUT socket or contactor fingers.

- c. Input voltages should be adjusted to compensate for inductive ground and VCC noise to maintain required DUT input levels relative to the DUT ground

- 10. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. Setup time, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from the point of view of the device. Output delay, for example, is specified as a maximum since worst-case operation of any device always provides data within that time,

- 11. Transition is measured ±200 mV from steady-state voltage with specified loading.

T-46-09-09

| # |    |            |      |

|---|----|------------|------|

| = | == | <b>#</b> = | == = |

|   | ~  | -          | ==   |

|   |    |            |      |