032778

001366

Orig

G8860 G8860X

# **Microcircuits**

T1366

5-39

6-18

## **CMOS DTMF Decoder**

#### **Features**

- 18 pin DIP package

- Central office quality detection

- Excellent voice talk-off

- Detect times down to 20mS

- Single supply 5V or 8 to 13V operation

- Latched 3 state buffered outputs

- Detects all 16 DTMF combinations

- Uses inexpensive 3.58MHz crystal

- Low power CMOS circuitry

#### Adjustable acquisition & release times

## Used in DTMF Receivers For:

- End to end signaling

- Control systems

- PABX

- Central office

**Applications**

- Mobile radio

- Key systemsTone to pulse converters

## Description

The GTE G8860 and G8860X detects and decodes all 16 DTMF tone pairs. The device accepts the high group and low group square wave signals from a DTMF filter (G8865/G8865X) and provides a 3 state buffered 4 bit binary output. The clock signals are derived from an on chip oscillator requiring a single resistor and low cost TV crystal as external components. The G8860 and G8860X are produced using state-of-the-art CMOS technology and incorporate an on chip regulator, providing low power operation and power supply flexibility. The G8860X differs from the G8860 in that it contains an improved decode algorithm which provides enhanced talk-off performance. The G8860X also features faster and more closely-controlled response time. The G8860X may be used as a direct replacement for the G8860 in existing designs, provided consideration is given to the effect of shorter response time on system performance.

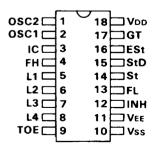

#### Pin Function

| Pin   | Description            |

|-------|------------------------|

| OSC1  | Clock Input            |

| OSC2  | Clock Output           |

| IC    | Internal Test Run      |

| FH    | High Freq. Group Input |

| L1-L4 | Data Outputs           |

| Pin | Description             |  |  |  |

|-----|-------------------------|--|--|--|

| TOE | Output Enable Input     |  |  |  |

| INH | Inhibit Input           |  |  |  |

| FL  | Low Freq. Group Input   |  |  |  |

| St  | Steering Input          |  |  |  |

| StD | Delayed Steering Output |  |  |  |

| Pin | Description           |  |  |  |

|-----|-----------------------|--|--|--|

| ESt | Early Steering Output |  |  |  |

| GT  | Guard Time Output     |  |  |  |

| VDD | Positive Power Supply |  |  |  |

| Vss | Internal Logic GND    |  |  |  |

| VEE | Neg. Supply           |  |  |  |

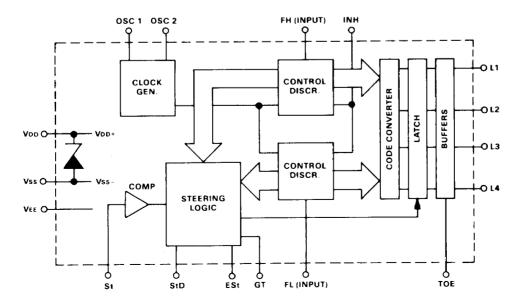

#### **Block Diagram**

#### **Pin Configuration**

## Absolute Maximum Ratings:(Note 1)

| Parameter                               | Symbol | Value              |

|-----------------------------------------|--------|--------------------|

| VDD - VEE                               | Vdc    | 15V Max.           |

| VDD - VSS (Low Impedance Supply)        | Vdc    | 5.5V Max.          |

| Voltage on any pin except OSC1 and OSC2 | Vdc    | VEE -0.3, VDD +0.3 |

| Voltage on OSC1 and OSC2                | Vdc    | Vss -0.3, VDD +0.3 |

| Current on any pin except VDD and VEE   | loo    | 10mA Max.          |

| Operating temperature                   | TA     | -40°C to +85°C     |

| Storage temperature                     | Ts     | -65°C to +150°C    |

| Power dissipation (2)                   | Р      | 1000 mW Max.       |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages.

## DC Characteristics: All voltages referenced to VEE unless otherwise noted. VDD (See Note 4), TA = 25°C, fc = 3.579545 MHz

| Parameter                         | Symbol | Min         | Typ (3) | Max  | Unit | Test Conditions      |

|-----------------------------------|--------|-------------|---------|------|------|----------------------|

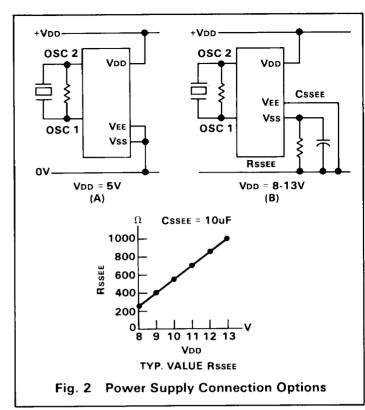

| Operating Supply Voltage          | VDD    | 4.75        | 5       | 5.25 | V    | Connections Fig. 2a  |

| (VDD - VEE)                       |        | 8           |         | 13   | V    | Connections Fig. 2b  |

| Internal Logic Ground Voltage     | VDDSS  | 4.75        |         | 5.25 | V    | Connections Fig. 2a  |

| (VDD - VSS)                       |        | 6.0         | 6.5     | 7.5  | V    | ldd = 7mA            |

| Operating Supply Current          | loo    |             | 1.3     | 4    | mA   | 5V                   |

| , , ,                             |        | <del></del> | 2.5     | 5    | mA   | 12V, VDD - VSS = 5.5 |

| Internal Logic Ground Pin Current | Iss    |             | 5.5     | 6.7  | mA   | 12V, RSSEE = 900 Ω   |

| Operating Power Consumption       | Po     | •           | 6.5     |      | mW   | 5V                   |

| ,                                 |        |             | 66      |      | mW   | 12V                  |

| High Level Input Voltage          | ViH    | 3.5         |         |      | V    | 5V                   |

| (All Inputs Except OSC1)          |        | 8.5         |         |      | V    | 12V                  |

| Low Level Input Voltage           | VIL    |             |         | 1.5  | V    | 5V                   |

| (All Inputs Except OSC1)          |        |             |         | 3.5  | V    | 12V                  |

| High Level Input Voltage          | Viho   | 3.5         |         |      | V    | 5V                   |

| OSC1                              |        | 10.5        |         |      | V    | 12V                  |

| Low Level Input Voltage           | Vilo   |             |         | 1.5  | V    | 5V, Ref Vss          |

| OSC1                              |        |             |         | 1.5  | V    | 12V, Ref Vss         |

| Steering Input Threshold          | VTSı   | 2.04        | 2.27    | 2.5  | V    | 5V                   |

| Voltage                           |        | 5.4         | 6.0     | 6.6  | V    | 12V                  |

| Pull Down Sink Current            | Isı    | 10          | 25      | 75   | μΑ   | 5V                   |

| (INH)                             |        | 10          | 190     | 400  | μΑ   | 12V                  |

| Pull Up Source Current            | Iso    | 2           | 7       | 45   | μΑ   | 5V + 12V             |

| (TOE)                             |        |             |         | Ì    |      |                      |

| Input High Leakage Current        | liH    |             | 0.1     | 1.5  | μΑ   | 5V or 12V            |

| Input Low Leakage Current         | lic    |             | 0.1     | 1.5  | μА   |                      |

| High Level Output Voltage         | Voн    | 4.9         |         |      | V    | 5V                   |

| (All Outputs Except OSC2)         |        | 11.9        |         |      | V    | 12V                  |

| Low Level Output Voltage          | Vol    |             |         | 0.1  | V    | 5V                   |

| (All Outputs Except OSC2)         |        |             |         | 0.1  | ٧    | 12V                  |

| High Level Output Voltage         | Vоно   | 4.9         |         |      | V    | 5V                   |

| OSC2                              |        | 11.9        |         |      | V    | 12V                  |

## **DC Characteristics (Continued)**

| Parameter Low Level Output Voltage |           | Symbol | Min | Тур   | Max | Unit | Test Conditions     |

|------------------------------------|-----------|--------|-----|-------|-----|------|---------------------|

|                                    |           | Vol    | VoL |       | 0.1 | V    | 5V, Ref Vss         |

| OSC2                               | -         |        |     |       | 0.1 | ٧    | 12V, Ref Vss        |

| Output Drive                       | P Channel | Іон    | 0.4 | 0.6   |     | mA   | 5V, Voн = 4.6V      |

| Current                            | Source    |        | 0.5 | 0.8   |     | mA   | 12V, Voн = 11.5V    |

| (All Outputs                       | N Channel | loL    | 0.8 | 1.2   |     | mA   | 5V, VoL = 0.4V      |

| Except OSC2)                       | Sink      | ,      | 1.0 | 1.6   |     | mA   | 12V, Vol = 0.5V     |

| Output Drive                       | P Channel | Іон    | 90  | 120   |     | μΑ   | 5V, Voн = 4.6V      |

| Current                            | Source    |        | 90  | 120   |     | μΑ   | 12V, VoH = 11.5V    |

| OSC2                               | N Channel | lou    | 100 | 160   |     | μΑ   | 5V, Vol = 0.5V      |

|                                    | Sink      |        | 100 | 160   |     | μΑ   | 12V, VoL = 0.5V     |

| Tristate Output                    | L1-L4 = H |        |     | 0.035 | 1.5 | μА   | 5V, Appl Vol = 0V   |

| Current                            | L1-L4 = L |        |     | 0.1   | 1.5 | μА   | 5V, Appl Von = 5V   |

| (High Impedance                    | L1-L4 = H | loz    |     | 0.1   | 1.5 | μА   | 12V, Appl Vol = 0V  |

| State)                             | L1-L4 = L |        |     | 0.3   | 1.5 | μА   | 12V, Appl Voн = 12V |

## AC Characteristics: VDD = 5V Unless Otherwise Noted, TA = 25°C, fc = 3.579545 MHz

| Pa                              | arameter           | Symbol          | Min            | Typ <sup>(3)</sup> | Max    | Unit   | Test Con  | ditions    |

|---------------------------------|--------------------|-----------------|----------------|--------------------|--------|--------|-----------|------------|

| Tone Frequency D                | eviation Accept    | ∆fA             |                |                    | ±2.5   | % Nom. |           |            |

| Tone Frequency Deviation Reject |                    | ∆fR             | ±3.5           |                    |        | % Nom. |           |            |

| Tone Present Detec              | tion Time (G8860)  | t <sub>DP</sub> | 8              | 10                 | 15     | mS     |           |            |

| Tone Absent Detec               | tion Time (G8860)  | t <sub>DA</sub> | Ø.6            | 4                  | 10     | mS     |           |            |

| Tone Present Detec              | tion Time (G8860X) | t <sub>DP</sub> | 6              |                    | 10     | mS     |           |            |

| Tone Absent Detec               | tion Time (G8860X) | t <sub>DA</sub> | 0              |                    | 6      | mS     |           |            |

| Guard Time                      |                    | tGT(P or E)     | A              | djustable Functio  | ns     |        |           |            |

| Time to Receive =               | (tDP + tGTP)       | tREC            |                | of tgt.            |        |        |           |            |

| Invalid Tone Durat              | ion (fn of tREC)   | tREC            |                | See Figs. 3 and 4  |        |        |           |            |

| Interdigit Pause =              | (tda + tgta)       | tiD             |                | and                |        |        |           |            |

| Acceptable Drop Out (fn of tip) |                    | tDO             | Timing Diagram |                    |        |        |           |            |

| FL FH Input Transition Time     |                    | tT              |                |                    | 1.0    | μS     | 10% - 9   | 0% Vdd     |

| Capacitance Any Input           |                    | С               |                | 5                  | 7.5    | pF     |           |            |

| Propagation Delay               | St to L1-L4        | <b>TPL</b>      |                | 8                  | 11     | μS     | 5V or     | 12V        |

| Propagation Delay               | St to StD          | tPStD           |                | 12                 | 14     | μS     | 5V or     | 12V        |

| Synch. Delay L1-L               | 4 to StD           | tQStD           |                | 3.43               |        | μS     |           |            |

| Propagation                     | Enable             | tpte .          |                | 300                |        | nS     | . 5'      | V          |

| Delay TOE to                    |                    |                 |                | 200                |        | nS     | 12        | !V         |

| L1-L4                           | Disable            | tPTD .          |                | 300                |        | nS     | 5         | V          |

|                                 |                    |                 |                | 200                |        | nS     | 12        | <u>V</u>   |

| Crystal/Clock Free              | quency             | fc              | 3.5759         | 3.5795             | 3.5831 | MHz    | OSC1      | OSC2       |

| Clock                           | Rise Time          | tLHCI           |                |                    | 110    | nS     | 10%-90%   | Externally |

| Input                           | Fall Time          | thLCI           |                |                    | 110    | nS     | VDD - Vss | Applied    |

| (OSC1)                          | Duty Cycle         | DCci            | 40             | 50                 | 60     | %      |           | Clock      |

| Clock Output<br>(OSC2)          | Capacitive<br>Load | CLO             |                |                    | 30     | pF     |           |            |

#### Notes:

- 1. Exceeding these ratings may cause permanent damage. Functional operation under these conditions is not implied.

- 2. Derate 16mW/°C above 75°C. All leads soldered to PC board.

- 3. All "typical" parametric information is for reference only, not guaranteed and not subject to production testing.

- 4. 5 V;  $V_{DD}$   $V_{EE}$  = 5V,  $V_{SS}$  =  $V_{EE}$  connection as Fig. 2a.

- 12V: VDD VEE = 12V, RSSEE = 900  $\Omega$  connection as Fig. 2b.

- 5. Outputs are not loaded unless stated.

- 6. For input current parameters only ViH VIHO = VDD, VIL = VEE, VILO = VSS.

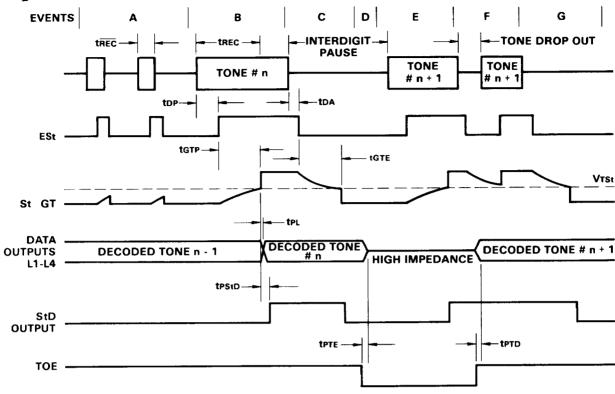

## Timing Diagram

#### EVENTS:

- A) Short tone bursts: detected, tone duration is invalid.

- B) Tone # n is detected, tone duration is valid, decoded to outputs.

- C) End of Tone # n is detected and validated.

- D) 3 stage outputs disabled (high impedance).

- E) Tone # n + 1 is detected, tone duration is valid, decoded to outputs.

- F) Tristate outputs are enabled. Acceptable drop out of Tone # n + 1 does not register at outputs.

- G) End of Tone # n + 1 is detected and validated.

### **Pin Function Table**

| OSC2                 | CLOCK OUTPUT                                                                                                                                                                                                                                                                                           | 3.58MHz crystal with parallel 5M\Omega resistor connected between these pins completes internal oscillator, running between Vpp and Vss. |  |  |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| OSC1                 | CLOCK INPUT                                                                                                                                                                                                                                                                                            | Talling bottoon vocality too.                                                                                                            |  |  |  |  |  |  |  |

| IC                   | Internal connection                                                                                                                                                                                                                                                                                    | Internal connection for testing only. Must be left open circuit.                                                                         |  |  |  |  |  |  |  |

| FH                   | High frequency grou                                                                                                                                                                                                                                                                                    | High frequency group input. Accepts single rectangular wave High group tone from DTMF filter.                                            |  |  |  |  |  |  |  |

| L1<br>L2<br>L3<br>L4 | Data Outputs. 3 state buffered. Provides 4 bit binary word corresponding to the tone pair decoded, when enabled by TOE. See Coding Tables.                                                                                                                                                             |                                                                                                                                          |  |  |  |  |  |  |  |

| TOE                  | 3 state output enab                                                                                                                                                                                                                                                                                    | le input. Logic high on this input enables outputs L1-L4. Internal pull up.                                                              |  |  |  |  |  |  |  |

| Vss                  | Internal logic groun                                                                                                                                                                                                                                                                                   | d. For VDD-VEE = 5V Vss connected to VEE. For VDD-VEE > 8V, Vss connected via resistor to VEE see Fig. 2.                                |  |  |  |  |  |  |  |

| VEE                  | Negative power sup                                                                                                                                                                                                                                                                                     | ply. External logic ground.                                                                                                              |  |  |  |  |  |  |  |

| INH                  |                                                                                                                                                                                                                                                                                                        | high inhibits detection of tones representing characters #, *, A, B, C, D. Internal pull down.                                           |  |  |  |  |  |  |  |

| FL                   | Low frequency grou                                                                                                                                                                                                                                                                                     | p input. Accepts single rectangular wave low group tone from DTMF filter.                                                                |  |  |  |  |  |  |  |

| St                   | Steering input. A voltage greater than VTst on this input causes the device to accept validity of the detected tone pair and latch the corresponding codeword at the outputs. Voltage < VTst on this pin frees the device to accept a new tone pair. See Coding Tables (c) and Functional Description. |                                                                                                                                          |  |  |  |  |  |  |  |

| StD                  | Delayed Steering Output. Flags when a valid tone pair has been received. Presents logic high when output latch updated based on St voltage exceeding VTSt. Returns to logic low when St voltage falls below VTSt.                                                                                      |                                                                                                                                          |  |  |  |  |  |  |  |

| ESt                  | Early Steering Output. Presents a logic high when the digital algorithm detects a recognizable tone pair. Any momentary loss of the incoming tone or excessive distortion of the tone will cause ESt to return to a logic low.                                                                         |                                                                                                                                          |  |  |  |  |  |  |  |

| GT                   | Guard Time Output<br>Coding Tables (c).                                                                                                                                                                                                                                                                | . 3 state output. Normally connected to St, is used in the steering algorithm and is a function of St and ESt. See                       |  |  |  |  |  |  |  |

| VDD                  | Positive power supp                                                                                                                                                                                                                                                                                    | oly.                                                                                                                                     |  |  |  |  |  |  |  |

## **Functional Description**

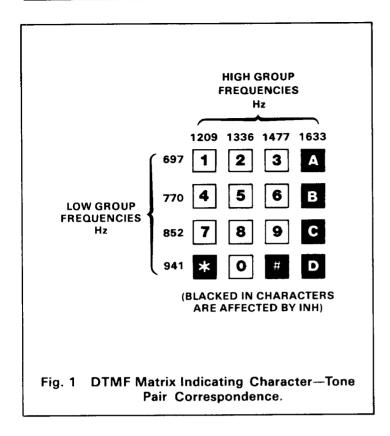

The GTE G8860 and G8860X are CMOS Digital DTMF detectors and decoders. Used in conjunction with a suitable DTMF filter (GTE G8865) it can detect and decode all 16 Standard DTMF tone pairs (Fig. 1), accurately discriminating between adjacent frequencies in both high and low groups in the presence of noise and normal voice signals.

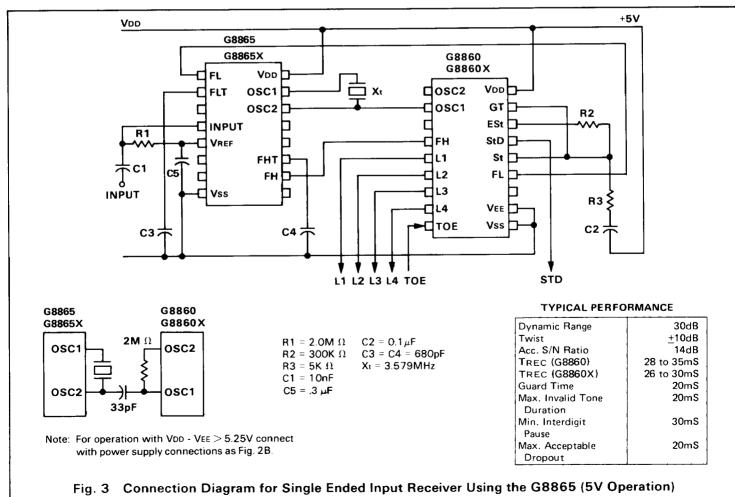

To form a complete DTMF receiver the G8860 must be preceded by a DTMF filter, the function of which is to separate the high group and low group components of the composite dual tone signal and limit the resulting pair of sine wave signals to produce rectangular wave signals having the same frequencies as the individual components of the composite DTMF input. The High Group and Low Group rectangular waves are applied to the G8860 FH and FL inputs respectively. The G8865 DTMF Filter provides these functions.

Within the G8860 the FL and FH signals are operated on by a complex averaging algorithm. This is implemented using digital counting techniques (Control/Discriminators, Block Diagram—Page 1) to determine the frequencies of the incoming tones and verify that they correspond to standard DTMF frequencies. When both High Group and Low Group signals have been simultaneously detected a flag ESt (Logic High) is generated. ESt is generated (cancelled) rapidly on detecting the presence (absence) of a DTMF tone pair (see Timing Diagram) and is used to perform a final validity check.

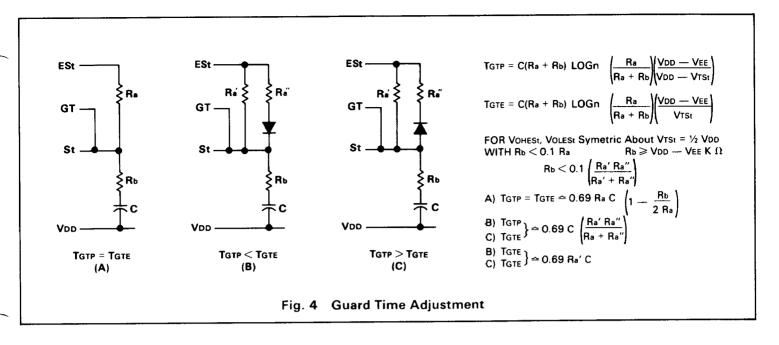

The final validity check requires the input DTMF signal to be present uninterrupted by drop out or excessive distortion (which would result in ESt being cancelled) for a minimum time (trec) before being considered valid. This contributes greatly to the talk off performance of the system. The check also imposes a minimum period of "tone absent" before a valid received tone is recognized as having ended. This allows short periods of drop out (too) or excessive noise to occur during a received tone, without it being misinterpreted as two successive characters by the steering circuit (ESt, St, GT). A capacitor C (Fig. 4a) is charged via resistor R from ESt when a DTMF tone pair is detected. After a period tGTP VC exceeds the St input threshold voltage VSTt setting an internal flag indicating the detected signal is valid. Functioning of the check algorithm is completed by the three state output

GT which is normally connected to St and operates under the control of ESt and St. Its mode of operation is shown by the steering state table (see Coding Tables) and Timing Diagram.

Internally the presence of the ESt flag allows the control/discriminator to identify the detected tones to the code converter which in turn presents a 4 bit binary code word, corresponding to the original transmitted character, to the output latch. The appearance of the internal St flag clocks the latch, presenting the output code at the tristate outputs L1 to L4. The St internal flag is delayed (by tpstD) and appears at the StD output to provide a strobe output function indicating that a new character has been received and the output updated. StD will return to a logic low after the St flag has been reset by VC (Fig. 4a) falling below VTst.

Increasing the "time to receive" tree tends to further improve talk off performance (discrimination against voice simulation of a DTMF tone pair) but degrades the acceptable signal to noise ratio for the incoming signal. Increasing interdigit pause tip further reduces the probability of receiving the same character twice and improves acceptable signal to noise ratio but imposes a longer interdigit pause. Reducing tree or tip has the opposite effect respectively. The values of tree and tip can be tailored by adjusting tree and tree as shown in Fig. 4.

When L1-L4 are connected to a data bus TOE may be controlled by external circuitry or connected directly to StD automatically enabling the outputs whenever a tone is received. In either case StD may be used to flag external circuitry indicating a character has been received.

The G8860 may be operated from either a 5 volt or 8 to 13 volt supply by use of the internal zener reference. The relevant connection diagrams are shown in Fig. 2. When using the G8860 with the G8865 DTMF Filter it is only necessary to use the G8865 crystal oscillator (see Fig. 3). When using the higher supply voltage range the G8865 OSC2 output should be capacitively coupled to the G8860 OSC1 input as shown in Fig. 3.

Where it is desirable to receive only the characters available on a rotary dial telephone, taking INH to a logic high inhibits detection of the additional DTMF characters. Incidentally this also further improves talk off due to the reduced number of detectable tones.

#### **Coding Tables**

#### A. Output Coding

| Orig<br>To<br>Char | ne     | TOE | L4 | L3     | L2 | L1  |

|--------------------|--------|-----|----|--------|----|-----|

|                    | X      | L   | Z  | Z<br>L | z  | Z   |

|                    | 1      | Н   | L  | L      | L  | н   |

|                    | 2      | н   | L  | L      | Н  | L   |

|                    | 2<br>3 | Н   | L  | L      | н  | н   |

|                    | 4      | н   | L  | н      | L  | L   |

| DR                 | 5      | н   | L  | н      | L  | н і |

|                    | 6      | н   | L  | н      | н  | L   |

|                    | 7      | н   | L  | н      | н  | н   |

|                    | 8      | Н   | н  | L      | L  | L   |

|                    | 9      | Н   | Н  | L      | L  | н   |

|                    | 0      | Н   | H  | L      | н  | L   |

|                    | *      | Н   | Н  | L      | Н  | н   |

|                    | #      | н   | Н  | Н      | L  | L   |

| D                  | Α      | Н   | Н  | Н      | L  | н   |

|                    | В      | Н   | Н  | Н      | Н  | L   |

|                    | С      | Н   | H  | Н      | Н  | Н   |

|                    | D      | Н   | L  | L      | L  | L   |

#### **B.** Inhibit Function

| Detected<br>Character | INH | ESt |

|-----------------------|-----|-----|

| None                  | 0   | ٦   |

| X                     | L   | Н   |

| DR                    | н   | Н   |

| D                     | Н   | L   |

C. Steering

| ESt | St | GT | StD(1) |

|-----|----|----|--------|

| L   | L  | L  | L      |

| н   | L  | Z  | L      |

| L   | н  | Z  | i H    |

| н   | Н  | Н  | н      |

#### Notes:

- 1. Delayed WRT St.

- 2. For the purpose of these tables consider:

Vst < VTst LOGIC LOW (L)

Vst > VTSt LOGIC HIGH (H)

- H = LOGIC HIGH

- L = LOGIC LOW

- O = "DON'T CARE" LOGIC HIGH OR LOW

- Z = HIGH IMPEDANCE

- X = ANY CHARACTER

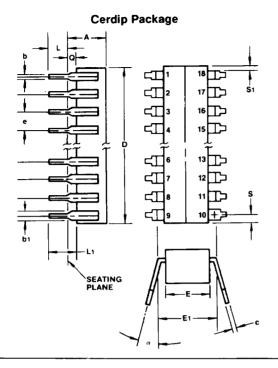

#### **Packaging Information**

|      | 18-PIN PACKAGE |       |             |       |  |  |  |  |

|------|----------------|-------|-------------|-------|--|--|--|--|

| SYM- | INC            | HES   | MILLIMETERS |       |  |  |  |  |

| BOL  | MIN            | MAX   | MIN         | MAX   |  |  |  |  |

| Α    | -              | 0.200 | _           | 5.08  |  |  |  |  |

| b    | 0.014          | 0.023 | 0.36        | 0.58  |  |  |  |  |

| b1   | 0.030          | 0.070 | 0.76        | 1.78  |  |  |  |  |

| С    | 0.008          | 0.015 | 0.20        | 0.38  |  |  |  |  |

| D    | -              | 0.960 | _           | 24.38 |  |  |  |  |

| E    | 0.220          | 0.310 | 5.59        | 7.87  |  |  |  |  |

| E1   | 0.290          | 0.320 | 7.37        | 8.13  |  |  |  |  |

| e    | 0.100          | BSC   | 2.54 BSC    |       |  |  |  |  |

| L    | 0.125          | 0.200 | 3.18        | 5.08  |  |  |  |  |

| L1   | 0.150          | _     | 3.81        |       |  |  |  |  |

| Q    | 0.015          | 0.060 | 0.38        | 1.52  |  |  |  |  |

| S    | _              | 0.098 | -           | 2.49  |  |  |  |  |

| Sı   | 0.005          | -     | 0.13        | _     |  |  |  |  |

| S2   | 0.005          | _     | 0.13        | -     |  |  |  |  |

| α    | 0°             | 15°   | 0°          | 15°   |  |  |  |  |

## **Ordering Information**

Device G8860DI G8860XDI Package 18 Pin Cerdip 18 Pin Cerdip Temp. Range -40°C to +85°C -40°C to +85°C

Sales Offices: Technical or sales assistance may be requested from the GTE Microcircuits area sales office nearest you.

#### Western

GTE Microcircuits 22691 Lambert Street Suite 507 El Toro, CA 92630 Tel: 714/855-9901 TWX: 910-595-2752

#### Central

GTE Microcircuits 3223 N. Frontage Road Suite 2311 Arlington Heights, IL 60004 Tel: 312/259-1112

TWX: 910-687-0282

#### Eastern

GTE Microcircuits 380 Town Line Road Hauppauge, NY 11788 Tel: 516/724-8300 TWX: 510-226-7847

#### Europe

GTE Microcircuits Montenstrasse 11 8000 Munich 19 West Germany Tel: 089/1 78 20 31 Telex: 528452 gtemc d

#### **WARNING:**

MOS CIRCUITS ARE SUBJECT TO DAMAGE FROM STATIC DISCHARGE

Internal static discharge circuits are provided to minimize part damage due to environmental static electrical charge build-ups. Industry established recommendations for handling MOS circuits include:

- 1 Ship and store product in conductive shipping tubes or in conductive foam plastic. Never ship or store product in non-conductive plastic containers or non-conductive plastic foam material.

- 2. Handle MOS parts only at conductive work stations

- Handle MOS parts only at conductive

Ground all assembly and repair tools.

Represented in your area by:

GTE reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.

The information contained herein is provided gratuitously and without liability, to any user. Reasonable efforts have been made to verify the accuracy of the information but no guarantee whatsoever is given as to the accuracy or as to its applicability to particular uses. In every instance, it must be the responsibility of the user to determine the suitability of the products for each application. GTE Microcircuits products are not authorized for use as critical components in life support devices or systems. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents or other rights of third parties. The sale of any GTE Microcircuits product is subject to all GTE Microcircuits Terms and Conditions of Sale and Sales Policies, copies of which are available upon request.

GTE Microcircuits / 2000 West 14th Street / Tempe, Arizona 85281 / (602) 968-4431 / TWX 910-951-1383

Revised July 1984 2001-01-03