# MTC-20276

# Single Chip ISDN NT 2B1Q (INTQ)

Data Sheet

Rev. 2.3 - October 1999

#### **Key Features**

- ▼ Fully integrated basic rate U to S/T ISDN NT device

- ▼ Pin compatible with MTC-20277 INTT (4B3T)

- ▼ Full compliance with the applicable ETSI and ITU requirements

- **▼** Minimal external components

- ▼ < 355mW power consumption, 3.3V operating voltage

- ▼ Fully integrated Embedded Operations Channel handling

- ▼ Advanced 0.5µ CMOS mixed analog/digital process technology

- ▼ -40°C to +85°C or 0 to 70°C operating ranges

- ▼ 44 pin PQFP

### **Applications**

- ▼ Standard ISDN NT1 applications (stand-alone mode)

- ▼ Advanced NT with analog line interfaces ("NT1+")

- **▼** Micro-PABX

- **▼** Data network gateways

- ▼ Pair gain systems

- **▼** Data terminals

- **▼** CTI

#### **General Description**

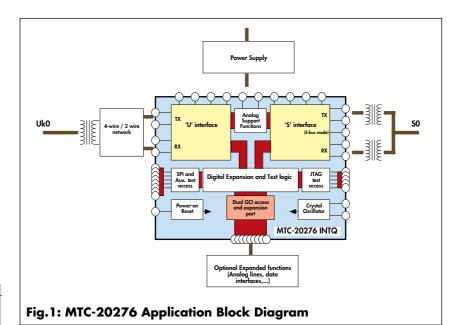

The MTC-20276 INTQ integrates all of the communications functions required in a Basic Rate ISDN Network Terminator on a single monolithic integrated circuit. It provides activation/ deactivation on chip and does not require an external microprocessor. The INTQ is designed for the 2B1Q line-code on the U-interface and is pin compatible with the MTC-20277 INTT, which performs identical functions but with the 4B3T U-interface line code. The MTC-20276 includes a GCI expansion port, to allow extended functions to be added (e.g. interfaces to existing analog terminal equipment by means of the MTK-40131 Short-Haul POTS chipset).

#### **Ordering Information**

| Part number   | Package     | Code | Temp.      |

|---------------|-------------|------|------------|

| MTC-20276PC-I | 44 pin PLCC | PC44 | -40 /+85°C |

| MTC-20276PC-C | 44 pin PLCC | PC44 | 0 /+70°C   |

# NT and Extended NT Functions ("NTplus")

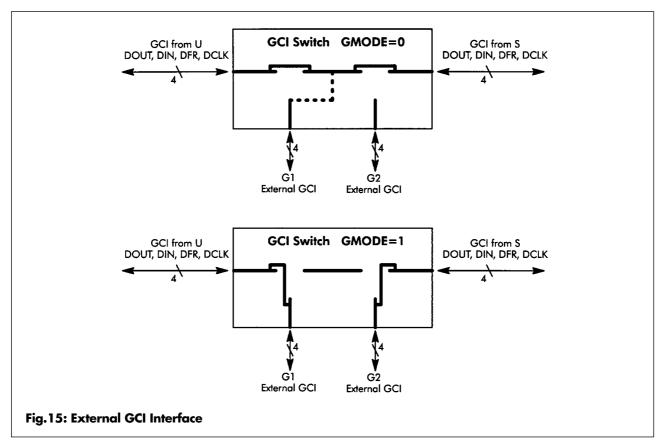

The MTC-20276 has a number of test access ports to facilitate system or production testing. One of these ports is configured as a dual GCI interface, which operates in one of two modes. In Mode 0 (GMode = logic 0), the GCI port allows the data flow between the 'U' and the 'S' ports to be optionally monitored.

This is the "stand alone" mode, which is the normal mode for simple NT1 applications. No additional microprocessor or other control device is required in this mode.

Mode 1 (GMode = logic1) allows separate access to the 'U' and the 'S' ports, for use by an external GCI compatible controller device. In this mode, the chip supports additional features required by extended NT modules ("NT1+") such as interfaces to existing analog equipment, or advanced data communication gateways.

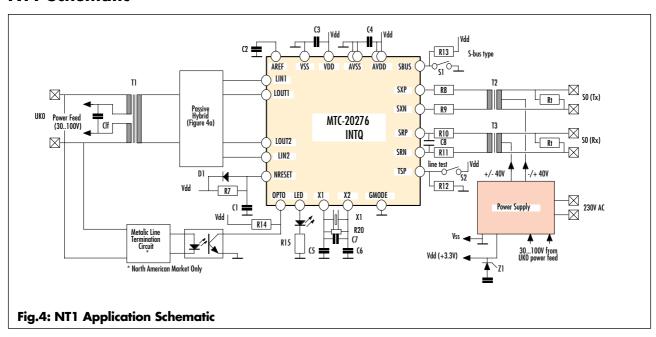

The application section describes the circuit configuration of the MTC-20276 in its stand alone mode, for conventional NT1 applications. (Figure 4)

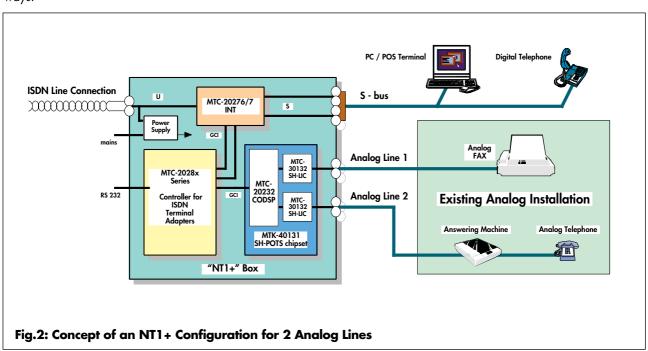

Figure 2 below shows the system concept of an MTC-20276/77 in an "NT1+" application, in combination with the MTK-40131 "SH-POTS" chipset for short-haul analog telephone lines.

MTC-2028xx is one of a family of interface and controller devices which cover a wide range of applications, e.g. MTC-20280 for ISDN NT+ or small PABX applications

#### **Standards Compliance**

MTC-20276 complies with relevant ANSI and ETSI specifications.

ETSI ETS 300 297 ETSI ETS 300 012 ETSI ETR 80 ANSI T1.601 ITU I.430 ITU G.961

\* GCI (General Circuit Interface), is an interface specification developed jointly by Alcatel, Italtel, GPT and Siemens, and can be obtained from Alcatel Microelectronics.

| Key Features                                                                 | 1        |

|------------------------------------------------------------------------------|----------|

| Applications                                                                 | 1        |

| • •                                                                          |          |

| General Description                                                          | 1        |

| NT and Extended NT Functions ("NTplus") Standards Compliance                 |          |

|                                                                              |          |

| Electrical Characteristics                                                   |          |

| Absolute Maximum Ratings Operating Conditions DC Characteristics             | 7        |

| AC Characteristics  Quality / Reliability                                    | 8        |

| Package / Pinout Pin Description LED Indicator                               | 10       |

| Application Information NT1 Schematic Recommended Component Values           | 12<br>12 |

| Application Information                                                      |          |

|                                                                              |          |

| Transformer Specifications S-Interface                                       | 14       |

| U-Interface Master Clock and XTAL Connections Typical Crystal Specifications | 14       |

| Overvoltage Protection Unused Pins                                           | 15       |

|                                                                              |          |

| Detailed Functional Description                                              |          |

| U-Interface Block                                                            | 18       |

| Physical Characteristics                                                     | 18       |

| Logical Characteristics of the U-interface                                   |          |

| Frame Structure                                                              |          |

| Encoding                                                                     |          |

| Scrambling                                                                   |          |

| Descrambling.                                                                |          |

| Activation and Deactivation Reset                                            |          |

| NGJCI                                                                        |          |

**Table of Content**

| GCI Interrace, Common Functions                                                    |    |

|------------------------------------------------------------------------------------|----|

| Data Format and Timing of the GCI Interface                                        | 25 |

| Continuous Modes                                                                   |    |

| The GCI Interface                                                                  |    |

| The Physical Organization of the GCI Bus                                           |    |

| General Content of the GCI Bus                                                     |    |

| Power-down on GCI                                                                  |    |

| Frame Format                                                                       |    |

| External Interfaces                                                                |    |

| G1 External GCI Interfaces                                                         |    |

| G2 External GCI Interfaces                                                         |    |

| U-Interface Command List                                                           |    |

| Command and Indicate (C/I) Channel (A bits)                                        |    |

| Power Down of the Interfaces                                                       |    |

| Transition from Synchronous to Power-Down State                                    |    |

| Wake-up Originated by Slave                                                        |    |

| Wake-up Originated by the Master                                                   |    |

| S-interface Commands and Indications Summary                                       |    |

| Commands in NT Mode                                                                |    |

| Indications in NT Mode                                                             |    |

| The S-interface Functional Overview                                                |    |

| General Description of the S-bus Interface                                         |    |

| S-interface - General Overview                                                     |    |

| Test Modes Summary                                                                 |    |

| GCI Clock Synchronization in the ISDN Environment for the Upstream S-interface (N7 | ·) |

| Clock Speed                                                                        |    |

| Power Saving / Deactivation of the S-interface                                     |    |

| Activation of the S-interface in NT Mode                                           |    |

|                                                                                    |    |

| Detailed Operational Description of the S-bus Interface                            | 38 |

| Introduction                                                                       | 38 |

| General Characteristics                                                            |    |

| Transmission Rate                                                                  |    |

| Frame Structure                                                                    |    |

| AMI S-bus Coding                                                                   |    |

| Balance Bits                                                                       |    |

| AMI Violations for Frame Synchronization                                           |    |

| Frame Synchronization - Distance Rule                                              |    |

| Frame Synchronization - Multiframing Exceptions                                    |    |

| Synchronization Principles - Adaptive Bit Timing                                   |    |

| Synchronization Principles - Fixed Bus Timing                                      | 39 |

| Pulse Polarity in the S-bus Frame                                                  |    |

| Transmitted Frames                                                                 |    |

| Details on Downlink Frames                                                         |    |

| Details on Uplink Frames                                                           |    |

| S-bus Transmitter Timing and Framing                                               |    |

| Transmitter Timing and Framing at the NT                                           |    |

| S-bus Receiver Timing and Synchronization                                          |    |

| Frame Synchronization Details in Adaptive Timing                                   |    |

| First Violation Detection                                                          |    |

| Violation Validation                                                               | 40 |

| RX Bit Synchronization N1 Adaptive bus                    |            |

|-----------------------------------------------------------|------------|

| Immediate Bit Synchronization at Instant t2               |            |

| Continuous Bit Synchronization at Each F/L Crossing       |            |

| Timing Relation Between RX and TX on the S-bus in NT Mode |            |

| Frame Relation Between GCI and S-Interface                |            |

| E-channel Generation                                      | 41         |

| Multiframing - S and Q Channels                           | 41         |

|                                                           |            |

| S-Interface Programming                                   |            |

|                                                           |            |

| M-Channel Messages and Registers                          |            |

| Introduction                                              |            |

| M-Channel Receiver and Transmitter                        | 42         |

| General Content of M-Channel Messages                     |            |

| S and Q Channel Messages                                  | 42         |

| Internal Register M-Channel Messages                      | 42         |

| M-Channel Operations                                      | 42         |

| M-Channel Format - Bit and Byte Numbering Convention      | 42         |

| Byte Transfer Procedure                                   |            |

| Idle M-Channel                                            | 42         |

| Start of Message (SOM) and First Byte Transfer            | 42         |

| Acknowledge of the SOM and First Byte                     |            |

| Further Byte transfers                                    |            |

| Further Byte Acknowledgement                              |            |

| End of Message (EOM)                                      |            |

| Acknowledge of EOM                                        |            |

| Sender Not Ready                                          |            |

| Receiver Not Ready                                        |            |

| IDLE forced From Sender                                   |            |

| Abort request From Receiver                               |            |

| Acknowledge Abort                                         |            |

| Reset of the M-channel Transceiver                        |            |

| Write Operation                                           |            |

| Read Operation and Content                                |            |

| Detailed Bitmap of the Internal Register                  |            |

| Identification Register Read Only Address Oh              |            |

| Version Number Register Read and Write Address 1h         |            |

| Configuration Register Read and Write Address 2h          |            |

| Output Register Read and Write Address 3h                 |            |

| IN1 and IN2 Registers Read Only Addresses 4h and 5h       |            |

| Performance Register Read Only Address 6h                 |            |

| M-Channel Operation Messages Overview                     |            |

| We Chaille Operation Wessages Overview                    | 40         |

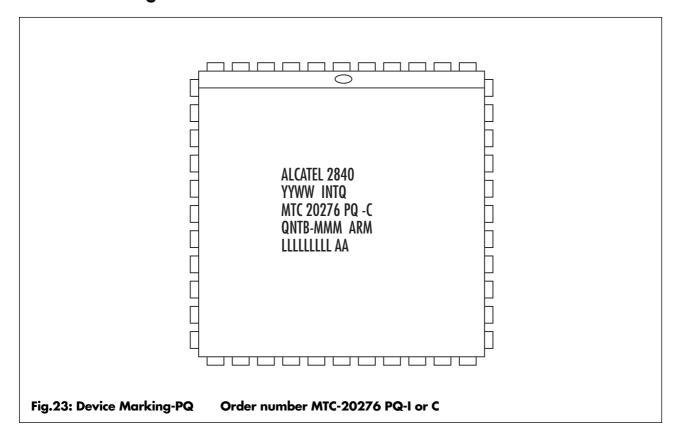

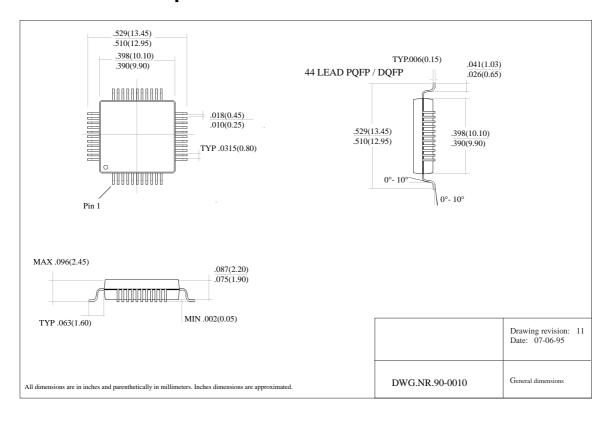

| Package Specification                                     | 47         |

| Device Branding                                           | 47         |

| 44PQFP Mechanical Specification                           |            |

| 44i XII Mechanical Specification                          | 40         |

| Application Note:                                         | <i>1</i> 9 |

| MTC 20276 INTO Compliance Issues                          | /0         |

#### **Lists of Tables**

| Absolute Maximum Ratings                            | 7  |

|-----------------------------------------------------|----|

| Operating Conditions                                |    |

| DC Characteristics                                  | 8  |

| AC Characteristics                                  | 8  |

| Pin Description                                     | 10 |

| LED Indicator                                       | 11 |

| Recommended Component Values                        | 13 |

| Transformer Specifications                          | 14 |

| Typical Crystal Specifications                      | 14 |

| Unused Pins                                         |    |

| Maintenance and Service Channel                     | 22 |

| Service and Maintenance Data Convention             | 22 |

| Service and Maintenance Data Convention             | 23 |

| Encoding                                            | 23 |

| Command and Indicate (C/I) Channel (A bits)         | 28 |

| S-interface Commands and Indications Summary        | 32 |

| Commands in NT Mode                                 | 32 |

| Indications in NT Mode                              | 33 |

| Transmitted Frames                                  |    |

| Write Operation                                     | 44 |

| Read Operation and Content                          | 44 |

| Detailed Bitmap of the Internal Registers           |    |

| Identification Register Read Only Address Oh        | 45 |

| Version Number Register Read and Write Address 1h   |    |

| Configuration Register Read and Write Address 2h    | 45 |

| Output Register Read and Write Address 3h           |    |

| IN1 and IN2 Registers Read Only Addresses 4h and 5h | 46 |

| Performance Register Read Only Address 6h           |    |

| M-Channel Operation Messages Overview               | 46 |

# **Electrical Characteristics**

### **Absolute Maximum Ratings**

Operation of the device beyond these conditions is not guaranteed. Sustained exposure to these limits will adversely effect device reliability.

Table 1

| Parameter                                                                               | Max                               | Units                                      |  |

|-----------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------|--|

| DVDD, AVDD<br>Vin, Voltage on any device pin                                            | 4.8<br>VSS-0.3<br>VDD+0.3 or 3.63 | V (see note)<br>V<br>V, whichever is lower |  |

| Storage temperature<br>Temperature under bias<br>Lead Temperature<br>(soldering 10 sec) | -65 to +150<br>-55 to +125<br>300 | °C<br>°C<br>°C                             |  |

**Note:** Exposure to voltages at or above this level for more than 10 hours accummulated over the device's operating life will adversely effect reliability.

Note 2. All logic pins except NRESET,

which is a Schmitt-trigger input with hysteresis.

# **Operating Conditions**

Unless otherwise stated, the following electrical characteristics are valid over the ranges specified here. (Vss = OV).

Table 2

| Min                      | Max                      | Units                                                          | Note                                                                    |

|--------------------------|--------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------|

| 3.15                     | 3.45                     | V                                                              | =3.3V ±5%                                                               |

|                          | 10                       | mVpp                                                           |                                                                         |

|                          | 100                      | mVpp                                                           |                                                                         |

|                          | 0.1                      | mVpp                                                           | Note 2                                                                  |

| - 0.25                   | + 0.25                   | mA                                                             | load on AREF Pin                                                        |

| Crystal frequency 15.359 |                          |                                                                | ±50ppm, Note 1                                                          |

| Temperature range -40    |                          |                                                                |                                                                         |

|                          | 3.15<br>- 0.25<br>15.359 | 3.15 3.45<br>10<br>100<br>0.1<br>-0.25 + 0.25<br>15.359 15.361 | 3.15 3.45 V 10 mVpp 100 mVpp 0.1 mVpp -0.25 + 0.25 mA 15.359 15.361 MHz |

**Note 1:** An external clock may be applied to XTAL2, pin 24. Temperature dependent drift <10ppm.

**Note 2:** AREF is an output, designed to allow a decoupling capacitor to be placed on the internal analog reference voltage. The external circuit layout must avoid the induction of noise on this pin.

#### **DC Characteristics**

#### Table 3

| MTB-20276 State                                                                                                                                                                                                                       | Тур                            | Max              | Unit                 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|----------------------|--|

| Full activated - ETSQI loop 1 on U loop, random data Full activated - ETSQI loop 2 (40dB) on U loop, random data U loop only activated - ETSI loop 1, random data U loop only activated - ETSI loop 2 (40dB), random data Deactivated | 362<br>325<br>340<br>301<br>20 | 390<br>355<br>22 | mW<br>mW<br>mW<br>mW |  |

#### Table 4

| Parameter          | Conditions                | Min  | Max         | Units | Note |

|--------------------|---------------------------|------|-------------|-------|------|

| VIH                | Input level, logic 1      | 0.8  |             | DVDD  | 1    |

| VIL                | Input level, logic 0      |      | 0.2         | DVDD  | 1    |

| VOH                | Output level, logic 1     | 0.85 |             | DVDD  | 1    |

| VOL                | Output level, logic 0     |      | 0.4         | V     | 1    |

| $V_{IH}$           | Rising, NRESET            | 1.7  | 1.9         | V     | 1    |

| $V_{IL}$           | Falling, NRESET           | 0.9  | 1.1         | V     | 1    |

| $V_{AREF}$         | Reference voltage output, |      |             |       |      |

| / WEI              | load current < ±250µA.    | 1.6  | 1.7         | V     |      |

| V <sub>TNRES</sub> | Nreset input threshold    | 1.6  | 1. <i>7</i> | ٧     |      |

**Note 1:** All logic pins except NRESET, which is a Schmitt-trigger input with hysteresis.

### **AC Characteristics**

#### Table 5

| Parameter                           | Conditions                                                                           | Min | Max      | Units          | Note |

|-------------------------------------|--------------------------------------------------------------------------------------|-----|----------|----------------|------|

| Cin<br>Cload<br>V <sub>TPWRES</sub> | Input capacitance any pin<br>Load capacitance on any output pin<br>Reset pulse width | 10  | 1<br>100 | pF<br>pF<br>mS |      |

# **Quality / Reliability**

Early failure rate  $\leq 0.3\%$  at 3000 hours

Long term failure rate  $\leq$  300 FIT for 45°C average ambient and 45% average humidity

Lifetime  $\geq 15$  years

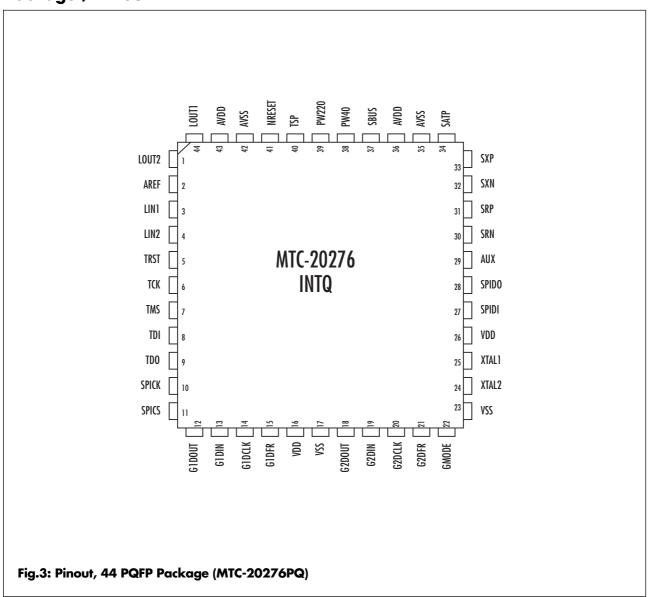

# Package / Pinout

# **Pin Description**

The table gives a summary of all MTC-20276 pins and their functions.

Table 6

| Nr. | Function | Name   | Dir. | Description                                                                                    |

|-----|----------|--------|------|------------------------------------------------------------------------------------------------|

| 44  |          | LOUT1  | 0    | U-interface analog outputs. The connections LOUT1 and LOUT2 interface                          |

| 1   |          | LOUT2  | 0    | the U driver outputs, via termination resistors and the line coupling                          |

|     | U        |        |      | transformer, to the U0 reference point.                                                        |

| 3   |          | LIN1   | I    | U-interface analog inputs to the INTQ from the analog 'hybrid'                                 |

| 4   |          | LIN2   | I    |                                                                                                |

| 2   |          | AREF   | 0    | Analog ground, $+1.65 \text{ V} \pm 3\%$ . Used as reference voltage for A/D and D/A.          |

| 43  |          | AVDD   | P    | +3.3V ±5% power supply for analog U-interface functions                                        |

| 42  |          | AVSS   | Р    | OV ground for analog U-interface functions                                                     |

| 33  |          | SXP    | 0    | S-interface analog outputs. SXP and SXN interface the S-driver outputs                         |

| 32  |          | SXN    | 0    | via terminating resistors and the Tx line coupling transformer to the SO reference point (Tx). |

| 31  | S        | SRP    | ı    | S-interface analog inputs. SRP and SRN interface the S-inputs via the Rx line                  |

| 30  |          | SRN    | I    | coupling transformer to the SO reference point (Rx).                                           |

| 37  |          | SBUS   | I    | S-bus type configuration. 1 = short bus with fixed timing, 0 = adaptive                        |

|     |          |        |      | timing for extended bus or point-to-point                                                      |

| 34  |          | SATP   | 0    | Analog test pin. Used for test purposes only, should be left open circuit                      |

| 36  |          | AVDD   | P    | +3.3 ±5% power supply for analog S-interface functions                                         |

| 35  |          | AVSS   | Р    | OV ground for analog S-interface functions                                                     |

| 12  |          | G1DOUT | 0    | Primary GCI interface G1:                                                                      |

| 13  |          | G1DIN  | 1/0  | GMODE = 0: Monitoring of the internal GCI between the U and S.                                 |

| 14  | GCI      | G1DCLK | 0    | GMODE = 1: NTplus mode; complete GCI connected to U with U as master.                          |

| 15  |          | G1DFR  | 0    | G1DOUT = data output                                                                           |

|     |          |        |      | G1DIN = data input (output direction in monitoring mode)                                       |

|     |          |        |      | G1DCLK = 512 KHz GCI clock                                                                     |

|     |          |        |      | G1DFR = 8KHz GCI frame clock which identifies the beginning of                                 |

|     |          |        |      | the frame of G1DIN and G1DOUT                                                                  |

| 18  |          | G2DOUT | 0    | Secondary GCI interface G2:                                                                    |

| 19  |          | G2DIN  | I    | GMODE = 0: No function                                                                         |

| 20  |          | G2DCLK | I    | GMODE = 1: NTplus mode; complete GCI connected to S with external master.                      |

| 21  |          | G2DFR  | I    | G2DOUT = data output                                                                           |

|     |          |        |      | G2DIN = data input                                                                             |

|     |          |        |      | G2DCLK = 512KHz GCI clock                                                                      |

|     |          |        |      | G2DFR = 8KHz GCI frame clock which identifies the beginning of                                 |

|     |          |        |      | the frame of G2DIN and G2DOUT                                                                  |

|     |          |        |      | Remark: if NT Plus mode is not used, the inputs should be strapped                             |

|     |          |        | _    | high or low.                                                                                   |

| 22  |          | GMODE  | I    | Select NTplus mode. 0 = monitoring mode, 1 = NTplus mode.                                      |

| 5   |          | TRST   | I    | TAP (Test Access Port) controller reset, active low                                            |

| 6   | JTAG     | TCK    | I    | TAP controller clock, maximum 10 MHz                                                           |

| 7   |          | TMS    | l    | TAP controller mode selection                                                                  |

| 8   |          | TDI    |      | TAP controller input                                                                           |

| 9   |          | TDO    | 0    | TAP controller output                                                                          |

| 41 | RESET   | NRESET |   | Hardware reset, active low. Schmitt-trigger input for connection to         |

|----|---------|--------|---|-----------------------------------------------------------------------------|

|    |         |        |   | external RC or logic device.                                                |

| 25 | OSC.    | XTAL1  | I | Connection to external crystal (15.36MHz ± 100ppm). May also be used        |

|    |         |        |   | as input for external master clock source.                                  |

| 24 |         | XTAL2  | I | Connection to external crystal.                                             |

| 40 | Monitor | TSP    | I | Transmit Single Pulses. INTQ transmits single pulses of alternating maximum |

|    |         |        |   | positive and negative polarity at the S and U-interface.                    |

|    |         |        |   | Pulse repetition rate is 0.67 kHz at the U-interface, for test purposes and |

|    |         |        |   | as a search tone on the line.                                               |

| 39 |         | PW220  | I | Indicate if the local mains power supply is available.*                     |

|    |         |        |   | 1 = mains power supply ON                                                   |

|    |         |        |   | 0 = mains power supply OFF                                                  |

| 38 |         | PW40   |   | Indicate if the local 40V power supply is available.*                       |

|    |         |        |   | 1 = 40V power supply ON                                                     |

|    |         |        |   | 0 = 40V power supply OFF                                                    |

| 10 |         | TESTO  | 0 | Factory use only. Leave open circuit.                                       |

| 11 |         | TEST 1 | 0 |                                                                             |

| 27 |         | OPTO   | Ī | Opto isolator input. See below.                                             |

| 28 |         | LED    | 0 | State indicator LED. See below.                                             |

| 29 |         | CSO    | Ī | Indicate cold-start-only operation mode:                                    |

|    |         |        |   | 0 = normal mode                                                             |

|    |         |        |   | 1 = cold-start-only operation mode**                                        |

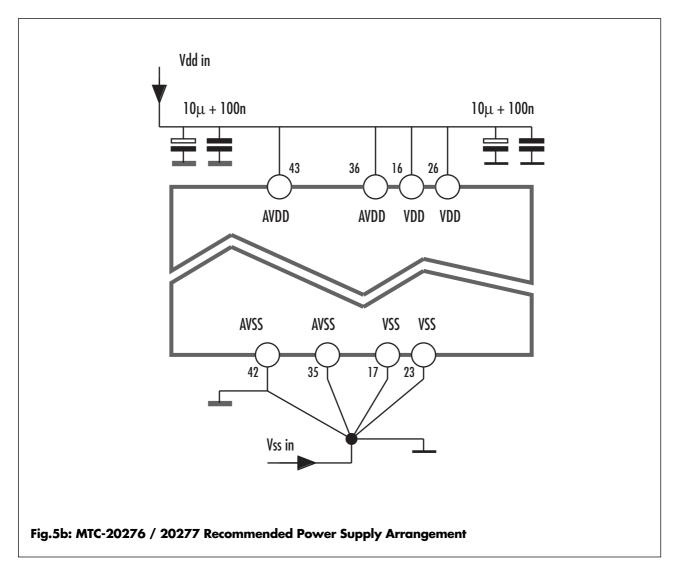

| 16 |         | VDD    | P | +3.3 V ±5% power supply for digital functions                               |

| 26 |         | VDD    | P | 10.0 1 20/0 portor supply for digital fortations                            |

| 17 |         | VSS    | P | OV ground for digital functions                                             |

| 23 |         | VSS    | P | or ground for digital fortelions                                            |

| 23 |         | ¥33    | ' |                                                                             |

**Note:** None of the Input pins are 5V tolerant.

- \* This only affects the "PS1" and "PS2" bits in the upstream M symbol, and does not have any functional implication.

- \*\* This only affects the "CSO" bit in the upstream M symbol, and does not influence the activation performance of the INTQ.

Device pin 27 (OPTO) is used to determine whether an automatic upstream activation request is performed after power-up or reset, or not. (New releases of the relevant ETSI specifications require automatic activation on power-up, whereas previous releases did not)

Pin 27 should be strapped as follows:

Function: Pin 27 strapped to:

Automatic activation request VDD

No automatic activation request VSS

#### **LED Indicator**

The LED output can source up to 4mA to directly drive an LED, via a current limiting resistor.

#### Table 7

| LED OFF             | Both U and S-interfaces are inactive                                              |

|---------------------|-----------------------------------------------------------------------------------|

| Fast flashing (8Hz) | The U-interface is attempting to synchronize, or the EOC has activated a          |

|                     | 2B+D loopback.                                                                    |

| Slow flashing (1Hz) | The U-interface is synchronized and the S-interface is attempting to synchronize. |

| LED ON              | Both U and S-interfaces are fully synchronized and 'connect through'              |

|                     | status is achieved.                                                               |

|                     |                                                                                   |

### **Application Information**

The MTC-20276 requires very few external components, all of which are low-cost and readily available types. In addition, the use of a 44PQFP

package style allows further savings in the total cost and physical size of the ISDN NT module. The following recommended applications information is constantly being reviewed to improve cost and performance. Please contact Alcatel Microelectronics' application support group for the latest details.

#### **NT1 Schematic**

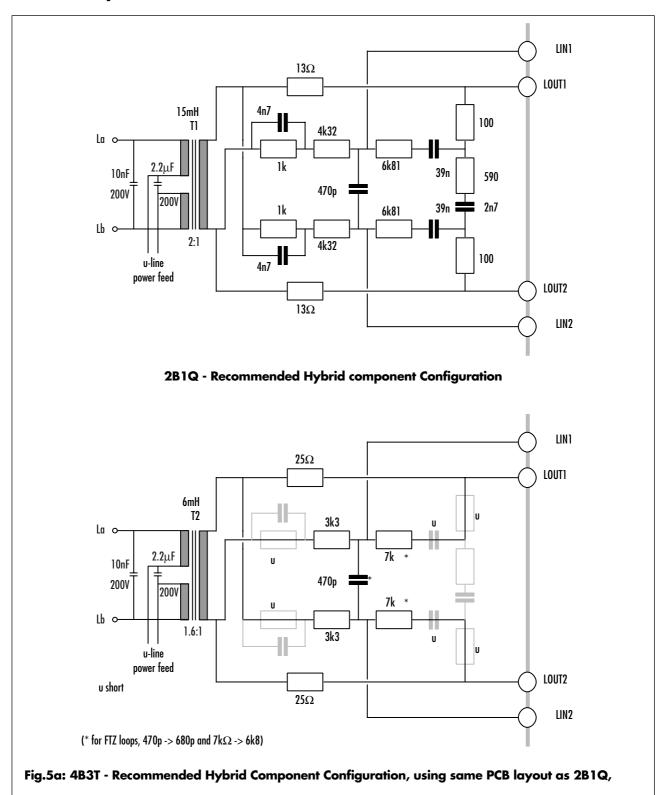

# **Recommended Component Values**

Table 8

| Component      | Function                   | Value                | Comment                 |

|----------------|----------------------------|----------------------|-------------------------|

| U Interface    |                            |                      |                         |

| T1             | U transformer              | 2:1, 15 mH           | see text                |

| Rh14, Rh24     | U feed bridge              | 13Ω                  | ±1%                     |

| Rh17           | Hybrid                     | 590Ω (470Ω+120Ω)     | ±1%                     |

| Rh11, Rh21     | Hybrid                     | 1k ' '               | ±1%                     |

| Rh12, Rh22     | Hybrid                     | 4.32kΩ               | ±1%                     |

| Rh13, Rh23     | Hybrid                     | 6.81kΩ               | ±1%                     |

| Rh16, Rh26     | Hybrid                     | 100Ω                 | ±1%                     |

| Ch1, Ch2       | Hybrid                     | 4.7nF                | ±5%                     |

| Ch3            | Hybrid                     | 470pF                | ±5%                     |

| Ch4, Ch5       | Hybrid                     | 39nF                 | ±5%                     |

| Chó Chó        | Hybrid                     | 2.7nF                | ±5%                     |

| Ch7            | <b>'</b>                   | 100nF                | 200V                    |

| Clf            | Line-feed coupling         | 2.2µF                | 200V                    |

|                |                            | '                    |                         |

| S/T Interface  |                            |                      |                         |

| T2,T3          | S transformer              | 2:1                  | see text                |

| R8,R9          | S-bus transmit impedance   | 33Ω                  | ±1%                     |

| R10,R11        | S-bus receive impedance    | 5kΩ                  | ±10%                    |

| Rt             | S-bus termination resistor | 100Ω                 |                         |

| C8             | S-bus receive capacitor    | 27pF                 | 10%                     |

|                |                            |                      |                         |

| Crystal        |                            |                      |                         |

| X1             | crystal                    | 15.36 MHz            | see text                |

| C5,C6          | crystal load               | 22pF                 | see text                |

| C7             | crystal load               | 0 to 22pF (optional) | see text                |

| R20            | crystal stabilizer         | 1ΜΩ                  |                         |

| Miscellaneous  |                            |                      |                         |

| R7,R12,R13,R14 | Pull-up/down               | 100kΩ                |                         |

| R15            | LED current limit          | 510Ω                 |                         |

| C1,C2          | reset delay                | 100nF                | -                       |

| C1,C2<br>C3,C4 | supply decoupling          | 100nF                |                         |

| D1             | loss-of-power reset        | 1N4148               | any small signal diode  |

| Z1             | Power Supply Clamp         | 4.1V zener           | uny sinaii signal aloae |

| S1             | switch                     | 4.1 ¥ 261161         | S-bus mode              |

| S2             | switch                     | _                    | Test signal             |

| J2             | SWIICH                     | _                    | Tesi signai             |

# **Application Information**

# **Transformer Specifications**

Table 9

| S-Interface              |      |      |                               |  |  |

|--------------------------|------|------|-------------------------------|--|--|

| Parameter                | Min  | Max  | Units                         |  |  |

| Turns Ratio              | 2:1  |      | Line: Chip                    |  |  |

| Primary Inductance       | 20   |      | mH                            |  |  |

| Leakage Inductance       |      | 13   | μH                            |  |  |

| Interwinding Capacitance |      | 50   | pF nominal                    |  |  |

| PRI DCR                  | 0.9  | 1.3  | $\Omega$ (1.1 $\Omega$ ± 20%) |  |  |

| SEC DCR                  | 2.1  | 3.1  | $\Omega$ (2.6 $\Omega$ ± 20%) |  |  |

| U-Interface              |      |      | •                             |  |  |

| Parameter                | Min  | Max  | Units                         |  |  |

| Turns Ratio              | 2:1  |      | Line: Chip                    |  |  |

| Primary Inductance       | 13.5 | 16.5 | mH                            |  |  |

| Leakage Inductance       |      | 60   | μH                            |  |  |

| Interwinding Capacitance |      | 90   | pF                            |  |  |

| PRI DCR                  | 6    | 7    | Ω                             |  |  |

| SEC DCR                  | 2.8  | 3.3  | Ω                             |  |  |

#### **Master Clock and XTAL Connections**

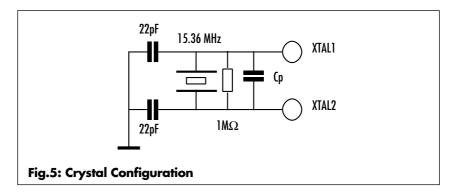

At the pins XTAL1 and XTAL2 a crystal must be connected to form a parallel mode oscillator. Two capacitors of 22 pF should be connected to ground.

Some crystals may require the parallel capacitor Cp to be used (10 pf Typ).

# **Typical Crystal Specifications**

Table 10

| AT cut, fundamental mode<br>Parallel resonance frequency<br>Total tolerance                                           | 15.360<br>± 50              | MHz<br>ppm               |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|

| Dynamic capacitance<br>Load capacitance<br>Parallel capacitance<br>Series resistance<br>Series resistance drift (age) | 15<br>30<br>7<br>40<br>± 10 | fF<br>pF<br>pF<br>Ω<br>% |

| Drive level                                                                                                           | 0.25                        | mW                       |

#### **Overvoltage Protection**

This is strongly dependant on the Printed Circuit Board layout and local specification variations. Generally, it is recommended to use standard small-signal diodes to clamp voltages from the S-interface (e.g. 1N4148) and U-interface (e.g. 1N4004) to Vdd and

ground. The recommended protection for the U-interface is to diode clamp the chip side transformer pins to the supply rails, and for the S-interface clamp the INTQ device pins (30, 31, 32, 33). In order to prevent excessive disturbance voltages from causing the

power-supply voltage to increase (full-wave rectifier effect through the protection diodes), it is recommended that a zener-diode is used to clamp the Vdd voltage < 4,8V.

#### **Unused Pins**

The INTQ has a number of device pins which are used only in specific applications, or for device testing. These pins should be connected as shown below to

ensure proper operation in a given application. 'O' means connect to ground, '1' means connect to Vdd, 'open' means make no connection.

A dash ('-') means that the pin is used in the application. All other pins have defined states as shown in the application schematic.

Table 11

| Pin    | Number | NT mode          | NT+ mode        |

|--------|--------|------------------|-----------------|

| GMODE  | 22     | 0                | 1               |

| G2DOUT | 18     | open             | -               |

| G2DIN  | 19     | 1                | -               |

| G2DCLK | 20     | 0                | -               |

| G2DFR  | 21     | 0                | -               |

| GIDOUT | 12     | open/monitor     | -               |

| G1DIN  | 13     | open/monitor     | -               |

| G1DCLK | 14     | open/monitor     | -               |

| G1DFR  | 15     | open/monitor     | -               |

| TRST   | 5      | 0 (pull down)    | 0 (pull down)   |

| TCK    | 6      | 1 (pull up)      | 1 (pull up)     |

| TMS    | 7      | 1 (pull up)      | 1 (pull up)     |

| TDI    | 8      | 1 (pull up)      | 1 (pull up)     |

| TDO    | 9      | open             | open            |

| CSO    | 29     | O (normal)       | O (normal)      |

|        |        | 1 (CSO)          | 1 (CSO)         |

| PW40   | 38     | - , ,            | - '             |

| PW220  | 39     | -                | -               |

| TESTO  | 10     | open             | open            |

| TEST1  | 11     | open .           | open            |

| OPTO   | 27     | <u>-</u> '       | _ '             |

| LED    | 28     | -                | -               |

| SATP   | 34     | open             | open            |

| TSP    | 40     | O (normal)       | O (normal)      |

|        |        | 1 ( test pulses) | 1 (test pulses) |

| PW40   | 38     |                  |                 |

|        |        | -                |                 |

| S BUS  | 37     | O (P-P S Bus)    | O (P-P S Bus)   |

|        |        | 1 (Short S Bus)  | 1 (Short S Bus) |

|        |        | (2 2.234)        | (               |

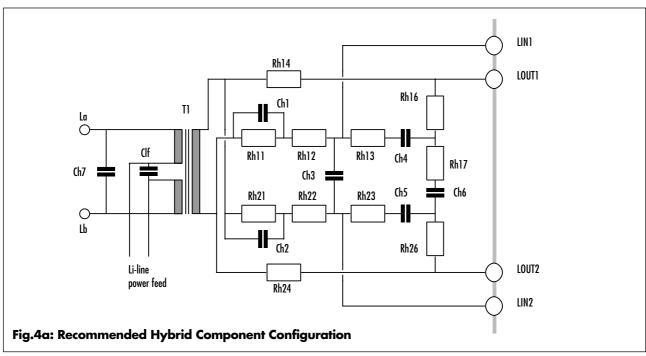

# Common Hybrid Schematics for 4B3T and 2B1Q

**Note:** It is recommended to put the decoupling capacitors close to the chip.

# **Detailed Functional Description**

#### **U-Interface Block**

### **Physical Characteristics**

The quaternary symbol stream on the U-interface has to the following physical characteristics:

#### Symbol rate

The symbol rate is 80 kbaud ± 1 ppm and applies to synchronous symbol transmission.

#### **Input Jitter**

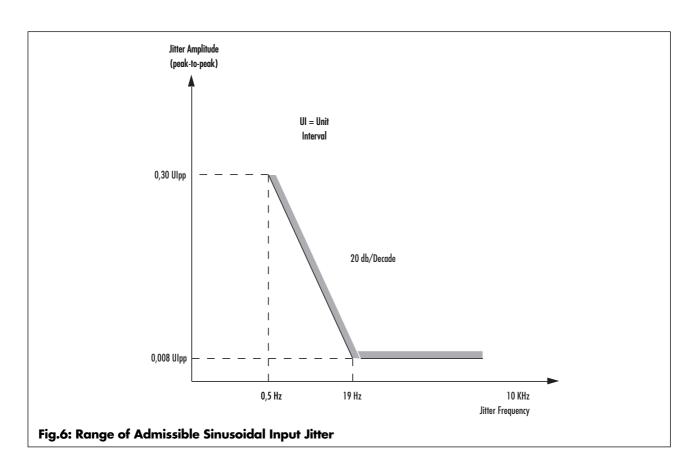

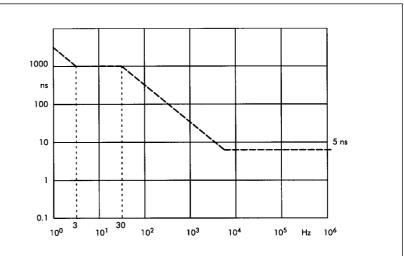

The INTQ tolerates a sinusoidal input jitter of the quaternary symbols as indicated in Figure 6.

#### **Jitter Transfer Function**

The jitter transfer function of the INTQ (looped between U-interfaces) doesn't exceed  $\pm$  1 dB in the frequency range 3 Hz to 30 Hz.

#### **Output Jitter**

The peak-to-peak jitter produced by the INTQ doesn't exceed 0.02 UI (≤ 166 ns), when measured via a high pass filter with a cut-off frequency of 30 Hz. Without this filter the same measurement doesn't read more than 0.1 UI.

#### **Transmit Signal Amplitude**

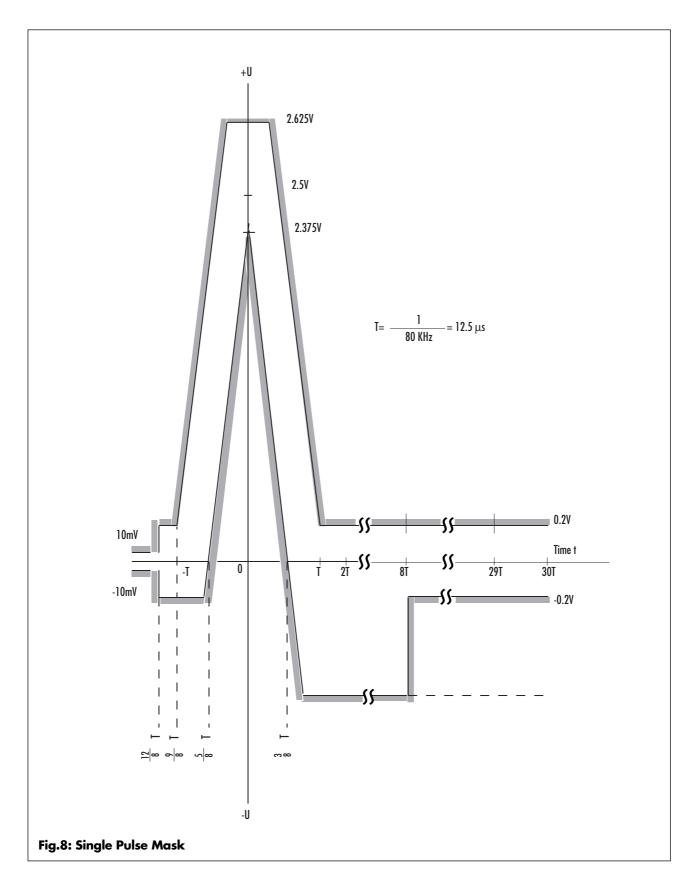

The absolute peak value VImax of a single pulse VI at the U0 interface terminated with a 135 Ohm resistance is  $2.5 \text{ V} \pm 5\%$ .

The absolute peak value of the coded quaternary signal measured at U0 interface terminated with 135 Ohm doesn't exceed 4 V.

#### **Stability**

The transmit signal amplitude measured over a period of one minute doesn't vary by more than 1% beginning 5 ms after the INTQ is switched into power-up state.

#### **Transmit Spectrum**

The spectrum of the quaternary transmit signal at U0 interface doesn't exceed the limits given in Figure 8.

#### **Pulse Shape**

A single pulse measured across a 135 Ohm resistance at U0 interface comply to the spectral requirements presented in Figure 8 and the pulse mask requirements given in Figure 9.

#### **Maximum Voltage**

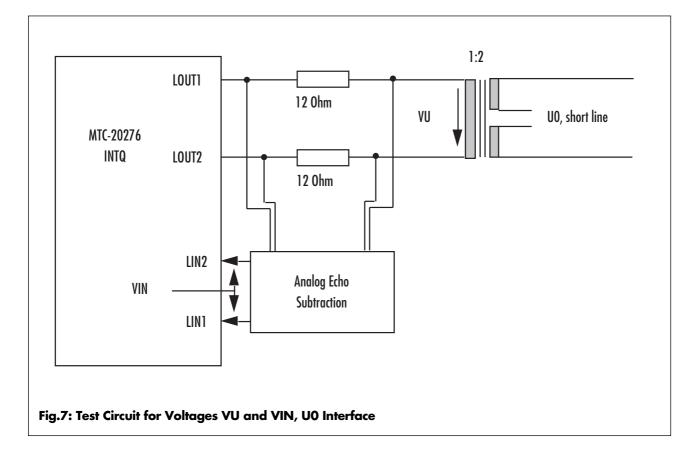

The maximum peak-to-peak value VUmax of the voltage VU as shown in figure 7 with full receive signal (short line), that can be accepted is 2 V. Due to the analog echo subtraction the maximum peak-to peak value Vinmax of the voltage Vin between LIN1 and LIN2 is 1.35 V.

#### **Input/Output Impedance**

The line terminating impedance is nominally 135 Ohm in power up and power down states. The return loss against  $135\Omega$  real exceeds 16 dB between 12 kHz and 50 kHz.

- slope below 12 kHz: 20 dB / decade

- slope above 50 kHz: -10 dB / decade

#### Load

The load is given by the line transformer and the subscriber line. The loops are standardised by the ANSI and ETSI documents.

- Turns ratio of line transformer: 2:1

- Transformer coil inductance (from line side): 15 mH ± 10%

### **Logical Characteristics of the U-Interface**

The quaternary symbol stream crossing the U-interface complies with the following logical characteristics:

#### Frame Structure

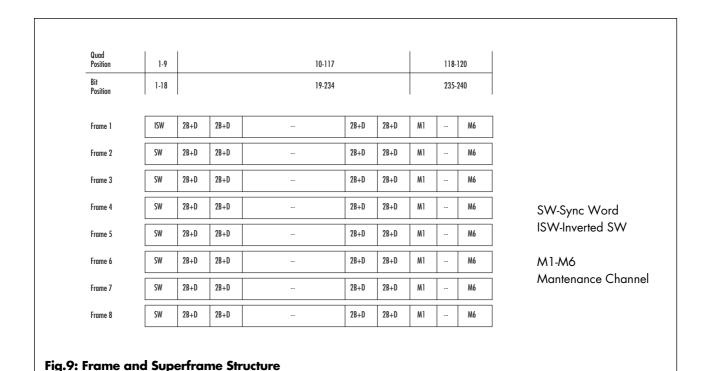

The information flow across the subscriber line uses frames as shown in Figure 10. The length of such a frame corresponds to 120 quaternary symbols being transmitted within 1.5 ms. The frame structure is detailed as follows:

#### B+B+D - Data

108 quaternary symbols represent 216 bits of scrambled and encoded B+B+D data. The 108 quaternary symbols are transmitted in succession. These blocks are assembled as follows:

Data of

B1 + B2 + D + B1 + B2 + D

Number of bits

8 8 2 8 8 2

#### **Synchronising Word**

9 quaternary symbols in each direction represent a non-scrambled synchronising word. They are used to generate frame clocks. If they are out of position for 60 ... 200 consecutive frames, the line resynchronization procedure is started. The quaternary values and the frame position are as follows:

1. From LT to NT or analog loop in LT (loop 1) or analog loop on NT, and from NT to LT.

| SW Polarity:  | +3 | +3 | -3 | -3 | -3 | +3 | -3 | +3 | +3 |

|---------------|----|----|----|----|----|----|----|----|----|

| ISW Polarity: | -3 | -3 | +3 | +3 | +3 | -3 | +3 | -3 | -3 |

#### **Maintenance and Service Channel**

3 quaternary symbols per frame are transmitted to convey maintenance and embedded operations channel information. This information is contained in a superframe consisting of 8 frames (duration: 12 ms). The start of a superframe in up and downstream directions is market by a single inversion of the synchronisation word (ISW). The quaternary symbol sequences represent data that can be transmitted at a rate of 4 kbits/s. They are transmitted immediately before the sync word (SW).

The M symbol is used for various purposes incluiding:

- 1. Maintenance Channel (control test loops and report frame errors)

- 2. Service channel (carry transparent user data in both directions) In detail the following convention applies (NT to LT):

Table 12

|         | M1     | M2     | МЗ     | M4  | M5     | M6     |

|---------|--------|--------|--------|-----|--------|--------|

| Frame1  | EOC a1 | EOC a2 | EOC a3 | ACT | 1      | 1      |

| Frame 2 | EOC dm | EOC i1 | EOC i2 | PS1 | 1      | FEBE   |

| Frame 3 | EOC i3 | EOC i4 | EOC i5 | PS2 | CRC 1  | CRC 2  |

| Frame 4 | EOC i6 | EOC i7 | EOC i8 | NTM | CRC 3  | CRC4   |

| Frame 5 | EOC a1 | EOC a2 | EOC a3 | CSO | CRC 5  | CRC6   |

| Frame 6 | EOC dm | EOC i1 | EOC i2 | 1   | CRC 7  | CRC8   |

| Frame 7 | EOC i3 | EOC i4 | EOC i5 | SAI | CRC9   | CRC10  |

| Frame 8 | EOC i6 | EOC i7 | EOC i8 | 1   | CRC 11 | CRC 12 |

#### **Service and Maintenance Data Convention**

Table 13: Messages required for command/response EOC mode

| Message                            | Message<br>code | Network | NTI | REG  |

|------------------------------------|-----------------|---------|-----|------|

| Operate 2B+D Loopback              | 0101 0000       | 0       | d   | t/d  |

| Operate B1-channel Loopback (note) | 0101 0001       | 0       | d   | t/d  |

| Operate B2-channel Loopback (note) | 0101 0010       | 0       | d   | t/d  |

| Request Corrupted CRC              | 0101 0011       | 0       | d   | t/d  |

| Notify of Corrupted CRC            | 0101 0100       | 0       | d   | t/d  |

| Return to Normal                   | 1111 1111       | 0       | d   | t/d  |

| Hold State                         | 0000 0000       | d/o     | o/d | o/d/ |

| Unable to Comply Acknowledgement   | 1010 1010       | d       | 0   | t/o  |

Table 14

| Symbol  | Description                                                   |

|---------|---------------------------------------------------------------|

| ACT     | Activation bit (set to ONE during activation)                 |

| CRC     | Cyclic Redundancy check: covers 2B+D & M4:                    |

|         | 1= most significant bit;                                      |

|         | 2= next most significant bit, etc.                            |

| CSO     | Cold-start-only bit (ONE indicates cold-start-only)           |

| EOC     | Embedded operations channel:                                  |

|         | a = address bit;                                              |

|         | dm = data/message indicator;                                  |

|         | i = information (data/message).                               |

| FEBE    | Far end block error bit (ZERO for errored multiframe).        |

| NTM     | NT in test mode bit (ZERO indicates test mode).               |

| PS1/PS2 | Power status bits (ZERO indicates power problems).            |

| SAI     | S-activation indicator bit (optional, set = 1 to activate S/T |

**Note:** Transmission errors in the data protected by the Cyclic Redundancy Check are detected during each superframe and reported back to the LT in the

next superframe.

This is for loop quality checking only and does not invoke retransmission of any sort.

#### **Encoding**

The encoding of a binary bit stream is such that 2 binary bits correspond to 1 quaternary symbol. The first symbol of a frame will always contain the information of the first 2 bits of a B1 channel (although these bits are of course scrambled).

In the receive direction, the first symbol of the quaternary frame is always converted (after descrambling) into the first two bits of a B1 channel.

The exact convertion is done according to the following rules (ANSI specification):

Table 15

| Quaternal Symbol | First bit (Sign) | Second Bit (Magnitude) |

|------------------|------------------|------------------------|

| +3               | 1                | 0                      |

| +1               | 1                | 1                      |

| -1               | 0                | 1                      |

| -3               | 0                | 0                      |

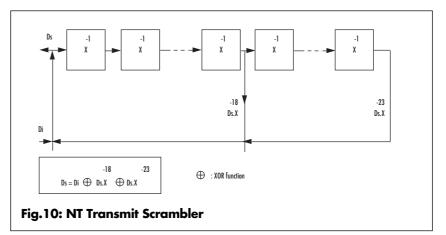

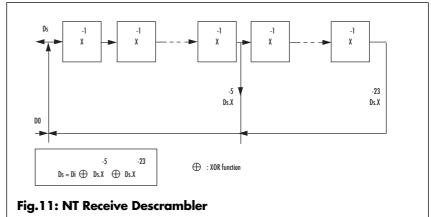

#### **Scrambling**

The received binary data stream is divided by generating polynomials.

The scrambler contains supervision circuitry which flags if a continuous series of ones or zeros have been detected at the output for a complete 1 ms frame.

#### **Descrambling**

The quaternary signals received on each side of the subscriber line are converted back into a binary bit stream and multiplied by the generating polynomials in order to recover the original data.

#### **Activation and Deactivation**

In order to reduce the power consumption of circuits connected to the subscriber line, INTQ can be switched to stand-by or powered down during idle periods. The components are powered up again during the line activation procedure. Two states are defined:

- Power-down state

Power consumption of the majority of the functions is reduced by stopping the clocks; maximum power reduction;

- Power-up state

All functions powered up; GCI interface

is activated; exchange of C/I messages

is possible.

The activation procedure consists of three phases:awake ( see the following sections), synchronise, and connect through.

Maximum activation time (from command ACT to indication CT) without repeater:

≤ 170 ms under normal conditions (starting with stored coefficients)

1 s after reset of the coefficients.

The deactivation procedure consists of two phases:line deactivation of the NT can be initiated only by INFO U0.

Deactivation time (from Command DEAC to Indication DC) is in the order of 4 ms.

#### Reset

The INTQ can be reset via an external pin (NRESET = LOW) or via the command RES in the C/I channel. Normally

the INTQ is reset via the pin NRESET (hardware reset).

Both reset requests cause a reset for various function blocks via the activation/deactivation control and the reset logic. The INTQ is initialised such that a "cold start" (resetting of the coefficients) is possible.

#### Analog Loop (Loop 2 in NT)

For maintenance purposes a loop can be closed by applying the correct command into the M channel or into the GCI C/I channel, described in the next section.

# GCI Interface, Common Functions Data Format and Timing of the GCI Interface (DIN, DOUT, DCLK, DFR)

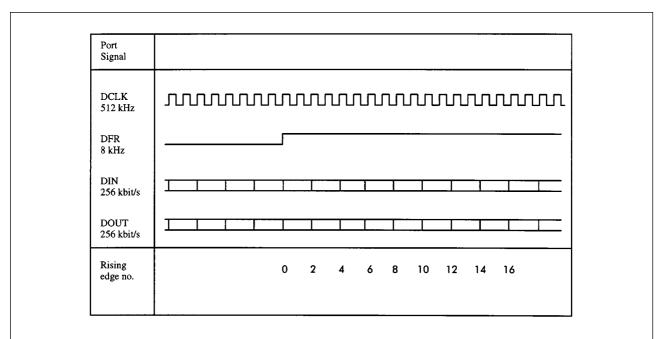

#### **Continuous Modes**

| Nominal bitrate of data (DIN and DOUT) | 256 kbit/s      |

|----------------------------------------|-----------------|

| Nominal frequency of clock (DCLK)      | 512 kHz         |

| Peak-to-peak output jitter (DCLK)      | ≤ 166 ns        |

| Nominal frequency of frame clock (DFR) | 8 kHz           |

| Mark-to-space ratio of DFR, i (input)  | 1:2 2:1         |

| Mark-to-space ratio of DFR, o (output) | 0.4:0.6 0.6:0.4 |

Figure 13 shows the timing of data and clocks at the digital interface 256 kbit/s (continuous modes).

Transitions of the data occur after even numbered rising edges of the DCLK. The data is valid on the odd numbered rising edges of the DCLK. Even-numbered rising edges of the clock are defined as the second rising edge following the rising edge of the frame clock and every second rising edge thereafter. The maximum allowed jitter is shown in figure 14.

The start of the frame is marked by the rising edge of the frame clock DFR.

One frame contains four time slots. The data streams at DIN and DOUT consist of four bytes per frame. See figure 15. The input data DIN and the output data DOUT are synchronous and in phase.

In the power-down state, the signal at DIN and at DOUT is high and the signal at DFR and DCLK is low.

Fig. 12: Timing of Data and Clocks at the GCI Interface

#### The GCI Interface

At the digital control interface the S-interface block is connected via a bidirectional serial interface, a digital bus called the General Circuit Interface (GCI), also called the ISDN Oriented Modular (IOM) interface. This bus is logically organized as many parallel point to point links, each at 256 kbit/s. The description of the GCI is available in the related documents and on page 23.

# The Physical Organization of the GCI Bus

The bus has a clock and frame signal as timing, and two data lines, one for each direction.

In NT mode the S-interface receives the GCI timing.

# General Content of the GCI Bus

The GCI interface is organized with 4 channels at 64 kbit/s: B1, B2, M (Maintenance or Monitor), and B1\* channel.

The B1 and B2 channels are transparent, switched at 64 kbit/s.

In ISDN applications the B1\* channel contains two D-channel bits, 4 bits C/I channel with the commands (towards S-interface) or the indications (from S-interface), and two extra bits (MR and MX) to control the M-channel.

The D-channel contains HDLC messages. It is transported transparently (NT) or terminated by an HDLC transceiver (LT-S/LT-T/TE). In the TE/LT-T a D-channel access protocol exists on the S-bus, which must be controlled by the S-interface, and obeyed by the HDLC transmitter.

Via the Command/Indication (C/I) channel, Commands to, and state Indications from the S-interface are exchanged with a control element (microcontroller) or with another uplink

Fig.13: Maximum Admissable Peak-To-Peak Input Jitter of Clocks (DCLK, DFR) at the GCI

or downlink ISDN circuit. Commands and Indications are debounced to avoid erroneous behaviour.

The M-channel is a 64 kbit/s channel. It has a byte oriented structure, and the content is indicated and acknowledged with the MR and MX bits, the two last bits in the B1\* channel. Content of the channel: write and read access of internal S-interface registers.

#### **Power-down on GCI**

For maximal power saving the GCI bus can be halted completely, and reactivated asynchronously from either side of the bus.

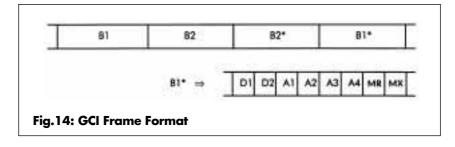

#### **Frame Format**

4 bytes are transmitted in each frame:

1st byte B1:

B-channel (64 kbit/s data), transparent

2nd byte B2:

B-channel (64 kbit/s data), transparent

3rd byte B2\*:

Monitor channel, DIN: 8 bit address, MSB first, DOUT: 8 bit data

4th byte B1\*:

2 bit D-channel (16 kbit/s data) 4 bit C/l channel A1, A2, A3, A4 A, E bit used to control the transfer of information on the Monitor channel

#### **External GCI Interfaces**

#### **G1 External GCI Interface**

Figure 16 shows a schematic representation of the two possible modes of the GCI ports.

In normal mode, corresponding to pin GMODE low, the two internal GCI interfaces are connected. The G1 interface is used as a monitorpoint.

In NTplus mode, corresponding to pin GMODE being high, the GCI interface coming from the U-interface block is connected to the G1 External GCI.

The S-interface block is connected to the G2 External GCI.

The U-interface block is the master of the GCI interface and thus controls the GCI clock (DCLK) and the GCI frame (DFR). DCLK and DFR signals at the G1 interface are outputs of the INTQ.

G1 interface characteristics:

- G1 DOUT: output, data channel, 256 KHz

- G1 DIN: input in NTplus mode, output in normal mode; data channel, 256 KHz

- G1 DFR: output, frame clock, 8 KHz

- G1 DCLK:output,clock, 512 KHz

The S-interface block is the slave of the GCI interface, so the GCI clock (DCLK) and the GCI frame (DFR) signals at the G2 interface are inputs of the INTQ.

G2 interface characteristics:

- G2 DOUT,: output, data channel, 256 KHz

- G2 DIN,: input, data channel, 256 KHz

- G2 DFR: input, frame clock, 8 KHz

- G2 DCLK: input, clock, 512 KHz

#### **G2 External GCI Interface**

In normal mode, corresponding to pin GMODE low, the two internal GCI interfaces are connected together. G2 interface has no function.

In NTplus mode, corresponding to pin GMODE high, the GCI interface of the S-interface block is connected to the G2 External GCI.

#### **U-Interface Command List**

The evaluation of any command is done according to a double last look criterion: any command is recognized only after the same command has been detected in two successive frames. Until then the preceding command is considered valid.

If commands are received that are not included in the list, the last recognized command is considered valid. Commands which are logically impossible to receive in the current state are ignored (ref. TS 102 080).

The indications are transmitted continuously in each frame. Under no circumstances can an indication that is not included in the list be transmitted. The maintenance and Service Channel, and the B2\* Channel are not used by the U-interface block.

#### Command and Indicate (C/I) Channel (A bits)

Command (DIN) (from GCI to U).

#### Table 16

| Table 10                   |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Awake                      | 0000: AW  | This command is to be used when the deactivated module interface is to be set in the power-up state. The control may be represented by a steady-state binary '0' condition at DIN. The module interface will be activated, i.e. provided with bit and frame clocks for synchronous transmission.  Any other command may now be applied.  The command AW, however, maintains the activated state of the module interface without emission of any signal at UO. |

| Activate                   | 1000: ACT | Layer 1 is activated at the U0 interface, starting with transmission of the wake-up signal INFO U1W. After execution of the wakeup procedure, the transmitter generates INFO U1A during synchronization process. When synchronization is completed successfully, the transmitter outputs INFO U1.                                                                                                                                                             |

| Synchronized               | 1100: SY  | When the synchronization process of the receiver is completed successfully, the transmitter outputs INFO U3. After reception of INFO U4H, Connect Through (CT) is indicated and the INTQ will be connected through from module interface to line interface (transparent).                                                                                                                                                                                     |

| Deactivate<br>Confirmation | 1111: DC  | This control has to be used if the reciever is to be able to recognize awake-<br>signals at interface UO, but the transmitter still is disabled. If no wake-up signal is<br>recognized, the INTQ is set to its power-down state. The module interface will<br>be deactivated.                                                                                                                                                                                 |

#### Indication (DOUT) (From U to GCI)

| Deactivate                           | 0000: DEAC  | A request to deactivate level 1 (INFO U0) has been detected. INFO U0 is transmitted at U0.                                                                                                                                                                          |  |

|--------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Test mode 1                          | 0010: TM1   | Forces S-interface in test mode 1, sending single zeros.  Not supported by the U-interface but recognized by the S-interface (NT mode only)                                                                                                                         |  |

| Resynchro-<br>nization               | 0100: RESYN | The receiver has lost framing and is attempting to resynchronize. The INTQ remains connected through from module interface to line interface (transparent).                                                                                                         |  |

| Activate                             | 1000: ACT   | The synchronous state of the receiver is established (without a loop 2 or a loop 4 command). The transmitter outputs INFO U1.                                                                                                                                       |  |

| Loop 2                               | 1010: L2    | The synchronous state of the receiver is established with a loop 2 command. The transmitter outputs INFO U3.                                                                                                                                                        |  |

| Connection<br>Through                | 1100: CT    | INFO U4H has been detected at the U-interface. The INTQ will be connected through from module interface to line interface (transparent).                                                                                                                            |  |

| Connection<br>Through<br>with Loop 2 | 1110: CTL2  | INFO U4H and a loop 2 command have been detected at the U-interface.  The INTQ will be connected through from module interface to line interface (transparent).                                                                                                     |  |

| Deactivated<br>Confirmation          | 1111: DC    | The transmitter is disabled, but the receiver remains enabled to detect wake-up signals at the U-interface. The INTQ is set in its power-down state, as long as wake-up signals are not recognized.  When a wake-up procedure is finished, INFO U1A is transmitted. |  |

#### **Power Down of the Interfaces**

In the following description, the U-interface port of the GCI interface (G1) is the master, and the S port of the GCI (G2) is the slave.

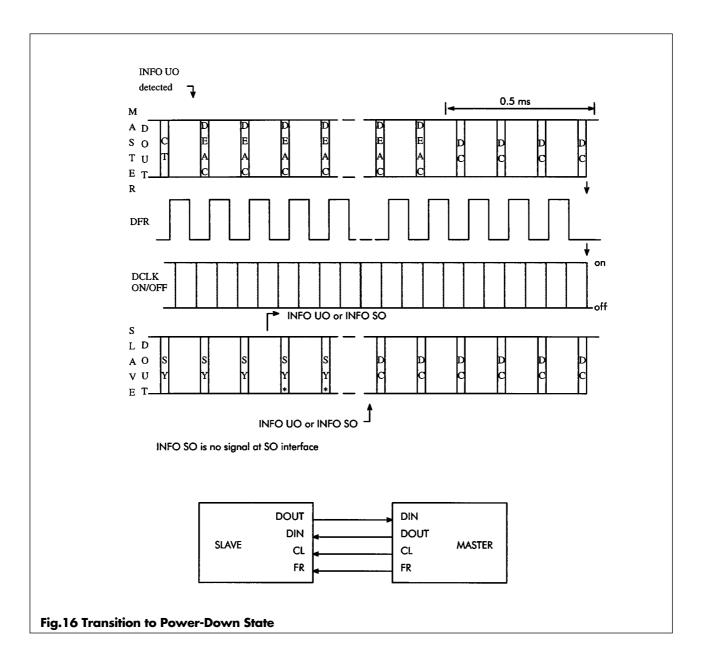

# Transition from Synchronous to Power-Down State

The corresponding procedure is shown in figure 17. After a DC code has been detected at the module interface of the master in two successive frames from the slave, the master responds by indicating DC four times and then the master turns off the timing signals at the end of bit A4 of the fourth DC indication. After this time, the DOUT pins of master and slave must be kept HIGH (quiescent condition).

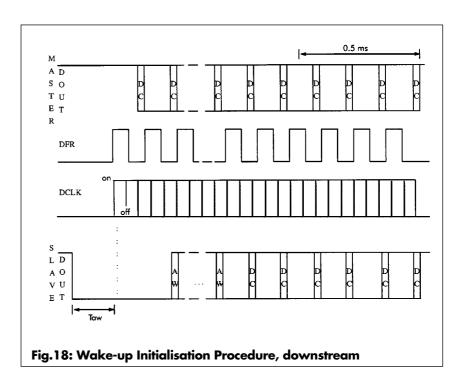

#### Wake-up Originated by Slave

Transition from power-down to synchronous operation is initiated by the slave by transmitting LOW at DOUT. See the figure above. The master responds by turning timing signals on within the wake-up time Taw (typical 4 ms, max. 10 ms). To ensure continuous supply of timing signals by the master the slave must keep DOUT LOW.

After the timing signals have been detected by the slave, the slave must transmit AW for at least two frames (e.g. 8 frames). Then the slave may insert a valid code in the C/I channel (e.g. ACT).

Monitoring of pin DOUT for LOW by the master will start only after the timing signals have been turned off.

It is required that the clock signals at DCLK and DFR will have the nominal frequency with the specified tolerance from the moment they are turned on. The slave may deactivate the master if only AW (not yet ACT) has been detected by the DC command or by transmitting continuous HIGH at DOUT. The master will respond by turning off the timing signals. See figure 18.

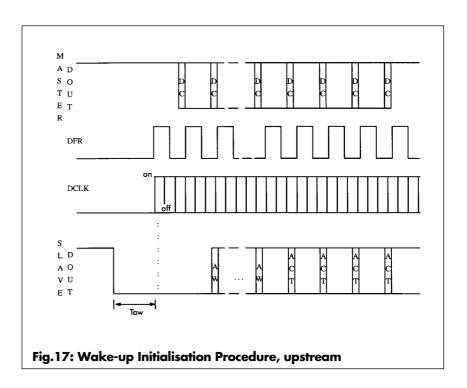

# Wake-up Originated by the Master

Transition of the device from power-down to synchronous state can be initiated by the master by turning on clock signals DCLK and DFR. Simultaneously, the master must apply the desired command code in the C/I channel.

The slave may enter the power-up state immediately after clock signals have been applied, and the received command code has been evaluated. See figure 19.

# S-Interface Commands and Indications Summary.

Table 17

| NT   | Downstr<br>Command | Upstr.<br>Indicat. |      | Downstr<br>Command | Upstr.<br>Indicat |

|------|--------------------|--------------------|------|--------------------|-------------------|

| 0000 | DR                 | TIM                | 1000 | ARd                | ARu               |

| 0001 | RES                | (IsI)              | 1001 | -                  | -                 |

| 0010 | ssz=TM1            | -                  | 1010 | ARL                | -                 |

| 0011 | TM2                | -                  | 1001 | -                  | -                 |

| 0100 | RSYd               | RSYu               | 1100 | Ald                | Alu               |

| 0101 | -                  | -                  | 1101 | -                  | -                 |

| 0110 | -                  | ei                 | 1110 | AIL                | -                 |

| 0111 | -                  | -                  | 1111 | did=DC             | Dlu               |

#### Commands (Downstream) in NT Mode

Table 18

| Table To |              |                              |                                                                                                           |  |

|----------|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| 0000     | DR           | Deactivate<br>Request        | Forces the S-interface block to deactivate the S-bus (=INFO0) followed by Dlu and did=DC                  |  |

| 0001     | RES          | RESET                        | Forces S-interface to soft reset, extended mode only,<br>S-interface accepts it in basic mode (merged)    |  |

| 0010     | ssz<br>= TM1 | TEST-MODE 1                  | Forces S-interface to test-mode 1, sending single zeros                                                   |  |

| 0011     | TM2          | TEST-MODE 2                  | Forces S-interface to test-mode 2, extended mode only, sending continuous zeros.                          |  |

| 0100     | RSYd         | Resynchon-<br>izing down     | The U-interface is not synchronous,<br>S-interface sends INFO2 (or SCZ), see remark 1 below               |  |

| 1000     | ARd          | Activation<br>Request down   | MTC-20172 S-interface forced to INFO2 transmission, receiver indicates the S-bus reaction                 |  |

| 1010     | ARL          | Activat. req<br>with S-loop  | INFO2 transmission on the S-bus<br>test loop2 switched (transparent loop)                                 |  |

| 1100     | Ald          | Activation<br>Indication     | INFO4 transmission, normally only after Alu indication is received                                        |  |

| 1110     | AIL          | Activ. Indic.<br>with S-loop | INFO4 transmission test loop2 switched (transparent loop)                                                 |  |

| 1111     | did=<br>DC   | Deactivate<br>Confirmation   | Deactivation confirmation, entering the power down state, INFO0 sent, critical timing to halt the clocks. |  |

**Remark 1:** When the U-interface is resynchronizing, the S-interface will send INFO2.

**Remark 2:** During loops, the S-interface simply ignores the incoming INFO3 from the S-bus. The receiver synchronizes on looped INFO2/4.

#### Indications (Upstream) in NT Mode

#### Table 19

| 0000 | TIM  | Timing<br>Request           | The S-interface requires GCI clocks.                                         |

|------|------|-----------------------------|------------------------------------------------------------------------------|

| 0100 | RSYu | Resynchron-<br>izing        | The S-bus receiver tries to synchronize                                      |

| 0101 |      |                             |                                                                              |

| 0110 | ei   | Error<br>Indication         | RSTB and SCZ- pin both low simultaneously                                    |

| 1000 | ARu  | Activation<br>Request up    | INFO1 received (actually any AMI signal)                                     |

| 1100 | Alu  | Activation<br>Indication up | Receiver synchronized on INFO2/3/4<br>(INFO3 normally, INFO2/4 in loop)      |

| 1111 | Dlu  | Deactivation<br>Indication  | Timer (32 ms) expired, or INFO0 received (16 ms) after DR (deactiv. request) |

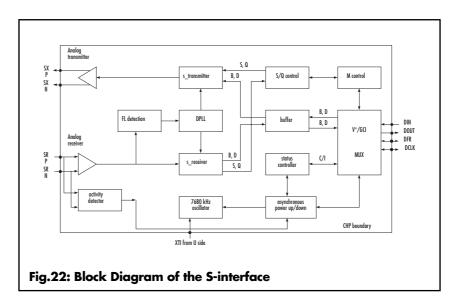

#### The S-Interface

#### **Functional Overview**

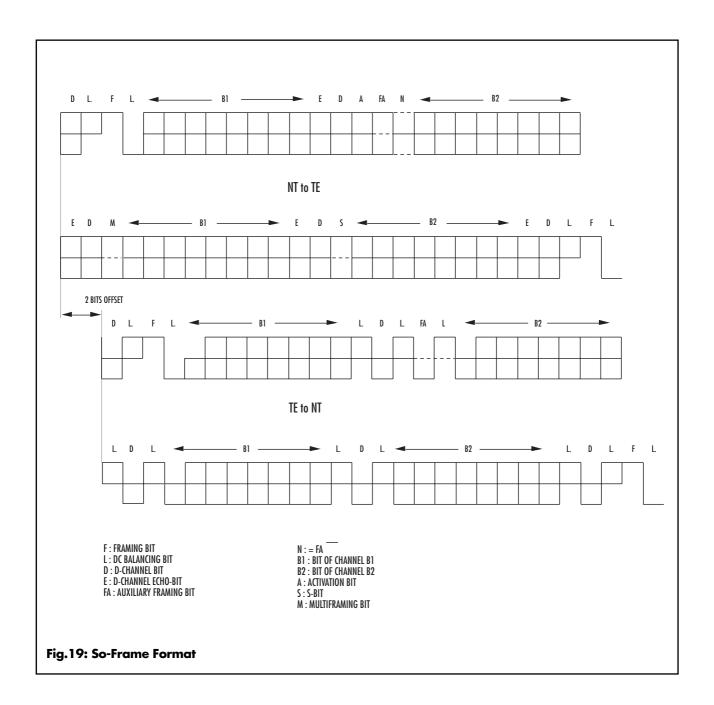

For transmission of data over the subscriber premises, the S-interface provides the So-interface. This interface enables full duplex transmission of data (2B + 1 D-channel) over 4 wires at a nominal data rate of 192 kBits/s. An Alternating Mark Invert (AMI) code is used for the line transmission. The transmission of data over the So-interface consists of frames of 250 µs. Each frame is 48 bits wide, and contains 4 data bytes (2 B1, 2 B2) and 4 D-bits.

The frame structures are shown in fig.20.

A frame start is marked using a first code violation (no mark inversion). To allow secure synchronization of the receiver, a second code violation is generated before the 14th bit of the frame. To guarantee this second violation, an auxiliary framing bit pair FA and N (from NT to TE) or the framing bit FA with associated balance bit (from TE to NT) are introduced.

The first bit of the transmitted frame from TE to NT is delayed for 2 bit periods with respect to the frame received from the NT. Furthermore, an echo bit (E-bit) for the D-channel and an activation bit (A-bit) are provided, where DC-balancing is done by means of the L-bits.

# General Description of the S-bus Interface

The S-interface can be used on the S-bus configured as a point-to-point connection or as a passive bus. The bus connection can handle up to 8 terminals. It is either a short bus with the terminals dispersed over a length of 200m, or an extended bus with a cluster of terminals within a 25 m range.

The chip handles full-duplex transmission of two B-channels (64 kbit/s each) and one D-channel (16 kbit/s). It handles also the echo E-channel, the multiframing S and Q bits, ...

The S-interface contains all circuit parts

necessary for the adaption of the S-interface, especially transmitter and receiver stages.

- S-bus outputs are balanced, allow ing bus operation;

- S-bus inputs are balanced;

- Out-of-band noise is filtered;

- RX has AGC and an adaptive threshold, and corrects long-line distortion by optimizing the sample moment.

- NT receiver bus type is selectable: short bus with fixed timing, or adap-

tive timing for extended bus or point to point.

The S-bus tranceiver stages must be connected to the bus via external interface circuitry (2:1 transformer) and protection. When the S-interface is in unpowered state (supply voltage = 0 V) the S-bus transmitter is high ohmic (see CCITT 1.430).

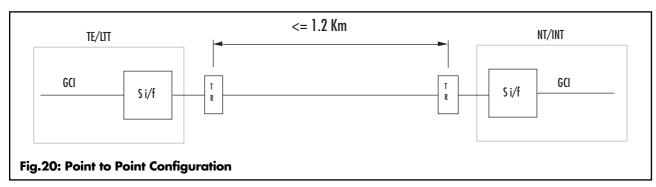

The S-interface can be used in a point-to-point and in a point to multipoint configuration (including extended passive bus). In the first configuration, the length of the cable is limited to aprox. 1.2 km (see fig. 21).

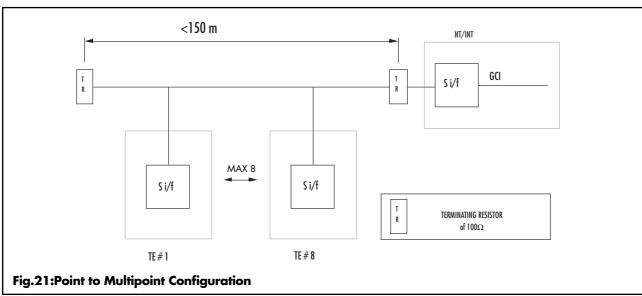

In the bus configuration (point to multipoint), up to 8 terminals may be connected to the SO-interface (fig.22)

The terminals must be connected in a range of 150 m. For the extended passive bus, the terminals must be clustered within a 25m range with a maximum cable length of about 1 km.