# **PM3392**

# S/UNI 1x10GE

# SATURN User Interface For 10 Gigabit Ethernet Lan Phy

**Data Sheet**

Proprietary and Confidential Released

Issue No. 7: December, 2006

#### **Legal Information**

#### Copyright

Copyright 2006 PMC-Sierra, Inc. All rights reserved.

The information in this document is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, no part of this document may be reproduced or redistributed in any form without the express written consent of PMC-Sierra, Inc.

PMC-2001304 (R7).

#### **Disclaimer**

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### **Trademarks**

S/UNI and SATURN are registered trademarks of PMC-Sierra, Inc. CRSU-4x2488, POS-PHY Level 4, and PMC-Sierra are trademarks of PMC-Sierra, Inc. Other product and company names mentioned herein may be the trademarks of their respective owners.

#### **Patents**

The technology discussed in this document may be protected by one or more patent grants.

## **Contacting PMC-Sierra**

PMC-Sierra 100-2700 Production Way Burnaby, BC Canada V5A 4X1

Tel: +1 (604) 415-6000 Fax: +1 (604) 415-6200

Document Information: <a href="mailto:document@pmc-sierra.com">document@pmc-sierra.com</a>

Corporate Information: <a href="mailto:info@pmc-sierra.com">info@pmc-sierra.com</a>

Technical Support: <a href="mailto:apps@pmc-sierra.com">apps@pmc-sierra.com</a>

Web Site: <a href="mailto:http://www.pmc-sierra.com">http://www.pmc-sierra.com</a>

# **Revision History**

| Issue No. | Issue Date     | Details of Change                                                                |  |

|-----------|----------------|----------------------------------------------------------------------------------|--|

| 7         | December 2006  | Updated package and ordering information.                                        |  |

| 6         | February 2006  | Updated ordering information including RoHS-compliant device details.            |  |

| 5         | October 2002   | Issue 5 data sheet created.                                                      |  |

| 4         | August 2002    | Issue 4 data sheet created.                                                      |  |

|           |                | Converted document to new template, modified doc to fix all Doc. related PREP's. |  |

| 3         | January 2002   | Issue 3 data sheet created.                                                      |  |

| 2         | October 2001   | Issue 2 data sheet created.                                                      |  |

| 1         | September 2000 | Preliminary data sheet created.                                                  |  |

## **Table of Contents**

| Leg | gal Info | rmation                                              | 2  |

|-----|----------|------------------------------------------------------|----|

|     | Copyr    | ight                                                 | 2  |

|     |          | ilmer                                                |    |

|     | Trade    | marks                                                | 2  |

|     | Paten    | ts 2                                                 |    |

|     |          | g PMC-Sierra                                         |    |

| Re  | vision l | History                                              | 4  |

| Tab | ole of C | contents                                             | 5  |

| Lis | t of Re  | gisters                                              | 8  |

|     | _        | ures                                                 |    |

| Lis | t of Tab | oles                                                 | 15 |

| 1   | Defini   | tions                                                | 17 |

| 2   | Featu    | res                                                  | 19 |

|     | 2.1      | General                                              | 19 |

|     | 2.2      | 10 Gigabit Ethernet MAC                              | 19 |

|     | 2.3      | Statistics                                           | 20 |

|     | 2.4      | POS-PHY Level 4 Interface                            | 20 |

| 3   | Applic   | cations                                              | 21 |

| 4   | Refer    | ences                                                | 22 |

| 5   | Applic   | cation Examples                                      | 23 |

| 6   | Block    | Diagram                                              | 24 |

| 7   | Descr    | iption                                               | 26 |

| 8   | Pin Di   | iagram                                               | 28 |

| 9   | Pin D    | escription                                           | 31 |

| 10  | Funct    | ional Description                                    | 57 |

|     | 10.1     | Primary Interfaces, Line Side and System Side        | 57 |

|     | 10.2     | Receive Channel (Ingress) – Line Side to System Side | 57 |

|     | 10.3     | Transmit Channel (Egress) – System Side to Line Side | 70 |

|     | 10.4     | Management Statistics (MSTAT)                        | 77 |

|     | 10.5     | Management Data Interface                            | 79 |

|     | 10.6     | JTAG Test Access Port Interface                      | 79 |

|     | 10.7     | Microprocessor Interface                             | 80 |

| 11  | Norma    | al Mode Register Description                         | 81 |

| 12 | Test F | eatures Description                                          | 293 |

|----|--------|--------------------------------------------------------------|-----|

|    | 12.1   | High Impedance State for IO                                  | 293 |

|    | 12.2   | Test Registers                                               | 293 |

|    | 12.3   | JTAG Test Port                                               | 295 |

| 13 | Opera  | tion                                                         | 303 |

|    | 13.1   | Power Sequencing                                             | 303 |

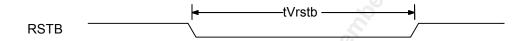

|    | 13.2   | Device Reset                                                 | 303 |

|    | 13.3   | Line-Side LVDS Interface Overview                            | 304 |

|    | 13.4   | POS-PHY Level 4 Introduction                                 |     |

|    | 13.5   | POS-PHY Level 4 Clocking                                     | 306 |

|    | 13.6   | POS-PHY Level 4 Initialization                               | 308 |

|    | 13.7   | PL4 Bus Operation                                            | 314 |

|    | 13.8   | XSBI Wrapper Line Interface                                  |     |

|    | 13.9   | Loopback Operation                                           | 323 |

|    | 13.10  | Controlling Ethernet Frame Reception and Transmission        | 324 |

|    | 13.11  | Ten Gigabit Ethernet InterFrameGap Support                   | 325 |

|    | 13.12  | Ten Gigabit Ethernet Preamble Support                        | 327 |

|    | 13.13  | Ten Gigabit Ethernet MAC Transmit Padding and CRC Generation | 328 |

|    | 13.14  | Ethernet Frame Transmit Errors                               | 329 |

|    | 13.15  | Frame Length Support                                         | 331 |

|    | 13.16  | Frame Data and Byte Format                                   | 333 |

|    | 13.17  | Frame Filtering                                              | 340 |

|    | 13.18  | PAUSE Flow Control                                           | 344 |

|    | 13.19  | Ethernet MAC Receive FIFO Overrun Condition                  | 348 |

|    | 13.20  | Using the Performance Monitoring Features                    | 349 |

|    | 13.21  | Interrupt Handling                                           | 349 |

|    | 13.22  | JTAG Support                                                 | 350 |

|    | 13.23  | Receive PCS Layer Error Handling                             | 355 |

|    | 13.24  | Transmit PCS Layer Error Handling                            | 358 |

|    | 13.25  | MDIO Access                                                  | 359 |

| 14 | Functi | onal Timing                                                  | 361 |

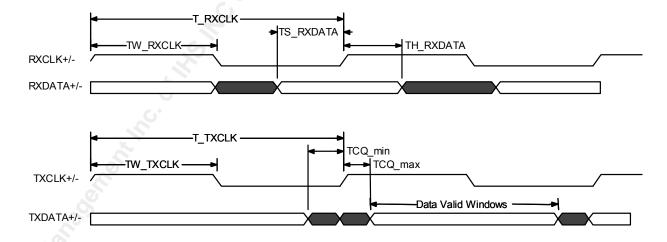

|    | 14.1   | PL4 Interface Data Path and FIFO Status Timing               | 361 |

|    | 14.2   | XSBI Functional Timing                                       | 362 |

| 15 | Absolu | ute Maximum Ratings                                          | 364 |

| 16 | D.C. C | Characteristics                                              | 365 |

| 17  | Microp | processor Interface Timing Characteristics | 368 |

|-----|--------|--------------------------------------------|-----|

| 18  |        | ning Characteristics                       |     |

|     | 18.1   | PL4 Interface Timing                       | 371 |

|     |        | System Miscellaneous Timing                |     |

|     | 18.3   | XSBI Interface Timing                      | 378 |

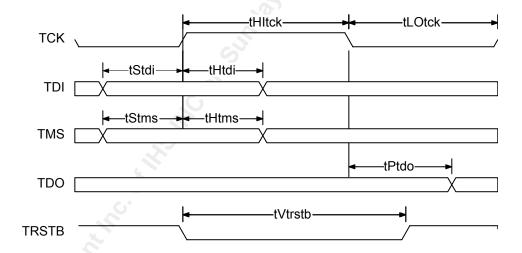

|     | 18.4   | JTAG Port Timing                           | 379 |

|     |        | MDIO/MDC Timing                            |     |

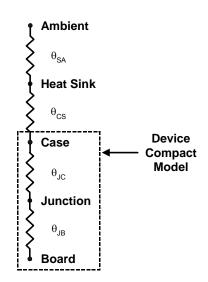

| 19  | Therm  | al Information                             | 381 |

|     | 19.1   | Power Requirements                         | 382 |

| 20  | Mecha  | nical Information                          | 384 |

| 21  | Orderi | ng Information                             | 386 |

| Not | es     | 387                                        |     |

# **List of Registers**

| Register 0x0000H:PM3392 Identification                    | 96  |

|-----------------------------------------------------------|-----|

| Register 0x0001H:PM3392 Product Revision                  | 97  |

| Register 0x0002H:PM3392 Configuration and Reset Control   | 98  |

| Register 0x0003H:PM3392 Master Interrupt Status           | 100 |

| Register 0x0004H:PM3392 Device Status                     | 103 |

| Register 0x0005H:PM3392 Global Performance Monitor Update | 105 |

| Register 0x0006H:MDIO Command Register                    | 106 |

| Register 0x0007H:MDIO Interrupt Mask Register             | 108 |

| Register 0x0008H:MDIO Interrupt Register                  |     |

| Register 0x0009H:MMD PHY Address Register                 | 110 |

| Register 0x000AH:MMD Control Address Data Register        | 111 |

| Register 0x000BH:MDIO Read Status Data Register           | 112 |

| Register 0x0100H:XSBI Wrapper Configuration Register      | 113 |

| Register 0x0104H:XSBI Interrupt Status                    | 116 |

| Register 0x0107H:XSBI Interrupt ENABLE2                   | 118 |

| Register 0x0108H:XSBI Interrupt ENABLE3                   | 119 |

| Register 0x0109H:XSBI RXOOLV                              | 120 |

| Register 0x010AH:XSBI Analog Debug Register               | 121 |

| Register 0x2040H:RXXG Configuration 1                     | 122 |

| Register 0x2042H:RXXG Configuration 3                     | 125 |

| Register 0x2043H:RXXG Interrupt                           | 127 |

| Register 0x2044H:RXXG Status                              | 129 |

| Register 0x2045H:RXXG Maximum Frame Length                | 130 |

| Register 0x2046H:RXXG SA[15:0] – Station Address          | 131 |

| Register 0x2047H:RXXG SA[31:16] – Station Address         | 132 |

| Register 0x2048H:RXXG SA[47:32] – Station Address         | 133 |

| Register 0x2049H:RXXG Receive FIFO Threshold              | 134 |

| Register 0x204AH:RXXG Exact Match Address 0 Low Word      | 137 |

| Register 0x204BH:RXXG Exact Match Address 0 Mid Word      | 138 |

| Register 0x204CH:RXXG Exact Match Address 0 High Word     | 139 |

| Register 0x204DH:RXXG Exact Match Address 1 Low Word      | 140 |

| Register 0x204EH: RXXG Exact Match Address 1 Mid Word     | 141 |

| Register 0x204FH:RXXG Exact Match Address 1 High Word     | 142 |

| Register 0x2050H:RXXG Exact Match Address 2 Low Word  | 143 |

|-------------------------------------------------------|-----|

| Register 0x2051H:RXXG Exact Match Address 2 Mid Word  |     |

| Register 0x2052H:RXXG Exact Match Address 2 High Word | 145 |

| Register 0x2053H:RXXG Exact Match Address 3 Low Word  | 146 |

| Register 0x2054H:RXXG Exact Match Address 3 Mid Word  | 147 |

| Register 0x2055H:RXXG Exact Match Address 3 High Word | 148 |

| Register 0x2056H:RXXG Exact Match Address 4 Low Word  |     |

| Register 0x2057H:RXXG Exact Match Address 4 Mid Word  |     |

| Register 0x2058H:RXXG Exact Match Address 4 High Word |     |

| Register 0x2059H:RXXG Exact Match Address 5 Low Word  | 152 |

| Register 0x205AH:RXXG Exact Match Address 5 Mid Word  | 153 |

| Register 0x205BH:RXXG Exact Match Address 5 High Word | 154 |

| Register 0x205CH:RXXG Exact Match Address 6 Low Word  | 155 |

| Register 0x205DH:RXXG Exact Match Address 6 Mid Word  | 156 |

| Register 0x205EH:RXXG Exact Match Address 6 High Word | 157 |

| Register 0x205FH: RXXG Exact Match Address 7 Low Word | 158 |

| Register 0x2060H:RXXG Exact Match Address 7 Mid Word  | 159 |

| Register 0x2061H:RXXG Exact Match Address 7 High Word | 160 |

| Register 0x2062H:RXXG Exact Match VID 0               | 161 |

| Register 0x2063H:RXXG Exact Match VID 1               | 162 |

| Register 0x2064H:RXXG Exact Match VID 2               | 163 |

| Register 0x2065H:RXXG Exact Match VID 3               | 164 |

| Register 0x2066H:RXXG Exact Match VID 4               | 165 |

| Register 0x2067H:RXXG Exact Match VID 5               | 166 |

| Register 0x2068H:RXXG Exact Match VID 6               | 167 |

| Register 0x2069H:RXXG Exact Match VID 7               | 168 |

| Register 0x206AH: RXXG Multicast HASH Low Word        | 169 |

| Register 0x206BH:RXXG Multicast HASH MidLow Word      | 170 |

| Register 0x206CH:RXXG Multicast HASH MidHigh Word     | 171 |

| Register 0x206DH:RXXG Multicast HASH High Word        | 172 |

| Register 0x206EH:RXXG Address Filter Control 0        | 173 |

| Register 0x206FH:RXXG Address Filter Control 1        | 175 |

| Register 0x2070H:RXXG Address Filter Control 2        | 177 |

| Register 0x2080H:R64B66B Configuration                | 178 |

| Register 0x2081H:R64B66B Interrupt Mask               | 179 |

| Register 0x2082H:R64B66B Interrupt Status                              | 181 |

|------------------------------------------------------------------------|-----|

| Register 0x2083H:R64B66B Status                                        |     |

| Register 0x2084H:R64B66B ERROR_FRAME_CNT                               | 185 |

| Register 0x2085H:R64B66B FRAME_LOCK_COUNT[15:0]                        | 186 |

| Register 0x2086H:R64B66B HI_BER_CNT[4:0]                               | 187 |

| Register 0x2087H: R64B66B JITTER_CNT[15:0]                             |     |

| Register 0x2100H:MSTAT Control                                         |     |

| Register 0x2101H:MSTAT Counter Rollover 0                              |     |

| Register 0x2102H:MSTAT Counter Rollover 1                              |     |

| Register 0x2103H:MSTAT Counter Rollover 2                              | 192 |

| Register 0x2104H:MSTAT Counter Rollover 3                              |     |

| Register 0x2105H:MSTAT Interrupt Mask 0                                | 194 |

| Register 0x2106H:MSTAT Interrupt Mask 1                                | 195 |

| Register 0x2107H:MSTAT Interrupt Mask 2                                | 196 |

| Register 0x2108H:MSTAT Interrupt Mask 3                                | 197 |

| Register 0x2109H:MSTAT Counter Write Address                           | 198 |

| Register 0x210AH:MSTAT Counter Write Data Low                          | 199 |

| Register 0x210BH:MSTAT Counter Write Data Middle                       | 200 |

| Register 0x210CH:MSTAT Counter Write Data High                         | 201 |

| Register 0x2110H to 0x21E6H:MSTAT Receive Statistical Counters' Low    | 202 |

| Register 0x2110H to 0x21E6H:MSTAT Receive Statistical Counters' Middle | 203 |

| Register 0x2110H to 0x21E6H:MSTAT Receive Statistical Counters' High   | 204 |

| Register 0x2200H:IFLX Global Configuration Register                    | 215 |

| Register 0x2201H:IFLX Channel Provision                                | 216 |

| Register 0x2209H:IFLX FIFO Overflow Enable                             | 217 |

| Register 0x220AH:IFLX FIFO Overflow Interrupt                          | 218 |

| Register 0x220DH:IFLX Indirect Channel Address                         | 219 |

| Register 0x220EH:IFLX Indirect Logical FIFO Low Limit & Provision      | 220 |

| Register 0x220FH:IFLX Indirect Logical FIFO High Limit                 | 221 |

| Register 0x2210H:IFLX Indirect Full/Almost Full Status & Limit         | 222 |

| Register 0x2211H:IFLX Indirect Empty/Almost Empty Status & Limit       | 223 |

| Register 0x2240H:PL4MOS Configuration Register                         | 224 |

| Register 0x2241H:PL4MOS Reserved                                       | 226 |

| Register 0x2242H:PL4MOS Fairness Mask                                  | 227 |

| Register 0x2243H:PL4MOS MaxBurst1 Register                             | 228 |

| Register 0x2244H:PL4MOS MaxBurst2 Register                       | 229 |

|------------------------------------------------------------------|-----|

| Register 0x2245H:PL4MOS Transfer Size Register                   | 230 |

| Register 0x2280H:PL4ODP Configuration                            | 231 |

| Register 0x2282H:PL4ODP Interrupt Mask                           | 233 |

| Register 0x2283H:PL4ODP Interrupt                                | 234 |

| Register 0x2284H:PL4ODP Configuration MAX_T Register             |     |

| Register 0x2300H:PL4IO Lock Detect Status                        |     |

| Register 0x2301H:PL4IO Lock Detect Change                        |     |

| Register 0x2302H:PL4IO Lock Detect Mask                          | 241 |

| Register 0x2303H:PL4IO Lock Detect Limits                        | 243 |

| Register 0x2304H:PL4IO Calendar Repetitions                      |     |

| Register 0x2305H:PL4IO Configuration                             |     |

| Register 0x3040H:TXXG Configuration Register 1                   | 250 |

| Register 0x3042H:TXXG Configuration Register 3                   |     |

| Register 0x3043H:TXXG Interrupt                                  | 255 |

| Register 0x3044H:TXXG Status Register                            | 257 |

| Register 0x3045H:TXXG TX_MAXFR Transmit Max Frame Size Register  | 258 |

| Register 0x3046H:TXXG TX_MINFR Transmit Min Frame Size Register  | 259 |

| Register 0x3047H:TXXG SA[15:0] Station Address                   | 260 |

| Register 0x3048H:TXXG SA[31:16] Station Address                  | 261 |

| Register 0x3049H:TXXG SA[47:32] Station Address                  | 262 |

| Register 0x304DH:TXXG PAUSE_TIME – PAUSE TIMER Register          | 263 |

| Register 0x304EH:TXXG PAUSE_IVAL PAUSE Timer Interval Register   | 264 |

| Register 0x3052H:TXXG Pause Quantum Value Configuration Register | 265 |

| Register 0x3080H:T64B66B Configuration 1                         | 266 |

| Register 0x3083H:T64B66B Status                                  | 268 |

| Register 0x3085H: JITTER TEST SEED A 3                           | 270 |

| Register 0x3086H: JITTER TEST SEED A 2                           | 271 |

| Register 0x3087H: JITTER TEST SEED A 1                           | 272 |

| Register 0x3088H: JITTER TEST SEED A 0                           | 273 |

| Register 0x3089H: JITTER TEST SEED B 3                           | 274 |

| Register 0x308AH: JITTER TEST SEED B 2                           | 275 |

| Register 0x308BH: JITTER TEST SEED B 1                           | 276 |

| Register 0x308CH: JITTER TEST SEED B 0                           | 277 |

| Register 0x3200H:EFLX Global Configuration                       | 278 |

| Register 0x3201H:EFLX ERCU Global Status                           | 279 |

|--------------------------------------------------------------------|-----|

| Register 0x3202H:EFLX Indirect Channel Address                     | 280 |

| Register 0x3203H:EFLX Indirect Logical FIFO Low Limit              | 281 |

| Register 0x3204H:EFLX Indirect Logical FIFO High Limit             | 282 |

| Register 0x3205H:EFLX Indirect Full/Almost-Full Status and Limit   | 283 |

| Register 0x3206H:EFLX Indirect Empty/Almost-Empty Status and Limit | 284 |

| Register 0x3207H:EFLX Indirect FIFO Cut-Through Threshold          | 285 |

| Register 0x320CH:EFLX FIFO Overflow Error Enable                   | 286 |

| Register 0x320DH: EFLX FIFO Overflow Error Indication              | 287 |

| Register 0x3210H:EFLX Channel Provision                            | 288 |

| Register 0x3280H:PL4IDU Configuration                              | 289 |

| Register 0x3281H:PL4IDU Status                                     | 290 |

| Register 0x3282H:PL4IDU Interrupt Mask                             | 291 |

| Register 0x3283H:PL4IDU Interrupt                                  | 292 |

| PM3392 Test Register 0                                             | 294 |

| PM3392 Test Register 4                                             |     |

# **List of Figures**

| Figure 1 10 Gigabit Ethernet Reference Model       | 21            |

|----------------------------------------------------|---------------|

| Figure 2 Router - 10G Port Capable                 | 23            |

| Figure 3 Normal Mode                               | 24            |

| Figure 4 Loopback Paths                            | 25            |

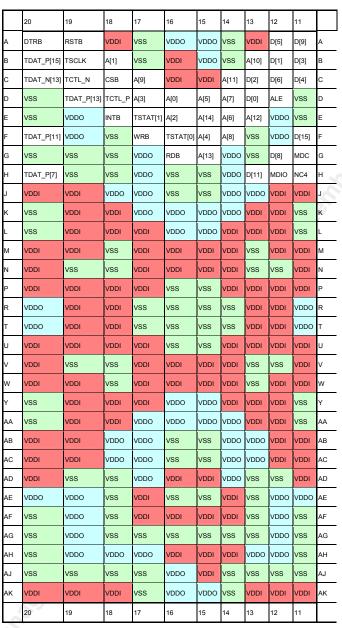

| Figure 5 Ball View 1                               |               |

| Figure 6 Ball View 2                               |               |

| Figure 7 Ball View 3                               | 29            |

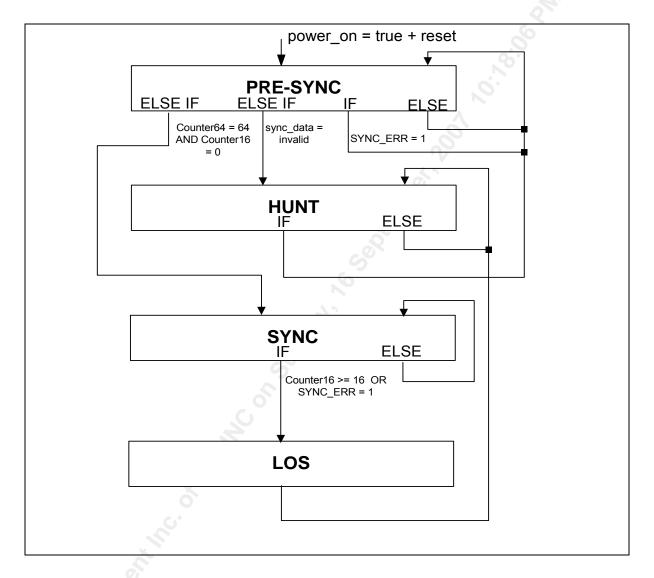

| Figure 8 RX SYNC State Machine                     |               |

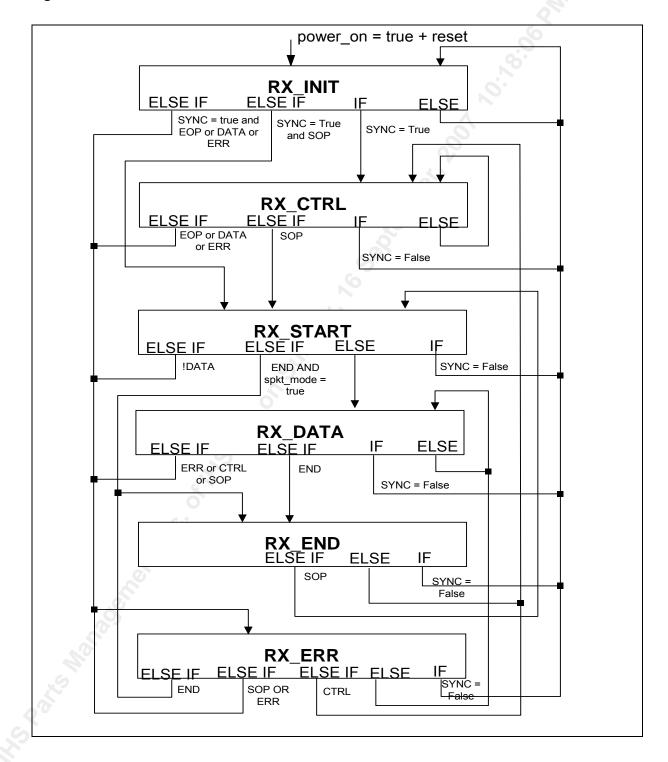

| Figure 9 Receive State Machine                     |               |

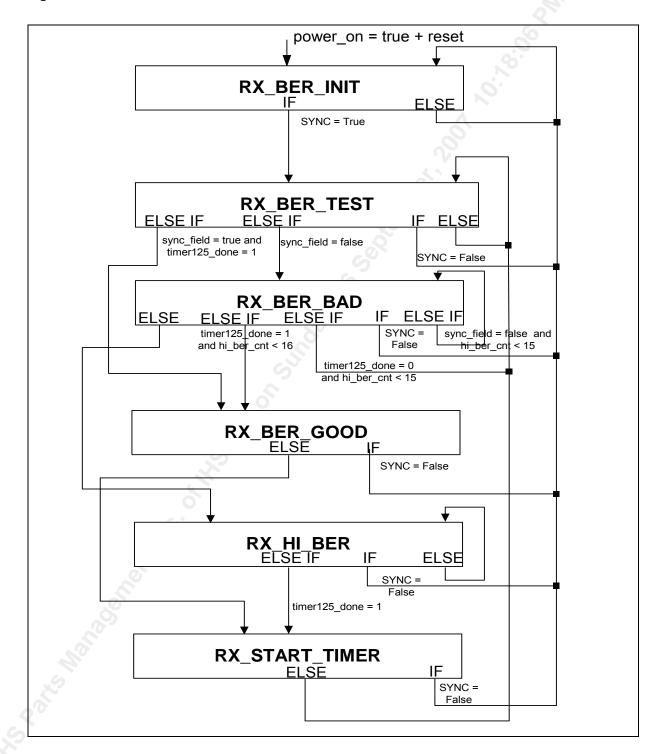

| Figure 10 RX BER State Machine                     |               |

| Figure 11 State Machine of a FIFO Channel          | 68            |

| Figure 12 TX Processing Steps For 66-Bit Codes     |               |

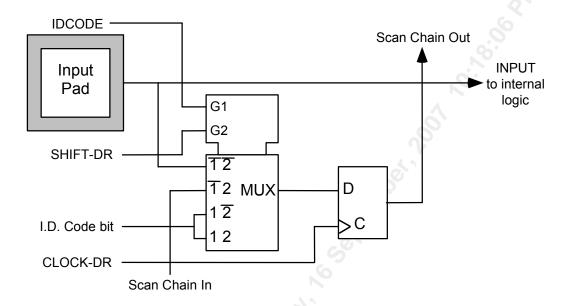

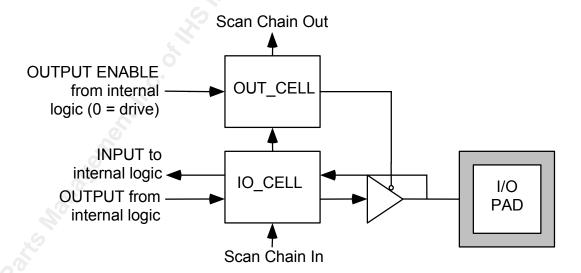

| Figure 13 Input Observation Cell (IN_CELL)         |               |

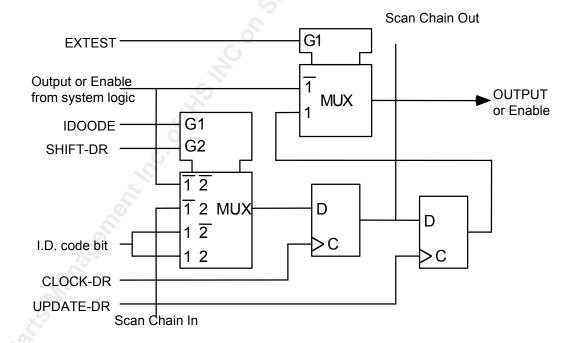

| Figure 14 Output Cell (OUT_CELL)                   |               |

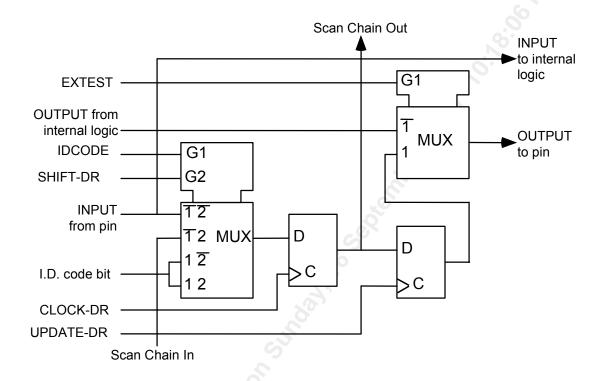

| Figure 15 Bi-directional Cell (IO_CELL)            | 302           |

| Figure 16 Layout of Output Enable and Bi-direction | onal Cells302 |

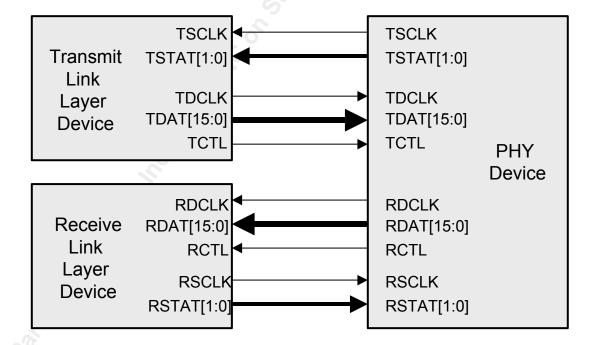

| Figure 17 POS-PHY Level 4 Interfaces               | 305           |

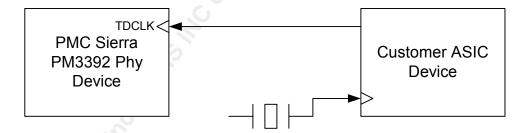

| Figure 18 POS-PHY Level 4 Slave Clocking Mod       | le306         |

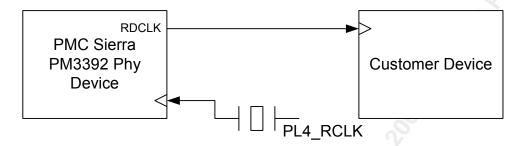

| Figure 19 POS-PHY Level 4 Master Clocking Mo       |               |

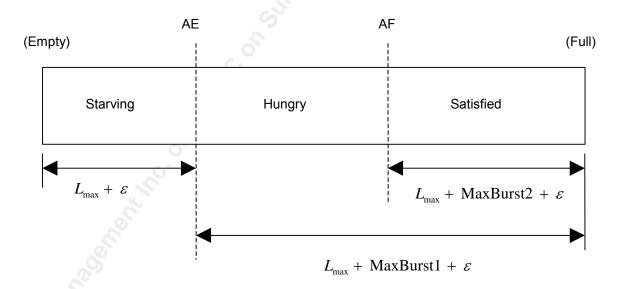

| Figure 20 Sample FIFO Thresholds                   | 312           |

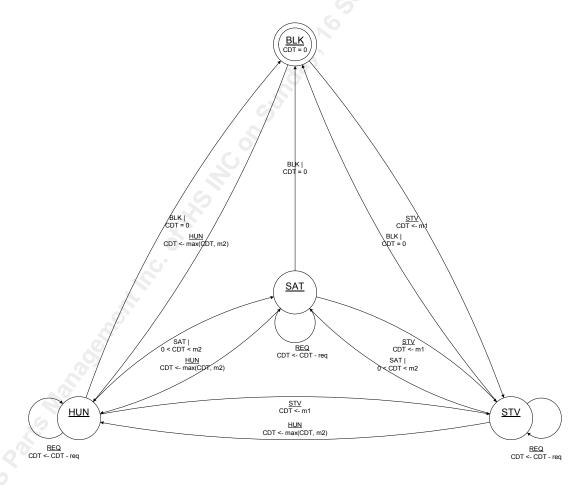

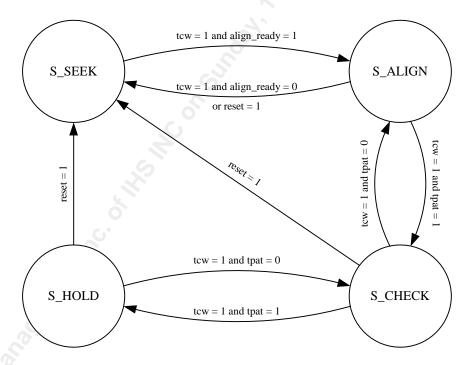

| Figure 21 PL4IO Data In State Diagram              | 317           |

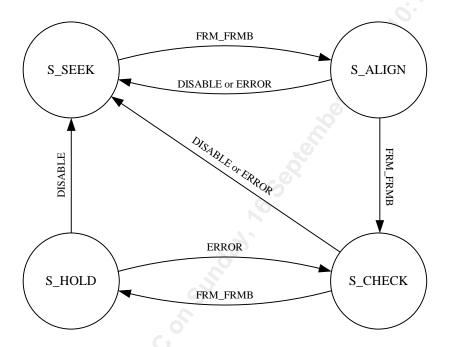

| Figure 22 PL4IO FIFO Status State Diagram          | 319           |

| Figure 23 PL4IO Status In State Diagram            | 320           |

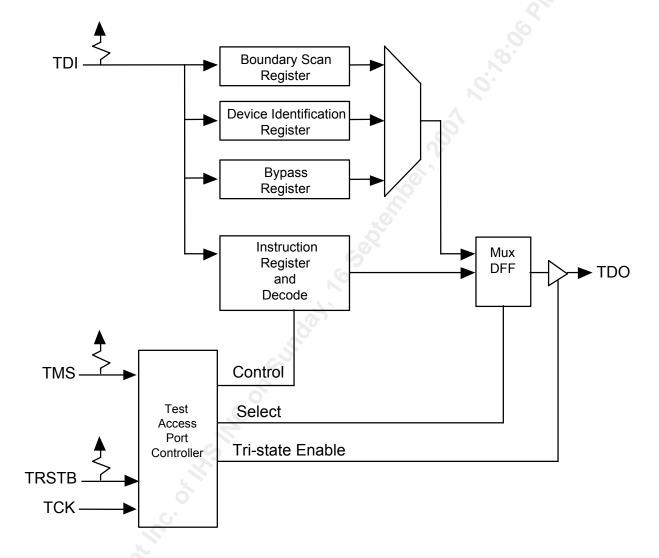

| Figure 24 Boundary Scan Architecture               |               |

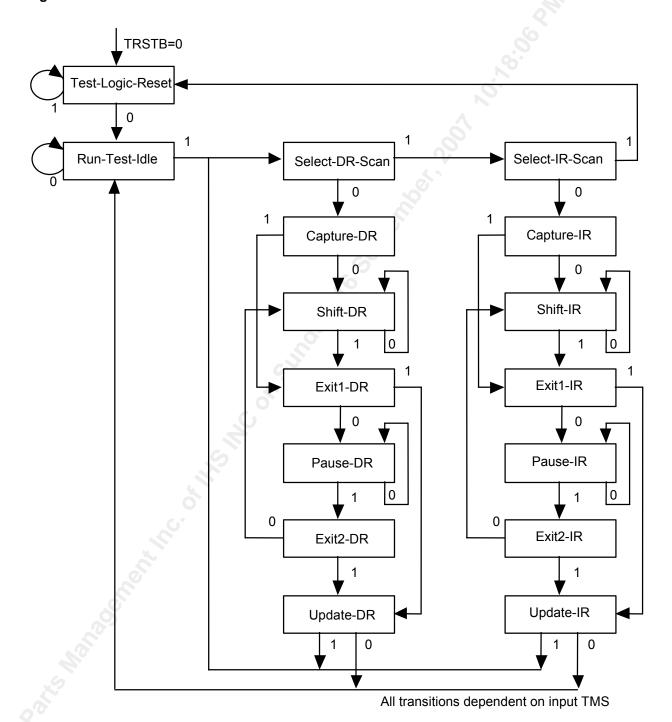

| Figure 25 TAP Controller Finite State Machine      | 353           |

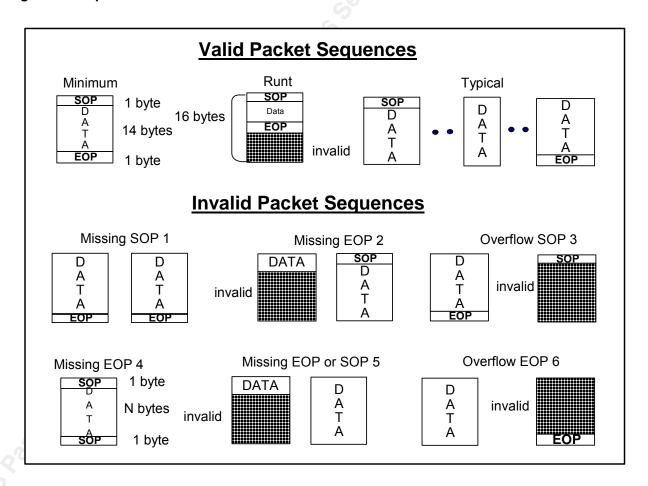

| Figure 26 Expected Packet Formats                  | 356           |

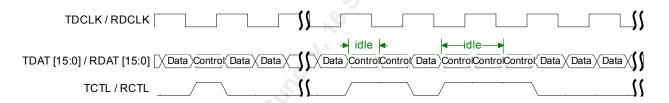

| Figure 27 PL4 Interface Data Path Functional Tir   | ning361       |

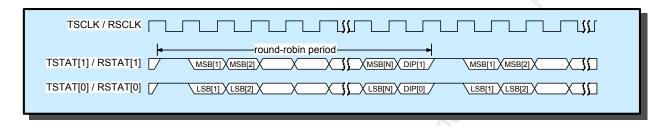

| Figure 28 PL4 Interface FIFO Status Functional     | Timing362     |

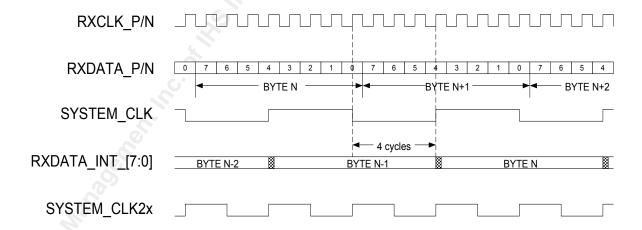

| Figure 29 Ingress Timing Diagram                   | 362           |

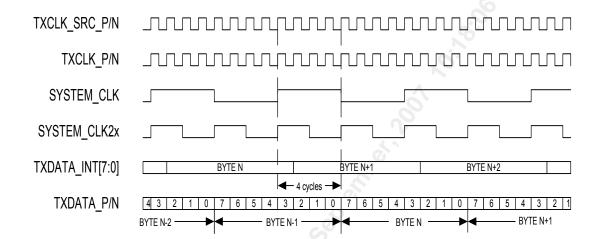

| Figure 30 Egress Timing Diagram                    | 363           |

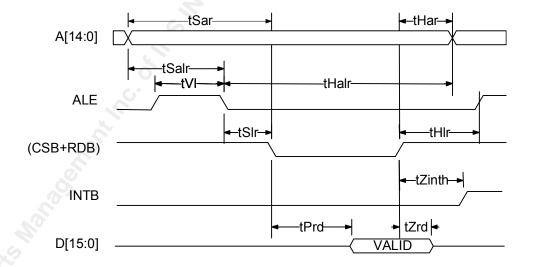

| Figure 31 Microprocessor Interface Read Timing     | 368           |

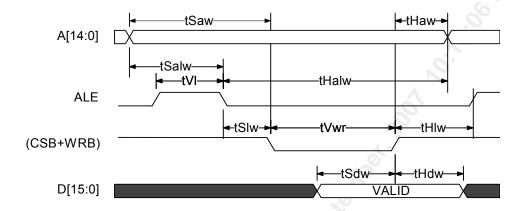

| Figure 32 Microprocessor Interface Write Timing    | 370           |

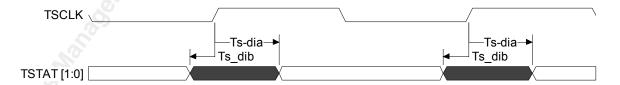

| Figure 33 PL4 Bus Output Status AC Timing Diag     | gram 374      |

#### S/UNI-1x10GE ASSP Telecom Standard Product Data Sheet Released

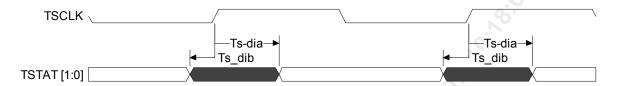

| Figure 34 | PL4 Bus Input Status AC Timing Diagram          | . 375 |

|-----------|-------------------------------------------------|-------|

| Figure 35 | PL4 Bus Output Status AC Timing Diagram         | . 376 |

| Figure 36 | PL4 Bus Input Status AC Timing Diagram          | . 376 |

| Figure 37 | System Miscellaneous Timing Diagram             | . 377 |

| Figure 38 | Line Interface Timing                           | . 378 |

| Figure 39 | JTAG Port Interface Timing                      | . 379 |

| Figure 40 | MDC / MDIO Physical Timing                      | . 380 |

| Figure 41 | 896 PIN FCBGA -31x31 MM BODY - (3M Substrate)   | . 384 |

| Figure 42 | 896 PIN FCBGA -31x31 MM BODY - (HDBU Substrate) | . 385 |

## **List of Tables**

| Table 1 S/UNI-1x10GE Abbreviations                                    | 17  |

|-----------------------------------------------------------------------|-----|

| Table 2 S/UNI-1x10GE Line Side Signaling Interface                    | 31  |

| Table 3 S/UNI-1x10GE System Side Signaling Interface                  |     |

| Table 4 ECBI Signals and MDC/MDIO                                     | 39  |

| Table 5 JTAG and Reserved Signals                                     | 41  |

| Table 6 S/UNI-1x10GE Analog Pins                                      | 43  |

| Table 7 Digital Power and Ground                                      |     |

| Table 8 Preamble Checking                                             | 64  |

| Table 9 Range, Size and CRC Result Processing                         | 64  |

| Table 10 Receive Statistics Counters                                  | 78  |

| Table 11 Transmit Statistics Counters                                 | 78  |

| Table 12 Register Memory Map                                          |     |

| Table 13 Normal Mode Register Map                                     | 81  |

| Table 14 CUT_THRU_THRES Packet Sizes                                  | 135 |

| Table 15 MSTAT Counter Description                                    | 205 |

| Table 16 InterPacket Gap Encoding                                     | 251 |

| Table 17 Instruction Register (Length - 3 Bits)                       | 295 |

| Table 18 Identification Register                                      | 296 |

| Table 19 Boundary Scan Register                                       | 296 |

| Table 20 PL4 Bus Data Transfer Rate For Non-Blocking Operation        | 308 |

| Table 21 Transmit InterPacket Gap Encoding                            | 326 |

| Table 22 PM3392 Minimum Transmit Frame Size Padding                   | 328 |

| Table 23 Std 802-1990, Figure 5-3 Universal Address                   | 334 |

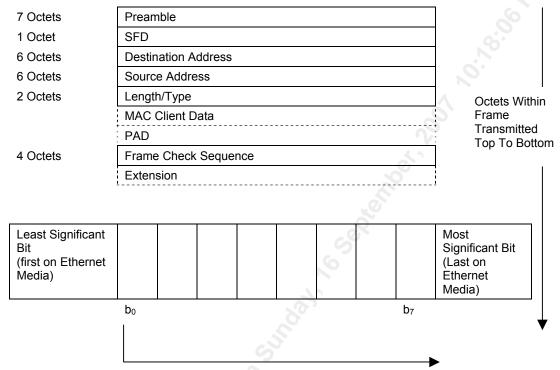

| Table 24 MAC Frame Format                                             | 336 |

| Table 25 PM3392 Data Order On PL4 Interface, Non-VLAN Ethernet Frame  | 337 |

| Table 26 PM3392 Data Order On PL4 Interface, VLAN Ethernet Frame Type | 338 |

| Table 27 Ten Gigabit Ethernet Frame Example                           | 339 |

| Table 28 Address Filter Result in Non-Promiscuous Mode                | 343 |

| Table 29 Address Filter in Promiscuous Mode                           | 343 |

| Table 30 PAUSE Control Frame Format                                   | 345 |

| Table 31 IFLX FIFO Settings for lossless flow control                 | 346 |

| Table 32 PAUSE Frame Programmable Control                             | 347 |

| Table 33 Maximum Ratings                                              | 364 |

| Table 34 | Core Supply Voltage Specs                                     | 364 |

|----------|---------------------------------------------------------------|-----|

| Table 35 | I/O Supply Voltage Specs                                      | 364 |

| Table 36 | D.C. Characteristics                                          | 365 |

| Table 37 | Microprocessor Interface Multiplexed Read Timing              | 368 |

| Table 38 | Microprocessor Interface Write Access                         | 369 |

| Table 39 | LVDS Electrical Specifications                                | 371 |

| Table 40 | Reference Clock Timing Specifications for divBy2 (PL4_REFCLK) | 371 |

| Table 41 | Reference Clock Timing Specifications for divBy4 (PL4_REFCLK) | 372 |

| Table 42 | Output Data Timing (RDCLK, RCTL, RDAT)                        |     |

| Table 43 | Input Data Timing (TDCLK, TCTL, TDAT)                         | 373 |

| Table 44 | Output Status Timing (TSCLK, TSTAT[1:0])                      | 374 |

| Table 45 | Input Status Timing (RSCLK, RSTAT[1:0])                       | 375 |

| Table 46 | Output Status Timing (TSCLK, TSTAT[1:0])                      | 375 |

| Table 47 | Input Status Timing (RSCLK, RSTAT[1:0])                       |     |

| Table 48 | System Miscellaneous Timing                                   |     |

| Table 49 | XSBI Interface Timing                                         | 378 |

| Table 50 | JTAG Port Interface                                           | 379 |

| Table 51 | MDC / MDIO Interface Timing                                   | 380 |

| Table 52 | Outside Plant Thermal Information                             | 381 |

| Table 53 | Device Compact Model <sup>3</sup>                             | 381 |

| Table 54 | Heat Sink Requirements                                        | 381 |

| Table 55 | Power Consumption                                             | 382 |

| Table 56 | Ordering Information                                          | 386 |

## 1 Definitions

Table 1 S/UNI-1x10GE Abbreviations

| PL4                 | Short hand notation for POS-PHY Level 4 System Interface                                                                                                                                                                           |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PL4IDU              | PL4 Input Data Unpacker                                                                                                                                                                                                            |

| PL4ODP              | PL4 Output Data Packer                                                                                                                                                                                                             |

| PL4IO               | PL4 Input and Output Interface                                                                                                                                                                                                     |

| PL4 Input           | POS-PHY Level 4 Input Interface: relates to data impressed on TDCLK+/- and TDAT[15:0]+/- pins.                                                                                                                                     |

| PL4 Output          | POS-PHY Level 4 Output Interface: relates to data impressed on RDCLK+/- and RDAT[15:0]+/- pins.                                                                                                                                    |

| PL4MOS              | PL4 Multi-stream Output Scheduler                                                                                                                                                                                                  |

| EFLX                | Egress FIFO                                                                                                                                                                                                                        |

| IFLX                | Ingress FIFO                                                                                                                                                                                                                       |

| TXXG                | 10 Gbit/s Transmit MAC                                                                                                                                                                                                             |

| RXXG                | 10 Gbit/s Receive MAC                                                                                                                                                                                                              |

| R64B66B             | 10.3 Gbit/s Receive PCS                                                                                                                                                                                                            |

| T64B66B             | 10.3 Gbit/s Transmit PCS                                                                                                                                                                                                           |

| XSBI                | 10.3 Gbit/s Serial Interface                                                                                                                                                                                                       |

| PHY                 | Physical layer interface                                                                                                                                                                                                           |

| LAN PHY             | Designated by IEEE 10gigabit Ethernet standards committee as one of two variants of the 10GE standard intended for applications in which SONET compatibility is not required and data rates should be maximized.                   |

| Data Frame or Frame | Consist of Destination Address, Source Address, Length Field, Logical Link Control (LLC) Data, PAD, and Frame Check Sequence.                                                                                                      |

| Full Duplex         | A mode of operation that supports simultaneous communication between a pair of stations, provided that the Physical Layer is capable of supporting simultaneous transmission and reception without interference.                   |

| IPG                 | Inter-Packet Gap (IPG): A delay or time gap between physical packets.                                                                                                                                                              |

| MIB                 | Management Information Base (MIB): A repository of information to describe the operation of specific network device.                                                                                                               |

| MAC                 | Media Access Control (MAC): The data link sub-layer that is responsible for transferring data to and from the Physical Layer.                                                                                                      |

| Packet              | The logical unit of data transferred across the POS-PHY Level 3 interface. This generally corresponds to the Data Frame as defined previously, although the CRC may or may not be present in the POS-PHY Level 3 egress direction. |

| Physical Packet     | Consists of a Data Frame as defined previously, preceded by the Preamble and the Start Frame Delimiter, encoded, as appropriate, for the Physical Layer (PHY) type.                                                                |

| POS-PHY             | SATURN compatible Packet over SONET interface specification for physical layer devices. POS-PHY level 4 defines an interface for bit rates up to and including 10Gbit/s.                                                           |

| SOF                 | Start of Frame.                                                                                                                                                                                                                    |

| SOP                 | Start of Packet.                                                                                                                                                                                                                   |

| EOF                 | End of Frame.                                                                                                                                                                                                                      |

| EOP         | End of Packet.                                                                                                                                                                                                          |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jumbo Frame | In the context of this document, Jumbo Frame refers to a data frame (see definition in this table) that has a frame size in number of octets that meets all of the following criteria:                                  |

|             | 1. It is greater than the maximum 802.3 standard specified frame length (1518 octets for untagged frames and 1522 octets for tagged frames)                                                                             |

|             | 2. It is less than or equal to the maximum configurable receive/transmit frame size (for receive, see RXXG register 2045H, Receive Max Frame Length; for transmit, see TXXG register 3045H, Transmit Max Frame Length). |

|             | 3. The frame length is less than or equal to 9600 octets                                                                                                                                                                |

|             | Other than the number of octets in the data frame, a Jumbo Frame otherwise meets all the requirements as outlined in the 802.3 Ethernet standard.                                                                       |

| PRBS        | Pseudo Random Bit Sequencing                                                                                                                                                                                            |

#### 2 Features

#### 2.1 General

- Implements 10 Gigabit Ethernet LAN PHY according to IEEE 802.3ae standard.

- Provides direct connection to optics via a 16-bit by 644.53125MHz IEEE 802.3ae XSBI line-side interface.

- Provides standard IEEE 802.3ae 10 Gigabit Ethernet Media Access Controller (10GMAC) for frame verification.

- Implements IEEE 802.3ae standard 64B/66B Physical Coding Sub-layer (PCS).

- Provides IEEE 802.3ae standard square wave and pseudo-random test pattern generation and checking.

- Provides SATURN® POS-PHY Level 4<sup>™</sup> 16-bit LVDS System Interface for 10 Gigabit Ethernet applications.

- Line-side and System side loopback for system level diagnostic capability.

- Internal 128 Kbyte ingress FIFO and 16kbyte egress FIFO to accommodate system latencies.

- Provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

- Provides a generic 16-bit microprocessor bus interface for configuration, control, and status monitoring.

- Low power 1.8V CMOS core logic with 3.3V CMOS/TTL compatible digital inputs and digital outputs.

- Industrial temperature range (-40C to +85C) Ambient.

- 896 pin FCBGA package.

## 2.2 10 Gigabit Ethernet MAC

- Provides an IEEE 802.3ae standard10 Gigabit MAC for Ethernet frame handling.

- Provides mapping to insert/extract Ethernet frames into/from the IEEE 802.3ae standard Physical Coding Sub-layer (PCS).

- Verifies frame integrity (FCS and length checks).

- Supports 64B/66B-based frame delineation.

- Supports Ethernet 2.0, IEEE 802.3 LLC and IEEE 802.3 SNAP/LLC encoding formats including VLAN tagged frames.

- In the receive direction, supports frame delineation, frame integrity (FCS and length) checks, frame filtering and passing based on erred frames, 64 byte minimum frame size and a 9600 byte maximum frame size.

- Supports address filtering on all standard Ethernet size frames up to 9.6k Bytes.

- In the transmit direction, supports frame generation (preamble, CRC), minimum frame size padding up to 64 bytes, truncation of over-length frames.

- Supports multicast and unicast address filtering using eight exact match filters and promiscuous mode. Frames can be filtered based on SA, SA/VID, DA, or DA/VID. Provides 64-bin hash based algorithm to filter multi-cast addresses.

- With in-band PAUSE flow control the PM3392 implements 3 Km lossless flow control for 9600 byte frames and 5 Km lossless flow control for 1518 byte frames.

- Provides support for out-of-band flow control for upper layer device by using dedicated pins or host signaling to cause generation of a PAUSE frame.

#### 2.3 Statistics

- Provides statistic counters to support

- o Ethernet MIB IEEE 802.3-2000, Clause 30 and 802.3ae

- o Compatible SNMP Interface Group MIB, RFC 1213 MIB II & RFC 2233 SMIv2

- o RMON Statistics Group MIB, RFC 1757

- o Ethernet-like MIB, RFC 2665

- Provides 40-bit wide counters for statistics

#### 2.4 POS-PHY Level 4 Interface

- Designed to transmit cells, packets, or frames between physical and data-link layer devices.

- Compliant with the following standards:

- o ATM Forum Frame Based ATM Interface Level 4 (ATMF0161.00)

- o Optical Internetworking Forum System Physical Interface Level 4 Phase II (OIF2000.088)

## 3 Applications

- Metro POP (Point of Presence)

- Uplink Cards

- IP POP Router

- IP Services

- Multi-Service Switch

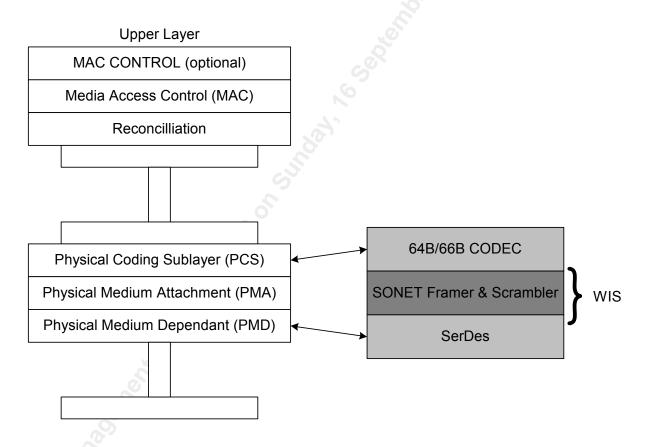

Figure 1 10 Gigabit Ethernet Reference Model

#### 4 References

- 1. OIF OIF99.102, "Proposal for a common electrical interface between SONET framers and SONET Serializer / Deserializer parts for STS-192/STM-64 interfaces." July 1999.

- 2. OIF OIF00.026.0, "SPI-4 Phase II." baseline text.

- 3. PMC-991635, "POS PHY Level 4, Saturn Interface Specification For Packet and Cell Transfer Between Physical Layer and Link Layer Devices for OC-192 SONET/SDH and 10 Gbit/s Ethernet Applications", Issue 4, April 2000.

- 4. IEEE 802.3aestandard; Media Access Control (MAC) Parameters, Physical Layer, and Management Parameters for 10 Gbit/s Operation

- 5. IEEE Std. 802.3, 2000 Edition; Carrier sense multiple access with collision detection (CSMA/CD) access method and physical layer specification

- 6. RFC 1757 Remote Network Monitoring Management Information Base

- 7. RFC 1213 Management Information Base for Network Management of TCP/IP-based internets: MIB-II

- 8. RFC 2233 The Interfaces Group MIB using SMIv2

- 9. RFC 2665 Definitions of Managed Objects for the Ethernet-like Interface Types

- 10. PMC-Sierra, Inc, PMC-2010502 POS-PHY Level 4 Frequently Asked Questions

- 11. PMC-Sierra, Inc., "POS-PHY Level 4 Static Alignment Design Considerations Application Note", Issue 1, March 2001

- 12. PMC-Sierra, Inc., PMC-2010198 "PMC PL4 Compliance Statement", Issue 1, February 2001

- 13. PMC-Sierra, Inc., PMC-2001305 "POS-PHY Level 4 Clocking and Initialization Application Note", Issue 1, November 2000

- PMC-Sierra, Inc., PMC-2020518 "PL4 Electrical Spec Clarifications Application Note", Issue 1, March 2002

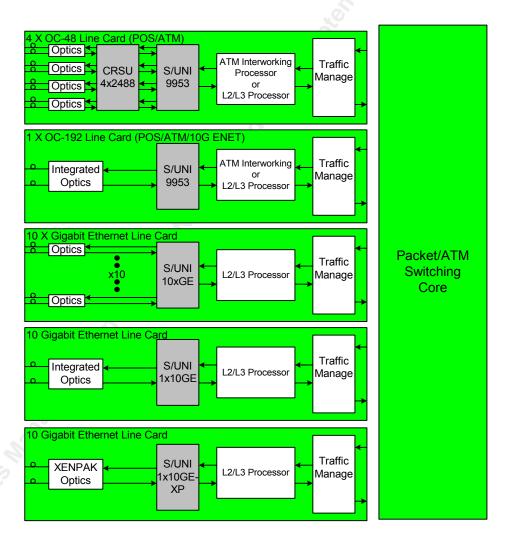

## 5 Application Examples

The PM3392 S/UNI®-1x10GE device is applicable to equipment implementing 10-Gigabit Ethernet LAN PHY interfaces. The S/UNI-1x10GE provides physical layer and MAC layer termination for connections between Edge, Enterprise Edge, and Core routers, Multi Service Switches and transport equipment at the 10 Gigabit rates. One of the most likely locations for initial deployment of 10GE LAN PHY is within the super-POP. Router to router connections is expected to be early adopters of 10GE LAN connections. Server farm connections will also provide a potential application for 10GE. It is also expected that 10GE WAN PHY will find application in connecting POPs to SONET or DWDM transport equipment.

Figure 2 Router - 10G Port Capable

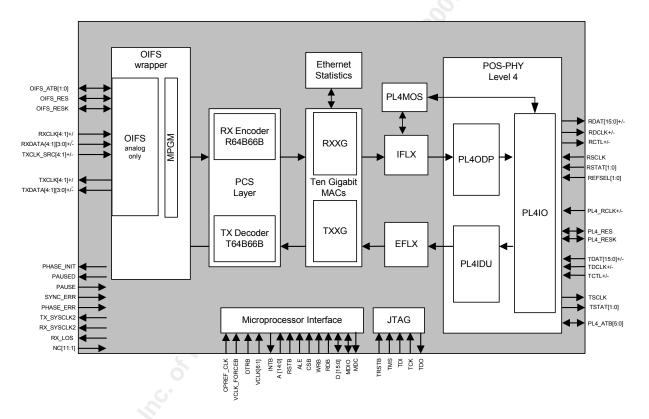

## 6 Block Diagram

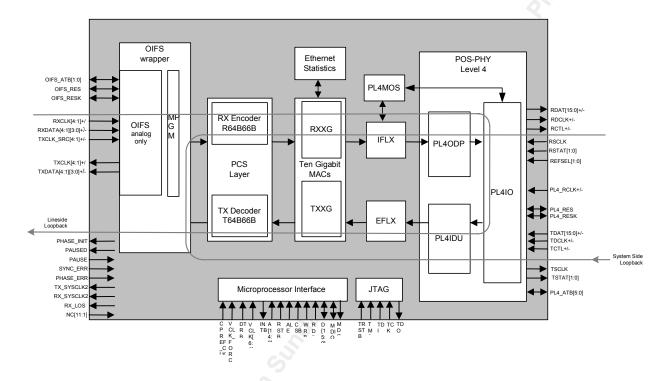

The following block diagrams give a high level view of the PM3392 S/UNI-1x10GE. The first depicts the device in normal mode exploiting all major paths. The second shows two distinct loop-back paths, system side and line side.

Figure 3 Normal Mode

Figure 3 gives a high-level block view of the SUNI-1x10GE. All major data paths are shown with the appropriate signaling interfaces.

Figure 4 Loopback Paths

Figure 4 shows 2 possible loopback paths that are supported in the PM3392. The device supports both system side loopback through the XSBI wrapper, line side loopback through the PL4IO and system side loopback through the PL4IO.

## 7 Description

The PM3392 S/UNI-1x10GE SATURN User Network Interface is a monolithic integrated circuit that implements all the required functions of a 10 Gigabit IEEE 802.3ae standard compatible Ethernet LAN physical layer device (LAN PHY). The S/UNI-1x10GE Ethernet PHY device consists of a Ten Gigabit Sixteen-Bit Interface (XSBI) block, a 64B66B based physical coding sub-layer, a 10-Gigabit MAC, and a POS-PHY Level 4 interface.

The S/UNI-1x10GE transmits and receives Ethernet packets via connections to an optical module. The XSBI block accomplishes the interface bus between the optical module and the PM3392. The XSBI is derived from the OIF99.102.5 SFI-4 specification. The XSBI bus uses Low Voltage Differential Signaling (LVDS) for both clock and data receiver/transmitters. Sixteen pairs of LVDS data signals are provided in the transmit channel and another sixteen pairs in the receive channel. The source clock for the data receivers is RXCLK+/- and is used for the internal reference. In the transmit direction, a single reference clock, TXCLK\_SRC+/- is provided for the 16 data channels. The source LVDS clock that is transmitted aligned with the data. The LVDS reference clock TXCLK\_SRC, an input to the PM3392, is provided by the SERDES to the XSBI as a reference clock for the PCS layer, the MAC, and the Transmit Framer functionality. When the clock rate is 644.53125MHz, an aggregate of 10320Mbit/s (16x644.53125Mbit/s) is transferred in each direction.

The S/UNI 1x10GE TXXG block processes all outgoing Ethernet frames and performs the MAC functionality on the egress path. The TXXG provides Ethernet framing, insertion of an 8-byte preamble/Start Frame Delimiter sequence, plus computation and optional insertion of a 32-bit FCS. Frame timing is provided relative to the system clock reference input. The Transmit Framer will insert the correct programmable inter-frame gap between frames to ensure that the LAN-mode operation conforms to the IEEE 802.3 specification. The inter-frame gap, preamble, FCS generation, and error checking features of the Transmit Framer can be configured by means of internal configuration registers accessible via a microprocessor interface. It provides PAUSE frame generation and insertion. The PM3392 also supports an external "PAUSE" pin so that the system can force the MAC to send pause frames. Generated PAUSE frames are multiplexed into the outgoing frame stream in between data frames, with the proper spacing.

The S/UNI 1x10GE RXXG block processes all incoming Ethernet packet streams while performing basic frame checks. The MAC provides Ethernet framing detection, framing to the standard preamble/SFD sequence, removal of the preamble/SFD, checking of the 32-bit CRC field and frame validation (marking of erred frames for discard). Frame timing checks are relative to the receive input reference clock. The RXXG will verify that the inter-frame gap does not fall below a pre-set minimum and will filter frames that violate this restriction when used in LAN-mode devices. Optional received frame filtering allows frames to be discarded if they are found to contain length or CRC errors. The RXXG implements a 2048-byte full-frame buffer to facilitate this filtering. Jumbo frames that are erred will not be filtered but marked as an error and passed on. Jumbo frames will however, be address filtered.

The RXXG supplies received frame stream parsing and PAUSE MAC Control frame detection, validation and extraction. The PAUSE Timer fields of received PAUSE frames are extracted and sent to flow control logic. If enabled the flow control logic will pause data frames from begin transmitted onto the XSBI interface and assert the external "PAUSED" pin for use by the system. When the PAUSED pin is asserted this means that the TXXG is in a PAUSED state and is no longer transmitting data frames. The RXXG checks every received frame against the IEEE 802.3 frame error criteria and updates the appropriate statistics counters, which can be used to implement the standard Ethernet MIB for link management. Configuration and status maintenance, the minimum IFG, maximum frame size, preamble checking and erred frame discard functions, can be configured by means of internal configuration registers. Status registers are also implemented by the RXXG to permit a host CPU to monitor its functions. The frame check sequence is optionally verified for correctness and the extracted packets are placed in a receive FIFO. A full suite of Ethernet statistics are counted and provided for performance monitoring.

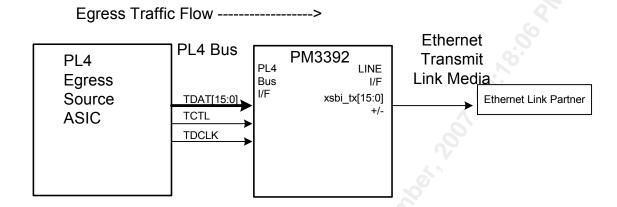

The PL4 interface provides a 16-bit wide data bus, an in-band control stream, a single control signal, and a dual phase source synchronous clock in the forward path. All forward path signals are differential LVDS. The clock signal is either loop timed from the TDCLK+/- or internally generated using the PL4\_RCLK+/- reference input. The control signal is used to identify the inband control words. In the return path, the PL4 interface provides a two-bit FIFO status bus with associated clock. These status signals are provided to the PL4MOS block to allow it to make scheduling decisions. In the case of the PM3392, decisions are limited to releasing data based on credit information. In addition, the Receive PL4 interface allows for the transmission of a training sequence to allow for dynamic de-skewing by a sink entity. Data must contain a sufficient training pattern density to allow reliable operation of the data recovery and deskewing units. The PL4 interfaces transfer un-encoded NRZ data streams. Consequently there may be arbitrarily long runs of consecutive zeros or ones. The Transmit PL4 interface is capable of properly recovering data once training has completed.

The Receive PL4 Interface implements the PL4 protocol as described in PMC-991635. The PL4 interface consists of a PHY interface (PL4IO), Output Data Packer (PL4ODP), Input Data Packer (PL4IDU), and Multi-stream Output Scheduler (PL4MOS). The PL4ODP encapsulates the outgoing data stream originating at the IFLX FIFO interface. The PL4IDU unpacks the incoming PL4 data stream and presents the framed data to the EFLX FIFO. The PL4MOS is used to generate transfer requests to the ingress FIFO using a credit based scheduling scheme.

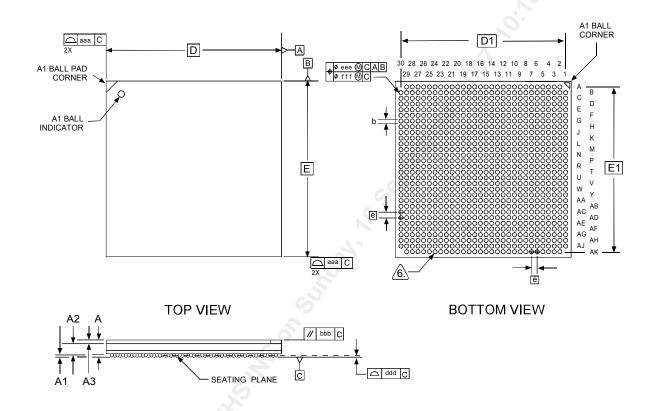

# 8 Pin Diagram

The PM3392 is packaged in an 896 Flip Chip Ball Grid array package. The body size is 31mm by 31mm with a 1.0mm ball pitch.

Figure 5 Ball View 1

|    |             |             |             |             |             |            |           |            |            |            | _  |

|----|-------------|-------------|-------------|-------------|-------------|------------|-----------|------------|------------|------------|----|

|    | 30          | 29          | 28          | 27          | 26          | 25         | 24        | 23         | 22         | 21         |    |

| Α  |             | VDDI        | TDAT_N[1]   | TDAT_N[4]   | TDCLK_N     | TDAT_N[9]  | vss       | VDDO       | TDAT_N[14] | TDAT_N[15] | Α  |

| В  | VDDI        | VDDI        | vss         | TDAT_P[1]   | TDAT_P[4]   | TDCLK_P    | TDAT_P[9] | VDDO       | VSS        | TDAT_P[14] | В  |

| O  | PL4_AVDH[2] | vss         | vss         | VDDO        | TDAT_N[0]   | TDAT_N[5]  | TDAT_N[8] | TDAT_N[12] | vss        | VDDO       | С  |

| D  | PL4_ATB[3]  | PL4_AVDH[1] | VDDO        | VDDO        | vss         | TDAT_P[0]  | TDAT_P[5] | TDAT_P[8]  | TDAT_P[12] | VDDO       | D  |

| ш  | PL4_RESK    | PL4_ATB[1]  | PL4_AVDL[3] | vss         | VSS         | VDDI       | TDAT_N[3] | TDAT_N[6]  | TDAT_N[10] | TDAT_N[11] | Е  |

| Ŀ  | RDAT_P[0]   | PL4_RES     | PL4_AVDL[2] | PL4_AVDH[0] | VDDI        | VDDI       | vss       | TDAT_P[3]  | TDAT_P[6]  | TDAT_P[10] | F  |

| G  | vss         | RDAT_N[0]   | PL4_ATB[0]  | PL4_AVDL[1] | PL4_RCLK_P  | vss        | vss       | VDDI       | TDAT_N[2]  | TDAT_N[7]  | G  |

| I  | VDDO        | VDDO        | RDAT_P[1]   | PL4_ATB[2]  | PL4_ATB[5]  | PL4_RCLK_N | VDDI      | VDDI       | VSS        | TDAT_P[2]  | Н  |

| 7  | RDAT_P[3]   | vss         | vss         | RDAT_N[1]   | PL4_AVDH[3] | PL4_ATB[4] | vss       | VSS        | vss        | VDDI       | J  |

| K  | RDAT_P[6]   | RDAT_N[3]   | VDDO        | VDDO        | RDAT_P[2]   | vss        | VDDO      | VDDO       | VDDI       | VDDI       | К  |

| L  | RDAT_P[7]   | RDAT_N[6]   | RDAT_P[4]   | vss         | vss         | RDAT_N[2]  | vss       | VSS        | VDDI       | vss        | L  |

| М  | RDAT_P[8]   | RDAT_N[7]   | RDCLK_P     | RDAT_N[4]   | VDDO        | VDDO       | VDDI      | VDDI       | VDDI       | VDDI       | М  |

| N  | VDDI        | RDAT_N[8]   | RDAT_P[9]   | RDCLK_N     | RDAT_P[5]   | vss        | VSS       | VSS        | VDDO       | VDDI       | N  |

| Р  | vss         | vss         | RDAT_P[10]  | RDAT_N[9]   | RDAT_P[11]  | RDAT_N[5]  | VDDO      | VDDO       | VDDO       | VDDO       | Р  |

| R  | VDDO        | VDDO        | VDDI        | RDAT_N[10]  | vss         | RDAT_N[11] | VSS       | vss        | vss        | VDDO       | R  |

| Т  | VDDO        | VDDI        | VDDI        | RDAT_N[13]  | vss         | REFSEL[0]  | VSS       | VSS        | VSS        | VDDO       | Т  |

| U  | vss         | vss         | RDAT_P[13]  | RDAT_N[14]  | REFSEL[1]   | vss        | VDDO      | VDDO       | VDDO       | VDDO       | U  |

| ٧  | VDDI        | RDAT_N[12]  | RDAT_P[14]  | NC5         | vss         | vss        | VSS       | VSS        | VDDO       | VDDI       | ٧  |

| w  | RDAT_P[12]  | RDAT_N[15]  | NC6         | RSTAT[1]    | VDDO        | VDDO       | VDDI      | VDDI       | VDDI       | VDDI       | w  |

| Y  | RDAT_P[15]  | RCTL_N      | RSTAT[0]    | vss         | vss         | vss        | VSS       | VSS        | VDDI       | VSS        | Υ  |

| AA | RCTL_P      | PAUSE       | VDDO        | VDDO        | VDDI        | VDDI       | VDDO      | VDDO       | VDDI       | VDDI       | AA |

| AB | RSCLK       | vss         | vss         | vss         | vss         | vss        | VSS       | VSS        | VSS        | VDDI       | AB |

| AC | VDDO        | VDDO        | VDDI        | VDDI        | VDDO        | VDDO       | VDDI      | VDDI       | vss        | VDDI       | AC |

| AD | vss         | NC8         | vss         | vss         | vss         | vss        | vss       | VDDI       | vss        | vss        | AD |

| ΑE | NC7         | NC10        | VDDO        | VDDO        | VDDI        | VDDI       | vss       | VDDO       | VDDO       | vss        | ΑE |

| AF | NC9         | vss         | vss         | vss         | vss         | VDDI       | vss       | VSS        | VDDO       | VSS        | AF |

| AG | VDDO        | VDDO        | VDDO        | VDDO        | vss         | VDDI       | VDDI      | VSS        | VDDO       | VDDO       | AG |

| АН | vss         | vss         | VSS         | VDDO        | VSS         | vss        | VDDI      | vss        | vss        | VDDO       | АН |

| AJ | VDDI        | VDDI        | VSS         | VDDO        | VDDO        | vss        | VDDO      | VDDO       | vss        | VDDI       | AJ |

| AK |             | VDDI        | vss         | vss         | VDDO        | VSS        | vss       | VDDO       | vss        | VDDI       | AK |

|    | 30          | 29          | 28          | 27          | 26          | 25         | 24        | 23         | 22         | 21         | Г  |

Figure 6 Ball View 2

Figure 7 Ball View 3

|   | 10    | 9     | 8     | 7     | 6          | 5           | 4        | 3          | 2            | 1            |   |

|---|-------|-------|-------|-------|------------|-------------|----------|------------|--------------|--------------|---|

| А | D[7]  | D[13] | VDDO  | vss   | TMS        | VCLK4       | RX_LOS   | PHASE_INIT | VDDI         |              | А |

| В | D[10] | VSS   | VDDO  | TRSTB | VCLK3      | VCLK_FORCEB | SYNC_ERR | vss        | VDDI         | VDDI         | В |

| С | VDDO  | vss   | TDI   | D[12] | VCLK5      | RX_SYSCLK2  | VDDO     | VSS        | VSS          | TXDATA4_P[3] | С |

| D | VDDO  | TCK   | VCLK1 | VCLK6 | TX_SYSCLK2 | vss         | VDDO     | VDDO       | TXDATA4_N[3] | TXDATA4_P[1] | D |

| F  | TDO       | NC3    | NC1          | CPREF_CLK    | VDDI         | VSS          | VSS          | OIFS_RES     | TXDATA4_N[1] | TXDATA3_P[2] | E  |

|----|-----------|--------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|----|

| _  |           |        |              | _            |              | VDDI         |              | _            |              |              |    |

|    |           | NC2    |              | VSS          |              |              | OIFS_RESK    |              | TXDATA3_N[2] | TXCLK_SRC4_N |    |

| G  | D[14]     | PAUSED | VDDI         | VSS          | VSS          | TXDATA4_P[2] | TXCLK4_N     | TXDATA4_P[0] | TXCLK_SRC4_P | VSS          | G  |

| Н  | PHASE_ERR | VSS    | VDDI         | VDDI         | TXDATA4_N[2] | VSS          | TXDATA4_N[0] | TXCLK2_P     | VDDO         | VDDO         | Н  |

| J  | VDDI      | vss    | vss          | vss          | vss          | TXDATA3_P[3] | TXCLK2_N     | vss          | vss          | TXCLK3_P     | J  |

| К  | VDDI      | VDDI   | vss          | AVDHVREF     | TXDATA3_N[3] | TXDATA3_P[1] | VDDO         | VDDO         | TXCLK3_N     | TXDATA3_P[0] | ĸ  |

| L  | VSS       | VDDI   | VSS          | VSS          | TXDATA3_N[1] | vss          | VSS          | TXCLK_SRC3_N | TXDATA3_N[0] | TXDATA2_P[3] | L  |

| М  | VDDI      | VDDI   | vss          | VSS          | VDDO         | VDDO         | TXCLK_SRC3_P | TXDATA2_P[2] | TXDATA2_N[3] | TXCLK_SRC2_N | М  |

| N  | VDDI      | VDDO   | vss          | VSS          | VSS          | TXCLK1_P     | TXDATA2_N[2] | TXDATA2_P[1] | TXCLK_SRC2_P | VDDI         | N  |

| Р  | VDDO      | VDDO   | VDDO         | VDDO         | TXCLK1_N     | TXDATA2_P[0] | TXDATA2_N[1] | TXDATA1_P[3] | vss          | vss          | Р  |

| R  | VDDO      | VSS    | vss          | VSS          | TXDATA2_N[0] | TXCLK_SRC1_P | TXDATA1_N[3] | VDDI         | VDDI         | VDDO         | R  |

| Т  | VDDO      | VSS    | VSS          | vss          | TXDATA1_N[2] | TXCLK_SRC1_N | TXDATA1_N[1] | VDDI         | VDDO         | VDDO         | Т  |

| U  | VDDO      | VDDO   | VDDO         | VDDO         | TXDATA1_N[0] | TXDATA1_P[2] | OIFS_ATB[1]  | TXDATA1_P[1] | vss          | vss          | U  |

| V  | VDDI      | VDDO   | RXDATA3_P[0] | VSS          | VSS          | TXDATA1_P[0] | RXDATA4_P[1] | OIFS_ATB[0]  | RXDATA4_P[3] | VDDI         | V  |

| w  | VDDI      | VDDI   | RXDATA3_P[1] | RXDATA3_N[0] | VDDO         | VDDO         | RXDATA3_P[3] | RXDATA4_N[1] | RXDATA4_P[0] | RXDATA4_N[3] | W  |

| Υ  | VSS       | VDDI   | VSS          | RXDATA3_N[1] | RXDATA3_P[2] | vss          | vss          | RXDATA3_N[3] | RXDATA4_P[2] | RXDATA4_N[0] | Y  |

| AA | VDDI      | VDDI   | vss          | VSS          | RXCLK3_P     | RXDATA3_N[2] | VDDO         | VDDO         | RXCLK4_P     | RXDATA4_N[2] | AA |

| AB | VDDI      | VSS    | VSS          | VSS          | RXDATA2_P[1] | RXCLK3_N     | RXCLK2_P     | vss          | vss          | RXCLK4_N     | AB |

| AC | VDDI      | VSS    | VDDI         | VDDI         | RXDATA1_P[0] | RXDATA2_N[1] | RXDATA2_P[2] | RXCLK2_N     | VDDO         | VDDO         | AC |

| AD | VSS       | VSS    | VDDI         | VSS          | VSS          | RXDATA1_N[0] | RXCLK1_P     | RXDATA2_N[2] | RXDATA2_P[3] | VSS          | AD |

| ΑE | VSS       | VDDO   | VDDO         | VSS          | VDDI         | VDDI         | RXDATA1_P[2] | RXCLK1_N     | RXDATA2_P[0] | RXDATA2_N[3] | AE |

| AF | VSS       | VDDO   | vss          | VSS          | VDDI         | vss          | VSS          | RXDATA1_N[2] | RXDATA1_P[3] | RXDATA2_N[0] | AF |

| AG | VDDO      | VDDO   | vss          | VDDI         | VDDI         | vss          | VDDO         | VDDO         | RXDATA1_P[1] | RXDATA1_N[3] | AG |

| АН | VDDO      | VSS    | vss          | VDDI         | VSS          | vss          | VDDO         | VSS          | VSS          | RXDATA1_N[1] | АН |

| AJ | VDDI      | VSS    | VDDO         | VDDO         | vss          | VDDO         | VDDO         | vss          | VDDI         | VDDI         | AJ |

| AK | VDDI      | vss    | VDDO         | vss          | vss          | VDDO         | vss          | vss          | VDDI         |              | AK |

# 9 Pin Description

Table 2 S/UNI-1x10GE Line Side Signaling Interface

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Туре                    | Pin<br>No.                                                                                                                                                                                                     | Function                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXCLK2+<br>RXCLK2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Analog<br>LVDS<br>Input | AB4<br>AC3                                                                                                                                                                                                     | Receive Clock 2  RXCLK2 is 644.53125MHz clock. RXCLK2 is used to sample the 16 receive data steams at rising edge. The RXCLK2 pins correspond to PMA_RX_CLK +/- in the IEEE 802.3ae standard                                                        |

| RXCLK4+<br>RXCLK4-<br>RXCLK3+<br>RXCLK3-<br>RXCLK1+<br>RXCLK1-                                                                                                                                                                                                                                                                                                                                                                                                                      | Analog<br>LVDS<br>Input | AA2<br>AB1<br>AA6<br>AB5<br>AD4<br>AE3                                                                                                                                                                         | Receive Clock [4, 3, 1] UNUSED  The UNUSED RXCLK[4,3,1] inputs need to have the Neg (-) pins tied to 3.3v through a 4.7k ohm resistor. The Pos (+) pins must be tied to ground through a zero ohm resistor.                                         |

| RXDATA1[0]+ RXDATA1[0]- RXDATA1[1]+ RXDATA1[1]- RXDATA1[2]+ RXDATA1[2]- RXDATA1[3]- RXDATA2[0]+ RXDATA2[0]- RXDATA2[1]+ RXDATA2[1]- RXDATA2[2]- RXDATA2[2]- RXDATA2[3]- RXDATA2[3]- RXDATA3[0]- RXDATA3[0]- RXDATA3[0]- RXDATA3[1]- RXDATA3[1]- RXDATA3[2]- RXDATA3[2]- RXDATA3[2]- RXDATA3[2]- RXDATA3[2]- RXDATA3[2]- RXDATA4[0]- RXDATA4[0]- RXDATA4[0]- RXDATA4[1]- RXDATA4[1]- RXDATA4[2]- RXDATA4[3]- RXDATA4[3]- RXDATA4[3]- RXDATA4[3]- RXDATA4[3]- RXDATA4[3]- RXDATA4[3]- | Analog<br>LVDS<br>Input | AC6<br>AD5<br>AG2<br>AH1<br>AE4<br>AF3<br>AF2<br>AG1<br>AE2<br>AF1<br>AB6<br>AC5<br>AC4<br>AD3<br>AD2<br>AE1<br>V8<br>W7<br>W8<br>Y7<br>Y6<br>AA5<br>W4<br>Y3<br>W2<br>Y1<br>V4<br>W3<br>Y2<br>AA1<br>V2<br>W1 | The Differential Receive Data (RXDATA) inputs carry the byte-serial 10Gigabit Ethernet stream.  Pin RXDATA1[0] corresponds to rx_data_unit<0> while RXDATA4[3] corresponds to rx_data_unit<15> as described in figure 49-2 of IEEE802.3ae standard. |

| Pin Name                                                 | Туре                     | Pin<br>No.                       | Function                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------|--------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXCLK_SRC2+<br>TXCLK_SRC2-                               | Analog<br>LVDS<br>Input  | N2<br>M1                         | Transmit Source Clock <b>TXCLK_SRC2</b> is a 644.53125MHz reference clock from SERDES. All 16 transmit data streams TXDATAi_j (i=1 to 4 & j=1 to 4) are transmitted with reference to TXCLK_SRC2. The TXCLK_SRC2 pins correspond to PMA_TXCLK_SRC +/- in the IEEE 802.3ae standard. |

| TXCLK_SRC4+<br>TXCLK_SRC4-                               | Analog<br>LVDS           | G2<br>F1                         | Transmit Source Clock <b>TXCLK_SRC[4, 3, 1]</b> UNUSED                                                                                                                                                                                                                              |

| TXCLK_SRC3+<br>TXCLK_SRC3-<br>TXCLK_SRC1+<br>TXCLK_SRC1- | Input                    | M4<br>L3<br>R5<br>T5             | The UNUSED TXCLK_SRC[4,3,1] inputs need to have the Neg (-) pins tied to 3.3v through a 4.7k ohm resistor. The Pos (+) pins must be tied to ground through a zero ohm resistor.                                                                                                     |

|                                                          |                          |                                  | 20                                                                                                                                                                                                                                                                                  |

| TXCLK2+<br>TXCLK2-                                       | Analog<br>LVDS<br>Output | H3<br>J4                         | Transmit Clock <b>TXCLK2</b> is a 644.53125MHz clock to synchronize the transmission of the 16 transmit data streams. The TXCLK2 pins correspond to PMA_TX_CLK +/- in the IEEE 802.3ae standard.                                                                                    |

|                                                          |                          | 80                               | The TXCLK2+/- LVDS outputs are internally terminated by the PM3392.                                                                                                                                                                                                                 |

|                                                          |                          |                                  |                                                                                                                                                                                                                                                                                     |

| TXCLK4+ TXCLK4- TXCLK3+ TXCLK3- TXCLK1+ TXCLK1-          | Analog<br>LVDS<br>Output | F3<br>G4<br>J1<br>K2<br>N5<br>P6 | Transmit Clock <b>TXCLK[4,3,1]</b> are UNUSED. The TXCLK2+/- LVDS outputs are internally terminated by the PM3392.                                                                                                                                                                  |

|                                                          | .59                      |                                  |                                                                                                                                                                                                                                                                                     |

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Туре                       | Pin<br>No.                                                                                                                                                                                   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDATA1[0]+ TXDATA1[0]- TXDATA1[1]+ TXDATA1[1]- TXDATA1[2]+ TXDATA1[2]- TXDATA1[3]- TXDATA1[3]- TXDATA2[0]- TXDATA2[0]- TXDATA2[1]+ TXDATA2[1]- TXDATA2[1]- TXDATA2[2]- TXDATA2[3]- TXDATA2[3]- TXDATA3[0]- TXDATA3[0]- TXDATA3[1]- TXDATA3[1]- TXDATA3[1]- TXDATA3[2]- TXDATA3[2]- TXDATA3[2]- TXDATA3[2]- TXDATA3[2]- TXDATA3[2]- TXDATA3[2]- TXDATA4[1]- TXDATA4[0]- TXDATA4[0]- TXDATA4[1]- TXDATA4[1]- TXDATA4[2]- TXDATA4[2]- TXDATA4[3]- TXDATA4[3]- TXDATA4[3]- TXDATA4[3]- | Analog<br>LVDS<br>Output   | V5<br>U6<br>U3<br>T4<br>U5<br>T6<br>P3<br>R4<br>P5<br>R6<br>N3<br>P4<br>M3<br>N4<br>L1<br>M2<br>K1<br>L2<br>K5<br>L6<br>E1<br>F2<br>J5<br>K6<br>G3<br>H4<br>D1<br>E2<br>G5<br>H6<br>C1<br>D2 | The Differential Transmit Data (TXDATA) outputs carries the byte-serial 10gigabit Ethernet stream.  Pin TXDATA1[0] corresponds to tx_data_unit<0> while TXDATA4[3] corresponds to tx_data_unit<15> as described in figure 49-2 of IEEE802.3ae standard  The TXDATA+/- LVDS outputs are internally terminated by the PM3392.                                                                                                                               |

| PHASE_ERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input<br>CMOS              | H10                                                                                                                                                                                          | The <b>Phase Error</b> (PHASE_ERR) input indicates when the TXCLK2+/- output is not aligned with the corresponding TXDATA+/- bus. When asserted, the receiving line side device cannot use the source synchronous TXCLK2 to sample the TXDATA bus. PHASE_ERR is treated as an asynchronous signal and is used to trigger maskable interrupt. In addition, the associated PHASE_INIT output should be asserted to reinitiate alignment under user control. |