# 1. Features

#### **General Features**

- Low external component count

- No external crystal required

- Technology: CMOS

- P-DSO-20 -1 package

#### **PDC Features**

- Reception of VPS data in line 16 of the vertical blanking interval

- Complete reception of BDSP packet 8/30/1 and packet 8/30/2

- Reception of the complete teletext header row

- 400KHz I<sup>2</sup>C-Bus interface

- Integrated OSD Module

#### **OSD Features**

- Display structure: 14 rows x 32 characters

12 rows x 30 characters (27 characters in visible frame area)

- 128 ROM characters (12 Pixel \* 18 Lines)

- Fringing

- Display start position programmable in horizontal and vertical direction

- Insertion of OSDs in the CVBS signal (Black and white)

- Colored full screen OSD mode

- Integrated Sync-Separator

- Integrated SECAM switch

- Analog CVBS Output

- 8 programmable background colors (via Look Up Table)

- Programmable flashing frequency (1.5Hz, 1 Hz or 0.5 Hz)

- Cursor

- Four size settings in vertical and horizontal directions

# 2. Order Information

| Туре        | Package          | Ordering Code |

|-------------|------------------|---------------|

| SDA 5652-2X | P - DSO - 20 - 1 |               |

# 3. General Description

The PDC/OSD SDA 5652-2X decoder chip receives all VPS and 8/30 Format 1 and 2 data together with the teletext header information for easy identification of the broadcaster. In addition to the well known PDC/VPS decoder an OSD module with an YUV to CVBS encoder is integrated. The OSD can be synchronized to an CVBS signal or can generate a complete multistandard (PAL/NTSC, 50Hz/60Hz frame rate) CVBS signal with a full screen colored OSD.

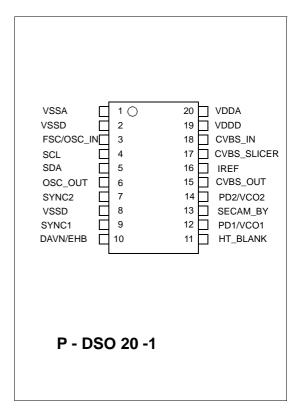

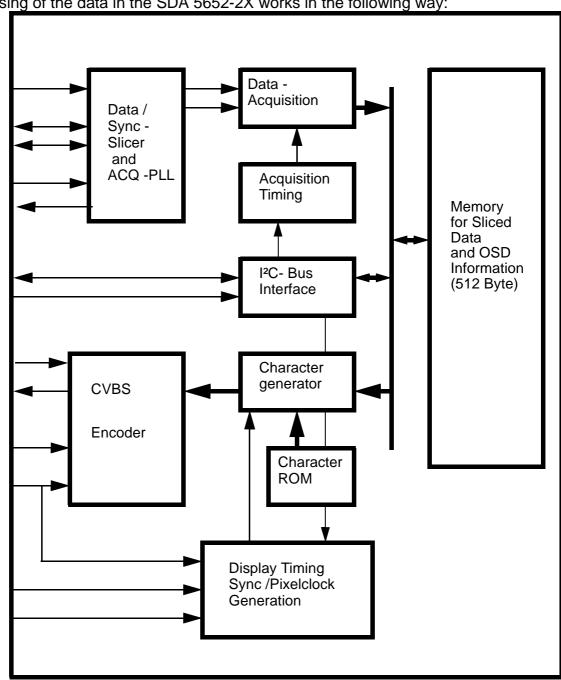

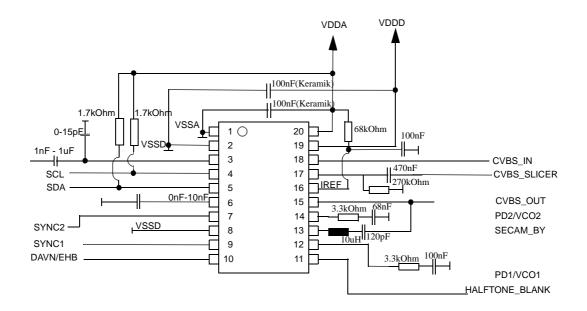

# 4. Pin Configurations

# 5. Pin Definitions and Functions

| Pin. No.<br>P-DSO-20      | Symbol           | Function                                                                                                                                                                                                       |

|---------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                         | V <sub>SSA</sub> | Analog ground (0 V)                                                                                                                                                                                            |

| 2                         | V <sub>SSD</sub> | Digital ground (0 V)                                                                                                                                                                                           |

| 3REF                      | FSC/OSC_IN       | Color Carrier Clock                                                                                                                                                                                            |

| 4                         | SCL              | Serial clock input of I <sup>2</sup> C-Bus.                                                                                                                                                                    |

| <sub>5</sub> PD2/VCO2     | SDA              | Serial data input of I <sup>2</sup> C-Bus.                                                                                                                                                                     |

| PD1/VCO1                  | OSC_OUT          | Optional oscillator for 2FSC                                                                                                                                                                                   |

| 7<br>CVBS_SLI<br>DAVN/EHB | SYNC2            | Vertical Sync/Vertical Composite Sync (Depending on I <sup>2</sup> C Bus definition it can be switched to either Input or Output. When it is switched as an input, analog or digital signals can be processed) |

| 8                         | V <sub>SSD</sub> | internal used; should be connected to GND                                                                                                                                                                      |

| 9<br>SDA                  | SYNC1            | Vertical/Horizontal Sync (Depending on I <sup>2</sup> C Bus definition it can be switched to either digital input or output)                                                                                   |

| 1 <b>3</b> CL             | DAVN/EHB         | output of the signals DAVN/EHB coming from the VPS/PDC-circuit.                                                                                                                                                |

| 11                        | HALFTONE_BLANK   | Output-Pin for Halftone-Blanking. Goes to high for halftone-blanked video-areas, low for non-halftoneblanked areas                                                                                             |

| CVBS_IN                   | PD1/VCO1         | Connector of the loop filter for the SYSPLL.                                                                                                                                                                   |

| 1êvbs_out                 | SECAM_BY         | Input for Secam bypass.                                                                                                                                                                                        |

| 14                        | PD2/VCO2         | Connector of the loop filter for the DAPLL.                                                                                                                                                                    |

| 15                        | CVBS_OUT         | Composite video signal output from the OSD path.                                                                                                                                                               |

| 18ECAM_BY                 | I REF            | Reference current input for the on-chip analog circuit.                                                                                                                                                        |

| 17<br>FSC                 | CVBS _SLICER     | Composite video signal input for the data slicer. The source of this signal must be the same as the source for signal at Pin 18.                                                                               |

| 18                        | CVBS_IN          | Composite video signal input for the OSD path. The source of thsi signal must be the same as the source for signal at Pin 17.                                                                                  |

| 19                        | V <sub>DDD</sub> | Positive supply voltage for the digital circuits. (+ 5 V nom.).                                                                                                                                                |

| 28ync1                    | $V_{DDA}$        | Positive supply voltage for the analog circuits (+ 5 V nom.).                                                                                                                                                  |

| Sync2                     |                  |                                                                                                                                                                                                                |

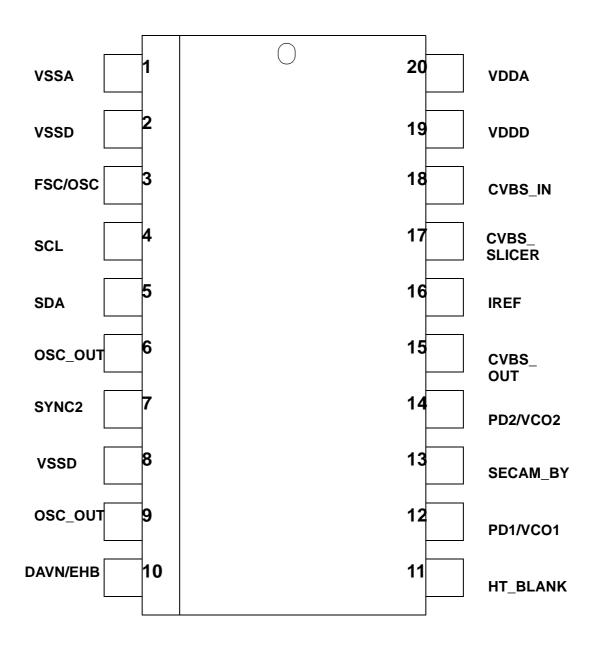

# **6.Block Diagram**

The processing of the data in the SDA 5652-2X works in the following way:

# 7. Circuit Description

# 7.1 VPS/PDC Functions

Referring to the functional block diagram the composite video signal with negative going sync pulses is coupled to the pin CVBS through a capacitor which is used for clamping the bottom of the sync pulses to an internally fixed level. The signal is passed to the slicer, an analogue circuitry separating the sync and the data parts of the CVBS signal, thus yielding the digital composite sync signal VCS and a digital data signal for further processing by comparing those signals to internally generated slicing levels.

The output of this sync separator is forwarded to the acquisition clock generator and the acquisition timing block in which teletext / vps related data-valid-windows are generated.

The data slicer separates the data signal from the CVBS signal by comparing the video voltage to an internally generated slicing level which is found by averaging the data signal during TV line no. 16 in the VPS mode or by averaging the data signal during the clock run-in period of the teletext lines during the data entry window (DEW) in PDC mode.

The acquisition clock generator delivers the system clock needed for the basic timing as well as for the regeneration of the dataclock. It is based on two phase locked loops (PLL's) all parts of which are integrated on chip with the exception of the loop filter components. Each of the PLL's is composed of a voltage controlled relaxation oscillator (VCO), a phase/frequency detector (PFD), and a charge pump which converts the digital output signals of the PFD to an analogue current. That current is transformed to a control voltage for the VCO by the off-chip loop filter. The generated VCO frequencies are 10 MHz and 13.875 MHz for VPS mode and PDC mode, respectively.

All signals necessary for the control of sync and data slicing as well as for the data acquisition are generated by this timing block.

The SDA 5652-2X can be operated in three different modes: Depending on the selected operating mode, either teletext lines carrying 8/30 packages, the dedicated TV line no. 16(VPS) or the teletext header bytes are acquired.

In PDC mode, only teletext rows 8/30 containing Broadcast Data Service Package (BDSP) information are acquired. The relevant bytes of 8/30 format 1 (8/30/1) and 8/30 format 2 (8/30/2) are extracted. The 8/30/1-bytes are stored in the acquisition register in a transparent way without any bit manipulation, whereas the hamming coded bytes of packet 8/30/2 are hamming-checked and bytes with one bit error are corrected.

In TTX header mode all bytes of the headers are stored. Hamming protected bytes are corrected and need not to be processed by the external controller. For the order of the stored bytes see I<sup>2</sup>C bus register description.

A micro controller can read the stored bytes via the I<sup>2</sup>C bus interface at any time.

In order to achieve maximum system performance it is recommended to start the SDA 5652-2X in VPS mode (state after power on) and read the register to check whether line 16 is received. After reception of VPS data in line 16 the SDA 5652-2X can be switched to 8/30

mode and waiting for packet 8/30 data. Since VPS data in line 16 is transmitted every frame and PDC data in packet 8/30 is transmitted nearly every second the recognition of both VPS and 8/30 packets can be done within PDC-system constraints (about 1 sec).

To differ between older (SDA5649/5650) and future (SDA5652-2X/...) PDC versions a special method can be used for chip identification:

SDA5649/5650 PDC-versions are not writeable. First step is, the user chooses a pattern of bytes and writes them to the RAM. Second step is to read these bytes from the RAM. By comparing the written bytes and the read bytes there may be correspondence or not. If there's correspondence the present IC is a new version (SDA5652-2X/...) if there's no correspondence its a older version (SDA5650/5651). In addition further versions (SDA5652-2X/...) could be differed with a special I<sup>2</sup>C-Register.

#### Valid-Data-Recognition:

The PDC/VPS-registers could be read by the external controller.

There is no necessity for the controller reading the PDC/VPS-contents if the register-contents aren't made topical by a new reception. There are three methods to identify if the register-contents are made topical after a previous reading-operation:

#### 1. Data-Set-Valid-Bit

After a new reception is fulfilled the data-set-valid-bit is set from low to high. If data-set-valid-bit is high and a I<sup>2</sup>C-read-operation for a subaddress between 4 and 40 is closed by a stop condition the data-set-valid bit is set from high to low, if during the IIC-Read-operation no new datas are received.

#### 2. DAVN-signal

On Pin10 the signal DAVN (Data Valid active low) will be available. The behaviour of this signal is described as follows:

a) VPS-Mode:

H/L-Transition (set to low): After VPS-data has been received.

L/H-Transition (set to high): At the start of line 16.

b) PDC/HTA/HTB/HTC-Mode:

H/L-Transition (set to high): In the line where valid data is carried. L/H-Transition (set to low): At the beginning of the next field

#### 3. VPS/PDC-register-contents

If a stop-condition is send to the I<sup>2</sup>C-bus-interface after a read-operation has been accessed for the addresses between 4 and 40, all register-contents from 4 to 40 are set to 255 if during the IIC-Read-operation no new datas are received (falling edge of DAVN). A new reception of VPS/PDC-datas during or after the IIC-Read-operation, will overwrite these FFh-contents. As a result a new data-reception could be detected by the register-contents itself.

#### Format of register ACQ\_CONTROL (default values in brackets)

|             | Bit 7 | Bit 6 | Bit 5      | Bit 4         | Bit 3         | Bit 2      | Bit 1              | Bit 0                |

|-------------|-------|-------|------------|---------------|---------------|------------|--------------------|----------------------|

| ACQ_CONTROL | (0)   | (0)   | DSV<br>(0) | MABC_1<br>(0) | MABC_0<br>(0) | HDT<br>(0) | PDC/<br>VPS<br>(0) | FOR1/<br>FOR2<br>(0) |

FOR1/FOR2: Determines which kind of data is stored in the decoder

when PDC mode is active: **0**: BDSP 8/30/2 accessible

1: BDSP 8/30/1 or header row data accessible (refer to de-

scription of bit PDC/VPS

PDC/VPS: 0: VPS mode is active

1: PDC mode is active

ATTENTION: Please refer to Errata-Sheet Item-No. H5 relating to VPS-Mode/Byte13

**HDT:** Determines whether BDSP 8/30/1 data or header row data

is stored.

0: BDSP 8/30/1 accessible

1: Teletext header mode is active. See also bit MAB

MABC\_1...0: 00: Mode A. Header bytes are accessed in order 38 - 45,

30 - 37.

01: Mode B. Header bytes are accessed in order 22 - 29,

14 - 21.

**1X**: Mode C. Header bytes are accessed in linear increasing

order 4-45.

**DSV:** Data set valid

This bit is only read and not writeable. Write-operations

have got no influence to this bit.

Declares when PDC/VPS-register-contents are renewed after a previous read-operation. It is not allowed to read the content of DSV-Bit (Subadr. 03h) and VPS/PDC-data (subadr. 04h - 27h) within one IIC-protocol. In this case DSV is not cleared and the data-registers are not set to FFh reliable.

**0:** Register-contents haven't been renewed up to the moment this bit is read.

**1:** Register-contents are renewed. The datas read out by a new IIC-read-operation from byte 4-40 are completly valid.

# 7.1.1 Format of stored data bytes

Bits are stored in the order of their reception, that means the first transmitted bit is stored in bit 7 of the appropriate I<sup>2</sup>c bus address. In format 2 of packet 8/30 the contents of two transmitted bytes is stored in one I<sup>2</sup>c bus register address. Hamming bits are not stored.

# ATTENTION: Please refer to errata-sheet item-no. H5 relating to VPS-Mode/Byte13 (I<sup>2</sup>C-subaddress 6)

| I <sup>2</sup> C- Subaddress | 4     | 5     | 6     | 7     | 8     | 9     | 10   | 11 | 12 | 13 | 14 | 15 |

|------------------------------|-------|-------|-------|-------|-------|-------|------|----|----|----|----|----|

| 8/30 Format 1                | 15    | 16    | 17    | 18    | 19    | 20    | 21   | 13 | 14 | 22 | 23 | 24 |

| 8/30 Format 2                | 16,17 | 18,19 | 20,21 | 22,23 | 14,15 | 24,25 | 13,x | х  | х  | х  | х  | х  |

| VPS                          | 11    | 12    | 13    | 14    | 5     | 15    | х    | х  | х  | х  | х  | х  |

| НТА                          | 38    | 39    | 40    | 41    | 42    | 43    | 44   | 45 | 30 | 31 | 32 | 33 |

| нтв                          | 22    | 23    | 24    | 25    | 26    | 27    | 28   | 29 | 14 | 15 | 16 | 17 |

| нтс                          | 4,5   | 6,7   | 8,9   | 10,11 | 12,13 | 14    | 15   | 16 | 17 | 18 | 19 | 20 |

| I <sup>2</sup> C- Subaddress | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 |

|------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|

| 8/30 Format 1                | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 |

| 8/30 Format 2                | х  | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 |

| VPS                          | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  |

| НТА                          | 34 | 35 | 36 | 37 | х  | х  | х  | х  | х  | х  | х  | Х  |

| нтв                          | 18 | 19 | 20 | 21 | х  | х  | х  | х  | х  | х  | х  | х  |

| нтс                          | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

| I <sup>2</sup> C- Subaddress | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 |

|------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|

| 8/30 Format 1                | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | х  | х  | х  |

| 8/30 Format 2                | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | х  | х  | х  |

| VPS                          | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  |

| НТА                          | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  |

| нтв                          | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  |

| нтс                          | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 |

| I <sup>2</sup> C- Subaddress | 40 |

|------------------------------|----|

|------------------------------|----|

# **SDA 5652-2X**

| 8/30 Format 1 | х  |

|---------------|----|

| 8/30 Format 2 | х  |

| VPS           | х  |

| НТА           | х  |

| нтв           | х  |

| нтс           | 45 |

# 7.2. OSD Functions

The OSD block consists of a character generator unit which reads out character addresses from the internal RAM and transforms them by the help of a character ROM into pixel information. The OSD memory has a size of 448 Bytes. As a result the display is fixed to a format of 14 rows with 32 characters. For a 50Hz-system 14 rows are displayed, for a 60Hz-system 12 rows. The count of columns can be defined by the user to 30 or 32. For systems using a color-carrier of 4,43MHz 32 characters should be choosen, for systems using a 3,58MHz color-carrier 30 characters should be choosen. So if needed the display-memory-contents from the two columns on the right side or the contents from the two last rows are ignored. Bytes are processed in linear binary increasing order. The display memory is accessed via the dataport. Starting address is  $0_{\rm d}$  (see also 7.3.2. Dataport access). The character structure is 12 pixels in horizontal direction and 18 lines in vertical direction.

| HORIZ<br>ONTAL<br>_SIZE<br>(2Bit) | VERTI-<br>CAL<br>_SIZE<br>(2Bit) | CHAR-<br>attribute_<br>2<br>(2Bit) | CHAR-<br>attribute_<br>1<br>(2Bit) |         | i = 0 |                            | i = 31 |

|-----------------------------------|----------------------------------|------------------------------------|------------------------------------|---------|-------|----------------------------|--------|

|                                   | хх                               | XX                                 | XX                                 | 0 + i   |       |                            | ,      |

|                                   | хх                               | XX                                 | ХХ                                 | 32 + i  | -     |                            |        |

|                                   | хх                               | XX                                 | XX                                 |         |       |                            |        |

|                                   |                                  |                                    |                                    |         |       |                            |        |

|                                   |                                  |                                    |                                    |         |       |                            |        |

|                                   |                                  |                                    |                                    |         |       | Display Memory             |        |

|                                   |                                  |                                    |                                    |         |       | 14 rows with 32 characters |        |

|                                   |                                  |                                    |                                    |         |       |                            |        |

|                                   |                                  |                                    |                                    |         |       |                            |        |

|                                   |                                  |                                    |                                    |         |       |                            |        |

|                                   |                                  |                                    |                                    |         |       |                            |        |

|                                   |                                  |                                    |                                    | 416 + i |       |                            |        |

With the Bits 0 to 6 of the address 128 characters of the character ROM can be addressed. The addresses of the characters are orientated on the wellknown ASCII-table.

Bit 7 of the character address is used to switch between two attribute definitions. These two attribute definitions can be chosen for each row individual. For this choice each row has two character-attribute-registers, CHAR\_attribute\_1 and CHAR\_attribute\_2.

CHAR-attribute\_1 consists of two bit and CHAR-attribute\_2 consists of two bits. One out of four character-definitions can be selected by these two bits. These four character-definitions are made for CHAR-attribute\_1 in the four registers CHAR-definition1\_1...1\_4. For CHAR-attribute\_2 these four definitions are made in CHAR-definition2\_1...2\_4.

The format of the CHAR-definition-Registers and the CHAR-attribute-Registers see below.

# Format of the registers CHAR-definition1\_1...1\_4 and CHAR-definition2\_1...2\_4: (default value in brackets):

|        | Bit 7         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|---------------|--------|--------|--------|--------|--------|--------|--------|

| BYTE 1 | HALF-<br>TONE | BL_1   | BL_0   | HS_1   | HS_0   | BK_0   | BK_1   | INV    |

| BYTE 2 | FCOL_4        | FCOL_3 | FCOL_2 | FCOL_1 | FCOL_0 | BCOL_2 | BCOL_1 | BCOL_0 |

#### HALFTONE:

#### Fullpage-Mode or if Display is turned off:

In Fullpage-Mode or if display is turned off this bit has got no influence. Pin11 is static switched to L-Level.

#### Mixed-Mode:

Switches between Halftone-Blanking on and off. Characters for which halftone-blanking is turned on, pin11 is switched to H-Level during these characters are displayed. Otherwise pin11 is switched to L-Level.

0: Switching Halftone-Blanking off

1: Switching Halftone-Blanking on

HS\_1...0:

Horizontal size per dot as multiples of the pixel clocks. Only used if the row-attribute HORIZONTAL\_SIZE\_SELECT bits are set to 0.

00: 1 pixel clock per dot.

01: 2 pixel clocks per dot.

10: 3 pixel clocks per dot.

11: 4 pixel clocks per dot.

BL 1...0:

Defines the blanking mode of the characters in mixed mode. There's a special fringing-mode. Fringing means, that the character is surrounded by a border. This border has the size of one pixel:

Settings for mixed mode:

**00**: Blanking is switched off. The complete character (border and background) is visible on the screen.

**01**: Background is blanked, only the foreground information

of the character is visible.

**10**: Background is blanked, only the foreground information of the character including the border (fringing) is visible.

**11**: The complete characters are blanked. (The character is not visible)

In full-page-mode no blanking is available. Fringing can be switched with bit BL 1.

Settings for full-page-mode: **0X**: Fringing is switched off **1X**: Fringing is switched on

BK\_1...0:

Defines the flashing mode and period for the appropriate row. When flashing is specified for reversed characters, the flashing will be between normal character and reversed display.

00: Flashing is switched off

**01**: Flashing is switched on. The period is approximately set to 0.5/s

**10**: Flashing is switched on. The period is approximately set to 1.0/s

**11**: Flashing is switched on. The period is approximately set to 1.5/s

**BCOL 2...0:**

**In full-page-mode:** Defines the background color vector. The final color depends on the values of the look up table (see below).

**In mixed-mode:** Defines the background grey-value. The final grey-value depends on the luminancevalue described in the look up table (see below).

FCOL\_4...0:

Defines the foreground grey-value. Up to 23 values between 1,4V and 2,9V in steps of about 68mV can be selected in full-page-mode (The values from 0 to 8 are not allowed because there levels are in the sync-area). Up to 32 values between 1,4V and 2,9V in steps of about 48 mV can be selected in mixed-mode.

INV:

0: Inverting is switched off1: Inverting is switched on

The characters can be zoomed in horizontal and vertical direction. Characters neighboured on the right or below of a zoomed character are overwritten and not shifted.

Each row has two **VERTICAL-SIZE-SELECT** bits in which the size of the characters are defined for the whole row. The size can be zoomed in vertical direction up to factor 4.

Each row has two HORIZONTAL-SIZE-SELECT bits in which the size of the characters can

be defined for the whole row. The size can be zoomed in horizontal direction up to factor 4. If the **HORIZONTAL\_SIZE\_SELECT** bits are set to 0 each character can be zoomed individual by the char\_attributes- and char\_definition-registers.

The HORIZONTAL\_SIZE\_SELECT bits, VERTICAL\_SIZE\_SELECT bits and the CHAR\_attribute\_1..2 bits are stored for each row in the register ROW\_ATTRIBUTE:

#### Format of the register ROW ATTRIBUTE:

|        | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| ROW 1  | HORIZO  | HORIZO  | VERTIC  | VERTIC  | CHAR_AT | CHAR_AT | CHAR_AT | CHAR_AT |

|        | NTAL_SI | NTAL_SI | AL_SIZE | AL_SIZE | TRIBUTE | TRIBUTE | TRIBUTE | TRIBUTE |

|        | ZE/Bit1 | ZE/Bit0 | /Bit1   | /Bit0   | _2/Bit1 | _2/Bit0 | _1/Bit1 | _1/Bit0 |

| ROW 2  | HORIZO  | HORIZO  | VERTIC  | VERTIC  | CHAR_AT | CHAR_AT | CHAR_AT | CHAR_AT |

|        | NTAL_SI | NTAL_SI | AL_SIZE | AL_SIZE | TRIBUTE | TRIBUTE | TRIBUTE | TRIBUTE |

|        | ZE/Bit1 | ZE/Bit0 | /Bit1   | /Bit0   | _2/Bit1 | _2/Bit0 | _1/Bit1 | _1/Bit0 |

|        |         |         |         |         |         |         |         |         |

| ROW 14 | HORIZO  | HORIZO  | VERTIC  | VERTIC  | CHAR_AT | CHAR_AT | CHAR_AT | CHAR_AT |

|        | NTAL_SI | NTAL_SI | AL_SIZE | AL_SIZE | TRIBUTE | TRIBUTE | TRIBUTE | TRIBUTE |

|        | ZE/Bit1 | ZE/Bit0 | /Bit1   | /Bit0   | _2/Bit1 | _2/Bit0 | _1/Bit1 | _1/Bit0 |

ATTENTION: Please refer to errata-sheet item-no. H1, H4 relating to vertical and horizontal zoom

# Format of the registers VERTICAL\_START\_POSITION and HORIZONTAL\_START\_POSITION:

The position of the display can be adjusted in terms of pixels and lines referring to the horizontal and vertical edge of the picture. The position is programmed in the register vertical\_start\_position and horizontal\_start\_position. The line-counter for the vertical-start-position is set to 0 during the negative going flank of V-Sync. The pixel-counter for the horizontal-start-position is set to 0 after the positive going flank of H-Sync (negative flank of VCS).

|                               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| VERTICAL_<br>START_POSITION   | (0)   | VSP_6 | VSP_5 | VSP_4 | VSP_3 | VSP_2 | VSP_1 | VSP_0 |

| HORIZONTAL_<br>START_POSITION | (0)   | HSP_6 | HSP_5 | HSP_4 | HSP_3 | HSP_2 | HSP_1 | HSP_0 |

ATTENTION: Please refer to errata-sheet item-no. H1, H2, H3, H4, H6 relating to horizontal and vertical start-position.

VSP\_6...0:

Vertical start position of the screen. VSP\_6...0 define the shift of the screen in vertical direction as multiples of horizontal lines.

HSP\_6...0:

Horizontal start position of the screen. HSP\_6...0 define the shift of the screen in horizontal direction in pixel clocks.

#### **Clock-Supply**

The pixel clock (2FSC, FSC, 2FSC/3, FSC/2) is derived from the system-clock (4FSC) depending on the horizontal-zoom-factor.

The system-clock(4FSC) is derived from a external frequency. There are two methods to provide these external frequency. One method is to fed in a frequency of 1FSC or 2FSC or 4FSC at Pin3. The second method is to plug a 2FSC-crystal-oscillator to Pin3 and Pin6. Which of these methods is used is defined in the register SYNCHRONISATION.

The pixel clock is internally synchronized to the horizontal- sync information by a discrete phase shifter.

#### **Synchronisation-modes**

The sync information may be delivered as external V/H impulses, as a composite sync signal or is derived from the analog CVBS-signal. In free run mode the timing block can generate its composite sync signal so a stable display can be produced even if no external sync source is available. There are different synchronisation-modes for mixed-mode-OSD. For more information of these modes, see register **SYNCHRONISATION** and the figure on page 22.

For high-end-sync-performance in mixed-mode a internal HPLL can be used for synchronisation.

The HPLL consist of a digital DTO, a digital phase-detector and a loop-filter.

There are different settings for the loop-filter possible. For high-performance we recommend a universal loop-filter-setting. For advanced high-performance there is the possibility to adapt the loop-filter to each customer-specific-VCR in the different replay-modes (Fast-Forward/Fast-Backward-mode, Long-Play/Short-Play).

|      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|------|-------|-------|-------|-------|--------|--------|--------|--------|

| HPLL | (0)   | (0)   | (0)   | (0)   | HPLL_3 | HPLL_2 | HPLL_1 | HPLL_0 |

**HPLL0:** Register to justify the integral filter-component

**0**: 1/128 **1**: 0

**HPLL1:** Register to justify the proportional filter-component

**0**: 1 **1**: 4

**HPLL2..3:** Register to justify the proportional/integral filter-component

**00**: 1/32

01: 1/1610: 1/811: 1/4

#### For universal VCR/Tuner-modes we recommend:

HPLL0: 0 HPLL1: 1 HPLL2: 1 HPLL3: 1

### For high-performance noise-surpress we recommend:

HPLL0: 0 HPLL1: 0 HPLL2: 0 HPLL3: 0

In mixed mode display the signal processing is synchronized to the CVBSin-Signal. For this at Pin7 and Pin9 the H-synchronization and V-synchronization-signals can be fed to the IC. In full-page-mode both pins(Pin7 and Pin9) are working as a output. In this case they deliver H-sync and V-sync-signals. They also can be switched in a highly impedant state.

#### Format of register SYNCHRONISATION (default values in brackets):

|              | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  |

|--------------|-------|--------|--------|--------|---------|--------|--------|--------|

| SYNCHRONISA- | (0)   | SYNC_2 | SYNC_1 | SYNC_0 | IIC_SWI | DISPON | OSC_SY | OSC_SY |

| TION         |       | (1)    | (0)    | (0)    | TCH(1)  | (0)    | S_1(0) | S_0(1) |

**DISPON:**

Switches the CVBS\_in-signal (Pin18) to CVBS\_out-signal(Pin15). This bit has highest priority. Switching it to low, the incoming CVBS-signal is fed through the IC to CVBS output.

0: CVBS in=CVBS out

The two states CVBS\_in=CVBS\_out and D/A=CVBS\_out is controlled by the charactergenerator

IIC\_SWITCH:

After RELEASE-bit has been set from 1 to 0, a new IIC-bus-protocol should be started to switch IIC-switch from 1 to 0. By this, highest noise-surpression of the SDA/

SCL-signals is guaranteed. (see also "10.1 After-Reset-Start-Sequence")

OSC SYS 1...0:

Defines source for system-clock generation. The frequency

of this source is internally multiplied to 4FSC.

This frequency is used for color-carrier-generation in full-

page-mode.

00: 1 FSC (Pin 3) with ext. feedback resistor

01: 2 FSC (Pin 3) with ext. feedback resistor

10: 4 FSC (Pin 3) with ext. feedback resistor

**11**: optional, external crystal-oscillator for system-clock-generation(Pin3/Pin6). This crystal-oscillator must have his resonance-frequency at 2FSC.

This mode also can be used as a alternative mode to 01: 2FSC (Pin3). In this mode the external feedback resistor is no longer necessary because in this mode a internal resistor is used.

The oscillator-mode can be installed by these bits as long as the bit RELEASE in the register LEVELS\_AND\_CHANGE is set to 1.

After setting bit RELEASE in register LEVELS\_AND\_CHANGE to 0, the oscillator-mode won't change anymore, anyway if the polarity of these bits are changed by the user.

Next to the oscillator-mode-settings, the bit OSC\_SYS(0) can be used to switch a special VCS-spike-surpress-filter for the slicer on and off. We recommend to keep this filter switched on in all modes.

**0:** The VCS-spike-filter is switched on.

1: The VCS-spike-filter is switched off.

Next to the oscillator-mode-settings the bit OSC\_SYS(1) can be used to switch a special algorithm to the slicer. This special algorithm allows high noise-surpress. The algorithm works for signals in which the CRI has the same length(8cycles) as it is described inside the ETSI-standard for teletext. If a CVBS-signal is processed in which the count of CRI-cycles is non-standard the special algorithm should be switched off. We recommend to start the data-slicing by switching the special algorithm on (for standard-signals and high-noise-performance). If this is not successfull we recommend to proceed the data-slicing by switching the special algorithm off. By this, non-standard-signals can be sliced with a little less noise-performance.

0: Special algorithm is switched on

1: Special algorithm is switched off

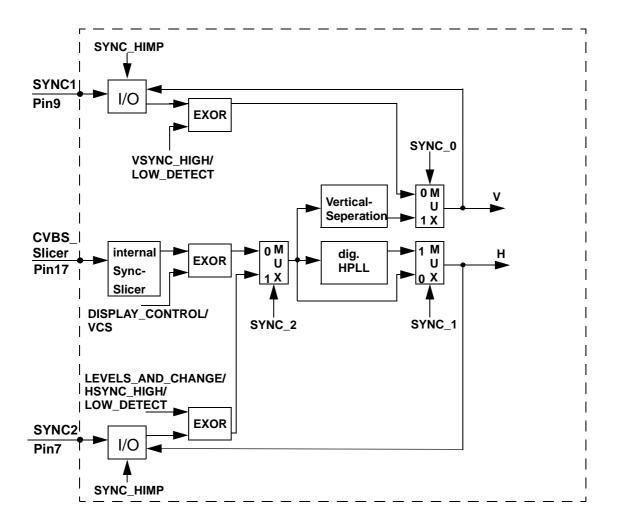

Three MUXes inside the synchronisation-signal-pathes are controlled by these three bits as shown below in the figure. Pin9 and Pin7 are used as a input/output for external syn

SYNC\_2...0:

chronisation. If bit SYNC\_2 is switched to 0 Pin7 is used as output, if SYNC\_0 is switched to 1 Pin9 is used as output.

Next to SYNC\_2...0 the synchronisation-signal-path is controlled by the bits SYNC\_HIMP, HSYNC\_HIGH/LOW\_DETECT and VSYNC\_HIGH/LOW\_DETECT of the register LEVELS\_AND\_CHANGE (see also page 26/27). SYNC\_HIMP is used to switch the outputs in high-impedant-state. HSYNC\_HIGH/LOW\_DETECT and VSYNC\_HIGH/LOW\_DETECT is used to invert the synchronisation-signals for enabling the detection of both edges synchronisation-edges.

Figure: Signal-pathes of the sync-seperation-circuit

#### Summary of Sync-Modes (SYNC2...0):

| SYNC_<br>2 | SYNC_<br>1 | SYNC_<br>0 | Н      | V      | HPLL       | Pin9   | Pin7   |

|------------|------------|------------|--------|--------|------------|--------|--------|

| 0          | 0          | 0          | intern | extern | out of use | input  | output |

| 0          | 0          | 1          | intern | intern | out of use | output | output |

| 0          | 1          | 0          | intern | extern | in use     | input  | output |

| 0          | 1          | 1          | intern | intern | in use     | output | output |

| 1          | 0          | 0          | extern | extern | out of use | input  | input  |

| 1          | 0          | 1          | extern | intern | out of use | output | input  |

| 1          | 1          | 0          | extern | extern | in use     | input  | input  |

| 1          | 1          | 1          | extern | intern | in use     | output | input  |

Negative going **HSync**-pulses are expected by default. Using the register LEVELS\_AND\_CHANGE this can be switched to positive going syncpulses.

With VSYNC\_EDGE\_POLARITY in the register LEVELS\_AND\_CHANGE the user can choose level or edge-sensitive vertical synchronisation.

The polarity of the digital output-H-sync-signal are positive going sync-impulses.

#### The color look-up-table

The IC is capable to display eight different color values in one picture. These eight values can be defined by the user in the registers **color\_value**:

On the assumption, that the color-values are given in voltage values which are related to a CVBS-Signal the corresponding register-contents could be derived as follows:

given color-value: phase

chromaamplitude (peak to peak in mV)

luminanceamplitude (in mV above porch-level)

corresponding register-contents:

Iuminance-register: INTEGER( 63\*(luminanceamplitude+300mV)/1000mV)

U-component-register: INTEGER(chromaamplitude\*cos(phase)\*63/2000mV)

V-component-register: -INTEGER(chromaamplitude\*sin(phase)\*63/2000mV)

For example these equations are solved for three color-values:

#### 1. Blue

Phase: -38° Chromaphase

162mV Chromaamplitude (peak to peak in mV)

200mV Luminanceamplitude (above Porch-Level)

luminance-register: 32U-component-register: +4

V-component-register: +3

#### 2. Blue-Green

Phase: -90° Chromaphase

286mV Chromaamplitude (peak to peak in mV)

250mV Luminanceamplitude (above Porch-Level)

Iuminance-register: 35U-component-register: 0V-component-register: +9

#### 3. Grey

Phase: indifferent Chromaphase

0mV Chromaamplitude

125mV Luminanceamplitude (above Porch-Level)

Iuminance-register: 27U-component-register: 0V-component-register: 0

The U/V-component-registers are programmed in two's-complement. This means:

01111b +15 = 01110b =+14 01101b =+13 . . . . . 00000b =0 11111b = -1 11110b = -2 11101b = -3 ..... .... 10001b =-15

The value 10000 b = -16 d is not allowed.

#### Format of the eight registers color-value1...8:

|              | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|

| LUMINANCE    | (0)   | (0)   | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

| U-COMPONENTE | (0)   | (0)   | (0)   | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

| V-COMPONENTE | (0)   | (0)   | (0)   | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

#### Format of border-color-register/Fringing-color-register:

There is a leftover of active video surrounding the field of characters. The colors of this border can be defined via the look-up-table described above.

Next to the border-color, the fringing color is defined in this register.

|                | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|-------|--------|--------|--------|-------|-------|-------|-------|

| BORDER_FRINGIN | (0)   | FRCO_2 | FRCO_1 | FRCO_0 | BO_ON | BORDE | BORDE | BORDE |

| G              |       |        |        |        | OFF   | R_2   | R_1   | R_0   |

Border can be switched on and off.

**Border off** means for **fullpage-mode:** The left part of the border in each row is set to the same color as the first character in each row is set. The right part of the border in each row is set to the same color as the last character is set. The upper and lower part of the border is set to the color defined for the border.

**Border on** means for **fullpage-mode:** The whole border has the color which is defined for the border.

BO\_ONOFF 0: Border on

1: Border off

BORDER2...0 Defines the color of the border via the color-look-up-

table (see above).

**FRCO\_2..0:** If fringing is turned on one out of eight fringing grey-values

can be selected. The levels for the grey-values in full-page mode are 1.4V and 1.9V in steps of about 67 mV. In mixed mode eight levels between 1.4V and 2.1V in steps of about

93mV can be selected in full-page-mode.

#### **Format of register Display Control:**

Switching between full-page-OSD and mixed-mode and turning display off, etc. ... is handled with the Display-Control-Register. The IC has a multi standard video output. That means, NTSC/PAL-color-systems can be encoded and field-frequencies of 50/60Hz can be choosen.

In standard-mode the pixel-clock is derived from color-carrier (2FSC). The user is free to choose the color-carrier which is fed in at Pin3. For example PAL color-carrier is 4.43MHz and NTSC color-carrier is 3.58MHz. The pixel-clock is derived from this color-carrier. A suitable count of character in horizontal direction can be choosen by the bit NORM1.

For NTSC and some PAL-derivates a frame-rate of 60Hz (525 lines) is used. In this case in vertical direction 12 character-rows are produced. In standard-PAL a frame-rate of 50Hz (625 lines) is used. As a result in vertical direction 14 character-rows are produced.

|                      | Bit 7        | Bit 6 | Bit 5         | Bit 4            | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|----------------------|--------------|-------|---------------|------------------|-------|--------|--------|--------|

| DISPLAY CON-<br>TROL | DAVN/<br>EHB | VCS   | FULL-<br>PAGE | SECAM_<br>SWITCH | SPACE | NORM_2 | NORM_1 | NORM_0 |

**DAVN/EHB:** The DAVN and EHB-signals can be made visible on the

output-pin10. Which of these two signals is shown on

the output-pin is defined in the bit DAVN/EHB.

1: EHB is shown at Pin10. 0: DAVN is shown at Pin10.

**VCS: 0:** Internal VCS is not inverted (front porch of H is used

for synchronisation).

1: Internal VCS is inverted (back porch of H is used for

synchronisation).

**NORM0:** This bit is only used in full-page-mode.

**0**: NTSC **1**: PAL

**NORM1:** This bit is used in both modes (full-page and mixed-mode)

**0:** 30 characters in horizontal direction **1:** 32 characters in horizontal direction

**NORM2:** This bit is used in both modes (full-page and mixed-mode)

**0:** 50Hz-system **1:** 60Hz-system

Following standards can be choosen by NORM2 and NORM0:

| NORM2 | NORM0 | standard                      | nominal color-car-<br>rier-frequency |

|-------|-------|-------------------------------|--------------------------------------|

| 0     | 0     | NTSC(equivalent to mode "10") | 3,57954500 MHz                       |

| 0     | 1     | PAL BG                        | 4,43361875 MHz                       |

| 1     | 0     | NTSC(equivalent to mode "00") | 3,57954500 MHz                       |

| 1     | 1     | PAL M                         | 3.57561149 MHz                       |

**SPACE: 0:** In this state the character-RAM is displayed.

1: In this state the contents of the character-RAM are ignored and space-characters are displayed all over the

screen.

**SECAM\_SWITCH: 0:**SECAM-Switch off for PAL/NTSC

**1:**SECAM-Switch on for SECAM-Signals. That means the current SECAM-color-frequency on CVBSin-side is added to the CVBS-out signal in the areas of characters

in mixed mode.

**FULLPAGE: 0:**Full-Page-OSD-Mode.

1:Mixed-Mode.

#### Format of register LEVELS\_AND\_CHANGE:

|                       | Bit 7 | Bit 6 | Bit 5                                   | Bit 4              | Bit 3            | Bit 2                                    | Bit 1         | Bit 0                          |

|-----------------------|-------|-------|-----------------------------------------|--------------------|------------------|------------------------------------------|---------------|--------------------------------|

| LEVELS_AND_CHA<br>NGE | (0)   | (0)   | VSYNC_<br>EDGE_<br>POLAR-<br>ITY<br>(1) | RELEAS<br>E<br>(1) | SYNC_<br>HIMP(1) | VSYNC_<br>HIGH/<br>LOW_<br>DETECT<br>(0) | HIGH/<br>LOW_ | CHNG_<br>MIXED_<br>FULL<br>(1) |

CHNG\_MIXED\_FULL: Next to the Register-Bit FULLPAGE in DISPLAY\_

CONTROL-Register this bit has to be used for switching

between fullpage-mode and mixed-mode.

0: For mixed-mode1: For fullpage-mode

1. Switching from mixed-mode to fullpage-mode:

**first step:** DISPLAY\_CONTROL/Bit5 set to 0 **second step:** CHNG\_MIXED\_FULL set to 1

2. Switching from fullpage-mode to mixed-mode:

**first step:** CHNG\_MIXED\_FULL set to 0 **second step:** DISPLAY\_CONTROL/Bit5 set to 1

HSYNC\_HIGH/LOW\_DETECT: Defines which polarity of the Hsync should be used for

OSD-synchronization.

**0:** Negative going sync-pulses are expected.

1: Positive going sync-pulses are expected.

VSYNC\_HIGH/LOW\_DETECT: Defines which edge of the Vsync should be used for

OSD-synchronization.

0: Uses the rising edge

1: Uses the falling edge

**SYNC\_HIMP:** 0: The output of the pins 7/9 are not switched to high-

impedant-state in all the modes.

1: The output of the pins 7/9 are switched to high-

impedant-state in all the modes.

**RELEASE:** After power-on-reset the contents of the synchronisation-

register may not refer to the frequency which is fed in at Pin9/7. After setting the bits OSC\_SYS1..0 in the Register SYNCHRONISATION to the contents which are referring to the input-frequency, the bit RELEASE has to be switched from 1 to 0. After switching to 0 the bit RELEASE cannot be changed anymore to 1 except by a IIC-bus- or power-on-

reset.

After switching bit RELEASE to 0 the bits

OSC\_SYS1..0 in Register SYNCHRONISATION cannot

be changed anymore without executing a IIC- or

power-on-reset..

**VSYNC\_EDGE\_POLARITY:**

This bit is used, to choose the synchronisation-mode in mixed-mode for the VSync. If polarity is choosen the OSD is synchronized by the levels of the VSync. In this case the Vsync should have a minimum-length of 1line. If edge is choosen the OSD is synchronized by the edge of the VSync. In this case there are no special efforts to the Vsync-length.

In general it's recommended to use the edges.

**0:** OSD is synchronized by VSync edges.

1: OSD is synchronized by VSYNC polarity.

# 7.3. I<sup>2</sup>C-Bus

Information is exchanged between an external controller and the SD 5652-2X on a fast asynchronous bidirectional data bus. The I<sup>2</sup>C-Bus uses two connections, the pins SDA (data) and SCL (clock), and operates according to the I<sup>2</sup>C-Bus specifications, which limits the maximum transfer rate at 400 kbit/s. The interface operates in the slave mode: either as receiver or transmitter. The chip address is fixed to **MSB 0010000X LSB**. The MSB is transmitted first. The LSB switches between reading-mode(1) and writing-mode(0).

The bus-system isn't blockaded if there is no power-supply switched to the SDA5652-2X

#### 7.3.1 Protocols

The following protocols are supported (in read mode the subaddress must be defined by a previously access):

#### Write followed by a read:

| S | S | W | Α | S | Α | D | Α | D | Α | <br> | <br>S | S | R | Α | D | Α | D | Α | D | Α | <br> | <br>S |

|---|---|---|---|---|---|---|---|---|---|------|-------|---|---|---|---|---|---|---|---|---|------|-------|

| Т | L | R | С | U | С | Α | С | Α | С |      | Т     | L | Е | С | Α | С | Α | С | Α | С |      | Т     |

| Α | _ | 1 | K | _ | K | Т | K | Т | K |      | Α     | _ | Α | K | Т | K | Т | K | Т | K |      | 0     |

| R | Α | Т | _ | Α | _ | Α | _ | Α | _ |      | R     | Α | D | _ | Α | _ | Α | _ | Α | _ |      | Р     |

| Т | D | Е | S | D | S |   | S |   | S |      | Т     | D |   | S |   | М |   | M |   | М |      |       |

**Please notice:** Before the stop-condition after the reading-operation, there is no ACK\_M allowed!!!

#### Write followed by a read with stop condition:

| S | S | W | Α | S | Α | D | Α | D | Α | <br> | S | S | S | R | Α | D | Α | D | Α | D | Α | <br> | <br>S |

|---|---|---|---|---|---|---|---|---|---|------|---|---|---|---|---|---|---|---|---|---|---|------|-------|

| Т | L | R | С | U | С | Α | С | Α | С |      | Т | Т | L | Ε | С | Α | С | Α | С | Α | С |      | Т     |

| Α | _ | 1 | K | _ | K | Т | K | Т | K |      | О | Α | _ | Α | K | Т | K | Т | K | Т | K |      | 0     |

| R | Α | Т | _ | Α | _ | Α | _ | Α | _ |      | Р | R | Α | D | _ | Α | _ | Α | _ | Α | _ |      | Р     |

| Т | D | Ε | S | D | S |   | S |   | S |      |   | Т | D |   | S |   | М |   | М |   | М |      |       |

**Please notice:** Before the stop-condition after the reading-operation, there is no ACK\_M allowed!!!

with the following abbreviations:

START: Start condition (I<sup>2</sup>C: see technical bus description)

STOP: Stop condition (I<sup>2</sup>C: see technical bus description)

ACK\_S: Acknowledge by slave (I<sup>2</sup>C: see technical bus description)

ACK\_M: Acknowledge by master (I2C: see technical bus description)

SL\_AD: 7- Bit chip select address

SU AD: 8- Bit subaddress

#### 7.3.2 Access modes

There are two possibilities to access SDA 5652-2X. One is addressing it direct by use of one of the 256 possible subaddresses of the I<sup>2</sup>C protocol. The other method is an indirect addressing method. This must be used if a byte from the display RAM should be read or written. In that case a dataport must be used for transfer (see below).

### **Autoincrement of Bus Registers**

After any read or write access to a register the subaddress will be incremented automatically. There are only one exceptions: in read and write mode, subaddress "2" is not incremented (see also dataport access).

# 7.3.3 Dataport access

The address pointer registers are used to address the internal memory to read or write data via the I<sup>2</sup>C Bus. A dataport (2) is an I<sup>2</sup>C-Bus register which can be read or written by addressing it with its subaddress. Independent from the transfer direction (read or write) the memory address is defined by the address pointer registers (0, 1) which must be defined before accessing the dataport. The display-RAM is accessed via the dataport. Its startaddress begins at address 0.

# **Autoincrement of the Dataport**

The autoincrement for the dataport is always switched on. That means, each time after the dataport address (2) is accessed, the contents of the addresspointer registers is incremented. The following protocols are supported:

# Writing the memory including initializing of addressport:

| S | S | W | Α | S | Α | Α | Α | Α | Α | D | Α | D | Α | D | Α | D | Α | <br> | <br> | <br> | <br>Α | S |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|------|------|-------|---|

| Т | L | R | С | U | С | D | С | D | С | Α | С | Α | С | Α | С | Α | С |      |      |      | С     | Т |

| Α | _ | I | K | _ | K | R | K | R | K | Т | K | Т | K | Т | K | Т | K |      |      |      | K     | 0 |

| R | Α | Т | _ | Α | _ | _ | _ | _ | _ | Α | _ | Α | _ | Α | _ | Α | _ |      |      |      | _     | Р |

| Т | D | Е | S | 0 | S | 0 | S | 1 | S |   | S |   | S |   | S |   | S |      |      |      | S     |   |

#### Writing the memory using an previous defined addressport:

| S  | S | W | Α | S | Α | D | Α | D | Α | D | Α | D | Α | D | Α | D | Α | D | Α | <br> | <br> | <br>Α | S |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|------|-------|---|

| TA | L | R | С | U | С | Α | С | Α | С | Α | С | Α | С | Α | С | Α | С | Α | С |      |      | С     | Т |

| R  | _ | I | K | _ | K | Т | K | Т | K | Т | K | Т | K | Т | K | Т | K | Т | K |      |      | K     | 0 |

| Т  | Α | Т | _ | Α | _ | Α | _ | Α | _ | Α | _ | Α | _ | Α | _ | Α | _ | Α | _ |      |      | _     | Р |

|    | D | Е | S | 2 | S |   | S |   | S |   | S |   | S |   | S |   | S |   | S |      |      | S     |   |

#### Reading the memory using an previous defined addressport:

| S | S | W | Α | S | Α | S | S | S | R | D | Α | D | Α | D | Α | D | Α | D | Α | <br> | <br> | <br> | S |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|------|------|---|

| Т | L | R | С | U | С | Т | Т | L | Ε | Α | С | Α | С | Α | С | Α | С | Α | С |      |      |      | Т |

| Α | _ | 1 | K | _ | K | 0 | Α | _ | Α | Т | K | Т | K | Т | K | Т | K | Т | K |      |      |      | 0 |

| R | Α | Т | _ | Α | _ | Р | R | Α | D | Α | _ | Α | _ | Α | _ | Α | _ | Α | _ |      |      |      | Р |

| Т | D | Е | S | 2 | S |   | Т | D |   |   | S |   | M |   | M |   | М |   | M |      |      |      |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |      |      |   |

Please notice: Before the stop-condition after the reading-operation, there is no more a

ACK\_M allowed!!!

with the following additional abbreviations:

SU A0...2: Subaddress

ADR\_1...0: Addresspointer

START: Start condition (I<sup>2</sup>C: see technical bus description, M3L Falling edge of I<sup>2</sup>CEN)

STOP: Stop condition (I<sup>2</sup>C: see technical bus description, M3L Rising edge of I<sup>2</sup>CEN)

ACK: Acknowledge (I<sup>2</sup>C: see technical bus description)

SL\_AD: 7-Bit chip select address

# Format of the register ADR\_POINTER (default values in brackets):

|               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1        | Bit 0        |

|---------------|-------|-------|-------|-------|-------|-------|--------------|--------------|

| ADR_POINTER_1 | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | ADR_9<br>(0) | ADR_8<br>(0) |

| ADR_POINTER_0 | ADR_7 | ADR_6 | ADR_5 | ADR_4 | ADR_3 | ADR_2 | ADR_1        | ADR_0        |

|               | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)          | (0)          |

| DATA_PORT     | DAT_7 | DAT_6 | DAT_5 | DAT_4 | DAT_3 | DAT_2 | DAT_1        | DAT_0        |

|               | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)          | (0)          |

#### ADR\_9...0

Addressport. Defines the internal memory address where data should be written or read from. Only address valid addresses defined in the memory map table are allowed.

#### Format of register DATA\_PORT (default values in brackets):

|           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

| DATA_PORT | DAT_7 | DAT_6 | DAT_5 | DAT_4 | DAT_3 | DAT_2 | DAT_1 | DAT_0 |

|           | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |

#### **DAT 7...0**

Dataport. This register contains the data to be transferred. Each time when this register is read or written the contents of the addressport is autoincremented and not the internal subaddress.

# Example for data port access (Beginning at address 292d (124h) the following data should be written: 11h, 12h, 13h, 14h

| Protocol          | Hex values | Comment                                                                                                                                                                                      |

|-------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chipadress, Write | 20h        | SDA 5652-2X chipaddress                                                                                                                                                                      |

| Subaddress        | 00h        | Subaddress is initialized                                                                                                                                                                    |

| Data, Ack         | 24h        | 24h is transmitted to subaddress "0" (Addresspointer). The internal subaddress is autoincremented.                                                                                           |

| Data, Ack         | 01h        | 01h is transmitted to subaddress "1" (Addresspointer) Addresspointer is now set to 124h.                                                                                                     |

| Data, Ack         | 11h        | Subaddress is now "2". Data is written to the dataport and then internally transferred to RAM address 124h. The addresspointer is autoincremented to 125h. The subaddress is not incremented |

| Data, Ack         | 12h        | Data is written to the dataport and then internally transferred to RAM address 125h. The addresspointer is autoincremented to 126h.                                                          |

| Data, Ack         | 13h        | Data is written to the dataport and then internally transferred to RAM address 126h. The addresspointer is autoincremented to 127h.                                                          |

| Data, Ack         | 14h        | Data is written to the dataport and then internally transferred to RAM address 127h. The addresspointer is autoincremented to 128h.                                                          |

| Stop              |            |                                                                                                                                                                                              |

# 7.3.4 Subaddresses and commands of I<sup>2</sup>C-Bus

# 7.3.4.1 I<sup>2</sup>C-register-addresses:

The above described I<sup>2</sup>C-Registers can be handled with the subaddresses described below. A special function is implemented for the address 255. If this address is submitted to the IC a reset is released.

| I <sup>2</sup> C-Address | Register-Name   | read/write                                     |

|--------------------------|-----------------|------------------------------------------------|

| 0                        | ADR_POINTER_0   | write                                          |

| 1                        | ADR_POINTER_1   | write                                          |

| 2                        | DATA-PORT       | read/write                                     |

| 3                        | ACQ-Control     | read (only Bit5) /<br>write(excluding<br>Bit5) |

| 4-40                     | VPS/PDC-datas   | read                                           |

| 41                       | SYNCHRONISATION | read(only<br>OSC_SYS10)/<br>write              |

| 42  | LEVELS_AND_CHANGE               | write |

|-----|---------------------------------|-------|

| 254 | IC-IDENTIFICATION (content:02h) | read  |

| 255 | RESET                           | write |

# 7.3.4.2. I<sup>2</sup>C-Commands

#### **RESET-Command: 255d**

This command resets the whole IC. The protocol which has to be used is defined as follows:

| S<br>T | S | W | Α | 2 | Α | D      | Α | S |

|--------|---|---|---|---|---|--------|---|---|

| Т      | L | R | С |   | С | A<br>T | С | Т |

| Α      | _ | I | K | 5 | K | Т      | K |   |

|        | Ā | Т |   |   |   | Α      |   | Р |

| Т      | D | Е |   | 5 |   |        |   |   |

START: Start condition (I<sup>2</sup>C: see technical bus description, M3L Falling edge of I<sup>2</sup>CEN)

STOP: Stop condition (I<sup>2</sup>C: see technical bus description, M3L Rising edge of I<sup>2</sup>CEN)

ACK: Acknowledge (I<sup>2</sup>C: see technical bus description)

SL\_AD: 7-Bit chip select address (Write-Mode)

255: Reset-Command

DATA: This data hasn't got any meaning. It's only used to keep the restrictions of a protocol.

# 7.3.4.3 RAM-registers

Some register-contents are stored in the RAM. These register-contents have to be accessed using the Data-Port of the I<sup>2</sup>C-bus:

| from | to  | content                    |  |  |  |  |  |  |

|------|-----|----------------------------|--|--|--|--|--|--|

| 0    | 447 | display-RAM                |  |  |  |  |  |  |

| 448  | 484 | used IC-internal           |  |  |  |  |  |  |

| 485  |     | ROW_ATTRIBUTE/ROW1         |  |  |  |  |  |  |

| 486  |     | ROW_ATTRIBUTE/ROW2         |  |  |  |  |  |  |

| 487  |     | ROW_ATTRIBUTE/ROW3         |  |  |  |  |  |  |

| 488  |     | ROW_ATTRIBUTE/ROW4         |  |  |  |  |  |  |

| 489  |     | ROW_ATTRIBUTE/ROW5         |  |  |  |  |  |  |

| 490  |     | ROW_ATTRIBUTE/ROW6         |  |  |  |  |  |  |

| 491  |     | ROW_ATTRIBUTE/ROW7         |  |  |  |  |  |  |

| 492  |     | ROW_ATTRIBUTE/ROW8         |  |  |  |  |  |  |

| 493  |     | ROW_ATTRIBUTE/ROW9         |  |  |  |  |  |  |

| 494  |     | ROW_ATTRIBUTE/ROW10        |  |  |  |  |  |  |

| 495  |     | ROW_ATTRIBUTE/ROW11        |  |  |  |  |  |  |

| 496  |     | ROW_ATTRIBUTE/ROW12        |  |  |  |  |  |  |

| 497  |     | ROW_ATTRIBUTE/ROW13        |  |  |  |  |  |  |

| 498  |     | ROW_ATTRIBUTE/ROW14        |  |  |  |  |  |  |

| 499  |     | CHAR_definition1_1/BYTE1   |  |  |  |  |  |  |

| 500  |     | CHAR_definition1_1/BYTE2   |  |  |  |  |  |  |

| 501  |     | CHAR_definition1_2/BYTE1   |  |  |  |  |  |  |

| 502  |     | CHAR_definition1_2/BYTE2   |  |  |  |  |  |  |

| 503  |     | CHAR_definition1_3/BYTE1   |  |  |  |  |  |  |

|      |     |                            |  |  |  |  |  |  |

| 507  |     | CHAR_definition2_1/BYTE1   |  |  |  |  |  |  |

|      |     |                            |  |  |  |  |  |  |

| 514  |     | CHAR_definition2_4/BYTE2   |  |  |  |  |  |  |

| 515  |     | VERTICAL_START_POSITION    |  |  |  |  |  |  |

| 516  |     | HORIZONTAL_START_POSITION  |  |  |  |  |  |  |

| 517  |     | DISPLAY_CONTROL            |  |  |  |  |  |  |

| 518  |     | BORDER_color               |  |  |  |  |  |  |

| 519  |     | COLOR_VALUE_1/LUMINANCE    |  |  |  |  |  |  |

| 520  |     | COLOR_VALUE_1/V_COMPONENTE |  |  |  |  |  |  |

| from | to  | content                    |

|------|-----|----------------------------|

| 521  |     | COLOR_VALUE_1/U_COMPONENTE |

| 522  |     | COLOR_VALUE_2/LUMINANCE    |

| 523  |     | COLOR_VALUE_2/V_COMPONENTE |

| 524  |     |                            |

| 525  |     | COLOR_VALUE_4/LUMINANCE    |

|      |     | COLOR_VALUE_4/V_COMPONENTE |

| 530  |     | COLOR_VALUE_4/U_COMPONENTE |

|      |     |                            |

|      |     | COLOR_VALUE_8/LUMINANCE    |

|      |     | COLOR_VALUE_8/V_COMPONENTE |

| 542  |     | COLOR_VALUE_8/U_COMPONENTE |

| 543  |     | HPLL                       |

| 544  | 575 | out of internal use        |

| 576  | 612 | used internal              |

# 8. Electrical Characteristics

#### Power-on-reset:

After Power-on a so called Power-on-reset is executed. The condition for a power-on-reset is a rising VDDA from a voltage value of less than 0,8V to a voltage value of at least 4,5V.

# **Absolute Maximum Ratings**

$T_{\mathsf{A}} = 25~^{\circ}\mathsf{C}$

| Parameter                    | Symbol              | Lin            | nit Values | Unit | <b>Test Condition</b> |  |

|------------------------------|---------------------|----------------|------------|------|-----------------------|--|

|                              |                     | min.           | max.       |      |                       |  |

| Ambient temperature          | $T_{A}$             | 0              | 70         | °C   | in operation          |  |

| Storage temperature          | $T_{\rm stg}$       | - 40           | 125        | °C   | by storage            |  |

| Total power dissipation      | $P_{tot}$           |                | tbd        | mW   |                       |  |

| Power dissipation per output | $P_{DQ}$            |                | 10         | mW   |                       |  |

| Supply voltage               | $V_{DDD} \ V_{DDA}$ | - 0.3<br>- 0.3 | 6<br>6     | V    |                       |  |

| Thermal resistance           | R <sub>th SU</sub>  |                | 80         | K/W  |                       |  |

| Operating Range              |                     |                |            |      |                       |  |

| Supply voltage               | $V_{DDD} \ V_{DDA}$ | 4.5<br>4.5     | 5.5<br>5.5 | V    |                       |  |

| Supply current               | $I_{DD}$            | 35             | 50         | mA   |                       |  |

0

$T_{\mathsf{A}}$

70

°С

#### **Characteristics**

Ambient temperature range

$T_{\mathsf{A}} = 25~^{\circ}\mathsf{C}$

| Parameter              | Symbol   | Limit         | Values           | Unit | <b>Test Condition</b> |  |

|------------------------|----------|---------------|------------------|------|-----------------------|--|

|                        |          | min.          | max.             |      |                       |  |

| Input Signals SDA, SCL |          |               |                  |      |                       |  |

| H-input voltage        | $V_{IH}$ | $0.7xV_{DDD}$ | $V_{DDD}$        | V    |                       |  |

| L-input voltage        | $V_{IL}$ | 0             | $0.3xV_{DDD}$    | V    |                       |  |

| Input capacitance      | $C_{I}$  |               | 10               | pF   |                       |  |

| Input current          | $I_{IM}$ |               | 10               | μΑ   |                       |  |

| Input Signal TMODE     |          |               |                  |      |                       |  |

| H-input voltage        | $V_{IH}$ | $0.9xV_{DDD}$ | $V_{DDD}$        | V    |                       |  |

| L-input voltage        | $V_{IL}$ | 0             | $0.1xV_{ m DDD}$ | V    |                       |  |

| Input capacitance      | $C_{I}$  |               | 10               | pF   |                       |  |

| Input current          | $I_{IM}$ |               | 10               | μΑ   |                       |  |

# Characteristics (cont'd)

$T_{\mathsf{A}} = 25~^{\circ}\mathsf{C}$

| Parameter | Symbol | Limit Values |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|----------------|

|           |        | min.         | max. |      |                |

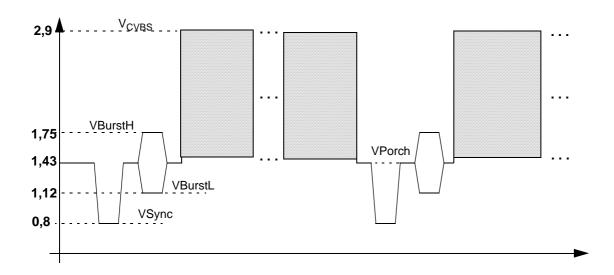

#### Input Signal CVBS/Output Signal mixed mode:

| synchron signal amplitude (bottom) | V <sub>SYNC</sub> | 0.7 | 0.9 | V |  |

|------------------------------------|-------------------|-----|-----|---|--|

| Black-Porch-Level                  | $V_{PORCH}$       | 1.3 | 1.5 | V |  |

Resistance of the switch between input and output-signal in mixed mode: <50 Ohm

#### **Output Signal CVBS in full page mode:**

Supplyvoltage is used as reference for D/A-converter. So the stability of voltage-values for the output signal depend on the supplyvoltage stability. Min-values are related to a supplyvoltage of 4,5V and max-values are related to a supplyvoltage of 5,5V.

| 100% - white level                 | $V_{CVBS}$          | 2.6                   | 3.2                   | V |  |

|------------------------------------|---------------------|-----------------------|-----------------------|---|--|

| Synchron signal amplitude (bottom) | V <sub>SYNC</sub>   | 0.7                   | 0.9                   | V |  |

| Color burst low                    | V <sub>BURSTL</sub> | 1.0(NTSC)<br>1.1(PAL) | 1.2(NTSC)<br>1.3(PAL) | V |  |

| Color burst high                   | V <sub>BURSTH</sub> | 1.6(NTSC)<br>1.5(PAL) | 1.9(NTSC)<br>1.8(PAL) | V |  |

| Black-Porch-Level                  | $V_{PORCH}$         | 1.3                   | 1.6                   | V |  |

#### Input Signal CVBS\_Slicer:

| Video input signal level peak to peak  | $V_{CVBS}$     | 0.7  | 2.0 | V |             |

|----------------------------------------|----------------|------|-----|---|-------------|

| Synchron signal amplitude peak to peak | $V_{\sf SYNC}$ | 0.15 | 1.0 | V | Vdat=450mV  |

| Data amplitude peak to peak            | $V_{DAT}$      | 0.25 | 1.0 | V | VSync=300mV |

$T_{\mathsf{A}} = 25~^{\circ}\mathsf{C}$

| Parameter | Symbol | Limit \ | <b>Values</b> | Unit | <b>Test Condition</b> |

|-----------|--------|---------|---------------|------|-----------------------|

|           |        | min.    | max.          |      |                       |

| Output Signals SD | A (Open-Drain-Stage) |

|-------------------|----------------------|

|-------------------|----------------------|

| L-output voltage            | $V_{QL}$         |     | 0.4 | V  | $I_{Q} = 3.0 \text{ mA}$    |

|-----------------------------|------------------|-----|-----|----|-----------------------------|

| Permissible output voltage  |                  |     | 5.5 | V  |                             |

| Open-drain-resistance (SDA) | R <sub>SDA</sub> | 1.7 | 2.2 | kΩ | max. 200pF<br>load capacity |

| Open-drain-resistance (SCL) | R <sub>SCL</sub> | 1.7 | 2.2 | kΩ | max. 200pF<br>load capacity |

# **PLL-Loop Filter Components**

| Resistance at PD1/VCO1 | R | 2.2 | 4.7 | kΩ |  |

|------------------------|---|-----|-----|----|--|

| Resistance at PD2/VCO2 | R | 2.2 | 4.7 | kΩ |  |

| Capacitor at PD1/VCO1  | C | 68  | 220 | nF |  |

| Capacitor at PD2/VCO2  | C | 2,2 | 100 | nF |  |

# VCO – Frequence Range Adjustment

| Resistance at IREF (for bias | $R_4$ | 68+/-5% | kΩ |  |

|------------------------------|-------|---------|----|--|

| current adjustment)          |       |         |    |  |

# Input Signal Composite/Horizontal/Vertical-Sync

| H-input voltage                        | $V_{SyncH}$ | $0.6xV_{ m DDD}$ | $V_{DDD}$        | V    |  |

|----------------------------------------|-------------|------------------|------------------|------|--|

| L-input voltage                        | $V_{SyncL}$ | 0                | $0.2xV_{ m DDD}$ | V    |  |

| SECAM-bypass - bandpass fi             | lter        |                  |                  |      |  |

| Coil at CVBS_OUT                       | $L_1$       | 10               |                  | uH   |  |

| Capacitor at SECAM-bypass              | $C_2$       | 120              |                  | pF   |  |

| FSCin (1x/2x/4x)                       |             |                  |                  |      |  |

| Amplitude of FSCin-Signal peak to peak | $A(f_{SC})$ | 250              | 550              | mV   |  |

| Coupling Capacitor                     | C           | 1                | 100              | nF   |  |

| Clamp components on input              | CVBS-Slice  | er               |                  |      |  |

| Capacitor                              | C           | 330              | 1000             | nF   |  |

| Resistance                             | R           | 220              | 270              | kOhm |  |

| Crystal-Oscillator-Capacitano          | es:         |                  |                  |      |  |

| Capacitor                              | C           | 27               |                  | pF   |  |

| Crystal-impedance                      | R           |                  | 30               | Ohm  |  |

|                                        |             |                  |                  |      |  |

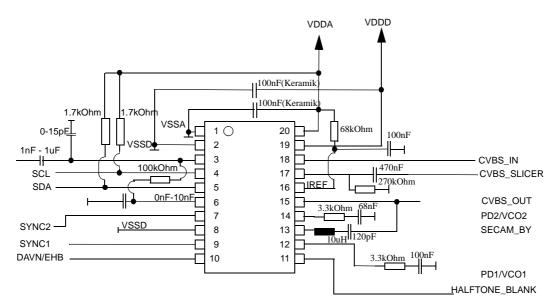

Environment for a system with 1fsc, 2fsc or 4fsc as external system-clock :

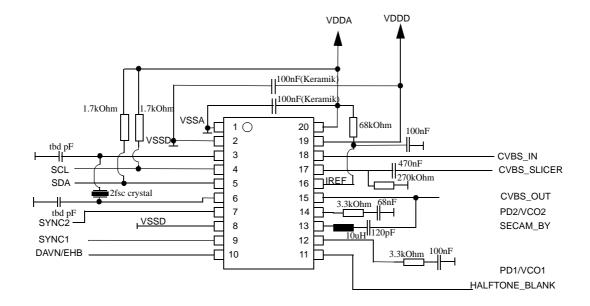

Environment for a system with a crystal-oscillator as system-clock:

Environment for a system with 2fsc as external system-clock in oscillator-mode 11:

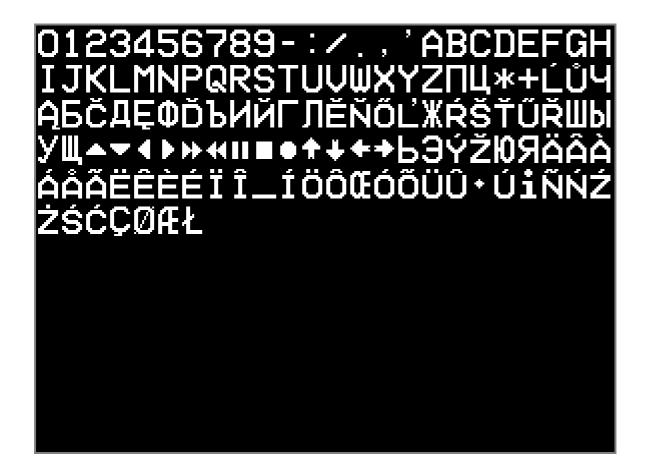

# 9. Character-ROM

In the character-ROM the shape of the characters is defined. 128 characters are stored in the ROM. Each character has got a structure of 12columnsx18lines:

The pixel-structur of the characters shown in the figure above refer to character-adresses shown in the table below:

| 79  | 49  | 50 | 51 | 52 | 53 | 54 | 55 | 56  | 57  | 45  | 58  | 47  | 46  | 44  | 39  | 65  | 66  | 67  | 68  | 69  | 70  | 71  | 72  |

|-----|-----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 73  | 74  | 75 | 76 | 77 | 78 | 80 | 81 | 82  | 83  | 84  | 85  | 86  | 87  | 88  | 89  | 90  | 40  | 41  | 42  | 43  | 48  | 37  | 38  |

| 91  | 92  | 93 | 94 | 95 | 96 | 97 | 98 | 99  | 100 | 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 | 109 | 110 | 111 | 112 | 113 | 114 |

| 115 | 116 | 59 | 60 | 61 | 62 | 63 | 64 | 117 | 118 | 119 | 120 | 121 | 122 | 123 | 124 | 125 | 126 | 127 | 0   | 1   | 2   | 3   | 4   |

| 5   | 6   | 7  | 8  | 9  | 10 | 11 | 12 | 13  | 14  | 15  | 16  | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  |

| 29  | 30  | 31 | 33 | 34 | 35 | 36 | 32 |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

# 10. Application notes

#### 10.1. After reset starting sequenz

After reset a maximum-time of 50us is needed in which the IC initializes itself. After this time, the following registers are set to their default-values:

ADR\_POINTER\_0, ADR\_POINTER\_1, DATA\_PORT, ACQ-Control SYNCHRONISATION

and

LEVELS\_AND\_CHANGE.

All the other register-values are set to random-values and must be initialized with IIC-bus.

After the time of 50us, the first IIC-access can be executed.

Within the first IIC-bus-accesses the following procedure should be carried out:

#### Procedure 1:

The register-bits OSC\_SYS0 and OSC\_SYS1 of the register SYNCHRONISATION have to be set to the values according the used external clock-source (1FSC, 2FSC, 4FSC or crystal).

#### Procedure 2:

The bits OSC\_SYS0 and OSC\_SYS1 are read and compared to the expected values which have been written in procedure 1. By this it is assured, that there has been no transmission-error to the IC.

If there has been no transmission error please go on with procedure 3 otherwise please go back to procedure 1.

#### Procedure 3:

Setting bit RELEASE of register LEVELS\_AND\_CHANGE from high to low. This will initialize the internal clock-generation-circuits according to the settings of the bits OSC\_SYS0 and OSC\_SYS1. If once register-bit RELEASE ist set to 0 it cannot be set to 1 anymore.

Setting bit IIC\_SWITCH of register SYNCHRONISATION from high to low. This will assure highest IIC-bus noise-surpressing.

# 11. Errata Sheet

# Hardware Items

| Item | Bug Desig-                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Affected | Correction |

|------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|