- 1 -

## **Unipolar Stepper Motor Driver**

#### **□ GENERAL DESCRIPTION**

The NJW4351 is a high efficiency DMOS unipolar stepper motor driver IC. Compared to previous devices, it is more suitable for low voltage operation, capable of handling 5.0V, 3.3V and the like logic circuits. Drive Stage consists of DMOS which produces high efficiency and low heat generation motor drive circuit.

The motor can be controlled by the STEP and DIR system. Further more, to improve controllability of system, MO, ENABLE, RESET and PD function are included, various applications are possible.

#### □ PACKAGE OUTLINE

NJW4351VC3

#### **□ FEATURES**

• Supply Voltage V<sub>DD</sub>=2.7 to 5.5V

$V_{MM}$ = to 55V

Output Current lo=1.5A peak at V<sub>DD</sub>=5V

• Low Quiescent Current I<sub>DD</sub>=500μA typ.

STEP&DIR Input Operation (Internal Translator)

• HALF/FULL Mode Generation

• TTL compatible Input With Schmitt-Comparator

• ENABLE Function

• RESET Function

• MO (Motor Origin Monitor) -Position-indication Output

• PD (Standby) Function

• Under Voltage Lock Out

• Thermal Shutdown Circuit

Alarm Output Function (As the protection circuit operates)

BCD Technology

Package Outline SSOP20-C3

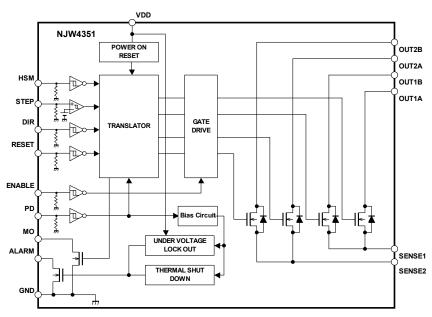

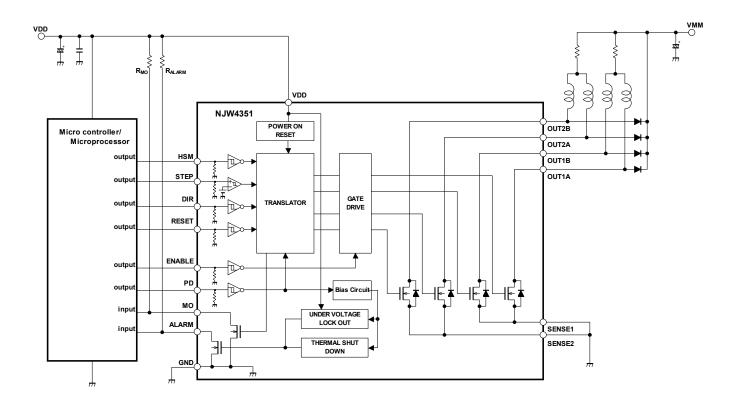

### ☐ BLOCK DIAGRAM

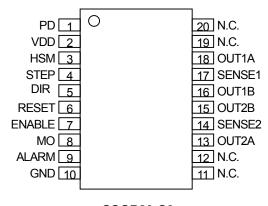

### ☐ PIN CONNECTION

SSOP20-C3

### ☐ PIN FUNCTION LIST

| Pin#<br>SSOP20-C3 | Terminal<br>Name | Function                                                | Remark                                                                                                 |

|-------------------|------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 1                 | PD               | Power Saving State Setting Input Terminal               | L=Standby, H=Normal Operation                                                                          |

| 2                 | VDD              | Logic Voltage Supply Terminal                           | Logic Voltage Supply                                                                                   |

| 3                 | HSM              | HALF/FULL Step Mode Setting Input Terminal              | L=FULL, H=HALF                                                                                         |

| 4                 | STEP             | Stepping Pulse Input Terminal                           | The Translator is triggered by positive edge of STEP Pulse.                                            |

| 5                 | DIR              | Direction Setting Input Terminal                        | L=FORWARD, H=REVERSE                                                                                   |

| 6                 | RESET            | Reset Input Terminal                                    | L=The Translator is initialized, H=Normal Operation                                                    |

| 7                 | ENABLE           | Phase Output Off Input Terminal                         | L=ACTIVE, H=Normal Operation                                                                           |

| 8                 | MO               | MO Output Terminal                                      | When the Translator is in initial status, L level is to output.                                        |

| 9                 | ALARM            | Internal Protection Operation Detection Output Terminal | When the internal protection operation is detected, L level is to output.                              |

| 10                | GND              | Logic Ground Terminal Logic Ground                      |                                                                                                        |

| 11,12,19,20       | N.C.             | No Connection                                           | No Connection                                                                                          |

| 13                | OUT2A            | 2ch Output Terminal A                                   | _                                                                                                      |

| 14                | SENSE2           | Current Detection Resistance<br>Connection Terminal 2   | It connects resistance for the detection of the side of 2ch. At the unused time, it connects with GND. |

| 15                | OUT2B            | 2ch Output Terminal B                                   |                                                                                                        |

| 16                | OUT1B            | 1ch Output Terminal B                                   | _                                                                                                      |

| 17                | SENSE1           | Current Detection Resistance<br>Connection Terminal 1   | It connects resistance for the detection of the side of 1ch. At the unused time, it connects with GND. |

| 18                | OUT1A            | 1ch Output Terminal A                                   | _                                                                                                      |

### ☐ ABSOLUTE MAXIMUM RATINGS

(Ta=25°C)

| PARAMETER             | SYMBOL             | RATINGS     | UNIT |                                          |

|-----------------------|--------------------|-------------|------|------------------------------------------|

| Logic Supply Voltage  | $V_{DD}$           | 7           | V    | VDD PIN                                  |

| Motor Output Voltage  | Vo                 | 55          | V    | OUT1A/1B/2A/2B PIN                       |

| Logic Input Voltage   | V <sub>IN</sub>    | 7           | ٧    | STEP, DIR, HSM, RESET,<br>ENABLE, PD PIN |

| ALARM Output Voltage  | $V_{ALARM}$        | 7           | V    | ALARM PIN                                |

| MO Output Voltage     | $V_{MO}$           | 7           | V    | MO PIN                                   |

| Output Current        | lo                 | 1.5         | Α    | OUT1A/1B/2A/2B PIN                       |

| ALARM Output Current  | I <sub>ALARM</sub> | 20          | mA   | ALARM PIN                                |

| MO Output Current     | I <sub>MO</sub>    | 20          | mA   | MO PIN                                   |

| Operating Temperature | Topr               | -40 to +85  | °C   | -                                        |

| Junction Temperature  | Tj                 | -40 to +150 | °C   | -                                        |

| Storage Temperature   | Tstg               | -50 to +150 | °C   | -                                        |

| Power Dissipation     | P <sub>D</sub>     | 1.0         | W    | (*1) Mounted on 2Layers PCB              |

| (SSOP20-C3)           | r <sub>D</sub>     | 1.5         | W    | (*1) Mounted on 4Layers PCB              |

<sup>(\*1):</sup> Mounted on glass epoxy board based on EIA/JEDEC. (114.3x76.2x1.6mm: 2Layers/4Layers)

### □ RECOMMENDED OPERATING CONDITIONS

(Ta=25°C)

| PARAMETER            | SYMBOL          | TEST CONDITION        | MIN. | TYP. | MAX. | UNIT |

|----------------------|-----------------|-----------------------|------|------|------|------|

| Logic Supply Voltage | V <sub>DD</sub> |                       | 2.7  | 3.3  | 5.5  | V    |

|                      |                 | V <sub>DD</sub> =5V   | -    | 500  | -    | mA   |

| Output Current       | lo lo           | V <sub>DD</sub> =3.3V | -    | -    | 500  | mA   |

# NJW4351

| ☐ ELECTRICAL CHARACTERIS    | STICS                  | ( $V_{MM}$ =24V, $V_{DD}$ =PD=3.3V, $R_L$ =1k $\Omega$ ,  | $R_{MO}$ =3.3 $k$ | $\Omega$ , $R_{ALARN}$ | <sub>//</sub> =3.3kΩ, | Ta=25°C) |

|-----------------------------|------------------------|-----------------------------------------------------------|-------------------|------------------------|-----------------------|----------|

| PARAMETER                   | SYMBOL                 | TEST CONDITION                                            | MIN.              | TYP.                   | MAX.                  | UNIT     |

| ☐ GENERAL                   |                        |                                                           |                   |                        |                       |          |

| Quiescent current           | I <sub>DD</sub>        | STEP,DIR,HSM,RESET,ENABLE=3.3V,<br>Except I <sub>IH</sub> | -                 | 0.5                    | 0.8                   | mA       |

| Quiescent current (Standby) | I <sub>PD</sub>        | PD=0V, except I <sub>IH</sub>                             | -                 | -                      | 1.0                   | uA       |

| ☐ INPUT BLOCK1 (STEP)       |                        |                                                           |                   |                        |                       |          |

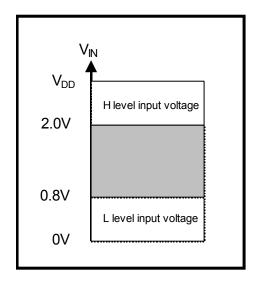

| H level input voltage1      | V <sub>IH1</sub>       |                                                           | 2.0               | -                      | _                     | V        |

| L level input voltage1      | V <sub>IL1</sub>       |                                                           | 0                 | -                      | 0.8                   | V        |

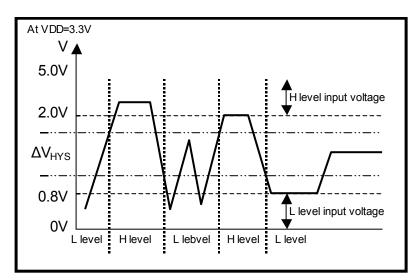

| Input hysteresis voltage1   | V <sub>IHYS1</sub>     |                                                           | 0.4               | 0.55                   | -                     | V        |

| H level input voltage2      | V <sub>IH2</sub>       | V <sub>DD</sub> =5V                                       | 2.4               | -                      | -                     | V        |

| L level input voltage2      | V <sub>IL2</sub>       | V <sub>DD</sub> =5V                                       | 0                 | -                      | 0.8                   | V        |

| Input hysteresis voltage2   | V <sub>IHYS2</sub>     | V <sub>DD</sub> =5V                                       | 0.4               | 0.55                   | -                     | V        |

| H level input current       | I <sub>H</sub>         | STEP=3.3V                                                 | 15                | 33                     | 45                    | uA       |

| L level input current       | I <sub>II</sub>        | STEP=0V                                                   | -                 | 10                     | 20                    | uA       |

| Input pull down resistance  | R <sub>DOWN</sub>      |                                                           | -                 | 100                    | -                     | kΩ       |

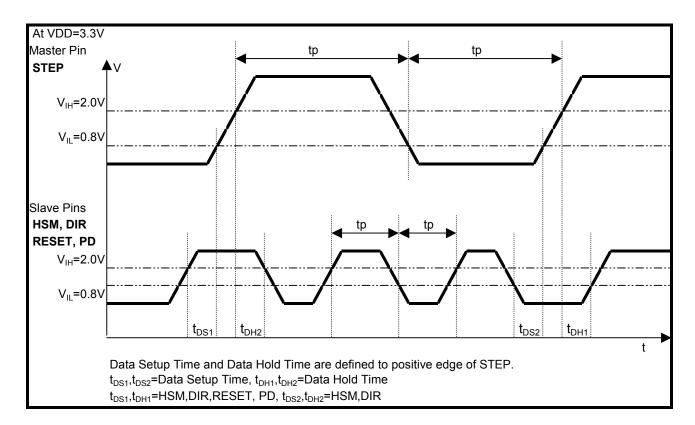

| Input pulse widths          | tp                     |                                                           | 2                 | -                      | -                     | us       |

| ☐ INPUT BLOCK2 (PD/DIR/HSN  |                        | ABLE)                                                     |                   |                        | u                     | l .      |

| H level input voltage1      | V <sub>IH1</sub>       |                                                           | 2.0               | _                      | _                     | V        |

| L level input voltage1      | V <sub>IL1</sub>       |                                                           | 0                 | -                      | 0.8                   | V        |

| Input hysteresis voltage1   | V <sub>IHYS1</sub>     |                                                           | -                 | 0.13                   | -                     | V        |

| H level input voltage2      | V <sub>IH2</sub>       | V <sub>DD</sub> =5V                                       | 2.4               | -                      | _                     | V        |

| L level input voltage2      | V <sub>IL2</sub>       | V <sub>DD</sub> =5V                                       | 0                 | _                      | 0.8                   | V        |

| Input hysteresis voltage2   | V <sub>IHYS2</sub>     | V <sub>DD</sub> =5V                                       | -                 | 0.14                   | -                     | V        |

|                             |                        | PD, DIR, HSM, RESET, ENABLE=3.3V,                         | 45                |                        | 45                    |          |

| H level input current       | I <sub>IH</sub>        | per input                                                 | 15                | 33                     | 45                    | uA       |

| L level input current       | I <sub>IL</sub>        | PD, DIR, HSM, RESET, ENABLE=0V, per input                 | -200              | 0                      | +200                  | nA       |

| Input pull down resistance  | R <sub>DOWN</sub>      |                                                           | -                 | 100                    | -                     | kΩ       |

| Input pulse widths          | tp                     |                                                           | 2                 | -                      | -                     | us       |

| Data setup time             | t <sub>DS</sub>        |                                                           | 1                 | -                      | -                     | us       |

| Data hold time              | $t_DH$                 |                                                           | 1                 | -                      | -                     | us       |

| ☐ MOTOR OUTPUT BLOCK (C     | UT1A/OUT1E             | B/OUT2A/OUT2B)                                            |                   |                        |                       |          |

| Output ON resistance1       | R <sub>O1</sub>        | lo=500mA                                                  | -                 | 1.2                    | 1.45                  | Ω        |

| Output ON resistance2       | R <sub>O2</sub>        | V <sub>DD</sub> =5.0V, lo=500mA                           | -                 | 0.9                    | 1.25                  | Ω        |

| Output leak current         | I <sub>OLEAK</sub>     | ENABLE=0V,Vo=50V                                          | -                 | 1                      | 5                     | uA       |

| Delay time                  | t <sub>DELAY</sub>     | Attumon                                                   | -                 | 0.3                    | -                     | us       |

| Sense terminal leak current | I <sub>SENSELEAK</sub> | ENABLE=0V, V <sub>SENSE</sub> =1V(SENSE→GND)              | -                 | -                      | 1                     | uA       |

| ☐ MO OUTPUT (MO)            |                        |                                                           |                   |                        |                       |          |

| L level output voltage      | $V_{MO}$               | I <sub>MO</sub> =10mA                                     | -                 | 0.3                    | 0.5                   | V        |

| MO terminal leak current    | I <sub>MOLEAK</sub>    | V <sub>MO</sub> =5.5V                                     | -                 | -                      | 1                     | uA       |

| ☐ MO OUTPUT (ALARM)         | WOLD W                 | , mo                                                      |                   |                        | ı                     | <u> </u> |

| L level output voltage      | $V_{ALARM}$            | I <sub>ALARM</sub> =10mA                                  | _                 | 0.3                    | 0.5                   | V        |

| ALARM terminal leak current | I <sub>ALARMLEAK</sub> | V <sub>ALARM</sub> =5.5V                                  | _                 | -                      | 1                     | uA       |

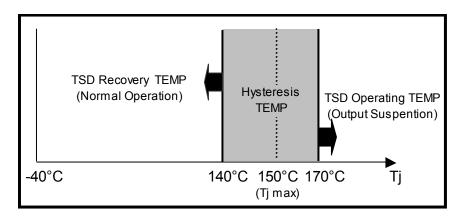

| ☐ THERMAL SHUTDOWN BLO      |                        | - ADAMI                                                   | 1                 | 1                      | 1                     |          |

| Thermal shutdown operating  |                        |                                                           |                   |                        |                       |          |

| temperature                 | T <sub>TSD1</sub>      |                                                           | -                 | 170                    | -                     | °C       |

| Thermal shutdown recovery   |                        |                                                           |                   |                        |                       |          |

| temperature                 | T <sub>TSD2</sub>      |                                                           | -                 | 140                    | -                     | °C       |

| Thermal shutdown hysteresis | $\Delta T_{TSD}$       |                                                           | _                 | 30                     | _                     | °C       |

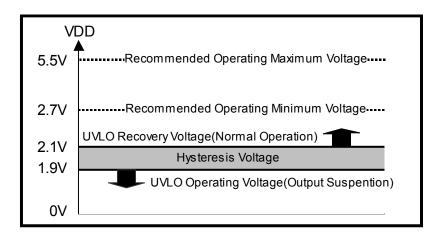

| ☐ UNDER VOLTAGE LOCK OL     |                        | <u> </u>                                                  | I                 |                        | 1                     |          |

| UVLO operating voltage      |                        |                                                           | 1.6               | 1.9                    | 2.2                   | V        |

| UVLO operating voltage      | V <sub>UVLO1</sub>     |                                                           | 1.0               | 2.2                    | 2.2                   | V        |

| UVLO hysteresis voltage     | V <sub>UVLO2</sub>     |                                                           | 0.2               | 0.3                    | 0.4                   | V        |

| OVEO HYSICIESIS VOILAGE     | $\Delta V_{UVLO}$      | 1                                                         | U.Z               | U.S                    | U. <del>4</del>       | V        |

### ☐ PIN/ CIRCUIT OPERATIONAL DEFINITION

◆ Logic Input Pins Operational Voltage Definition

♦ Logic Input Pins Timing Definition

## **NJW4351**

♦ Thermal Shutdown Operational Definition

♦ Under Voltage Protection Operational Definition

### ☐ TERMINAL STATUS

### STEP-Motor Stepping Pulse Input

| STEP          | Function                                    |

|---------------|---------------------------------------------|

| Negative Edge | -                                           |

| Positive Edge | Internal translator gose on every this edge |

| OPEN          | -                                           |

### HSM-HALF/FULL Step Mode Input

| HSM  | Function           |  |  |

|------|--------------------|--|--|

| Н    | HALF Step          |  |  |

| L    | FULL Step          |  |  |

| OPFN | FULL Step          |  |  |

| OPEN | (Inside PULL DOWN) |  |  |

#### **DIR-Direction Command Input**

|      | •                  |

|------|--------------------|

| DIR  | Function           |

| Н    | REVERSE            |

| L    | FORWARD            |

| OPFN | FORWARD            |

| OFEN | (Inside PULL DOWN) |

### **ENABLE-Enable Input**

| ENABLE | Function                                                                           |

|--------|------------------------------------------------------------------------------------|

| Н      | ACTIVE                                                                             |

| L      | OUT terminals are OFF, but internal logic circuit is ON.                           |

| OPEN   | OUT terminals are OFF , but<br>internal logic circuit is ON.<br>(Inside PULL DOWN) |

### **RESET-Reset Input**

| RESET | Function           |  |  |

|-------|--------------------|--|--|

| Н     | ACTIVE             |  |  |

| L     | RESET              |  |  |

| OPFN  | RESET              |  |  |

| OFEN  | (Inside PULL DOWN) |  |  |

### PD-Power Down State Input

| PD     | Function           |  |  |

|--------|--------------------|--|--|

| Н      | ACTIVE             |  |  |

| L      | RESET+POWER SAVING |  |  |

| OPFN   | RESET+POWER SAVING |  |  |

| OI LIN | (Inside PULL DOWN) |  |  |

### MO-Motor Origin Position Output

| MO | Function                        |

|----|---------------------------------|

| Н  | The translator is in noninitial |

|    | status                          |

| 1  | The translator is in initial    |

| L  | status                          |

### ALARM-Alarm Output

| ALARM | Function                                                   |

|-------|------------------------------------------------------------|

| Н     | Normal Operation                                           |

|       | OUT terminals are OFF, as the protection circuit operates. |

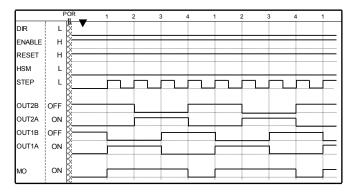

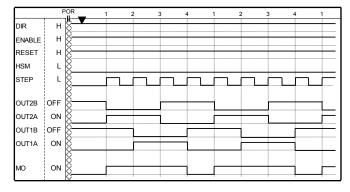

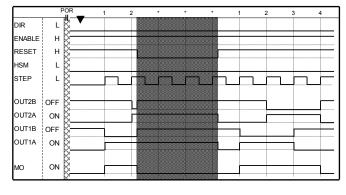

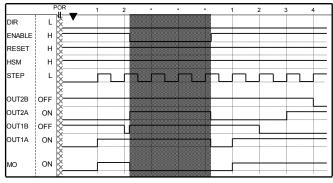

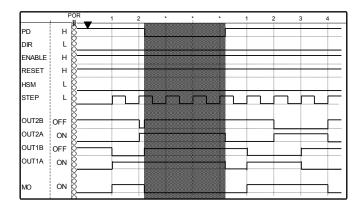

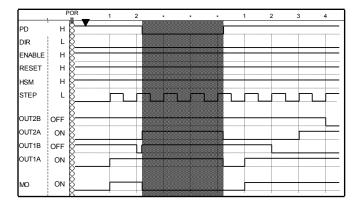

### ☐ TIMING CHART

| STEP  | After<br>POR | 1   | 2   | 3   | 4   |

|-------|--------------|-----|-----|-----|-----|

| OUT2B | OFF          | OFF | ON  | ON  | OFF |

| OUT2A | ON           | ON  | OFF | OFF | ON  |

| OUT1B | OFF          | ON  | ON  | OFF | OFF |

| OUT1A | ON           | OFF | OFF | ON  | ON  |

| MO    | ON           | OFF | OFF | OFF | ON  |

Fig.1 Full Step Mode / Forward Direction Sequence

| STEP  | After<br>POR | 1   | 2   | 3   | 4   |

|-------|--------------|-----|-----|-----|-----|

| OUT2B | OFF          | ON  | ON  | OFF | OFF |

| OUT2A | ON           | OFF | OFF | ON  | ON  |

| OUT1B | OFF          | OFF | ON  | ON  | OFF |

| OUT1A | ON           | ON  | OFF | OFF | ON  |

| MO    | ON           | OFF | OFF | OFF | ON  |

Fig.2 Full Step Mode / Reverse Direction Sequence

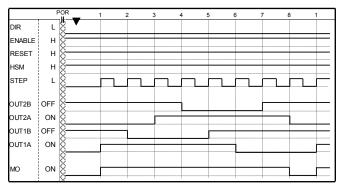

| STEP  | After<br>POR | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   |

|-------|--------------|-----|-----|-----|-----|-----|-----|-----|-----|

| OUT2B | OFF          | OFF | OFF | OFF | ON  | ON  | ON  | OFF | OFF |

| OUT2A | ON           | ON  | ON  | OFF | OFF | OFF | OFF | OFF | ON  |

| OUT1B | OFF          | OFF | ON  | ON  | ON  | OFF | OFF | OFF | OFF |

| OUT1A | ON           | OFF | OFF | OFF | OFF | OFF | ON  | ON  | ON  |

| MO    | ON           | OFF | ON  |

Fig.3 Half Step Mode / Forward Direction Sequence

|        | Р   | POR .    | 1 2 | 2 3 | 3 / | 4 5 | 5 ( | 6 7 | 7                 | 8 | 1        |

|--------|-----|----------|-----|-----|-----|-----|-----|-----|-------------------|---|----------|

| DIR    | Н   |          |     |     |     |     | _   |     |                   |   | $\vdash$ |

| ENABLE | н   | 8        |     |     |     |     |     |     |                   |   |          |

| RESET  | н   | <u> </u> |     |     |     |     |     |     |                   |   | _        |

| HSM    | н   | <u> </u> |     |     |     |     |     |     |                   |   | -        |

| STEP   | L   | 8        |     |     |     |     | h   |     | $\overline{\Box}$ |   |          |

|        |     | <u> </u> |     |     |     |     |     |     |                   |   |          |

| OUT2B  | OFF | <u> </u> |     |     |     |     |     |     |                   |   | $\vdash$ |

| OUT2A  | ON  | 8        |     |     |     |     |     | i   |                   |   |          |

| OUT1B  | OFF | <u> </u> |     |     |     |     |     |     |                   |   |          |

| OUT1A  | ON  | 8        |     |     |     |     |     |     |                   | i |          |

| МО     | ON  | <u> </u> |     |     |     |     |     |     |                   |   |          |

| STEP  | After<br>POR | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   |

|-------|--------------|-----|-----|-----|-----|-----|-----|-----|-----|

| OUT2B | OFF          | OFF | ON  | ON  | ON  | OFF | OFF | OFF | OFF |

| OUT2A | ON           | OFF | OFF | OFF | OFF | OFF | ON  | ON  | ON  |

| OUT1B | OFF          | OFF | OFF | OFF | ON  | ON  | ON  | OFF | OFF |

| OUT1A | ON           | ON  | ON  | OFF | OFF | OFF | OFF | OFF | ON  |

| MO    | ON           | OFF | ON  |

Fig.4 Half Step Mode / Reverse Direction Sequence

\* When ENABLE is active OUT terminals are OFF, but internal logic circuit is ON.

Fig.5 Full Step Mode / Enable Sequence

\* When ENABLE is active OUT terminals are OFF, but internal logic circuit is ON.

Fig.6 Half Step Mode / Enable Sequence

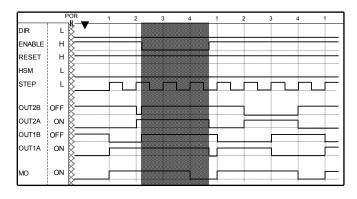

\* When RESET is active OUT terminals are OFF, and internal logic circuit is to reset.

Fig.7 Full Step Mode / Reset Sequence

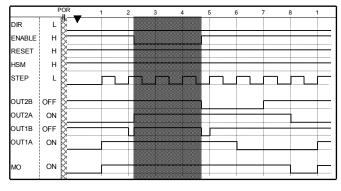

\* When RESET is active OUT terminals are OFF, and internal logic circuit is to reset.

Fig.8 Half Step Mode / Rest Sequence

\* When PD is active it forces all settings to initialize and be in stand-by mode, and MO is to be low.

Fig.9 Full Step Mode / PD Sequence

\* When PD is active it forces all settings to initialize and be in stand-by mode, and MO is to be low.

Fig.10 Full Step Mode / PD Sequence

#### **□ FUNCTION DESCRIPTION**

The NJW4351 is designed for a high-performance constant-voltage unipolar stepper motor.

Using a general-purpose STEP&DIR motion controller, the device can easily control a stepper motor when combined with a pulse generator.

The maximum value of the phase output is 55 V that keeps the voltage margin of the motor from exceeding the limit, which is a common problem with unipolar winding systems. It simplifies the design of power control circuits during phase turn-off.

#### ☐ LOGIC INPUT BLOCK

All inputs are LS-TTL compatible. Input Block1 (STEP) has Schmitt Comparator to keep the thresh voltage unchanged even if logic supply voltage applied to it varies. It produces hesteresis voltage for noise immunity. Input Block2 (PD, DIR, HSM, RESET, ENABLE) has Schmitt Inverter for the main purpose of noise immunity.

Inputs are internally connected to GND by pull-down resistances, being open, the device recognizes to be low.

#### • STEP - Stepping Pulse

The Translator starts counting on every positive edge of the STEP. In full step mode, the pulse turns the stepper motor at the basic step angle. In half step mode, two pulses are required to turn the motor at the basic step angle.

The DIR (direction) signal and HSM (half/full mode) are latched to the STEP positive edge and must therefore be established before the start of the positive edge.

### • DIR - Direction

The DIR signal determines the step direction. The direction of the stepper motor depends on how the NJW4351 is connected to the motor. DIR can be modified anytime, it miss-steps when it is simultaneous with the positive edge.

### • HSM - Half/full Step Mode Switching

This signal determines whether the stepper motor runs at half step or full step mode. The Translator is set to half step mode when HSM is low. Like DIR, HSM can be modified anytime but not when its simultaneous with the positive edge.

### ENABLE – Phase Output Off

All phase outputs are turned off when ENABLE goes high reducing power consumption.

### RESET

A two-phase stepper motor repeats the same winding energizing sequence every angle that is a multiple of four of the basic step. The Translator is repeated every four pulses in full step mode and every eight pulses in half step mode.

When RESET is low, the Translator is initialized and the phase outputs turn-off.

When returning to high, the phase outputs are set to the initial energizing pattern output status.

#### • PD-Power Down

When PD goes low, it forces all settings to initialize and be in stand-by mode.

AND MO is to be low.

## NJW4351

#### □ POR - Power On And Reset Function

The POR connected to VDD is to prevent miss-step under unstable condition of the inputting of logic supply voltage VDD.

After inputting VDD, the phase outputs are set to the initial energizing pattern output status.

### ☐ PHASE OUTPUT BLOCK

The phase output block consists of four open-drain DMOS FET capable of sinking max 1.5A.

### ☐ MO – Motor Origin Monitor

In initialized position of the Translator, MO output low to indicate to external devices that it is the initial energizing pattern output status.

#### □ PRECAUTIONS

- 1. Never disconnect the device or PC-board when power is supplied.

- 2. Remember that excessive voltages might be generated by motor, even though clamping diodes are used.

- 3. Choose a motor that is proportional to the current you need to establish desired torque. A high supply voltage will gain better stepping performance. If the motor is not specified for the VMM voltage, a current limiting resistor will be necessary to connect in series with center tap. This changes the L/R time constant.

- 4. Avoid VMM and VDD power supplies with serial diodes (without filter capacitor) and common ground with VDD

- 5. To change actual motor rotation direction, exchange motor connections at OUT1A and OUT1B (OUT2A and OUT2B).

- 6. Half-stepping

In the half-step mode, the power input to the motor alternates between one or two phase windings. In half-step mode, motor resonances are reduced. In a two-phase motor, the electrical phase shift between the windings is 90 degrees. The torque developed is the vector sum of two windings energized. Therefore, when only one winding is energized, which is the case in half-step mode for every second step, the torque of the motor is reduced by approximately 30%. This causes a torque ripple.

7. Drive Circuits

High-performance stepper motor operation requires windings to be energized immediately at phase turn-on and quickly turned off when not in use.

8. Phase Turn-off Considerations

When the winding current is turned off, induced high voltage spike will damage the drive circuits if not properly suppressed.

Refer to the description of turn-off circuit as follow.

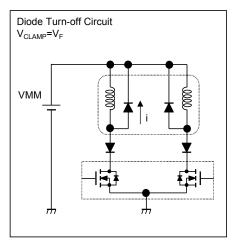

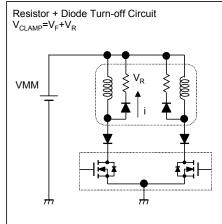

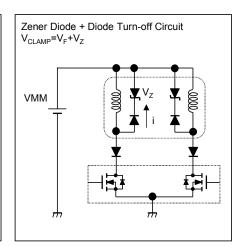

#### < About the turn-off circuit >

There are various turn-off circuit methods for the purpose of extracting the speed performance of the motor.

The turn-off time of motor current depends on the clamp voltage of the turn-off circuit.

Therefore, it is necessary to select an appropriate turn-off method according to the motor speed.

However, the larger the clamp voltage of the turn-off circuit, the negative voltage is generated by electromagnetic induction to the other winding.

| Method                 | Diode Turn-off | Resistor + Diode Tum-off | Zener Diode + Diode Turn-off |  |  |  |

|------------------------|----------------|--------------------------|------------------------------|--|--|--|

| External parts scale   | Small          | Medium                   | Large                        |  |  |  |

| Motor Speed            | Low            | High                     |                              |  |  |  |

| Negative voltage value | Low            | Middle to High           |                              |  |  |  |

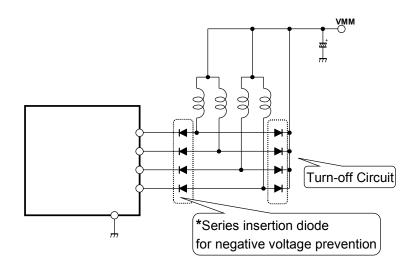

### < Prevention of Malfunction for Negative Voltage >

In unipolar motor drive, when switching the winding current electromagnetically coupled, the output pin may become below the GND potential due to long wiring of the motor, routing of the GND wiring of the mounting board, turn-off circuit type, and so on.

Due to the nature of the monolithically structured IC, when a large negative voltage is applied to the output pin, the inside of the IC may cause unexpected operation, which may cause circuit malfunction (miss step).

Therefore, in order to reliably prevent circuit malfunction due to negative voltage, it is recommended to insert a diode in series at the output pin and take countermeasures.

### **□ APPLICATION CIRCUIT**

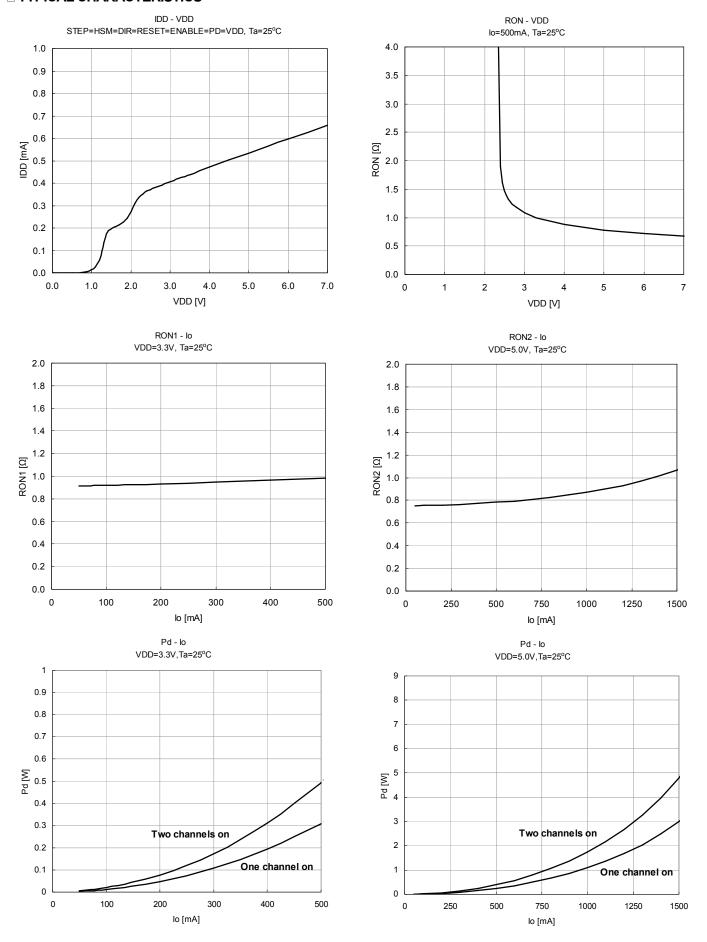

### ☐ TYPICAL CHARACTERISTICS

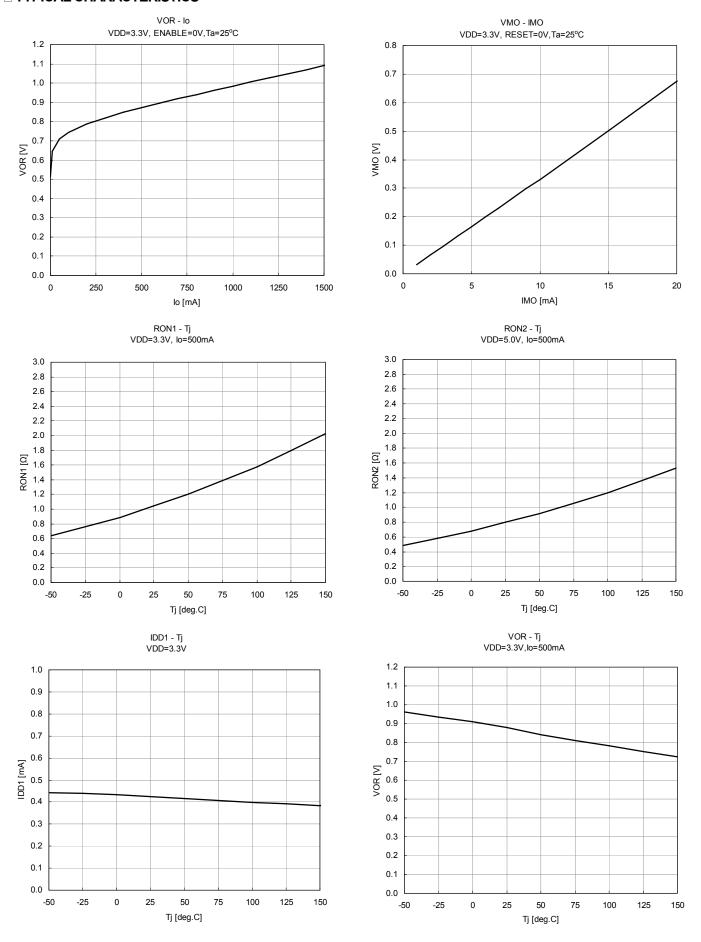

### ☐ TYPICAL CHARACTERISTICS

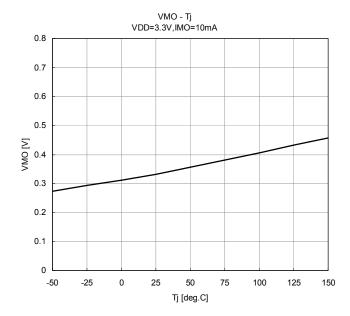

### ☐ TYPICAL CHARACTERISTICS

[CAUTION]

The specifications on this databook are only given for information, without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.