# Oki, Network Solutions for a Global Society

**FEDL6588-6588L-04** Issue Date: Jan. 25, 2002

# OKI Semiconductor MSM6588/6588L

ADPCM Solid-State Recorder (for Serial Registers)

# **GENERAL DESCRIPTION**

The MSM6588/6588L is a "solid-state recorder" IC developed using the ADPCM method. By externally connecting a microphone, a speaker, a speaker amplifier and a serial register or other memory device to store ADPCM data, it can record and playback voice data like a tape recorder.

The MSM6588/6588L has a stand-alone mode and a microcontroller interface mode. In stand-alone mode, record or playback can be selected via a pin and it is possible to control the MSM6588 at a simple drive timing. In microcontroller interface mode, record/playback can be controlled by commands from the microcontroller, the MSM6588/6588L is much more flexible in microcontroller mode than in stand-alone mode. In addition, recording and playback with fixed message are easily implemented by connecting a serial voice ROM.

The MSM6588 and the MSM6588L support 5 V and 3 V operation respectively.

# **FEATURES**

- 12-bit A/D converter

- 12-bit D/A converter

- Microphone amplifier

- Low-pass filter (LPF)

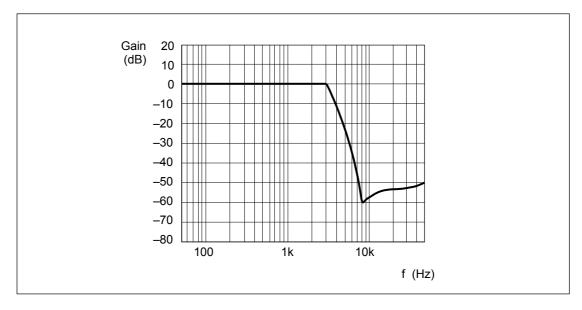

- Filter characteristics –40 dB/oct

- Serial registers

- MSM6588

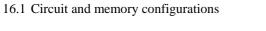

Up to four 1M bit serial registers (MSM6389C) can be driven directly One 512K bit serial register (MSM6587) can be driven directly

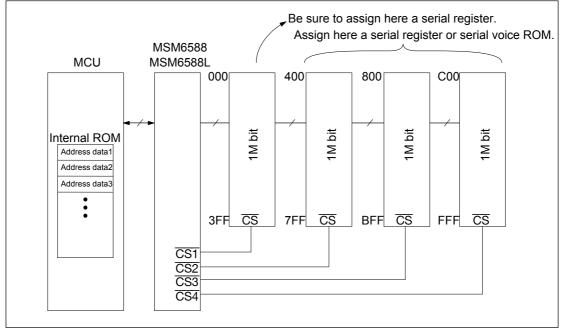

One 256K bit serial register (MSM6586) can be driven directly

MSM6588L

Up to four 1M bit serial registers (MSM63V89C) can be driven directly

• Serial Voice ROMs

1M bit serial voice ROM (MSM6595A-xxx)

- 2M bit serial voice ROM (MSM6596A-xxx)

- 3M bit serial voice ROM (MSM6597A-xxx)

- Maximum recording time

- 262 seconds (when using 3-bit ADPCM, 5.3 kHz sampling)

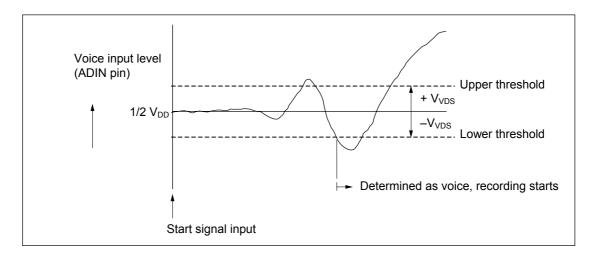

- Voice triggered starting

- Pause function

- Master clock frequency: 4.096 to 8.192 MHz

- Power supply voltage

- MSM6588: Single 5 V Power supply

- MSM6588L: Single 3 V Power supply

- Package options:

| 44-pin plastic QFP  | (QFP44-P-910-0.80-2K)  | (MSM6588GS-2K)  |

|---------------------|------------------------|-----------------|

| 44-pin plastic QFP  | (QFP44-P-910-0.80-2K)  | (MSM6588LGS-2K) |

| 44-pin plastic TQFP | (TQFP44-P-1010-0.80-K) | (MSM6588LTB)    |

#### MSM6588/6588L

#### • Differences between MSM6588 and MSM6588L

The major differences between the MSM6588 and the MSM6588L are shown below.

| Parameter                                          | MSM6588                                                                     | MSM6588L                                                                     |

|----------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Operating voltage                                  | 3.5 to 5.5 V                                                                | 2.7 to 3.6 V                                                                 |

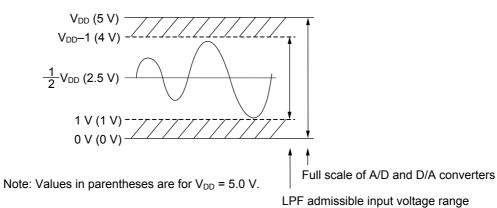

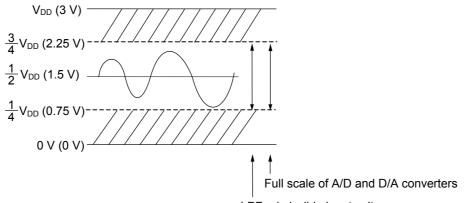

| Full scale of A/D and D/A converters               | 0 to $V_{DD}$                                                               | $\frac{1}{4}$ V <sub>DD</sub> to $\frac{3}{4}$ V <sub>DD</sub>               |

| Voice detection level for voice triggered starting | $\pm \frac{V_{DD}}{64}$ , $\pm \frac{V_{DD}}{32}$ , $\pm \frac{V_{DD}}{16}$ | $\pm \frac{V_{DD}}{128}$ , $\pm \frac{V_{DD}}{64}$ , $\pm \frac{V_{DD}}{32}$ |

| External only register                             | 1M bits (MSM6389C)<br>512K bits (MSM6587)<br>256K bits (MSM6586)            | 1M bits (MSM63V89C)                                                          |

#### 1. Characteristics in stand-alone mode

- 3-bit ADPCM

- Sampling frequency:

- 5.3 kHz or 8.0 kHz (when the oscillator operates at 4.096 MHz)

- 10.6 kHz or 16.0 kHz (when the oscillator operates at 8.192 MHz)

- Number of phrases: 1, 2, 4 or 8

#### 2. Characteristics in microcontroller interface mode

- 3-bit/4-bit ADPCM selectable

- Sampling frequency:

4.0 kHz, 5.3 kHz, 6.4 kHz or 8.0 kHz (when the oscillator operates at 4.096 MHz)

- 8.0 kHz, 10.6 kHz, 12.8 kHz or 16.0 kHz (when the oscillator operates at 8.192 MHz)

- Condition setting, start, and stop of record/playback controllable by 13 commands.

# CONTENTS

| GENERAL DESCRIPTION                                                                    | 1  |

|----------------------------------------------------------------------------------------|----|

| FEATURES                                                                               | 1  |

| BLOCK DIAGRAM                                                                          | 6  |

| Stand-Alone Mode                                                                       |    |

| Microcontroller Interface Mode                                                         | 7  |

| PIN CONFIGURATION (TOP VIEW)                                                           | 8  |

| 1. Stand-alone mode (MCUM pin = "L")                                                   |    |

| 2. Microcontroller interface mode (MCUM pin = "H")                                     | 9  |

| PIN DESCRIPTIONS                                                                       |    |

| Common Functions in Stand-Alone Mode and Microcontroller Interface Mode                |    |

| Stand-Alone Mode                                                                       |    |

| Microcontroller Interface Mode                                                         |    |

| ABSOLUTE MAXIMUM RATINGS (for MSM6588 (5 V Version))                                   |    |

| RECOMMENDED OPERATING CONDITIONS (for MSM6588 (5 V Version))                           |    |

| ELECTRICAL CHARACTERISTICS (for MSM6588 (5 V Version))                                 |    |

| DC Characteristics                                                                     |    |

| Analog Characteristics                                                                 |    |

| AC Characteristics                                                                     |    |

| 1. Common characteristics in stand-alone mode and microcontroller interface mode       |    |

| 2. Stand-alone mode                                                                    |    |

| 3. Microcontroller interface mode                                                      |    |

| ABSOLUTE MAXIMUM RATINGS (for MSM6588L (3 V Version))                                  |    |

| RECOMMENDED OPERATING CONDITIONS (for MSM6588L (3 V Version))                          |    |

| ELECTRICAL CHARACTERISTICS (for MSM6588L (3 V Version))                                |    |

| DC Characteristics                                                                     |    |

| Analog Characteristics                                                                 |    |

| AC Characteristics                                                                     |    |

| 1. Common characteristics in stand-alone mode and microcontroller interface mode       |    |

| 2. Stand-alone mode                                                                    |    |

| 3. Microcontroller interface mode                                                      |    |

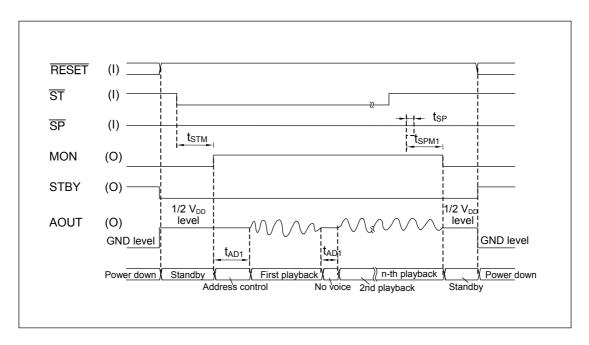

| TIMING DIAGRAMS                                                                        |    |

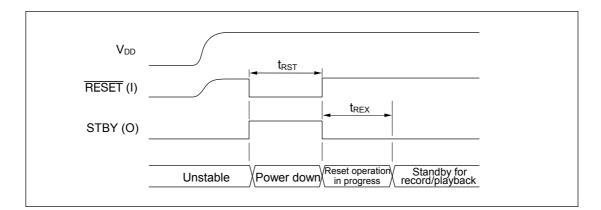

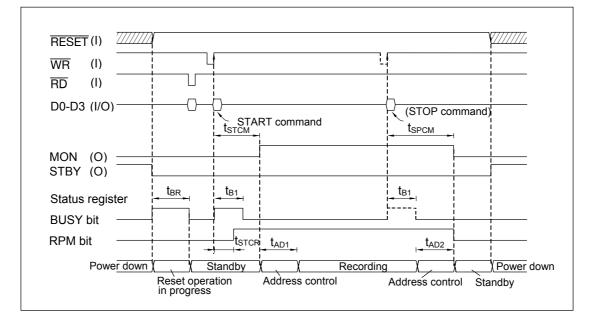

| Reset Function and Power Down Function                                                 |    |

| 1. Stand-alone mode when the PDMD pin is "L"                                           |    |

| 2. Stand-alone mode when the PDMD pin is "H" and in microcontroller interface mode     |    |

| Stand-alone Mode                                                                       |    |

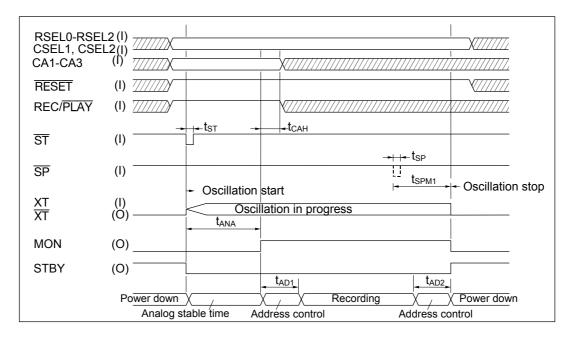

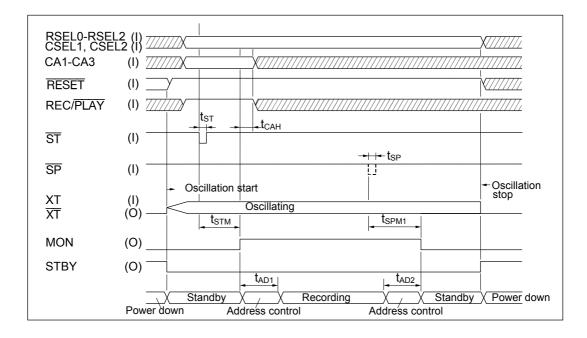

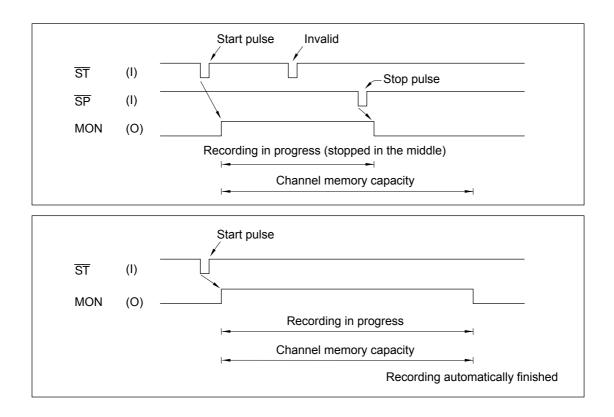

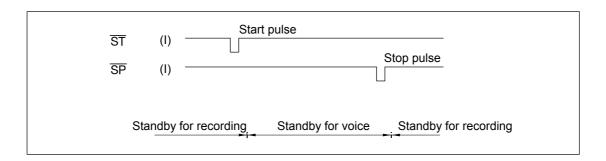

| 1. Timing during recording (PDMD pin = "L", VDS pin = "L")                             |    |

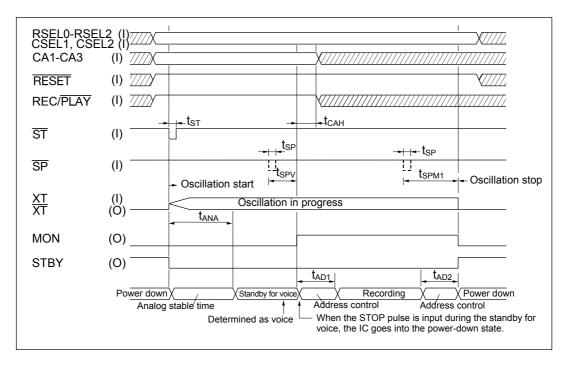

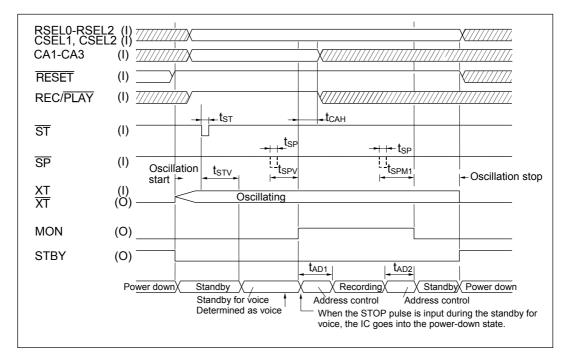

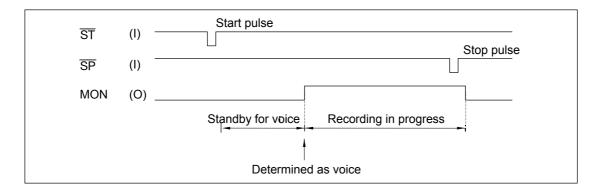

| 2. Timing during recording by voice triggered starting (PDMD pin = "L", VDS pin = "H") |    |

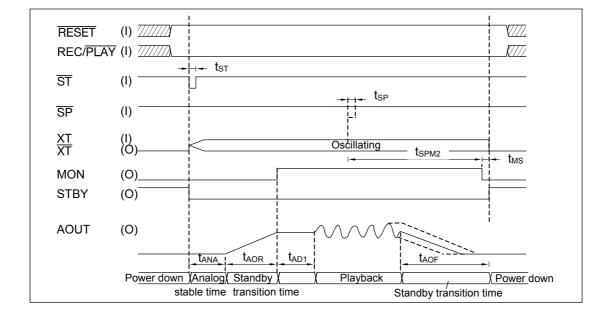

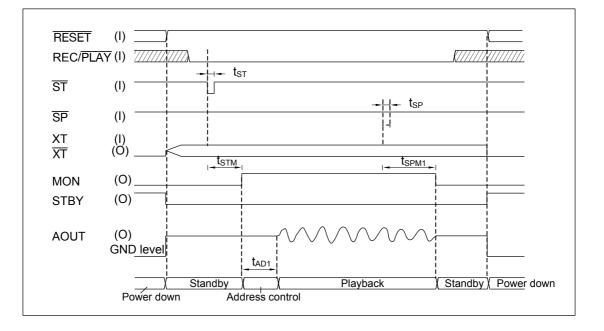

| 3. Timing during playback (PDMD pin = "L")                                             |    |

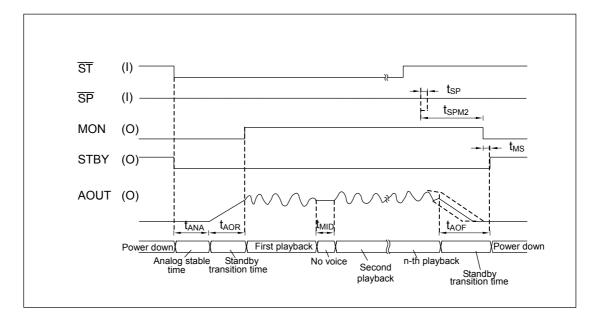

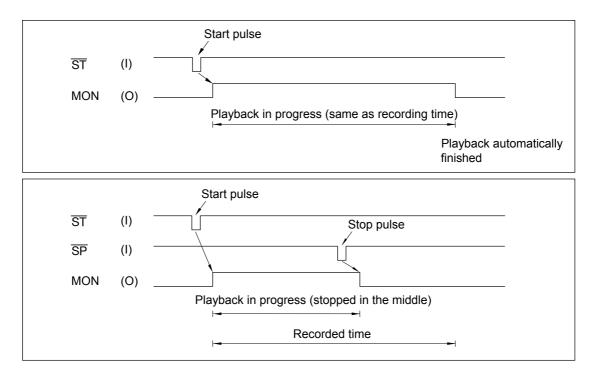

| 4. Timing during repeated playback (PDMD pin = "L")                                    |    |

| 5. Timing during recording (PDMD pin = "H", VDS pin = "L")                             |    |

| 6. Timing during recording by voice triggered starting (PDMD pin = "H", VDS pin = "H") |    |

| 7. Timing during playback (PDMD pin = "H")                                             |    |

| 8. Timing during repeated playback (PDMD pin = "H")                                    |    |

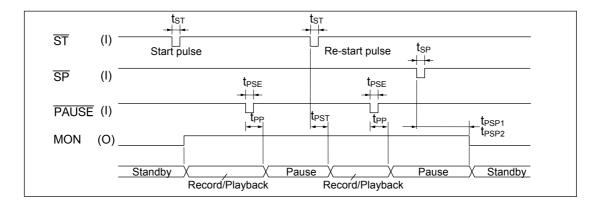

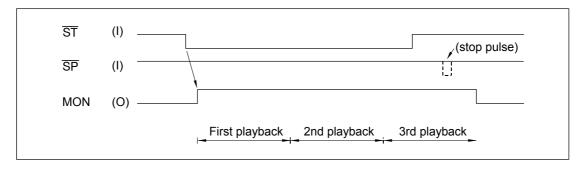

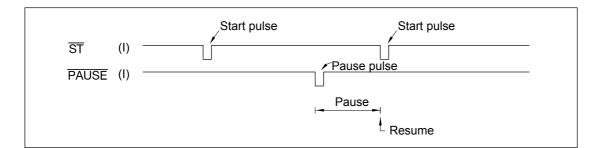

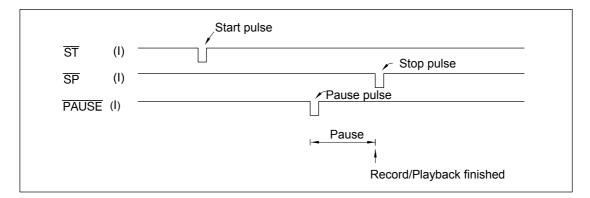

| 9. Timing of pause in record/playback                                                  | 29 |

# MSM6588/6588L

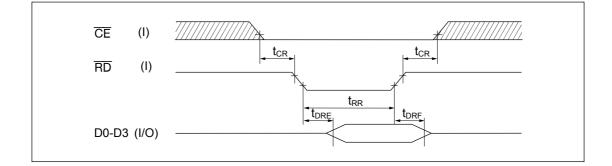

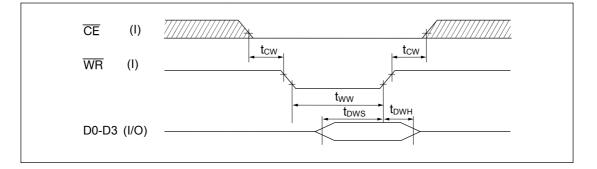

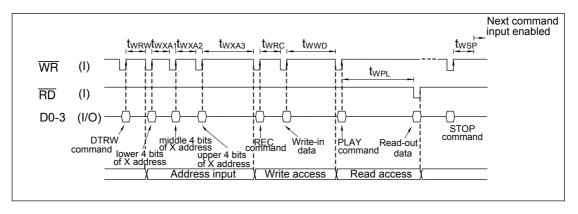

| Microcontroller Interface                                                            | . 30 |

|--------------------------------------------------------------------------------------|------|

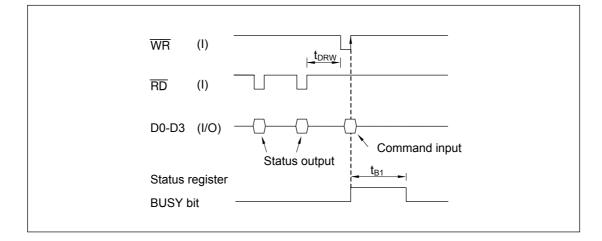

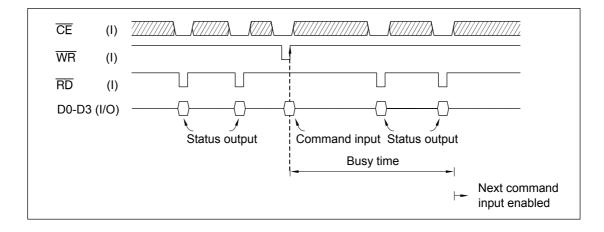

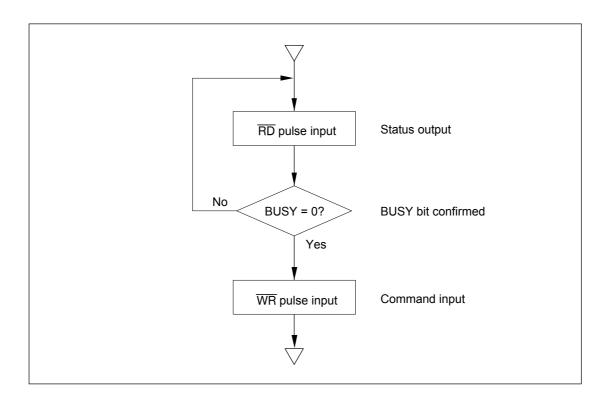

| 1. Data read (RD pulse)                                                              | . 30 |

| 2. Data write (WR pulse)                                                             | . 30 |

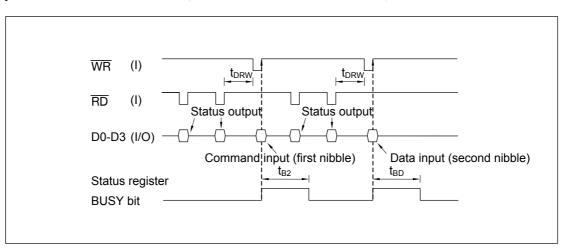

| 3. Input method of 1 nibble command (NOP, PAUSE, PLAY, REC, START and STOP commands) | . 31 |

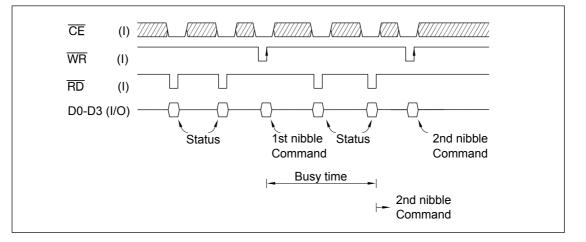

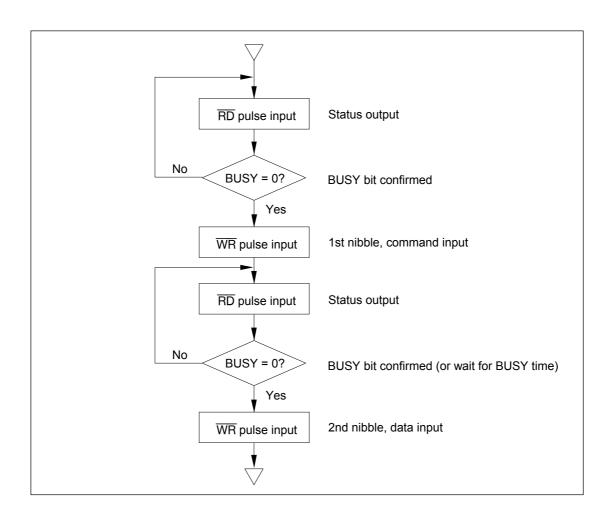

| 4. Input method of 2 nibble command (SAMP, CHAN and VDS commands)                    |      |

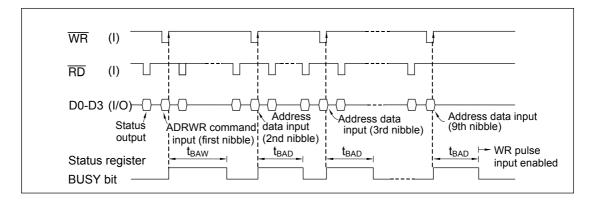

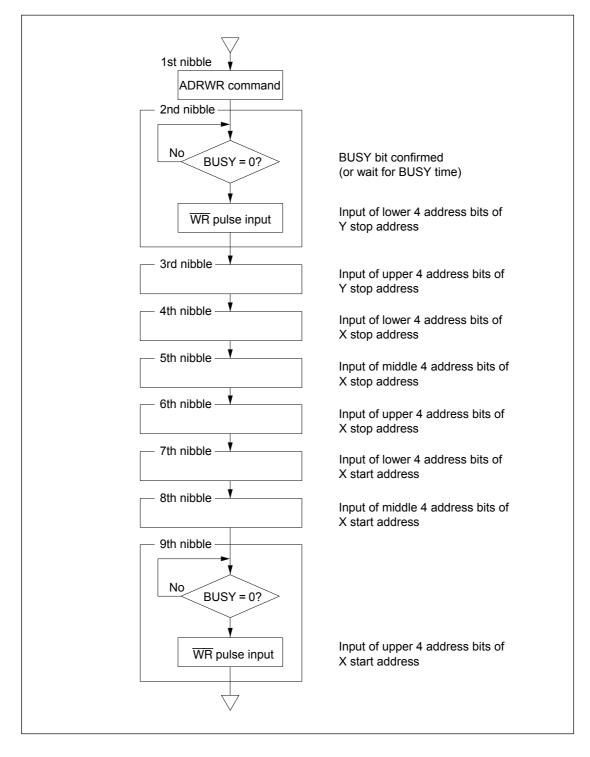

| 5. Input method of ADRWR command                                                     |      |

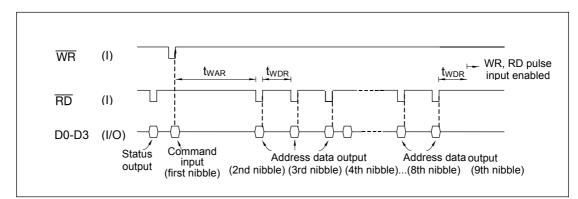

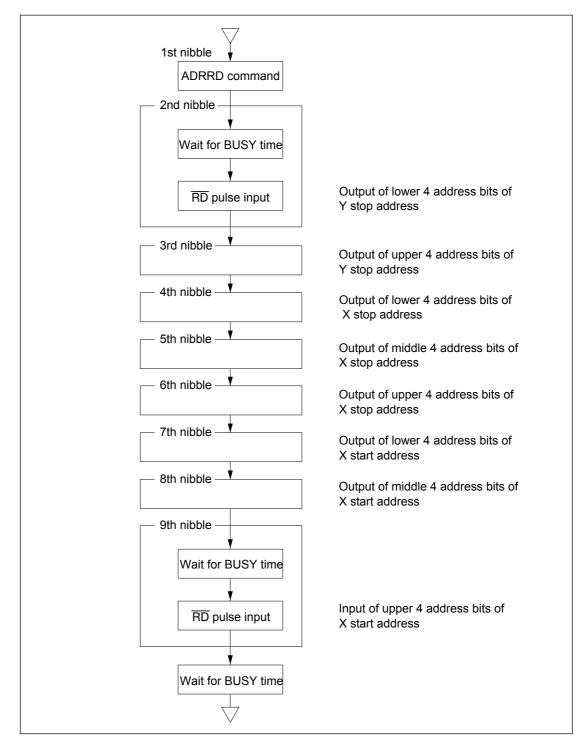

| 6. Input method of ADRRD command                                                     | . 32 |

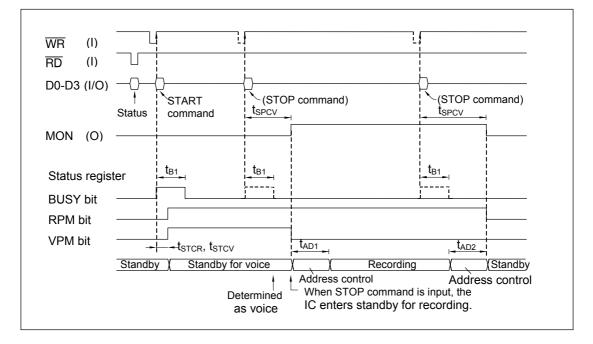

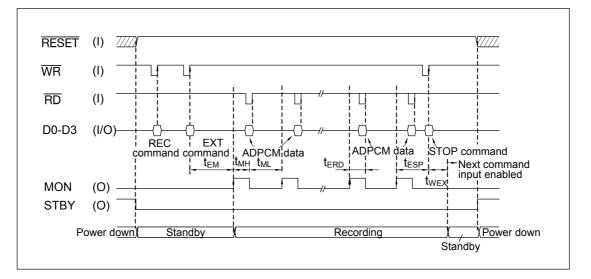

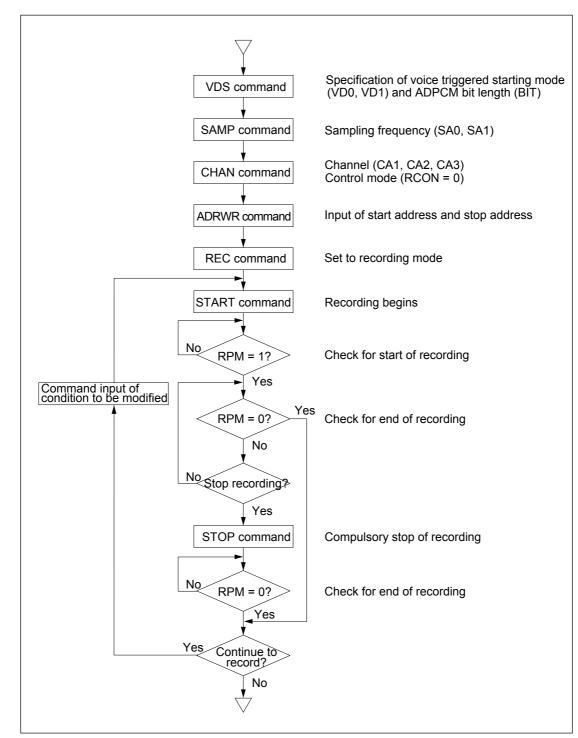

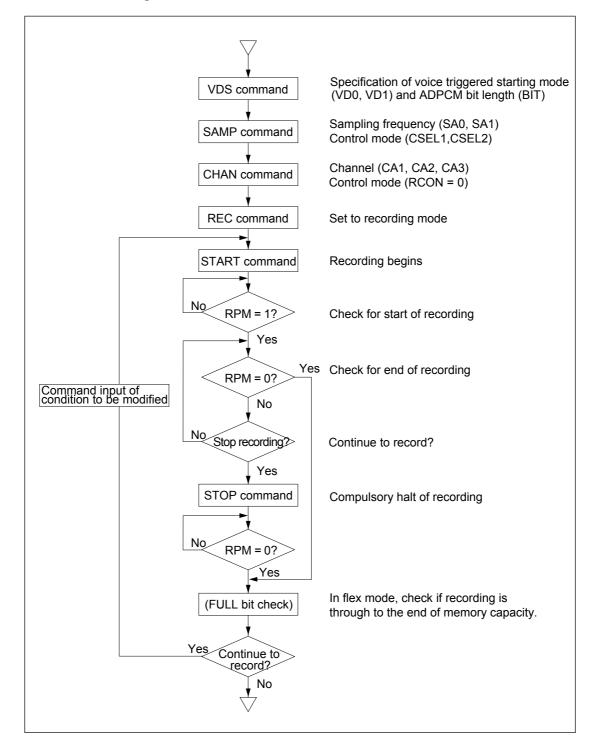

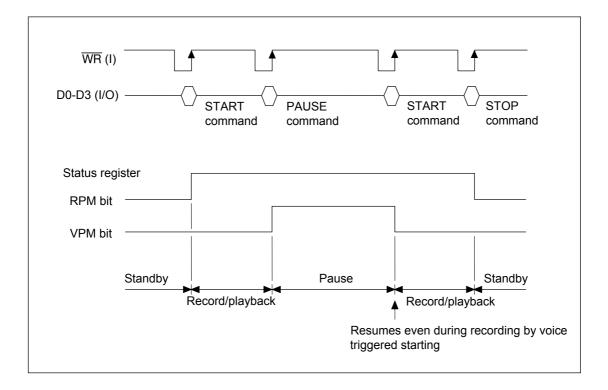

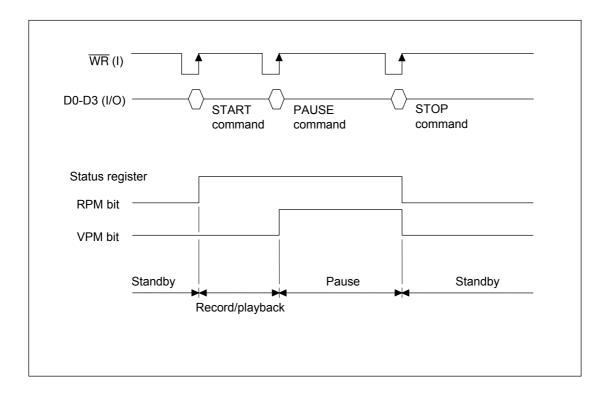

| 7. Recording method by START command                                                 | . 33 |

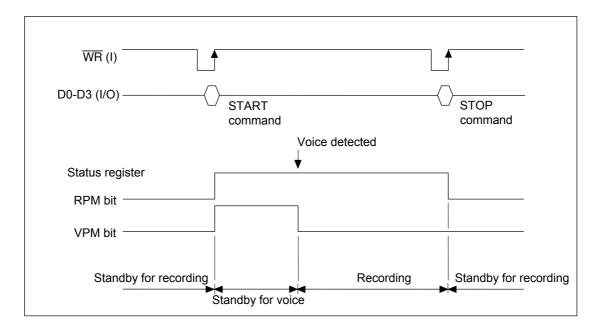

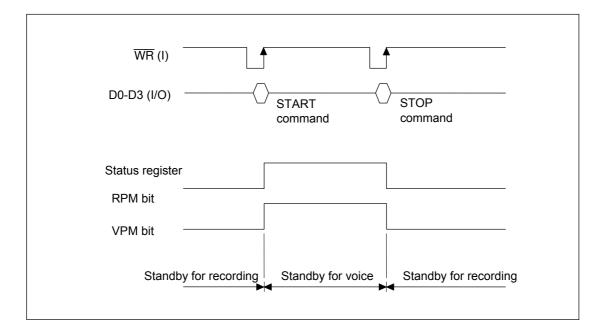

| 8. Timing of voice triggered starting                                                | . 33 |

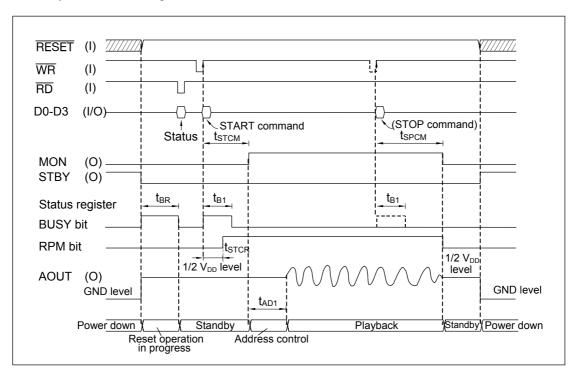

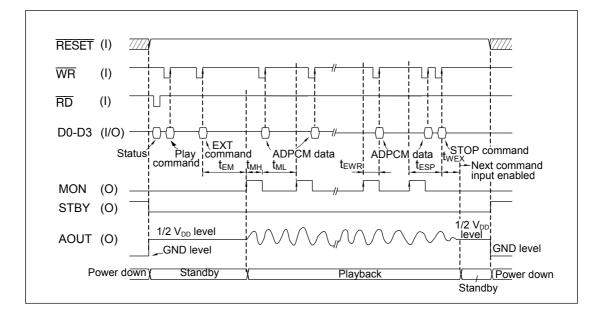

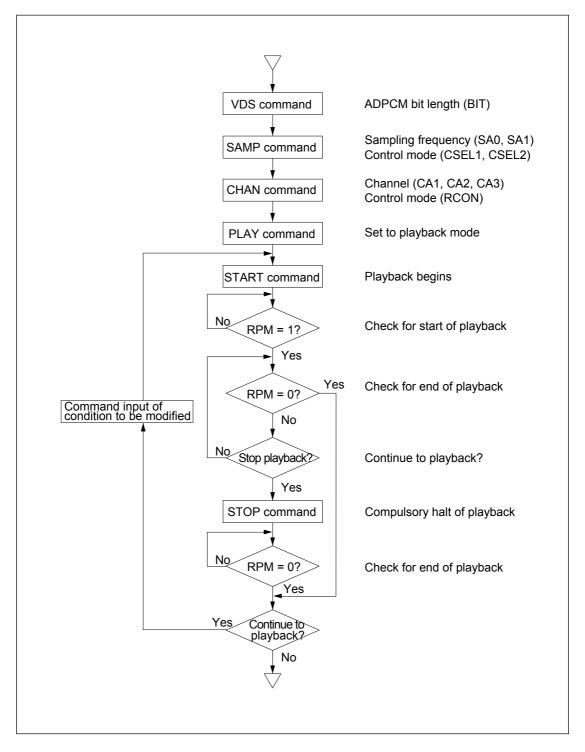

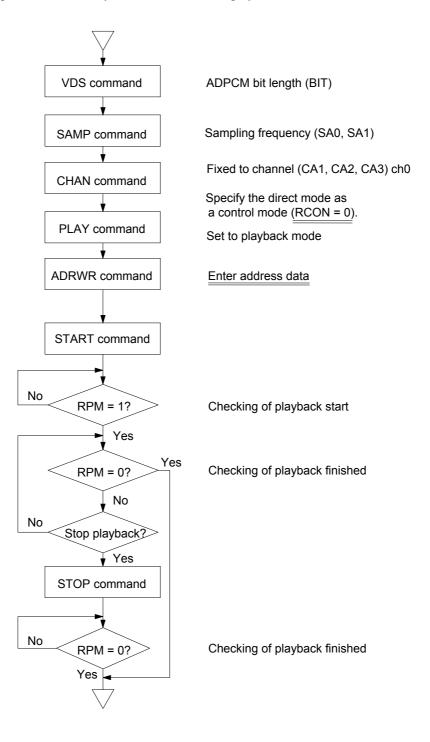

| 9. Playback method using START command                                               | . 34 |

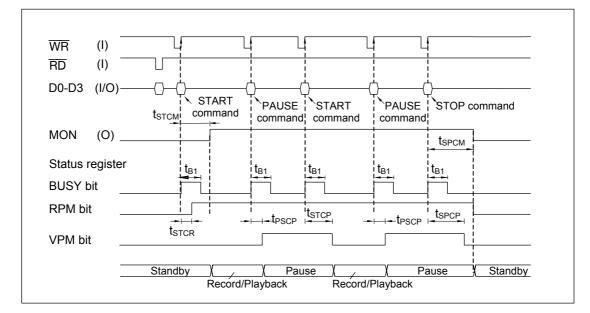

| 10. Timing of pause in record/playback using PAUSE command                           | . 34 |

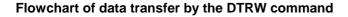

| 11. Timing of data transfer by DTRW command                                          |      |

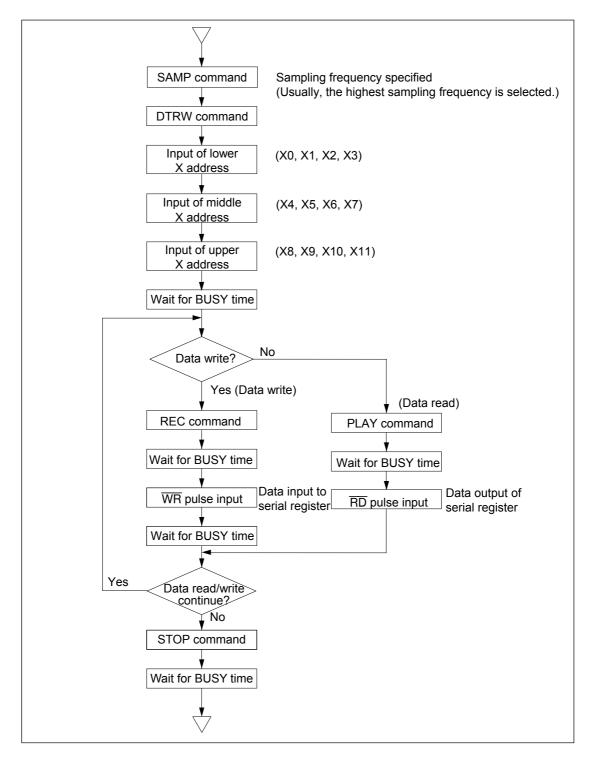

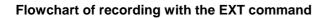

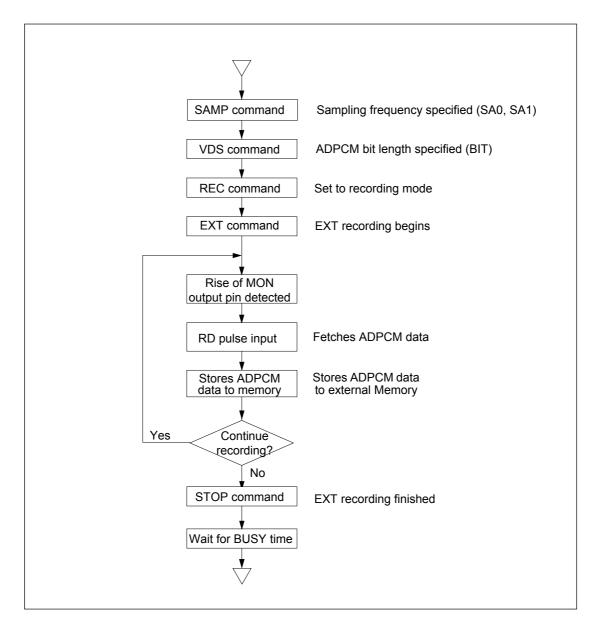

| 12. Timing of recording by EXT command                                               |      |

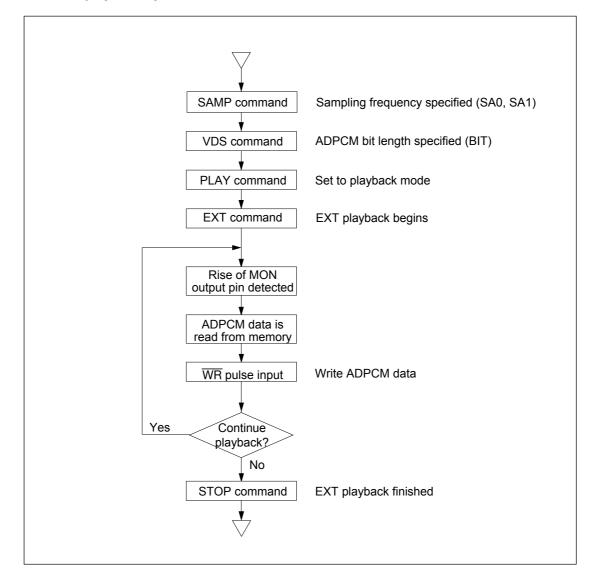

| 13. Timing of playback by EXT command                                                |      |

| FUNCTIONAL DESCRIPTION                                                               |      |

| Recording Time and Memory Capacity                                                   |      |

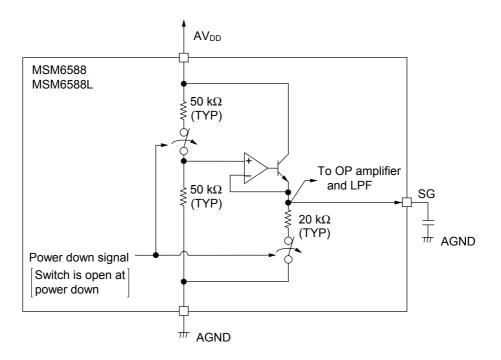

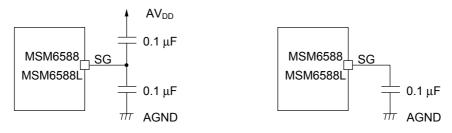

| Configuring SG pin                                                                   |      |

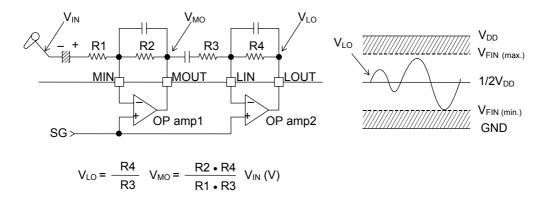

| Analog Input Amplifier Circuit                                                       |      |

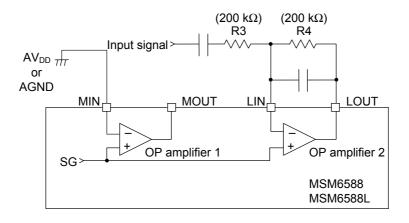

| Connection of LPF Circuit Peripherals                                                |      |

| LPF Characteristics                                                                  |      |

| Full Scale of A/D and D/A Converters                                                 |      |

| Voice Triggered Starting                                                             |      |

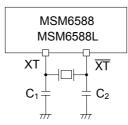

| How to Connect an Oscillator                                                         |      |

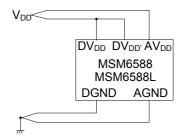

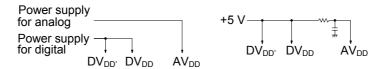

| How to Connect Power Supply                                                          |      |

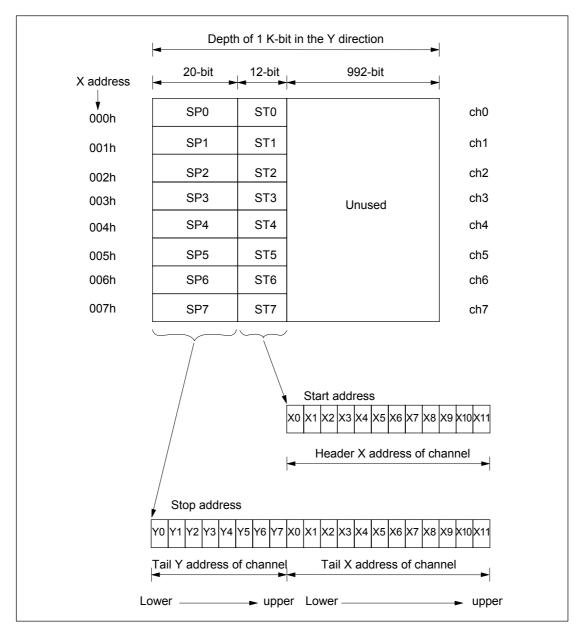

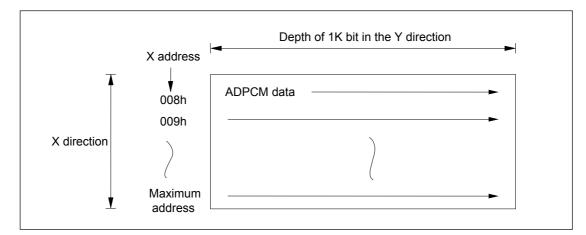

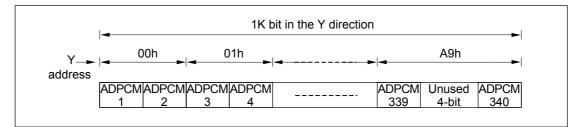

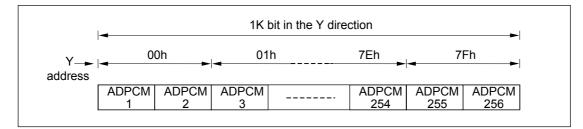

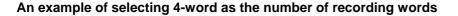

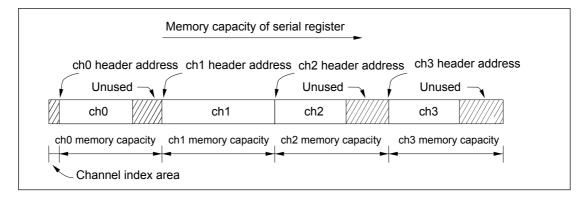

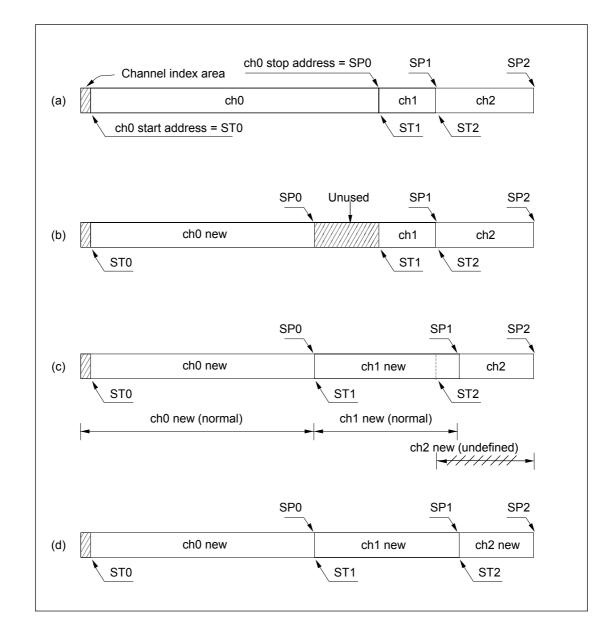

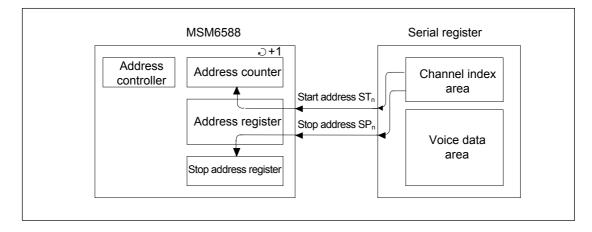

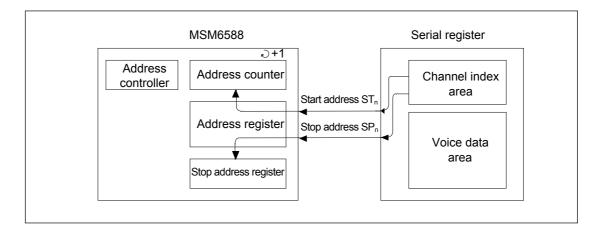

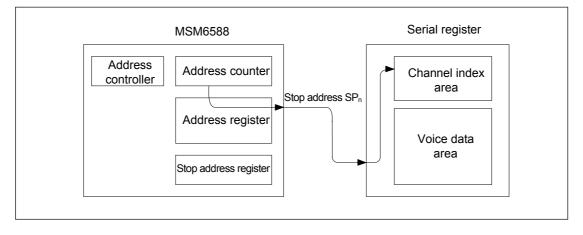

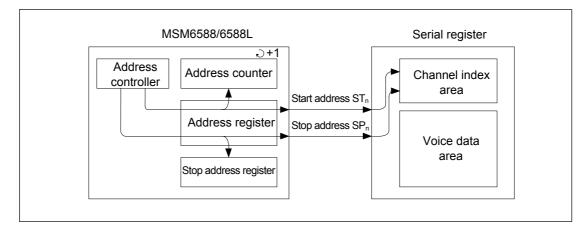

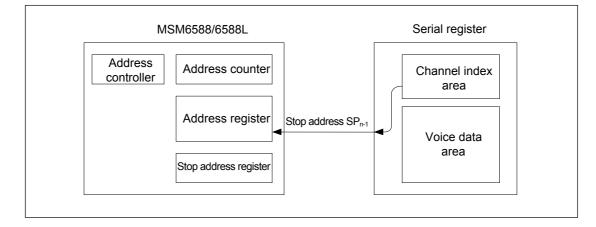

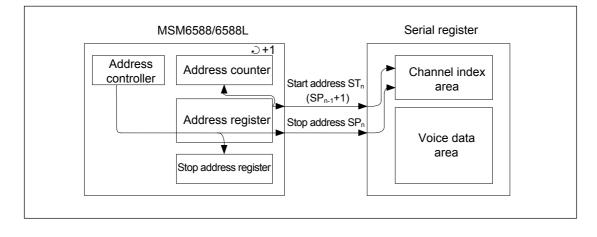

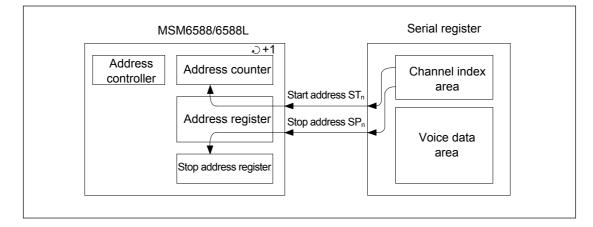

| Data Configuration of External Serial Registers                                      |      |

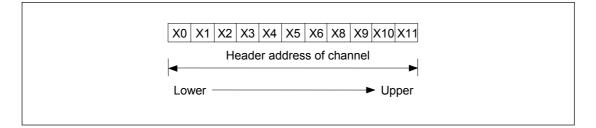

| 1. Channel index area                                                                |      |

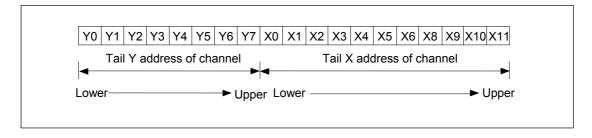

| 2. Voice (ADPCM) data area                                                           |      |

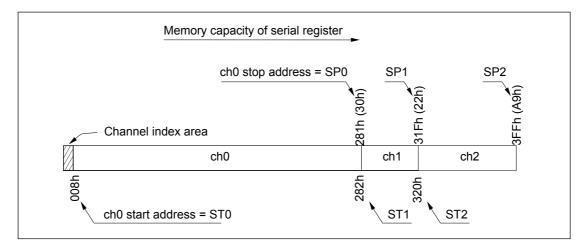

| Selection of Serial Registers                                                        |      |

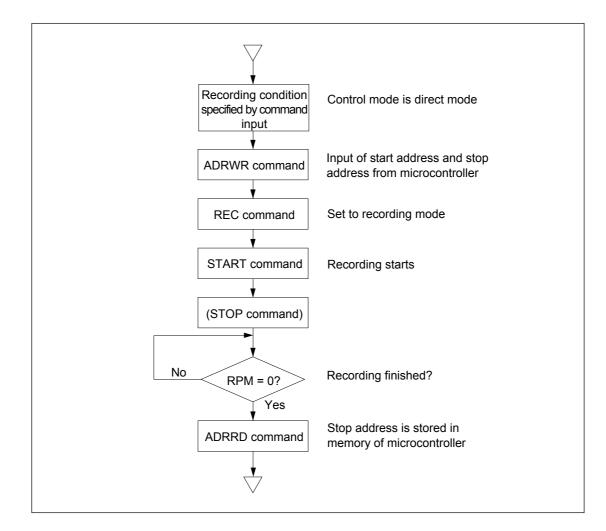

| Recording Control Modes                                                              |      |

| 1. Direct mode                                                                       |      |

| 2. Fixed mode                                                                        |      |

| 3. Flex mode                                                                         |      |

| Channel Usage                                                                        |      |

| 1. Selection of a channel in direct mode and flex mode                               |      |

| 2. Channel selection in fixed mode                                                   |      |

| Operation in Stand-alone Mode                                                        |      |

| 1. Power down function                                                               |      |

| 2. Master clock frequency and sampling frequency                                     |      |

| 3. Method of recording                                                               |      |

| 4. Method of playback                                                                |      |

| 5. Method of pause in record/playback                                                |      |

| 6. Operation in voice triggered starting                                             |      |

| 7. Method of re-recording                                                            |      |

| 8. Pull-up resistor                                                                  | . 59 |

|                                                                                      |      |

# MSM6588/6588L

| Operation in Microcontroller Interface Mode                                                 | 60  |

|---------------------------------------------------------------------------------------------|-----|

| 1. Command input method                                                                     | 60  |

| 2. Explanation of commands                                                                  | 63  |

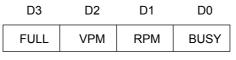

| 3. Explanation of status register                                                           | 65  |

| 4. Selection of sampling frequency (SAMP command)                                           | 67  |

| 5. Recording control modes (SAMP and CHAN commands)                                         | 67  |

| 6. Selection of channel (CHAN command)                                                      | 68  |

| 7. Input/output of start and stop address (ADRWR and ADRRD commands)                        | 69  |

| 8. Specifying ADPCM bit length (VDS command)                                                | 73  |

| 9. Specifying voice triggered starting mode (VDS command)                                   | 73  |

| 10. Recording method                                                                        |     |

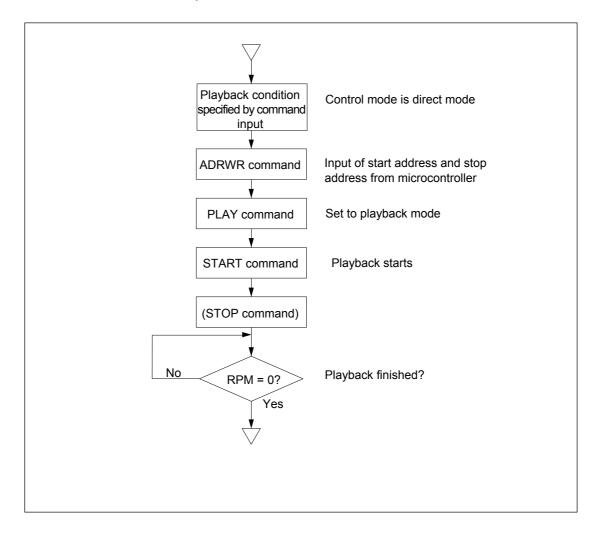

| 11. Playback method                                                                         | 77  |

| 12. Pause method (temporary suspension) with the (PAUSE command)                            | 79  |

| 13. Operation in voice triggered starting (VDS command)                                     | 81  |

| 14. Address control operation                                                               | 82  |

| 15. Multi-channel record/playback method                                                    |     |

| 16. Playback method by means of a serial voice ROM                                          | 89  |

| 17. Data transfer method with external serial registers (DTRW command)                      | 93  |

| 18. Method of record/playback by input/output of voice data from the data bus (EXT command) | 95  |

| 19. Reset and power down function                                                           | 99  |

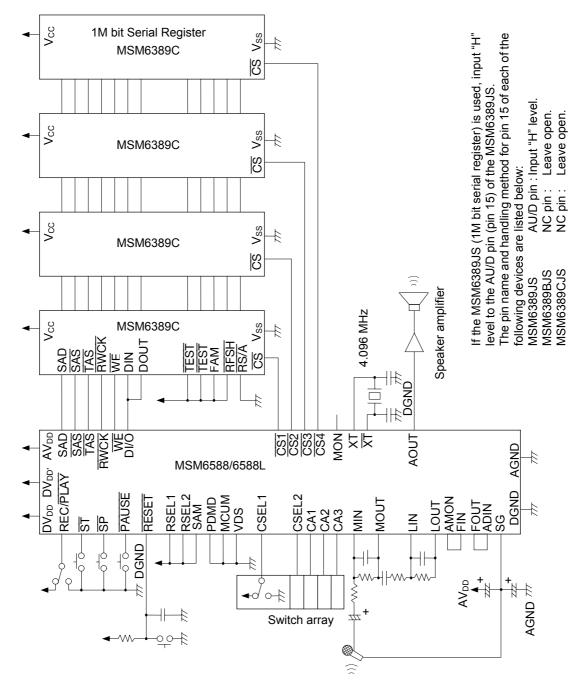

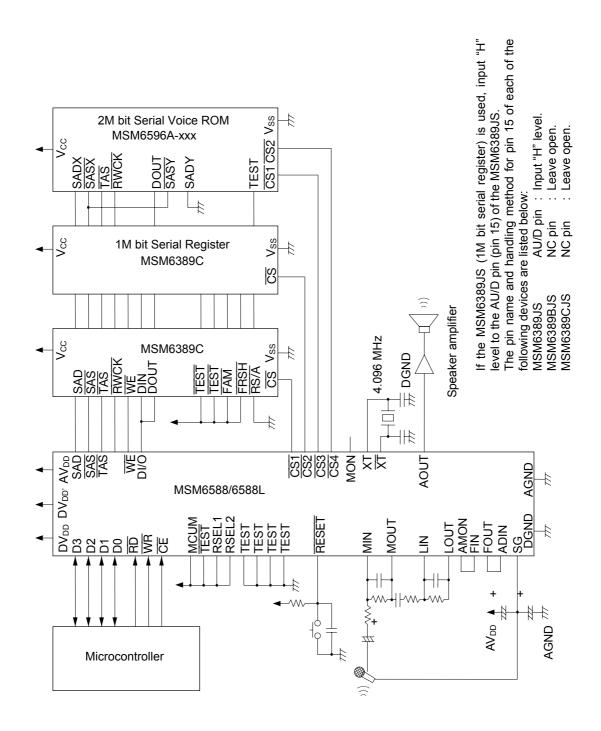

| APPLICATION CIRCUITS                                                                        | 100 |

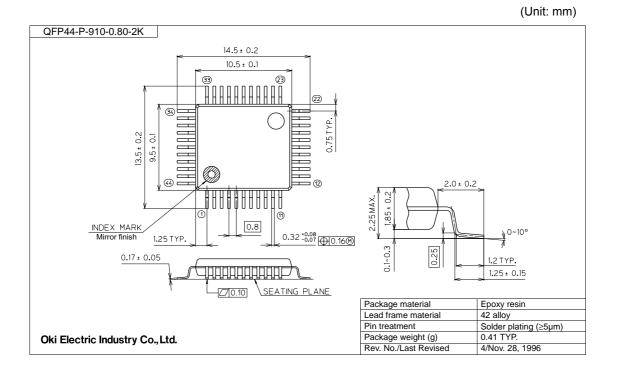

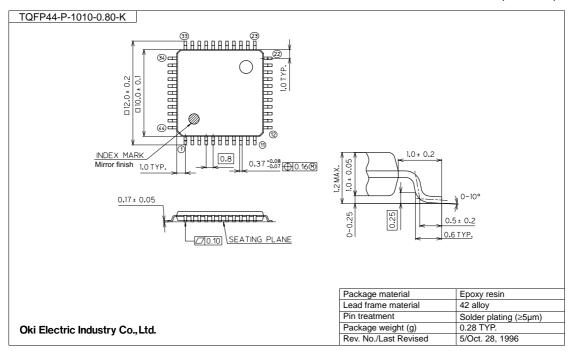

| PACKAGE DIMENSIONS                                                                          | 103 |

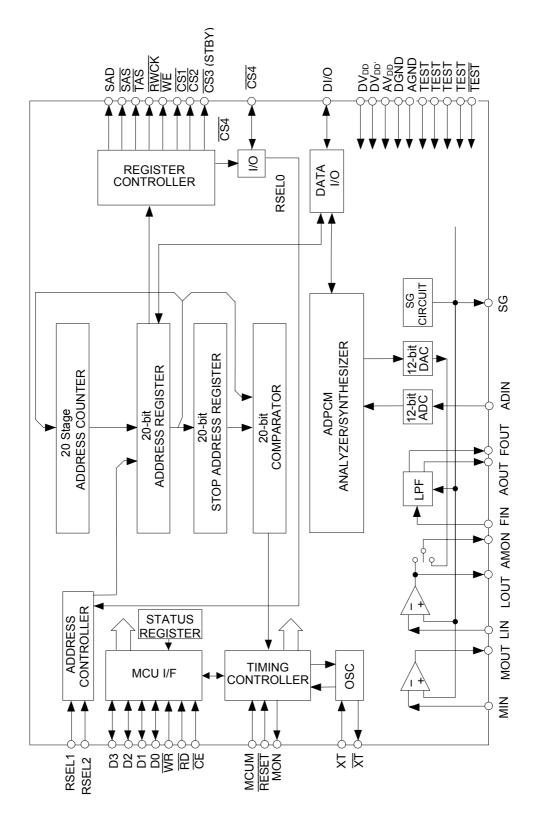

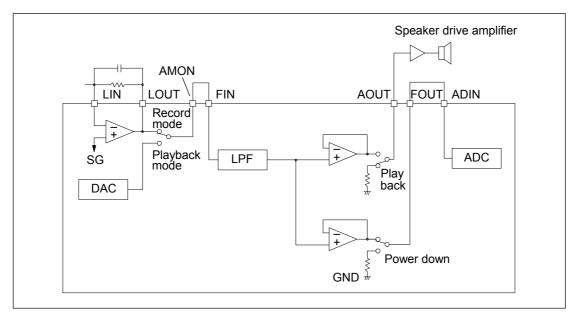

#### **BLOCK DIAGRAM**

#### **Stand-Alone Mode**

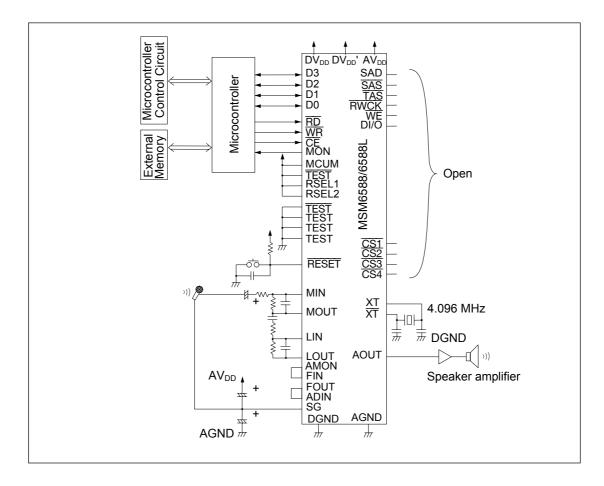

#### Microcontroller Interface Mode

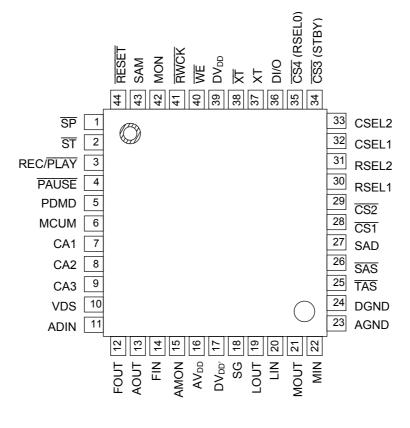

#### **PIN CONFIGURATION (TOP VIEW)**

#### 1. Stand-alone mode (MCUM pin = "L")

44-Pin Plastic QFP 44-Pin Plastic TQFP

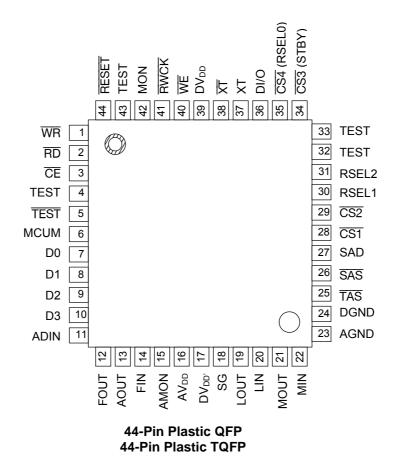

#### 2. Microcontroller interface mode (MCUM pin = "H")

Selection of stand-alone mode or microcontroller interface mode is controlled by the level of the MCUM pin. MCUM = "H": microcontroller interface mode MCUM = "L": stand-alone mode

# **PIN DESCRIPTIONS**

| Pin | Symbol            | Туре | Description                                                                                                                                                                                    |

|-----|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39  | $DV_{DD}$         | _    | Digital power supply pin. Insert a bypass capacitor of 0.1 $\mu\text{F}$ or more between this pin and the DGND pin.                                                                            |

| 17  | DV <sub>DD'</sub> |      | Digital power supply pin                                                                                                                                                                       |

| 16  | AV <sub>DD</sub>  | _    | Analog power supply pin. Insert a bypass capacitor of 0.1 $\mu F$ or more between this pin and the AGND pin.                                                                                   |

| 24  | DGND              |      | Digital GND pin                                                                                                                                                                                |

| 23  | AGND              | _    | Analog GND pin                                                                                                                                                                                 |

| 18  | SG                | 0    | Output pin for analog circuit reference voltage (signal ground)                                                                                                                                |

| 22  | MIN               | 1    | Inverting input pin for the built-in OP amplifier. Non-inverting input pin is                                                                                                                  |

| 20  | LIN               | I    | connected to SG internally.                                                                                                                                                                    |

| 21  | MOUT              | ο    | MOUT and LOUT are output pins of the built-in OP amplifier for MIN and                                                                                                                         |

| 19  | LOUT              | 0    | LIN, respectively.                                                                                                                                                                             |

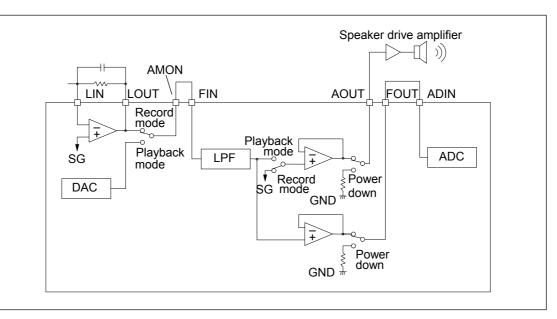

| 15  | AMON              | 0    | This pin is connected to the LOUT pin in recording mode and to the DA converter output in playing mode. Connected to the built-in LPF input (FIN pin).                                         |

| 14  | FIN               | I    | Input pin for the built-in LPF                                                                                                                                                                 |

| 12  | FOUT              | 0    | Output pin of the built-in LPF. Connected to the AD converter (ADIN pin) input.                                                                                                                |

| 11  | ADIN              | I    | Input pin for the built-in 12-bit AD converter                                                                                                                                                 |

| 13  | AOUT              | 0    | Output pin for the built-in LPF. Output pin for playback waveform.<br>Connected to the speaker drive amplifier.                                                                                |

| 27  | SAD               | 0    | (Serial Address Data) Connected to the SAD pin of serial register. This pin outputs the Read/Write header address.                                                                             |

| 26  | SAS               | 0    | (Serial Address Strobe) Connected to the $\overline{SAS}$ pin of serial register. Clock pin to write the serial address.                                                                       |

| 25  | TAS               | 0    | (Transfer Address Strobe) Connected to the $\overline{TAS}$ pin of serial register.<br>Clock pin which transfers the serial address data to the address counter<br>inside the serial register. |

# Common Functions in Stand-Alone Mode and Microcontroller Interface Mode

| Pin | Symbol      | Туре |                                                                                                                               |                                    | Descrip                                            | otion                          |               |                           |  |  |

|-----|-------------|------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------|--------------------------------|---------------|---------------------------|--|--|

| 41  | RWCK        | 0    | (Read/Write Clock) Connected to the $\overline{\text{RWCK}}$ pin of the serial register.                                      |                                    |                                                    |                                |               |                           |  |  |

|     | mon         | Ŭ    | Clock pin for reading and writing data to the serial registers.                                                               |                                    |                                                    |                                |               |                           |  |  |

| 40  | WE          | ο    | (Write Enable) Co<br>select read or writ                                                                                      |                                    | o the WE p                                         | oin of seria                   | al register   | . The pin to              |  |  |

| 36  | DI/O        | I/O  | (Data I/O) Connec                                                                                                             | cted to the                        | DIN and [                                          | DOUT pin                       | s of serial   | register.                 |  |  |

| 50  | DI/O        | 1/0  | Data input and ou                                                                                                             | Data input and output mode.        |                                                    |                                |               |                           |  |  |

|     |             |      | (Chip Select) Con                                                                                                             |                                    | -                                                  |                                | -             |                           |  |  |

| 28  | CS1         | 0    | CS3 pin and CS4of serial registersselected by the RCS3 (STBY) pin botherwise it is the                                        | to be con<br>SELI and<br>becomes ( | nected. Th<br>RSEL2 pin<br>$\overline{CS3}$ when f | e numbei<br>is.<br>four serial | of serial     | registers is<br>are used, |  |  |

| 29  | CS2         | 0    | $\overline{\text{CS4}}$ (RSEL0) pin                                                                                           |                                    |                                                    |                                |               |                           |  |  |

| 34  | CS3 (STBY)  | 0    | otherwise it is the                                                                                                           | RSEL0-pi                           | in used to s                                       | elect the                      | number o      | f serial registers        |  |  |

| 35  | CS4 (RSEL0) | I/O  | used.                                                                                                                         |                                    |                                                    |                                |               |                           |  |  |

|     |             |      | RSEL2                                                                                                                         | L                                  | L                                                  |                                | Н             | Н                         |  |  |

|     |             |      | RSEL1                                                                                                                         | L                                  | Н                                                  |                                | L             | H                         |  |  |

|     |             |      | CS3 (STBY)                                                                                                                    | STBY                               |                                                    |                                | STBY          | CS3                       |  |  |

|     |             |      | CS4 (RSEL0)                                                                                                                   | RSEL<br>(I)                        | 0 RSE                                              |                                | RSEL0<br>(I)  | CS4<br>(O)                |  |  |

|     |             |      | (Register Select)<br>to be connected.                                                                                         | Those pin                          |                                                    | lect the n                     | umber of      | serial registers          |  |  |

| 35  | CS4 (RSEL0) | I/O  | RSEL1                                                                                                                         | L                                  |                                                    | H                              | L             | <u> </u>                  |  |  |

| 30  | RSEL1       |      | RSEL0                                                                                                                         | L                                  | L                                                  |                                | _             | CS4                       |  |  |

| 31  | RSEL2       |      | <u>(CS4)</u>                                                                                                                  | (I)                                | (I)                                                | (I)                            | (I)           | (O)                       |  |  |

|     |             |      | Number of<br>serial voice<br>registers                                                                                        | One<br>256K bit                    | One<br>512K bit                                    | One<br>1M bit                  | Two<br>1M bit | Four<br>1M bit            |  |  |

|     |             |      | This pip is to sale                                                                                                           | ot atond a                         | lono mode                                          | or miore                       | ontrollor     | intorface mode            |  |  |

| 6   | MCUM        | 1    | This pin is to select stand-alone mode or microcontroller interface mode.<br>"L" level stand-alone mode                       |                                    |                                                    |                                |               |                           |  |  |

| U   |             |      |                                                                                                                               |                                    | rocontrolle                                        |                                | mode          |                           |  |  |

| 44  | RESET       | I    | The IC is initialize level.                                                                                                   |                                    |                                                    |                                |               | y input of a "L"          |  |  |

|     | NT.         |      | Connect to an oscillator. Use this input when providing an external clock.<br>When at power down input the GND level instead. |                                    |                                                    |                                |               |                           |  |  |

| 37  | XT          |      | When at power do                                                                                                              | own input                          | the GND le                                         | evel instea                    | ad.           |                           |  |  |

# MSM6588/6588L

# Stand-Alone Mode

| Pin | Symbol   | Туре |                                                                                                                                                                                                                                                   | Description                                                  | ı                                             |                         |                        |  |  |  |  |  |                   |           |         |    |  |

|-----|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------|-------------------------|------------------------|--|--|--|--|--|-------------------|-----------|---------|----|--|

| 3   | REC/PLAY | 1    | This pin is to select recording or playback.                                                                                                                                                                                                      |                                                              |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

| 5   | REG/LEAT | -    | When a "H" level is input,                                                                                                                                                                                                                        | When a "H" level is input, the IC is in record mode.         |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

| 2   | ST       | 1    | When a "L" level pulse is                                                                                                                                                                                                                         | When a "L" level pulse is input, record/playback is started. |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

|     | 61       |      | Internal pull up connected                                                                                                                                                                                                                        | b                                                            |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

| 1   | SP       | 1    | When a "L" level pulse is                                                                                                                                                                                                                         | When a "L" level pulse is input, record/playback is ended.   |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

|     | 61       |      | Internal pull up connected                                                                                                                                                                                                                        | d.                                                           |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

| 4   | PAUSE    | 1    | When a "L" level pulse is input, record/playback is suspended.                                                                                                                                                                                    |                                                              |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

|     |          |      | Internal pull up connected                                                                                                                                                                                                                        |                                                              |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

|     |          |      | These pins are to select the When the number of the word, select Flex mode.                                                                                                                                                                       |                                                              |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

| 32  | CSEL1    |      | CSEL2                                                                                                                                                                                                                                             | L                                                            | L                                             | Н                       | Н                      |  |  |  |  |  |                   |           |         |    |  |

| 33  | CSEL2    | '    | CSEL1                                                                                                                                                                                                                                             | L                                                            | Н                                             | L                       | Н                      |  |  |  |  |  |                   |           |         |    |  |

|     |          |      | Number of recorded v                                                                                                                                                                                                                              | vord 8                                                       | 4                                             | 2                       | 8                      |  |  |  |  |  |                   |           |         |    |  |

|     |          |      | Control mode                                                                                                                                                                                                                                      |                                                              | fixed                                         |                         | flex                   |  |  |  |  |  |                   |           |         |    |  |

|     |          |      |                                                                                                                                                                                                                                                   |                                                              |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

| 7   | CA1      |      | These pins are to specify                                                                                                                                                                                                                         | the channel.                                                 |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

| 8   | CA2      | I.   | (Refer to Explanation of F                                                                                                                                                                                                                        | <sup>-</sup> unctions.)                                      |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

| 9   | CA3      |      |                                                                                                                                                                                                                                                   |                                                              |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

|     |          |      | This pin is to select the sa<br>The following is the relation<br>and sampling frequency (<br>Numbers inside the paren                                                                                                                             | on between the (<br>(f <sub>samp</sub> ).                    | master clock                                  |                         | cy (f <sub>osc</sub> ) |  |  |  |  |  |                   |           |         |    |  |

| 43  | SAM      | I    | SAM                                                                                                                                                                                                                                               | L                                                            | Н                                             |                         |                        |  |  |  |  |  |                   |           |         |    |  |

|     |          |      |                                                                                                                                                                                                                                                   | f <sub>OSC</sub>                                             | f <sub>osc</sub>                              |                         |                        |  |  |  |  |  |                   |           |         |    |  |

|     |          |      |                                                                                                                                                                                                                                                   |                                                              |                                               |                         |                        |  |  |  |  |  | f <sub>samp</sub> | 768       | 512     | -  |  |

|     |          |      |                                                                                                                                                                                                                                                   |                                                              |                                               |                         |                        |  |  |  |  |  |                   | (5.3 kHz) | (8.0 kH | z) |  |

| 5   | PDMD     | 1    | This pin selects transition<br>"L" level The IC enter<br>record/playback.<br>"H" level The IC enter<br>The power down state ca<br>be active when using the                                                                                        | s power down st<br>rs standby state<br>n be entered by       | ate automati<br>except during<br>the RESET pi | g record/<br>in. This n | playback.              |  |  |  |  |  |                   |           |         |    |  |

|     |          | 1    | This pin is to select voice triggered starting that starts recording when the voice input exceeds the preset amplitude. Input a "H" level and the voice activation circuit is enabled. Input a "L" level to disable the voice activation circuit. |                                                              |                                               |                         |                        |  |  |  |  |  |                   |           |         |    |  |

| 10  | VDS      | I    | voice input exceeds the p<br>activation circuit is enable                                                                                                                                                                                         | preset amplitude                                             | Input a "H" I                                 | evel and                | the voice              |  |  |  |  |  |                   |           |         |    |  |

# MSM6588/6588L

# Microcontroller Interface Mode

| Pin                | Symbol       | Туре | Description                                                                                                                                                       |

|--------------------|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                  | D0           |      | Bi-directional data bus. Performs input/output of commands and data                                                                                               |

| 8                  | D1           | I/O  | with an external microcontroller.                                                                                                                                 |

| 9                  | D2           | 1/0  |                                                                                                                                                                   |

| 10                 | D3           |      |                                                                                                                                                                   |

| 1                  | WR           | Ι    | This pin is to input WRITE pulses. Input is a "L" pulse when commands or data to the D0 to D3 pins are to be input.                                               |

| 2                  | RD           | Ι    | This pin is to input READ pulses. Input is a "L" pulse when output status or data from the D0 to D3 pins is to read.                                              |

| 3                  | CE           | I    | Chip enable. A"H" level on this pin disables WRITE (WR)/READ ( $\overline{\text{RD}}$ ) input pulses. Input/output of data through the D0 to D3 pins is disabled. |

| 42                 | MON          | 0    | Outputs a "H" level during record/playback. When record/playback is in operation using the EXT command, clocks for synchronization are output.                    |

| 4, 32, 33, 43<br>5 | TEST<br>TEST | I    | These pins are for IC testing at the factory. Input a "L" level to the TEST pin and a "H" level to the TEST pin.                                                  |

#### ABSOLUTE MAXIMUM RATINGS (for MSM6588 (5 V Version))

| Parameter            | Symbol           | Condition | Rating                       | Unit |

|----------------------|------------------|-----------|------------------------------|------|

| Power supply voltage | V <sub>DD</sub>  | Ta = 25°C | -0.3 to +7.0                 | V    |

| Input voltage        | V <sub>IN</sub>  | Ta = 25 C | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Storage temperature  | T <sub>STG</sub> | —         | –55 to +150                  | °C   |

## **RECOMMENDED OPERATING CONDITIONS (for MSM6588 (5 V Version))**

| Parameter              | Symbol           | Condition         | Range               | Unit |

|------------------------|------------------|-------------------|---------------------|------|

| Power supply voltage   | V <sub>DD</sub>  | DGND = AGND = 0 V | 3.5 to 5.5 (Note 5) | V    |

| Operating temperature  | T <sub>OP</sub>  | —                 | -40 to +85          | °C   |

| Master clock frequency | f <sub>OSC</sub> | —                 | 4.0 to 8.192        | MHz  |

## ELECTRICAL CHARACTERISTICS (for MSM6588 (5 V Version))

#### **DC** Characteristics

| $DV_{DD} = DV_{DD'} = AV_{DD} = 4.5$ to 5.5 V (Note 5), DGND = AGND = 0 V, Ta = -40 to +85°C |                  |                                                  |                            |      |                            |      |  |  |  |  |

|----------------------------------------------------------------------------------------------|------------------|--------------------------------------------------|----------------------------|------|----------------------------|------|--|--|--|--|

| Parameter                                                                                    | Symbol           | Condition                                        | Min.                       | Тур. | Max.                       | Unit |  |  |  |  |

| "H" input voltage                                                                            | V <sub>IH</sub>  | —                                                | $0.8 \times V_{\text{DD}}$ |      | —                          | V    |  |  |  |  |

| "L" input voltage                                                                            | VIL              | —                                                | _                          |      | $0.2 \times V_{\text{DD}}$ | V    |  |  |  |  |

| "H" output voltage                                                                           | V <sub>OH</sub>  | I <sub>OH</sub> = –40 μA                         | V <sub>DD</sub> -0.3       |      | —                          | V    |  |  |  |  |

| "L" output voltage                                                                           | V <sub>OL</sub>  | I <sub>OL</sub> = 2 mA                           | —                          |      | 0.45                       | V    |  |  |  |  |

| "H" input current (Note 1)                                                                   | I <sub>IH1</sub> | $V_{IH} = V_{DD}$                                | —                          |      | 10                         | μA   |  |  |  |  |

| "H" input current (Note 2)                                                                   | I <sub>IH2</sub> | $V_{IH} = V_{DD}$                                | —                          |      | 20                         | μA   |  |  |  |  |

| "L" input current (Note 3)                                                                   | I <sub>IL1</sub> | V <sub>IL</sub> = GND                            | -10                        |      | —                          | μA   |  |  |  |  |

| "L" input current (Note 2)                                                                   | I <sub>IL2</sub> | V <sub>IL</sub> = GND                            | -20                        |      | —                          | μA   |  |  |  |  |

| "L" input current (Note 4)                                                                   | I <sub>IL3</sub> | V <sub>IL</sub> = GND                            | -400                       |      | -20                        | μA   |  |  |  |  |

| Operating current consumption                                                                | I <sub>DD</sub>  | f <sub>osc</sub> = 8 MHz, no load                | _                          | 7    | 15                         | mA   |  |  |  |  |

| Standby current                                                                              |                  | When power down,<br>no load<br>Ta = –40 to +70°C | _                          | _    | 10                         | μA   |  |  |  |  |

| Consumption                                                                                  | I <sub>DDS</sub> | When power down,<br>no load<br>Ta = –40 to +85°C | _                          |      | 50                         | μA   |  |  |  |  |

Notes: 1. Applicable to all input pins, excluding the XT pin.

- 2. Applicable to the XT pin.

- 3. Applicable to all input pins without pull-up resistors, excluding the XT pin.

- Applicable to input pins (ST, SP, PAUSE) with pull-up resistors, excluding the XT pin.

Recording and playback should be performed at a power supply voltage of 4.5 to 5.5 V. For other operations such as backing up a serial register, the IC operates at 3.5 to 5.5 V.

#### MSM6588/6588L

#### **Analog Characteristics**

| $DV_{DD} = DV_{DD'} = AV_{DD} = 4.5$ to 5.5 V, DGND = AGND = 0 V, Ta = -40 to +85°C |                   |                       |      |      |                    |      |  |  |  |  |

|-------------------------------------------------------------------------------------|-------------------|-----------------------|------|------|--------------------|------|--|--|--|--|

| Parameter                                                                           | Symbol            | Condition             | Min. | Тур. | Max.               | Unit |  |  |  |  |

| DA output relative error                                                            | V <sub>DAE</sub>  | no load               | _    | _    | 10                 | mV   |  |  |  |  |

| FIN admissible input voltage range                                                  | $V_{FIN}$         | _                     | 1    | _    | V <sub>DD</sub> -1 | V    |  |  |  |  |

| FIN input impedance                                                                 | $R_{FIN}$         | —                     | 1    | _    | —                  | MΩ   |  |  |  |  |

| ADIN admissible input voltage range                                                 | V <sub>ADIN</sub> | _                     | 0    | _    | $V_{DD}$           | V    |  |  |  |  |

| ADIN input impedance                                                                | R <sub>ADIN</sub> | —                     | 1    | _    | _                  | MΩ   |  |  |  |  |

| Op-amp open loop gain                                                               | G <sub>OP</sub>   | $f_{IN} = 0$ to 4 kHz | 40   | _    | —                  | dB   |  |  |  |  |

| Op-amp input impedance                                                              | R <sub>INA</sub>  | —                     | 1    | _    | _                  | MΩ   |  |  |  |  |

| Op-amp load resistance                                                              | Routa             | —                     | 200  | _    | _                  | kΩ   |  |  |  |  |

| AOUT load resistance                                                                | R <sub>AOUT</sub> | _                     | 50   |      | _                  | kΩ   |  |  |  |  |

| FOUT load resistance                                                                | R <sub>FOUT</sub> | _                     | 50   |      | _                  | kΩ   |  |  |  |  |

# **AC Characteristics**

1. Common characteristics in stand-alone mode and microcontroller interface mode

$DV_{DD} = DV_{DD'} = AV_{DD} = 4.5$  to 5.5 V, DGND = AGND = 0 V, Ta = -40 to +85°C When  $f_{samp} = 8 \text{ kHz}$

|                                 |                  |      |      | 111011150 |      |

|---------------------------------|------------------|------|------|-----------|------|

| Parameter                       | Symbol           | Min. | Тур. | Max.      | Unit |

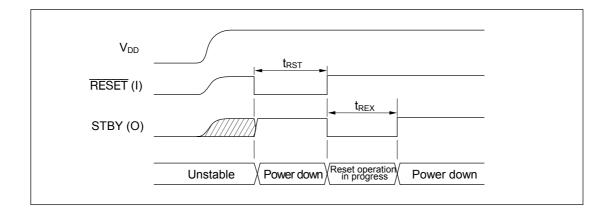

| RESET pulse width               | t <sub>RST</sub> | 1    | _    | _         | μs   |

| RESET execution time (Note 1) * | t <sub>REX</sub> | _    | 125  | _         | μs   |

Item with \* is proportional to the period of sampling frequency ( $f_{samp}$ ). Note: 1. The oscillation stable time is added to  $t_{REX}$ .

The oscillation stable time is several tens of milliseconds for crystal oscillators and is several hundreds of microseconds.

#### **OKI** Semiconductor

# 2. Stand-alone mode

The AC characteristics values of stand-alone mode are proportional to the period of the sampling frequency ( $f_{samp}$ ).

| When f <sub>samp</sub> = |                                                                          |                   |      |      |      |      |  |

|--------------------------|--------------------------------------------------------------------------|-------------------|------|------|------|------|--|

|                          | Parameter                                                                | Symbol            | Min. | Тур. | Max. | Unit |  |

| ST pulse                 | width (Note 1)                                                           | ts⊤               | 40   | —    | —    | μs   |  |

| SP pulse                 | width                                                                    | t <sub>SP</sub>   | 40   |      | —    | μs   |  |

| PAUSE p                  | oulse width                                                              | t <sub>PSE</sub>  | 40   | _    | _    | μs   |  |

| Hold time                | e of CA1, CA2, CA3, REC/PLAY for MON rise                                | t <sub>CAH</sub>  | 1    |      | _    | ms   |  |

| Address                  | control time at the start of record/playback                             | t <sub>AD1</sub>  | _    | 1    | _    | ms   |  |

| Address                  | control time at the end of recording                                     | t <sub>AD2</sub>  | _    | 1    |      | ms   |  |

|                          | il the release of recording standby after input lse during voice standby | t <sub>SPV</sub>  | _    | _    | 500  | μs   |  |

| Silence of               | luring repeated playback                                                 | t <sub>MID</sub>  | _    | 1.5  | _    | ms   |  |

| Time from                | n input of PAUSE pulse until pause                                       | t <sub>PP</sub>   | _    |      | 250  | μs   |  |

|                          | n input of ST pulse to the continuation of ayback during pause           | t <sub>PSP</sub>  | _    | _    | 500  | μs   |  |

|                          | Oscillator stable time after input of $\overline{ST}$ pulse              | t <sub>ANA</sub>  | _    | 32   | _    | ms   |  |

|                          | SP pulse (during recording) to the fall of MON                           | t <sub>SPM1</sub> | _    | _    | 1    | ms   |  |

|                          | SP pulse (during playback) to the fall of MON                            | t <sub>SPM2</sub> | —    | _    | 260  | ms   |  |

| PDMD                     | Standby transient time at start of playback                              | t <sub>AOR</sub>  | _    | 64   | _    | ms   |  |

| = "L"                    | Standby transient time at end of playback                                | t <sub>AOF</sub>  | —    | 256  | _    | ms   |  |

|                          | Time from fall of MON to power down state at the end of playback         | t <sub>MS</sub>   | _    | 70   | —    | μs   |  |

|                          | SP pulse during pause to record end                                      | t <sub>PSP1</sub> | _    | _    | 1    | ms   |  |

|                          | SP pulse during pause to playback end                                    | t <sub>PSP2</sub> | _    | _    | 260  | ms   |  |

|                          | ST pulse to MON rise                                                     | t <sub>S™</sub>   | _    | —    | 1    | ms   |  |

| PDMD                     | SP pulse to MON fall                                                     | t <sub>SPM1</sub> | _    |      | 1    | ms   |  |

| ΡΟΙνίΟ<br>= "H"          | ST pulse to voice standby state                                          | t <sub>STV</sub>  | _    | —    | 1    | ms   |  |

|                          | SP pulse during pause to record/playback end                             | t <sub>PSP1</sub> | _    |      | 1    | ms   |  |

| $DV_{DD} = DV_{DD'} = AV_{DD} = 4.5$ to 5.5 V, DGND = AGND = 0 V, Ta = -40 to +85°C |

|-------------------------------------------------------------------------------------|

| When f <sub>samp</sub> = 8 kHz                                                      |

Note: 1. When the PDMD pin is "L", the oscillation stable time is added to t<sub>ST</sub>. The oscillation stable time is several tens of milliseconds for crystal oscillators and is several hundreds of microseconds for ceramic oscillators.

#### MSM6588/6588L

#### 3. Microcontroller interface mode

|                                                                  |   |                  |      |      | When fsa | amp = 8 kHz |

|------------------------------------------------------------------|---|------------------|------|------|----------|-------------|

| Parameter                                                        |   | Symbol           | Min. | Тур. | Max.     | Unit        |

| RD pulse width                                                   |   | t <sub>RR</sub>  | 200  | _    | _        | ns          |

| Setup and hold time of CE for RD                                 |   | t <sub>CR</sub>  | 0    | _    | _        | ns          |

| Data valid from fall of RD                                       |   | t <sub>DRE</sub> |      | _    | 200      | ns          |

| Data Hi-Z from rise of RD                                        |   | t <sub>DRF</sub> |      | 10   | 50       | ns          |

| WR pulse width                                                   |   | tww              | 200  | _    | _        | ns          |

| Setup and hold time of $\overline{CE}$ from $\overline{WR}$      |   | t <sub>CW</sub>  | 0    | _    | _        | ns          |

| Data setup time to rise of WR                                    |   | t <sub>DWS</sub> | 100  | _    | _        | ns          |

| Data Hold time from rise of WR                                   |   | t <sub>DWH</sub> | 30   | _    | _        | ns          |

| Disable time for $\overline{RD}$ and WR                          |   | t <sub>DRW</sub> | 250  | _    | —        | ns          |

| BUSY time after release of RESET (Note 1)                        | * | t <sub>BR</sub>  |      | _    | 125      | μs          |

| BUSY time after input of 1 nibble command                        | * | t <sub>B1</sub>  |      | _    | 16       | μs          |

| BUSY time after input of 2 nibble command                        | * | t <sub>B2</sub>  |      | _    | 16       | μs          |

| BUSY time after input of 2 nibble command data                   | * | t <sub>BD</sub>  |      | _    | 16       | μs          |

| BUSY time after input of ADRWR command                           | * | t <sub>BAW</sub> |      | _    | 270      | μs          |

| BUSY time after input address data of ADRWR command              | * | t <sub>BAD</sub> | _    | —    | 50       | μs          |

| Data input time after input of ADRRD command                     | * | t <sub>WAR</sub> | 270  | _    |          | μs          |

| Time between output of address data nibbles during ADRRD command | * | t <sub>wDR</sub> | 50   | _    | _        | μs          |

# $DV_{DD} = DV_{DD'} = AV_{DD} = 4.5$ to 5.5 V, DGND = AGND = 0 V, Ta = -40 to +85°C - <u>o</u> ru

Items with \* are proportional to the period of sampling frequency ( $f_{samp}$ ).

Note: 1. The oscillation stable time is added to t<sub>BR</sub>. The oscillation stable time is several tens of milliseconds for crystal oscillators and is several hundred of microseconds for ceramic oscillators.

#### FEDL6588-6588L-04

#### **OKI** Semiconductor

# MSM6588/6588L

| Parameter                                          |                                                                 |   | Symbol             | Min. | Тур. | Max. | Unit |

|----------------------------------------------------|-----------------------------------------------------------------|---|--------------------|------|------|------|------|

| Address control time at start of record/playback * |                                                                 |   | t <sub>AD1</sub>   | _    | 1    | _    | ms   |

| Address cor                                        | trol time at end of recording                                   | * | t <sub>AD2</sub>   | —    | 1    | _    | ms   |

| START com                                          | mand to rise of MON                                             | * | t <sub>sтсм</sub>  | —    | _    | 1    | ms   |

| STOP comn                                          | nand to fall of MON                                             | * | t <sub>SPCM</sub>  | —    | _    | 1    | ms   |

| START com                                          | mand to RPM bit set ("H" level)                                 | * | t <sub>STCR</sub>  | —    | _    | 16   | μs   |

|                                                    | mand (during voice triggered starting)<br>et ("H" level)        | * | t <sub>STCV</sub>  | _    | _    | 16   | μs   |

|                                                    | nand to release of voice standby<br>e triggered starting)       | * | t <sub>SPCV</sub>  | _    | —    | 500  | μs   |

| PAUSE com                                          | mand to VPM bit set ("H" level)                                 | * | t <sub>PSCP</sub>  | _    | _    | 16   | μs   |

| START com<br>("L" level)                           | mand (during pause) to VPM bit reset                            | * | t <sub>STCP</sub>  | _    | _    | 500  | μs   |

| STOP comn<br>("L" level)                           | nand (during pause) to VPM bit reset                            | * | t <sub>SPCP</sub>  | _    |      | 500  | μs   |

|                                                    | Delay time after input of DTRW command                          | * | t <sub>wrw</sub>   | 16   | _    | _    | μs   |

|                                                    | Delay time after input of lower 4-bit of X address              | * | t <sub>WXA1</sub>  | 16   | —    | _    | μs   |

| When                                               | Delay time after input of middle 4-bit of X address             | * | t <sub>WXA2</sub>  | 16   | _    | —    | μs   |

| DTRW<br>command                                    | Delay time after input of upper 4-bit of X address              | * | t <sub>WXA3</sub>  | 270  | _    | _    | μs   |

| is being<br>executed                               | Delay time after input of REC command                           | * | t <sub>wrc</sub>   | 16   | _    | _    | μs   |

|                                                    | Delay time after input of write data                            | * | t <sub>WWD</sub>   | 50   | _    | _    | μs   |

|                                                    | Delay time after input of PLAY command                          | * | t <sub>WPL</sub>   | 50   | _    | _    | μs   |

|                                                    | Delay time after input of STOP command                          | * | t <sub>wsp</sub>   | 16   | _    | _    | μs   |

|                                                    | EXT command to rise of MON                                      | * | t <sub>EM</sub>    | 125  |      | 330  | μs   |

|                                                    | "H" level time of MON                                           | * | t <sub>мн</sub>    |      | 31   |      | μs   |

|                                                    | "L" level time of MON                                           | * | t <sub>ML</sub>    |      | 94   | —    | μs   |

| When                                               | MON rise to RD pulse rise (during recording)                    | * | t <sub>ERD</sub>   | _    | —    | 120  | μs   |

| executing<br>EXT                                   | MON rise to $\overline{\text{WR}}$ pulse rise (during playback) | * | t <sub>EWR</sub>   | _    | _    | 120  | μs   |

| command                                            | ADPCM data write pulse to input of STOP command                 | * | t <sub>WE1</sub>   | 16   |      |      | μs   |

|                                                    | STOP command until rise of MON                                  | * | t <sub>ESP</sub>   |      |      | 100  | μs   |

|                                                    | STOP command to record/playback end                             | * | $\mathbf{t}_{WEX}$ | _    | _    | 250  | μs   |

Items with \* are proportional to the period of sampling frequency ( $\ensuremath{f_{\text{samp}}}\xspace).$

#### ABSOLUTE MAXIMUM RATINGS (for MSM6588L (3 V Version))

| Parameter            | Symbol           | Condition | Rating                       | Unit |

|----------------------|------------------|-----------|------------------------------|------|

| Power supply voltage | V <sub>DD</sub>  | Ta = 25°C | -0.3 to +7.0                 | V    |

| Input voltage        | V <sub>IN</sub>  | Ta = 25 C | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Storage temperature  | T <sub>STG</sub> | —         | -55 to +150                  | °C   |

## **RECOMMENDED OPERATING CONDITIONS (for MSM6588L (3 V Version))**

| Parameter              | Symbol           | Condition         | Range        | Unit |

|------------------------|------------------|-------------------|--------------|------|

| Power supply voltage   | V <sub>DD</sub>  | DGND = AGND = 0 V | 2.7 to 3.6   | V    |

| Operating temperature  | T <sub>OP</sub>  | —                 | -40 to +85   | °C   |

| Master clock frequency | f <sub>OSC</sub> | —                 | 4.0 to 8.192 | MHz  |

## ELECTRICAL CHARACTERISTICS (for MSM6588L (3 V Version))

#### **DC** Characteristics

| $DV_{DD} = DV_{DD} = AV_{DD} = 2.7$ to 3.6 V, DGND = AGND = 0 V, Ta = -40 to +85°C |                  |                                                  |                             |      |                             |      |  |  |  |  |

|------------------------------------------------------------------------------------|------------------|--------------------------------------------------|-----------------------------|------|-----------------------------|------|--|--|--|--|

| Parameter                                                                          | Symbol           | Condition                                        | Min.                        | Тур. | Max.                        | Unit |  |  |  |  |

| "H" input voltage                                                                  | VIH              | —                                                | $0.85 \times V_{\text{DD}}$ |      | —                           | V    |  |  |  |  |

| "L" input voltage                                                                  | VIL              | —                                                | —                           |      | $0.15 \times V_{\text{DD}}$ | V    |  |  |  |  |

| "H" output voltage                                                                 | V <sub>OH</sub>  | I <sub>OH</sub> = –40 μA                         | V <sub>DD</sub> -0.3        |      | —                           | V    |  |  |  |  |

| "L" output voltage                                                                 | V <sub>OL</sub>  | I <sub>OL</sub> = 2 mA                           | —                           |      | 0.45                        | V    |  |  |  |  |

| "H" input current (Note 1)                                                         | I <sub>IH1</sub> | $V_{IH} = V_{DD}$                                | —                           |      | 10                          | μA   |  |  |  |  |

| "H" input current (Note 2)                                                         | I <sub>IH2</sub> | $V_{IH} = V_{DD}$                                | _                           |      | 20                          | μA   |  |  |  |  |

| "L" input current (Note 3)                                                         | I <sub>IL1</sub> | V <sub>IL</sub> = GND                            | -10                         |      | —                           | μA   |  |  |  |  |

| "L" input current (Note 2)                                                         | I <sub>IL2</sub> | V <sub>IL</sub> = GND                            | -20                         |      | —                           | μA   |  |  |  |  |

| "L" input current (Note 4)                                                         | I <sub>IL3</sub> | V <sub>IL</sub> = GND                            | -400                        |      | -10                         | μA   |  |  |  |  |

| Operating current consumption                                                      | I <sub>DD</sub>  | f <sub>OSC</sub> = 8 MHz, no load                | —                           | 7    | 15                          | mA   |  |  |  |  |

| Standby current                                                                    |                  | When power down,<br>no load<br>Ta = –40 to +70°C | _                           | _    | 15                          | μΑ   |  |  |  |  |

| consumption                                                                        | I <sub>DDS</sub> | When power down,<br>no load<br>Ta = –40 to +85°C |                             |      | 100                         | μΑ   |  |  |  |  |

Notes: 1. Applicable to all input pins, excluding the XT pin.

2. Applicable to the XT pin.

3. Applicable to all input pins without pull-up resistors, excluding the XT pin.

4. Applicable to input pins (ST, SP, PAUSE) with pull-up resistors, excluding the XT pin.

#### MSM6588/6588L

#### **Analog Characteristics**

| $DV_{DD} = DV_{DD'} = AV_{DD} = 2.7$ to 3.6 V, DGND = AGND = 0 V, Ta = -40 to +85°C |                   |                       |                     |      |                    |      |  |  |  |  |

|-------------------------------------------------------------------------------------|-------------------|-----------------------|---------------------|------|--------------------|------|--|--|--|--|

| Parameter                                                                           | Symbol            | Condition             | Min.                | Тур. | Max.               | Unit |  |  |  |  |

| DA output relative error                                                            | V <sub>DAE</sub>  | no load               | —                   |      | 5                  | mV   |  |  |  |  |

| FIN admissible input voltage range                                                  | $V_{FIN}$         | _                     | $1/4 \times V_{DD}$ | _    | $3/4 	imes V_{DD}$ | V    |  |  |  |  |

| FIN input impedance                                                                 | R <sub>FIN</sub>  | —                     | 1                   |      | _                  | MΩ   |  |  |  |  |

| ADIN admissible input voltage range                                                 | V <sub>ADIN</sub> | _                     | $1/4 \times V_{DD}$ | _    | $3/4 	imes V_{DD}$ | V    |  |  |  |  |

| ADIN input impedance                                                                | R <sub>ADIN</sub> | —                     | 1                   |      | _                  | MΩ   |  |  |  |  |

| Op-amp open loop gain                                                               | G <sub>OP</sub>   | $f_{IN} = 0$ to 4 kHz | 40                  |      | _                  | dB   |  |  |  |  |

| Op-amp input impedance                                                              | R <sub>INA</sub>  | —                     | 1                   |      | —                  | MΩ   |  |  |  |  |

| Op-amp load resistance                                                              | Routa             | _                     | 200                 | _    | _                  | kΩ   |  |  |  |  |

| AOUT load resistance                                                                | R <sub>AOUT</sub> | —                     | 50                  | _    | _                  | kΩ   |  |  |  |  |

| FOUT load resistance                                                                | R <sub>FOUT</sub> | —                     | 50                  |      | _                  | kΩ   |  |  |  |  |

#### **AC Characteristics**

1. Common characteristics in stand-alone mode and microcontroller interface mode

$DV_{DD} = DV_{DD'} = AV_{DD} = 2.7$  to 3.6 V, DGND = AGND = 0 V, Ta = -40 to +85°C When  $f_{samp} = 8 \text{ kHz}$

| Parameter                               | Symbol           | Min. | Тур. | Max. | Unit |

|-----------------------------------------|------------------|------|------|------|------|

| RESET pulse width                       | t <sub>RST</sub> | 1    | _    | _    | μs   |

| RESET execution time (Note 1)         * | t <sub>REX</sub> | _    | 125  | _    | μs   |

Item with \* is proportional to the period of sampling frequency ( $f_{samp}$ ). Note: 1. The oscillation stable time is added to  $t_{REX}$ .

The oscillation stable time is several tens of milliseconds for crystal oscillators and is several hundreds of microseconds.

#### **OKI** Semiconductor

# 2. Stand-alone mode

The AC characteristics values of stand-alone mode are proportional to the period of the sampling frequency ( $f_{samp}$ ).

|                                                                                          |                                                                                 |                   |      | •    | When f <sub>sa</sub> | amp = 8 kHz |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------|------|------|----------------------|-------------|

| Parameter                                                                                |                                                                                 | Symbol            | Min. | Тур. | Max.                 | Unit        |

| ST pulse width (Note 1)                                                                  |                                                                                 | t <sub>s⊤</sub>   | 40   | —    | —                    | μs          |

| SP pulse width                                                                           |                                                                                 | t <sub>SP</sub>   | 40   | —    | —                    | μs          |

| PAUSE p                                                                                  | PAUSE pulse width                                                               |                   | 40   | _    | -                    | μs          |

| Hold time of CA1, CA2, CA3, REC/PLAY for MON rise                                        |                                                                                 | t <sub>CAH</sub>  | 1    | _    | _                    | ms          |