Now

SLVSD18C -JUNE 2015-REVISED AUGUST 2017

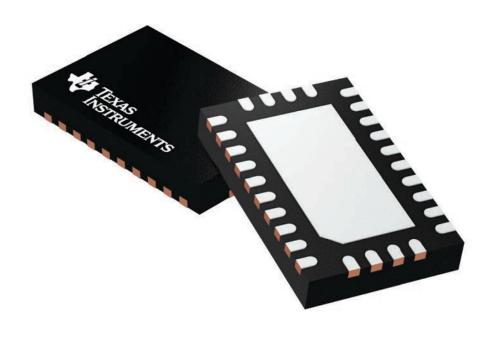

# DRV8880 2-A Stepper Motor Driver With Smart Tune

Technical

Documents

# Features

- Microstepping Stepper Motor Driver

- STEP/DIR Interface

- Up to 1/16 Microstepping Indexer

- Non-Circular and Standard ½ Step Modes

- 6.5- to 45-V Operating Supply Voltage Range

- Multiple Decay Modes to Support Any Motor

- Smart tune

- Mixed Decay

- Slow Decay

- Fast Decay

- Adaptive Blanking Time for Smooth Stepping

- Configurable Off-Time PWM Chopping

- 10-, 20-, or 30-µs Off-Time

- 3.3-V, 10-mA LDO Regulator

- Low-Current Sleep Mode (28 µA)

- Small Package and Footprint

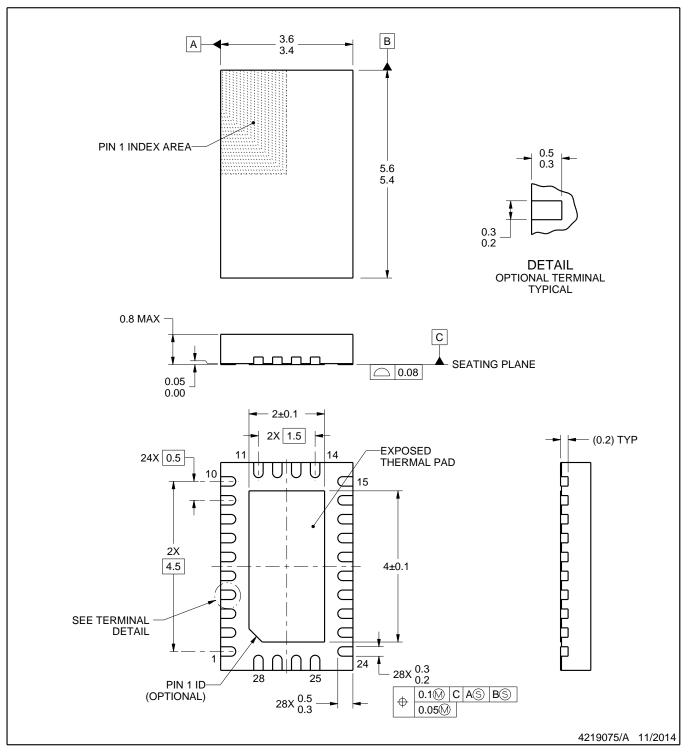

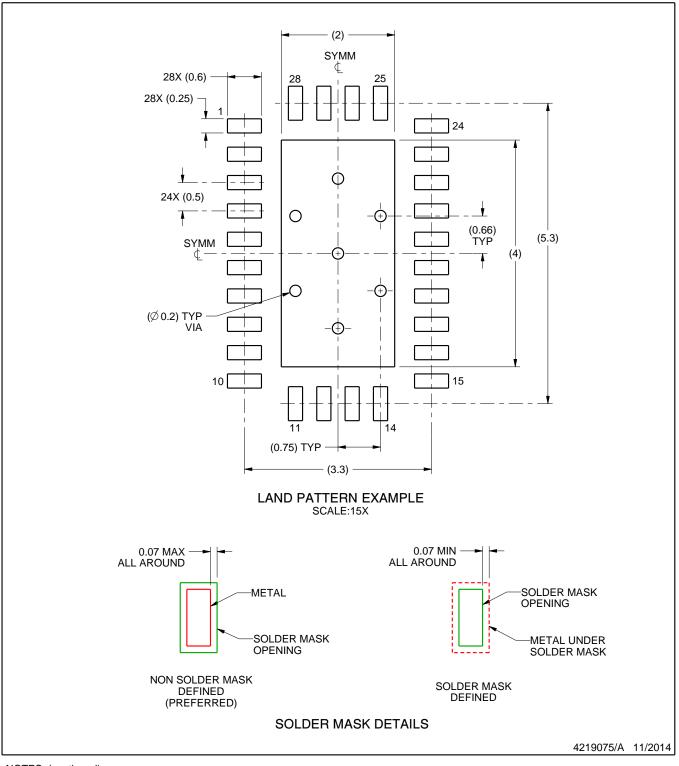

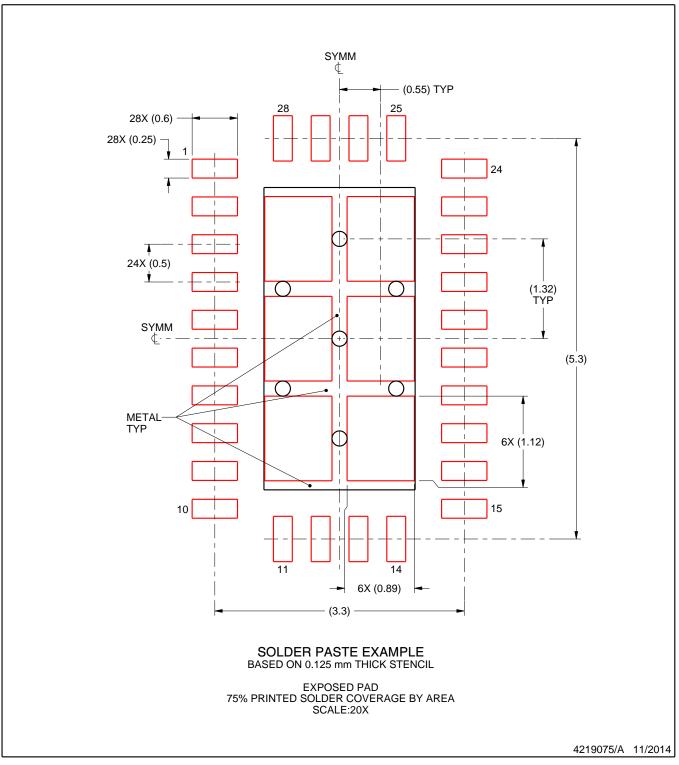

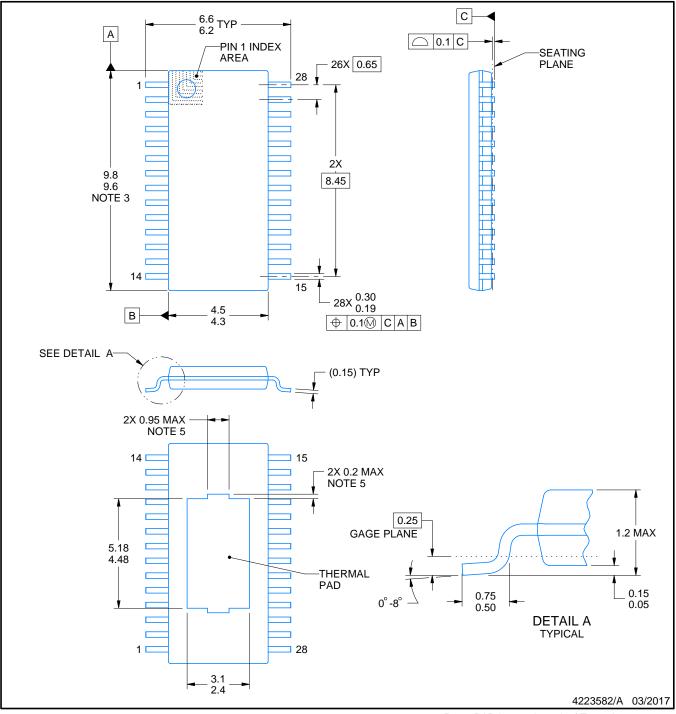

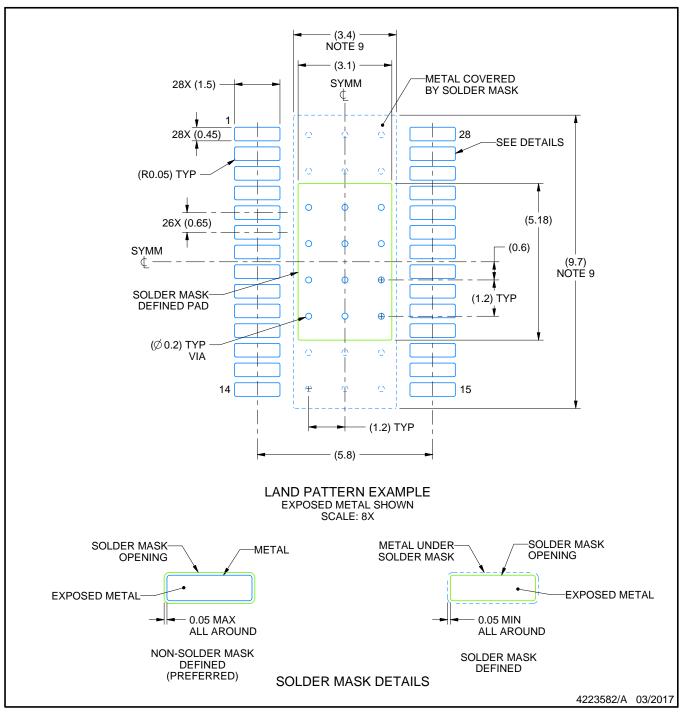

- 28 HTSSOP (PowerPAD<sup>™</sup>)

- 28 WQFN

# Protection Features

- VM Undervoltage Lockout (UVLO2)

- Logic Undervoltage (UVLO1)

- Charge Pump Undervoltage (CPUV)

- Overcurrent Protection (OCP)

- Latched OCP Mode

- Retry OCP Mode

- Thermal Shutdown (TSD)

- Fault Condition Indication Pin (nFAULT)

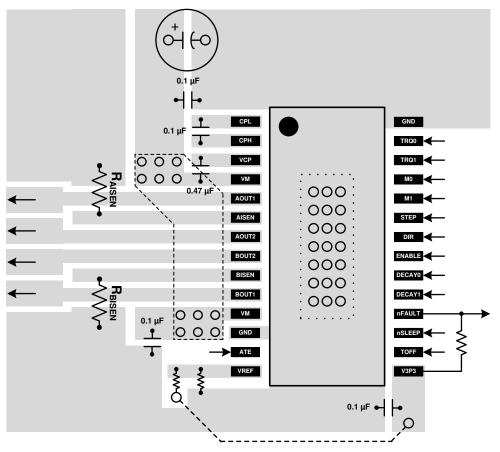

Simplified System Diagram

#### **Applications** 2

Tools &

Software

Automatic Teller and Money Handling Machines

Support &

Community

20

- Video Security Cameras

- **Multi-Function Printers and Document Scanners**

- **3D** Printers

- Office Automation Machines •

- Factory Automation and Robotics

# **3** Description

The DRV8880 is a bipolar stepper motor driver for industrial applications. The device has two N-channel power MOSFET H-bridge drivers and a microstepping indexer. The DRV8880 is capable of driving 2.0 A fullscale current or 1.4-A rms current (with proper PCB ground plane for thermal dissipation and at 24 V and  $T_{A} = 25^{\circ}C$ ).

Smart tune automatically tunes stepper motors for optimal current regulation performance and compensates for motor variation and aging effects. Additionally slow, fast, and mixed decay modes are available.

The STEP/DIR pins provide a simple control interface. The device can be configured in full-step up to 1/16- step modes. A low-power sleep mode is provided for very low quiescent current standby using a dedicated nSLEEP pin.

Internal protection functions are provided for undervoltage, charge pump faults, overcurrent, shortcircuits, and overtemperature. Fault conditions are indicated by a nFAULT pin.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |

|-------------|-------------|-------------------|

| DRV8880     | HTSSOP (28) | 9.70 mm × 4.40 mm |

| DR V 0000   | WQFN (28)   | 5.50 mm × 3.50 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### 6.5 to 45 V STEP/DIR М 2.0 A Controlle Stepper Step size Motor Driver $\overline{000}$ Decay mode AutoTune™ 2.0 A 1/16 µstep

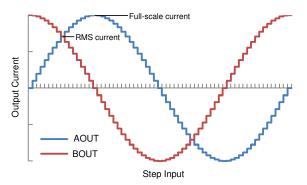

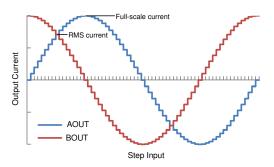

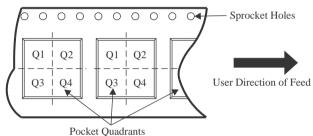

### Microstepping Current Waveform

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

TEXAS INSTRUMENTS

www.ti.com

# Table of Contents

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications5                       |

|   | 6.1  | Absolute Maximum Ratings 5         |

|   | 6.2  | ESD Ratings 5                      |

|   | 6.3  | Recommended Operating Conditions 5 |

|   | 6.4  | Thermal Information 6              |

|   | 6.5  | Electrical Characteristics 6       |

|   | 6.6  | Indexer Timing Requirements8       |

|   | 6.7  | Typical Characteristics 9          |

| 7 | Deta | ailed Description 11               |

|   | 7.1  | Overview 11                        |

|   | 7.2  | Functional Block Diagram 12        |

|   | 7.3  | Feature Description 13             |

|   |      |                                    |

|    | 7.4   | Device Functional Modes                           | 0  |

|----|-------|---------------------------------------------------|----|

| 8  | Appl  | ication and Implementation3                       | 1  |

|    | 8.1   | Application Information                           | 1  |

|    | 8.2   | Typical Application                               |    |

| 9  | Pow   | er Supply Recommendations 3                       | 5  |

|    | 9.1   | Bulk Capacitance Sizing 3                         | 5  |

| 10 | Layo  | out                                               | 6  |

|    | 10.1  | Layout Guidelines 3                               | 6  |

|    | 10.2  | Layout Example 3                                  | 6  |

| 11 | Devi  | ice and Documentation Support                     | 7  |

|    | 11.1  | Documentation Support 3                           | 57 |

|    | 11.2  | Receiving Notification of Documentation Updates 3 | 57 |

|    | 11.3  | Community Resources 3                             | 7  |

|    | 11.4  | Trademarks 3                                      | 7  |

|    | 11.5  | Electrostatic Discharge Caution 3                 | 7  |

|    | 11.6  | Glossary 3                                        | 7  |

| 12 |       | hanical, Packaging, and Orderable                 |    |

|    | Infor | mation 3                                          | 7  |

|    |       |                                                   |    |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision B (August 2017) to Revision C                                            | Page       |

|------------------------------------------------------------------------------------------------|------------|

| • Changed the maximum value for VREF from V3P3 + 0.5 V to 4.1 V in the Absolute Maximum Rating | gs table 5 |

| Changes from Revision A (July 2015) to Revision B                                              | Page       |

| Added the Power Supplies and Input Pins section                                                | 27         |

| Added the Receiving Notification of Documentation Updates section                              |            |

| Changes from Original (June 2015) to Revision A                                                | Page       |

| Updated device status to production data                                                       | 1          |

| Updated from "PowerPAD" to "thermal pad"                                                       | 4          |

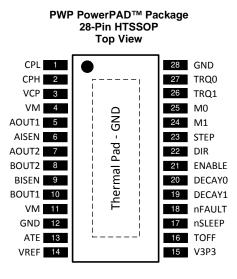

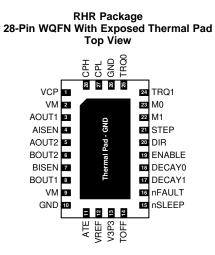

# 5 Pin Configuration and Functions

### **Pin Functions**

|        | PIN    |        | ТҮРЕ |                                       | DESCRIPTION                                                                                                                                                                                                                                                                               |

|--------|--------|--------|------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | PWP    | RHR    | ITPE |                                       | DESCRIPTION                                                                                                                                                                                                                                                                               |

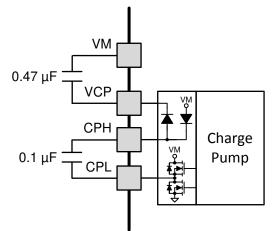

| CPL    | 1      | 27     | PWR  | Charge pump switching                 | Connect a VM rated, 0.1-µF ceramic capacitor between                                                                                                                                                                                                                                      |

| CPH    | 2      | 28     | PWK  | pins                                  | CPH and CPL                                                                                                                                                                                                                                                                               |

| VCP    | 3      | 1      | 0    | Charge pump output                    | Connect a 16 V, 0.47 µF ceramic capacitor to VM                                                                                                                                                                                                                                           |

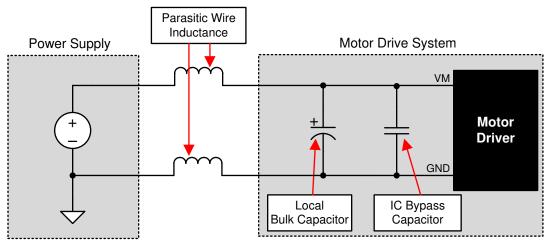

| VM     | 4, 11  | 2, 9   | PWR  | Power supply                          | Connect to motor supply voltage; bypass to GND with two 0.1 $\mu F$ (for each pin) plus one bulk capacitor rated for VM                                                                                                                                                                   |

| AOUT1  | 5      | 3      | 0    | Winding A gutnut                      | H-bridge outputs, drives one winding of a stepper motor                                                                                                                                                                                                                                   |

| AOUT2  | 7      | 5      | 0    | Winding A output                      |                                                                                                                                                                                                                                                                                           |

| AISEN  | 6      | 4      | 0    | Winding A sense                       | Requires sense resistor to GND; value sets peak current in winding A                                                                                                                                                                                                                      |

| BOUT2  | 8      | 6      | 0    | Winding Doutput                       | H-bridge outputs, drives one winding of a stepper motor                                                                                                                                                                                                                                   |

| BOUT1  | 10     | 8      | 0    | Winding B output                      |                                                                                                                                                                                                                                                                                           |

| BISEN  | 9      | 7      | 0    | Winding B sense                       | Requires sense resistor to GND; value sets peak current in winding B                                                                                                                                                                                                                      |

| GND    | 12, 28 | 10, 26 | PWR  | Device ground                         | Must be connected to ground                                                                                                                                                                                                                                                               |

| ATE    | 13     | 11     | I    | Smart tune enable pin                 | Logic high enables smart tune operation; when logic low,<br>the decay mode is set through the DECAYx pins; smart<br>tune must be pulled high prior to power-up or coming out<br>of sleep, or else tied to V3P3 in order to enable smart<br>tune; internal pulldown; see <i>Smart Tune</i> |

| VREF   | 14     | 12     | I    | Full scale current<br>reference input | Voltage on this pin sets the full scale chopping current.                                                                                                                                                                                                                                 |

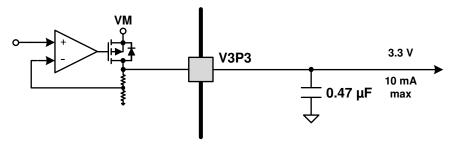

| V3P3   | 15     | 13     | PWR  | Internal regulator                    | Internal supply voltage; bypass to GND with a 6.3 V, 0.47 $\mu$ F ceramic capacitor; up to 10 mA external load                                                                                                                                                                            |

| TOFF   | 16     | 14     | I    | Decay mode off time set               | Sets the off-time during current chopping; tri-level pin                                                                                                                                                                                                                                  |

| nSLEEP | 17     | 15     | I    | Sleep mode input                      | Logic high to enable device; logic low to enter low-power sleep mode; internal pulldown                                                                                                                                                                                                   |

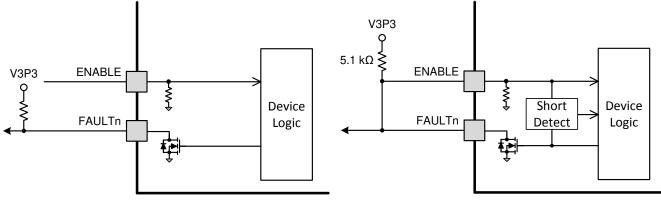

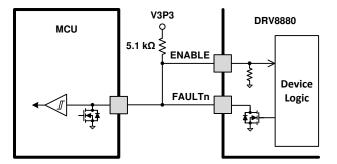

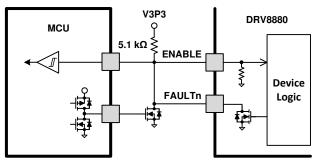

| nFAULT | 18     | 16     | 0    | Fault indication pin                  | Pulled logic low with fault condition; open-drain output requires an external pullup                                                                                                                                                                                                      |

| DECAY1 | 19     | 17     | - 1  | Deservers de settine sins             | Sets the decay mode; see description section; tri-level pin                                                                                                                                                                                                                               |

| DECAY0 | 20     | 18     |      | Decay mode setting pins               |                                                                                                                                                                                                                                                                                           |

| ENABLE | 21     | 19     | I    | Enable driver input                   | Logic high to enable device outputs and internal indexer;<br>logic low to disable; internal pulldown                                                                                                                                                                                      |

| DIR    | 22     | 20     | I    | Direction input                       | Logic level sets the direction of stepping; internal pulldown                                                                                                                                                                                                                             |

DRV8880 SLVSD18C – JUNE 2015–REVISED AUGUST 2017

www.ti.com

Texas Instruments

# Pin Functions (continued)

|      | PIN |     | ТҮРЕ | DESCRIPTION        |                                                                         |  |  |

|------|-----|-----|------|--------------------|-------------------------------------------------------------------------|--|--|

| NAME | PWP | RHR | ITPE |                    | DESCRIPTION                                                             |  |  |

| STEP | 23  | 21  | I    | Step input         | A rising edge causes the indexer to advance one step; internal pulldown |  |  |

| M1   | 24  | 22  | 1    | Microstepping mode | Sets the step mode; full, 1/2, 1/4, 1/8, 1/16; tri-level pin            |  |  |

| MO   | 25  | 23  |      | setting pins       |                                                                         |  |  |

| TRQ1 | 26  | 24  |      | Torque DAC current | Scales the current by 100%, 75%, 50%, or 25%; internal                  |  |  |

| TRQ0 | 27  | 25  |      | scalar             | pulldown                                                                |  |  |

| PAD  | PAD | PAD | PWR  | Thermal pad        | Must be connected to ground                                             |  |  |

#### Specifications 6

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range referenced with respect to GND (unless otherwise noted) <sup>(1)</sup>

|                                                                                                  | MIN     | MAX         | UNIT |

|--------------------------------------------------------------------------------------------------|---------|-------------|------|

| Power supply voltage (VM)                                                                        | -0.3    | 50          | V    |

| Power supply voltage ramp rate (VM)                                                              | 0       | 2           | V/µs |

| Charge pump voltage (VCP, CPH)                                                                   | -0.3    | VM + 12     | V    |

| Charge pump negative switching pin (CPL)                                                         | -0.3    | VM          | V    |

| Internal regulator voltage (V3P3)                                                                | -0.3    | 3.8         | V    |

| Internal regulator current output (V3P3)                                                         | 0       | 10          | mA   |

| Control pin voltage (STEP, DIR, ENABLE, nSLEEP, nFAULT, M0, M1, DECAY0, DECAY1, TRQ0, TRQ1, ATE) | -0.3    | 7.0         | V    |

| Open drain output current (nFAULT)                                                               | 0       | 10          | mA   |

| Reference input pin voltage (VREF)                                                               | -0.3    | 4.1         | V    |

| Continuous phase node pin voltage (AOUT1, AOUT2, BOUT1, BOUT2)                                   | -0.7    | VM + 0.7    | V    |

| Continuous shunt amplifier input pin voltage (AISEN, BISEN) (2)                                  | -0.55   | 0.55        | V    |

| Peak drive current (AOUT1, AOUT2, BOUT1, BOUT2, AISEN, BISEN)                                    | Interna | lly limited | А    |

| Operating junction temperature, T <sub>J</sub>                                                   | -40     | 150         | °C   |

| Storage temperature, T <sub>stg</sub>                                                            | -65     | 150         | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Transients of ±1 V for less than 25 ns are acceptable

# 6.2 ESD Ratings

|        |               |                                                                                | VALUE | UNIT |

|--------|---------------|--------------------------------------------------------------------------------|-------|------|

| V      | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±4000 | M    |

| V(ESD) | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (2)

# 6.3 Recommended Operating Conditions

|                   |                               | MIN                | MAX                | UNIT |

|-------------------|-------------------------------|--------------------|--------------------|------|

| VM                | Power supply voltage range    | 6.5 <sup>(1)</sup> | 45                 | V    |

| V <sub>IN</sub>   | Digital pin voltage range     | 0                  | 5.3                | V    |

| VREF              | Reference rms voltage range   | 0.3 <sup>(2)</sup> | V3P3               | V    |

| f <sub>PWM</sub>  | Applied STEP signal           | 0                  | 100 <sup>(3)</sup> | kHz  |

| I <sub>V3P3</sub> | V3P3 external load current    | 0                  | 10 <sup>(4)</sup>  | mA   |

| I <sub>FS</sub>   | Motor full scale current      | 0                  | 2.0                | А    |

| I <sub>rms</sub>  | Motor rms current             | 0                  | 1.4                | А    |

| T <sub>A</sub>    | Operating ambient temperature | -40                | 125                | °C   |

Internal logic and indexer remain active down to V<sub>UVLO2</sub> (4.9 V maximum) even though the output H-bridges are disabled Operational at VREF  $\approx$  0 to 0.3 V, but accuracy is degraded (1)

(2)

(3) STEP input can operate up to 1 MHz, but system bandwidth is limited by the motor load

Power dissipation and thermal limits must be observed (4)

# 6.4 Thermal Information

|                       |                                              | DRV          | 8880       |      |

|-----------------------|----------------------------------------------|--------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | RHR (WQFN) | UNIT |

|                       |                                              | 28 PINS      | 28 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 33.1         | 37.5       | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 16.6         | 23.0       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 14.4         | 8.0        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.4          | 0.2        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 14.2         | 7.8        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.3          | 1.7        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                          | TEST CONDITIONS                                                                             | MIN | TYP        | MAX | UNIT |  |

|-----------------------|------------------------------------|---------------------------------------------------------------------------------------------|-----|------------|-----|------|--|

| POWER S               | SUPPLIES (VM, V3P3)                |                                                                                             |     |            |     |      |  |

| VM                    | VM operating voltage               |                                                                                             | 6.5 |            | 45  | V    |  |

| I <sub>VM</sub>       | VM operating supply current        | nSLEEP high; ENABLE high; no motor<br>load; VM = 24 V                                       |     | 8          | 18  | mA   |  |

|                       |                                    | nSLEEP low; VM = 24 V; $T_A = 25^{\circ}C$                                                  |     | 28         |     |      |  |

| I <sub>VMQ</sub>      | VM sleep mode supply current       | $\underset{(1)}{\text{nSLEEP low; VM}} = 24 \text{ V; } T_{\text{A}} = 125^{\circ}\text{C}$ |     |            | 77  | μA   |  |

| t <sub>SLEEP</sub>    | Sleep time                         | nSLEEP low to sleep mode                                                                    |     |            | 100 | μS   |  |

| t <sub>WAKE</sub>     | Wake-up time                       | nSLEEP high to output transition                                                            |     |            | 1.5 | ms   |  |

| t <sub>ON</sub>       | Turn-on time                       | $VM > V_{UVLO2}$ to output transition                                                       |     |            | 1.5 | ms   |  |

| V3P3                  | LDO regulator voltage              | External load 0 to 10 mA                                                                    | 2.9 | 3.3        | 3.6 | V    |  |

| CHARGE                | PUMP (VCP, CPH, CPL)               |                                                                                             |     |            |     |      |  |

| V                     | VCD operating valtage              | VM > 12 V                                                                                   | V   | ′M + 11.5  |     | V    |  |

| V <sub>CP</sub>       | VCP operating voltage              | $V_{UVLO2} < VM < 12 V$                                                                     | 2×  | 2×VM – 1.5 |     | V    |  |

| $f_{ m VCP}$ $^{(1)}$ | Charge pump switching<br>frequency | $VM > V_{UVLO2}$                                                                            | 175 |            | 715 | kHz  |  |

| LOGIC-LE              | EVEL INPUTS (STEP, DIR, ENABLE     | E, nSLEEP, TRQ0, TRQ1, ATE)                                                                 |     |            |     |      |  |

| V <sub>IL</sub>       | Input logic low voltage            |                                                                                             | 0   |            | 0.6 | V    |  |

| VIH                   | Input logic high voltage           |                                                                                             | 1.6 |            | 5.3 | V    |  |

| V <sub>HYS</sub>      | Input logic hysteresis             |                                                                                             | 100 |            |     | mV   |  |

| IIL                   | Input logic low current            | V <sub>IN</sub> = 0 V                                                                       | -1  |            | 1   | μA   |  |

| I <sub>IH</sub>       | Input logic high current           | V <sub>IN</sub> = 5.0 V                                                                     |     | 50         | 100 | μA   |  |

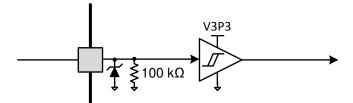

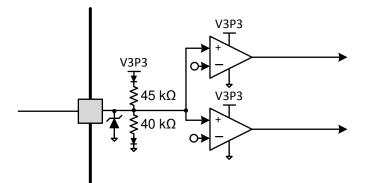

| R <sub>PD</sub>       | Pulldown resistance                | Measured between the pin and GND                                                            |     | 100        |     | kΩ   |  |

| t <sub>PD</sub>       | Propagation delay                  | STEP input to current change                                                                |     | 450        |     | ns   |  |

| TRI-LEVE              | L INPUTS (M0, M1, DECAYO, DEC.     | AY1, TOFF)                                                                                  |     |            |     |      |  |

| V <sub>IL</sub>       | Tri-level input logic low voltage  |                                                                                             | 0   |            | 0.6 | V    |  |

| V <sub>IZ</sub>       | Tri-level input Hi-Z voltage       |                                                                                             |     | 1.1        |     | V    |  |

| VIH                   | Tri-level input logic high voltage |                                                                                             | 1.6 |            | 5.3 | V    |  |

| V <sub>HYS</sub>      | Tri-level input hysteresis         |                                                                                             | 100 |            |     | mV   |  |

| IIL                   | Tri-level input logic low current  | V <sub>IN</sub> = 0 V                                                                       | -55 |            | -35 | μA   |  |

| I <sub>IZ</sub>       | Tri-level input Hi-Z current       | V <sub>IN</sub> = 1.3 V                                                                     |     | 15         |     | μA   |  |

| I <sub>IH</sub>       | Tri-level input logic high current | V <sub>IN</sub> = 3.3 V                                                                     |     | 85         |     | μA   |  |

| R <sub>PD</sub>       | Tri-level pulldown resistance      | Measured between the pin and GND                                                            |     | 40         |     | kΩ   |  |

| R <sub>PU</sub>       | Tri-level pullup resistance        | Measured between V3P3 and the pin                                                           |     | 45         |     | kΩ   |  |

(1) Specified by design and characterization data

6 Submit Documentation Feedback

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                                                    | PARAMETER                         | TEST CONDITIONS                                           | MIN  | ТҮР      | MAX  | UNIT      |

|----------------------------------------------------|-----------------------------------|-----------------------------------------------------------|------|----------|------|-----------|

| CONTROL                                            | OUTPUTS (nFAULT)                  |                                                           |      |          |      |           |

| V <sub>OL</sub>                                    | Output logic low voltage          | $I_0 = 4 \text{ mA}$                                      |      |          | 0.5  | V         |

| ОН                                                 | Output logic high leakage         | External pullup resistor to 3.3 V                         | -1   |          | 1    | μA        |

| IOTOR D                                            | RIVER OUTPUTS (AOUT1, AOUT2       | 2, BOUT1, BOUT2)                                          |      |          |      |           |

|                                                    |                                   | VM = 24 V, I = 1 A, T <sub>A</sub> = 25°C                 |      | 330      |      |           |

| -                                                  |                                   | VM = 24 V, I = 1 A, T <sub>A</sub> = 125°C <sup>(1)</sup> |      | 400      | 440  | 440<br>mΩ |

| RDS(ON)                                            | High-side FET on resistance       | VM = 6.5 V, I = 1 A, T <sub>A</sub> = 25°C                |      | 430      |      |           |

|                                                    |                                   | $VM = 6.5 V, I = 1 A, T_A = 125^{\circ}C^{(1)}$           |      | 500      | 560  |           |

|                                                    |                                   | VM = 24 V, I = 1 A, T <sub>A</sub> = 25°C                 |      | 300      |      |           |

| -                                                  |                                   | $VM = 24 V, I = 1 A, T_A = 125^{\circ}C^{(1)}$            |      | 370      | 400  |           |

| R <sub>DS(ON)</sub>                                | Low-side FET on resistance        | VM = 6.5 V, I = 1 A, T <sub>A</sub> = 25°C                |      | 370      |      | mΩ        |

|                                                    |                                   | $VM = 6.5 V, I = 1 A, T_A = 125^{\circ}C^{(1)}$           |      | 450      | 490  |           |

| RISE                                               | Output rise time                  | VM = 24 V, 50 $\Omega$ load from xOUTx to GND             |      | 70       |      | ns        |

| FALL                                               | Output fall time                  | VM = 24 V, 50 $\Omega$ load from VM to xOUTx              |      | 70       |      | ns        |

| DEAD                                               | Output dead time (2)              |                                                           |      | 200      |      | ns        |

| V <sub>d</sub>                                     | Body diode forward voltage        | I <sub>OUT</sub> = 0.5 A                                  |      | 0.7      | 1    | V         |

| PWM CUR                                            | RENT CONTROL (VREF, AISEN,        | BISEN)                                                    |      |          |      |           |

|                                                    |                                   | TRQ at 100%, VREF = 3.3 V                                 |      | 500      |      |           |

| ,                                                  |                                   | TRQ at 75%, VREF = 3.3 V                                  |      | 375      |      | mV        |

| V <sub>TRIP</sub> xISENSE trip voltage, full scale | xISENSE trip voltage, full scale  | TRQ at 50%, VREF = 3.3 V                                  |      | 250      |      |           |

|                                                    | TRQ at 25%, VREF = 3.3 V          |                                                           | 125  |          |      |           |

|                                                    |                                   | TRQ at 100% (TRQ0 = 0, TRQ1 = 0)                          | 6.25 | 6.58     | 6.91 |           |

| •                                                  |                                   | TRQ at 75% (TRQ0 = 1, TRQ1 = 0)                           | 6.2  | 6.56     | 6.92 |           |

| A <sub>V</sub>                                     | Amplifier attenuation             | TRQ at 50% (TRQ0 = 0, TRQ1 = 1)                           | 6.09 | 6.51     | 6.94 | V/V       |

|                                                    |                                   | TRQ at 25% (TRQ0 = 1, TRQ1 = 1)                           | 5.83 | 6.38     | 6.93 |           |

|                                                    |                                   | TOFF Logic Low                                            |      | 20       |      |           |

| OFF                                                | PWM off-time                      | TOFF Logic High                                           |      | 30       |      | μS        |

|                                                    |                                   | TOFF Hi-Z                                                 |      | 10       |      |           |

|                                                    |                                   |                                                           |      | 1.8      |      |           |

|                                                    |                                   |                                                           |      | 1.5      |      |           |

| t <sub>BLANK</sub>                                 | PWM blanking time                 | See Table 9 for details                                   |      | 1.2      |      | μs        |

|                                                    |                                   |                                                           |      | 0.9      |      |           |

| PROTECT                                            | ION CIRCUITS                      |                                                           |      |          | +    |           |

|                                                    |                                   | VM falling; UVLO2 report                                  |      | 5.8      | 6.4  |           |

| V <sub>UVLO2</sub>                                 | VM undervoltage lockout           | VM rising; UVLO2 recovery                                 |      | 6.1      | 6.5  | V         |

| .,                                                 |                                   | VM falling; logic disabled                                |      | 4.5      | 4.9  |           |

| V <sub>UVLO1</sub>                                 | Logic undervoltage                | VM rising; logic enabled                                  |      | 4.8      | 5    | V         |

| VUVLO,HYS                                          | undervoltage hysteresis           | Rising to falling threshold                               | 100  |          |      | mV        |

|                                                    |                                   | VCP falling; CPUV report                                  |      | VM + 1.8 |      |           |

| V <sub>CPUV</sub>                                  | Charge pump undervoltage          | VCP rising; CPUV recovery                                 |      | VM + 1.9 |      | V         |

| V <sub>CPUV,HYS</sub>                              | CP undervoltage hysteresis        | Rising to falling threshold                               | 50   |          |      | mV        |

| OCP                                                | Overcurrent protection trip level | Current through any FET                                   | 2.5  | 3.6      |      | А         |

| V <sub>OCP</sub>                                   | Sense pin overcurrent trip level  | Voltage at AISEN or BISEN                                 | 0.9  | 1.25     |      | V         |

| t <sub>OCP</sub>                                   | Overcurrent deglitch time         | <b>5</b>                                                  |      | 2        |      | μS        |

(2) Specified by design and characterization data

Copyright © 2015–2017, Texas Instruments Incorporated

STRUMENTS

XAS

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                       |                              | TEST CONDITIONS                | MIN | ТҮР | MAX | UNIT |

|---------------------------------|------------------------------|--------------------------------|-----|-----|-----|------|

| t <sub>RETRY</sub>              | Overcurrent retry time       |                                | 0.5 |     | 2   | ms   |

| $T_{TSD}$ <sup>(2)</sup>        | Thermal shutdown temperature | Die temperature T <sub>J</sub> | 150 |     |     | °C   |

| T <sub>HYS</sub> <sup>(2)</sup> | Thermal shutdown hysteresis  | Die temperature T <sub>J</sub> |     | 35  |     | °C   |

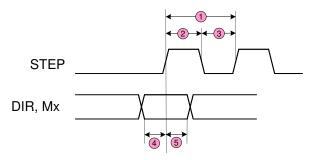

# 6.6 Indexer Timing Requirements

| NO. |                          |                                      | MIN | MAX              | UNIT |

|-----|--------------------------|--------------------------------------|-----|------------------|------|

| 1   | f <sub>step</sub>        | Step frequency                       |     | 1 <sup>(1)</sup> | MHz  |

| 2   | t <sub>WH(STEP)</sub>    | Pulse duration, STEP high            | 470 |                  | ns   |

| 3   | t <sub>WL(STEP)</sub>    | Pulse duration, STEP low             | 470 |                  | ns   |

| 4   | t <sub>SU(DIR, Mx)</sub> | Setup time, DIR or Mx to STEP rising | 200 |                  | ns   |

| 5   | t <sub>H(DIR, Mx)</sub>  | Hold time, DIR or Mx to STEP rising  | 200 |                  | ns   |

(1) STEP input can operate up to 1 MHz, but system bandwidth is limited by the motor load

Figure 1. Timing Diagram

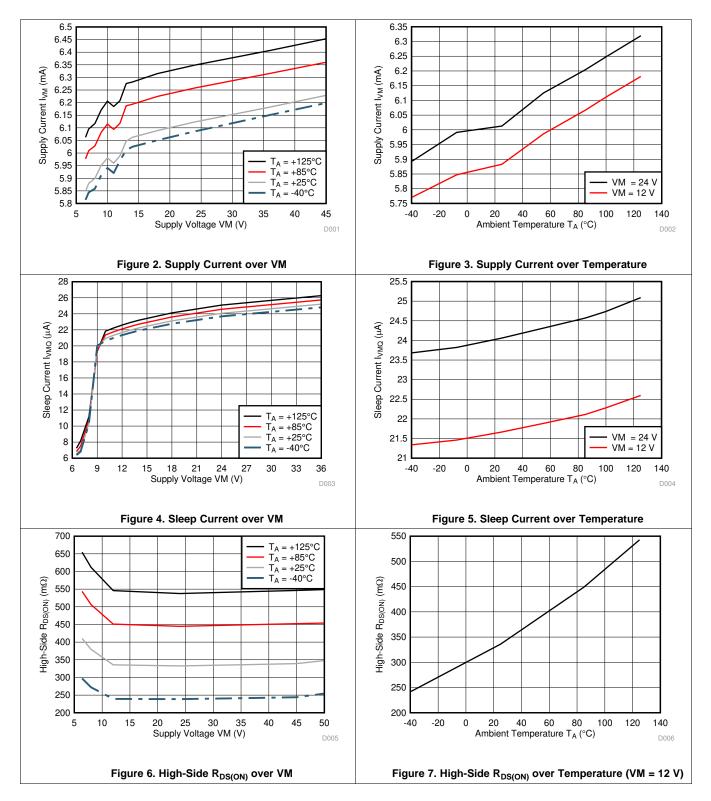

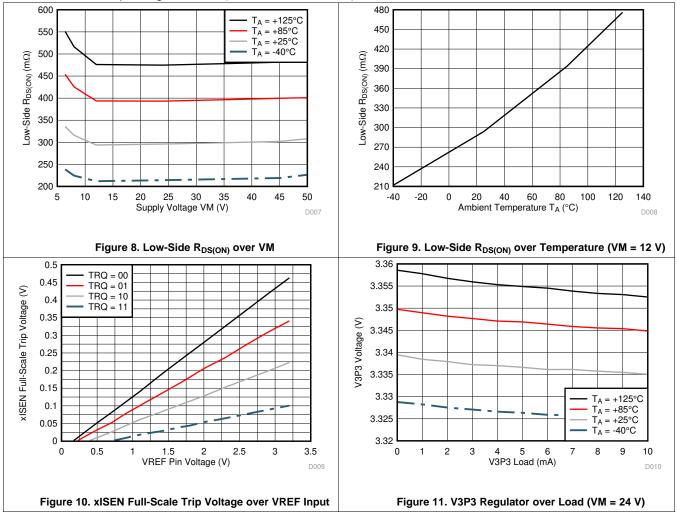

# 6.7 Typical Characteristics

Over recommended operating conditions (unless otherwise noted)

# **Typical Characteristics (continued)**

Over recommended operating conditions (unless otherwise noted)

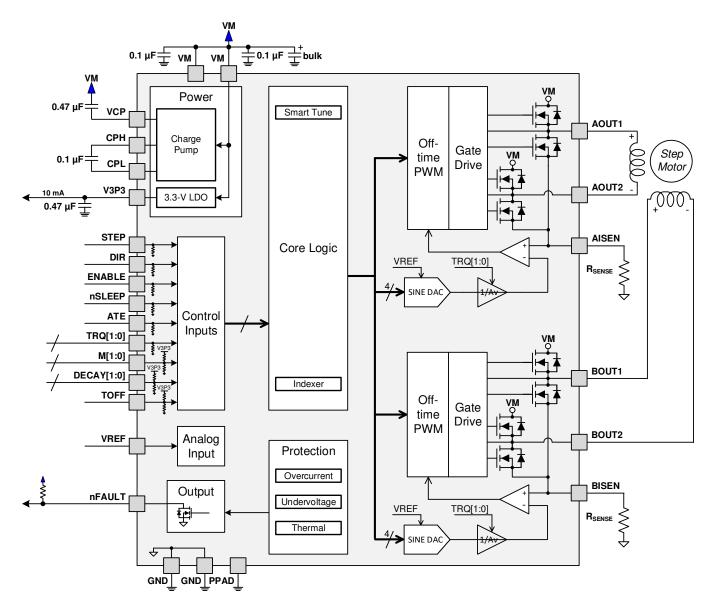

# 7 Detailed Description

# 7.1 Overview

The DRV8880 is an integrated motor driver solution for bipolar stepper motors. The device integrates two NMOS H-bridges, current regulation circuitry, and a microstepping indexer. The DRV8880 can be powered with a supply voltage between 6.5 and 45 V, and is capable of providing an output current up to 2.5 A peak current, 2.0 A full-scale current, or 1.4 A rms current. Actual operable full-scale and rms current will depend on ambient temperature, supply voltage, and PCB ground plane size. Between VM = 6.4 V and VM = 4.9 V the H-bridge outputs are shut down, but the internal logic remains active in order to prevent missed steps.

A simple STEP/DIR interface allows easy interfacing to the controller circuit. The internal indexer is able to execute high-accuracy microstepping without requiring the processor to control the current level. The indexer is capable of full step and half step as well as microstepping to 1/4, 1/8, and 1/16. In addition to the standard half stepping mode, a non-circular 1/2-stepping mode is available for increased torque output at higher motor rpm.

The current regulation is highly configurable, with several decay modes of operation. The decay mode can be selected as a fixed slow, slow/mixed, mixed, slow/fast, or fast decay. The slow/mixed decay mode uses slow decay on increasing steps and mixed decay on decreasing steps. Similarly, the slow/fast decay mode uses slow decay on increasing steps and fast decay on decreasing steps.

In addition, an smart tune mode can be used which automatically adjusts the decay setting to minimize current ripple while still reacting quickly to step changes. This feature greatly simplifies stepper driver integration into a motor drive system.

The PWM off-time,  $t_{OFF}$ , can be adjusted to 10, 20, or 30 µs.

An adaptive blanking time feature automatically scales the minimum drive time with output current. This helps alleviate zero-crossing distortion by limiting the drive time at low-current steps.

A torque DAC feature allows the controller to scale the output current without needing to scale the analog reference voltage input VREF. The torque DAC is accessed using digital input pins. This allows the controller to save power by decreasing the current consumption when not required.

A low-power sleep mode is included which allows the system to save power when not driving the motor.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

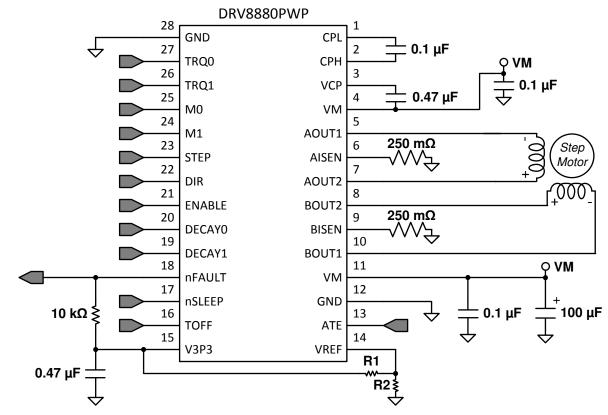

Table 1 lists the recommended values of the external components.

| COMPONENT           | PIN 1                           | PIN 2  | RECOMMENDED                                                                                               |  |  |  |

|---------------------|---------------------------------|--------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| C <sub>VM1</sub>    | VM                              | GND    | 0.1-µF ceramic capacitor rated for VM per VM pin                                                          |  |  |  |

| C <sub>VM1</sub>    | VM                              | GND    | Bulk electrolytic capacitor rated for VM, recommended value is 100 µF, see <i>Bulk Capacitance Sizing</i> |  |  |  |

| C <sub>VCP</sub>    | VCP                             | VM     | 16-V, 0.47-µF ceramic capacitor                                                                           |  |  |  |

| C <sub>SW</sub>     | CPH                             | CPL    | 0.1-µF X7R capacitor rated for VM                                                                         |  |  |  |

| C <sub>V3P3</sub>   | V3P3                            | GND    | 6.3-V, 0.47-µF ceramic capacitor                                                                          |  |  |  |

| R <sub>nFAULT</sub> | V <sub>MCU</sub> <sup>(1)</sup> | nFAULT | > 5 kΩ pullup                                                                                             |  |  |  |

| R <sub>AISEN</sub>  | AISEN                           | GND    | Sense resistor, see Sense Resistor                                                                        |  |  |  |

| R <sub>BISEN</sub>  | BISEN                           | GND    |                                                                                                           |  |  |  |

#### **Table 1. External Components**

V<sub>MCU</sub> is not a pin on the DRV8880, but a supply voltage pullup is required for open-drain output nFAULT; nFAULT may be pulled up to V3P3

### 7.3.1 Stepper Motor Driver Current Ratings

Stepper motor drivers can be classified using three different numbers to describe the output current: peak, rms, and full-scale.

### 7.3.1.1 Peak Current Rating

The peak current in a stepper driver is limited by the overcurrent protection trip threshold  $I_{OCP}$ . The peak current describes any transient duration current pulse, for example when charging capacitance, when the overall duty cycle is very low. In general the minimum value of  $I_{OCP}$  specifies the peak current rating of the stepper motor driver. For the DRV8880, the peak current rating is 2.5 A per bridge.

### 7.3.1.2 RMS Current Rating

The rms (average) current is determined by the thermal considerations of the IC. The rms current is calculated based on the  $R_{DS(ON)}$ , rise and fall time, PWM frequency, device quiescent current, and package thermal performance in a typical system at 25°C. The real operating rms current may be higher or lower depending on heatsinking and ambient temperature. For the DRV8880, the rms current rating is 1.4 A per bridge.

### 7.3.1.3 Full-Scale Current Rating

The full-scale current describes the top of the sinusoid current waveform while microstepping. Since the sineusoid amplitude is related to the rms current, the full-scale current is also determined by the thermal considerations of the IC. The full-scale current rating is approximately  $\sqrt{2 \times I_{rms}}$ . The full-scale current is set by VREF, the sense resistor, and Torque DAC when configuring the DRV8880, see *Current Regulation* for details. For the DRV8880, the full-scale current rating is 2.0 A per bridge.

Figure 12. Full-Scale and rms Current

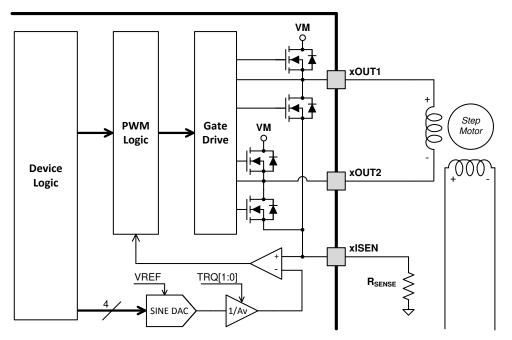

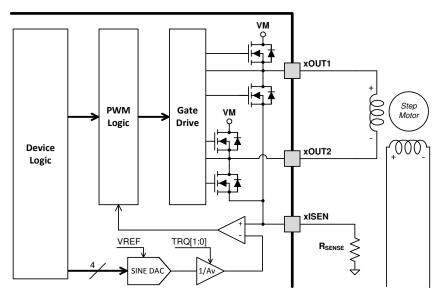

## 7.3.2 PWM Motor Drivers

The DRV8880 contains drivers for two full H-bridges. A block diagram of the circuitry is shown in Figure 13.

Figure 13. PWM Motor Driver Block Diagram

## 7.3.3 Microstepping Indexer

Built-in indexer logic in the DRV8880 allows a number of different stepping configurations. The Mx pins are used to configure the stepping format as shown in Table 2.

| M1 | MO | STEP MODE                                       |  |  |

|----|----|-------------------------------------------------|--|--|

| 0  | 0  | Full step (2-phase excitation) with 71% current |  |  |

| 0  | 1  | Non-circular 1/2 step                           |  |  |

| 1  | 0  | 1/2 step                                        |  |  |

| 1  | 1  | 1/4 step                                        |  |  |

| 0  | Z  | 1/8 step                                        |  |  |

| 1  | Z  | 1/16 step                                       |  |  |

| Z  | 0  | Reserved                                        |  |  |

| Z  | 1  | Reserved                                        |  |  |

| Z  | Z  | Reserved                                        |  |  |

### Table 2. Microstepping Settings

Table 3 shows the relative current and step directions for full-step through 1/16-step operation. The AOUT current is the sine of the electrical angle; BOUT current is the cosine of the electrical angle. Positive current is defined as current flowing from xOUT1 to xOUT2 while driving.

At each rising edge of the STEP input the indexer travels to the next state in the table. The direction is shown with the DIR pin logic high. If the DIR pin is logic low, the sequence is reversed.

Note that if the step mode is changed while stepping, the indexer will advance to the next valid state for the new MODE setting at the rising edge of STEP.

The home state is an electrical angle of 45°. This state is entered after power-up, after exiting logic undervoltage lockout, or after exiting sleep mode. This is shown in Table 3 with the highlighted row.

| Table 3. Microstepping Relative Current Per Step |          |          |          |           |                         |                                |                                |

|--------------------------------------------------|----------|----------|----------|-----------|-------------------------|--------------------------------|--------------------------------|

| FULL<br>STEP                                     | 1/2 STEP | 1/4 STEP | 1/8 STEP | 1/16 STEP | ELECTRICAL ANGLE<br>(°) | AOUT CURRENT<br>(% full-scale) | BOUT CURRENT<br>(% full-scale) |

|                                                  | 1        | 1        | 1        | 1         | 0.000°                  | 0%                             | 100%                           |

|                                                  |          |          |          | 2         | 5.625°                  | 10%                            | 100%                           |

|                                                  |          |          | 2        | 3         | 11.250°                 | 20%                            | 98%                            |

|                                                  |          |          |          | 4         | 16.875°                 | 29%                            | 96%                            |

|                                                  |          | 2        | 3        | 5         | 22.500°                 | 38%                            | 92%                            |

|                                                  |          |          |          | 6         | 28.125°                 | 47%                            | 88%                            |

|                                                  |          |          | 4        | 7         | 33.750°                 | 56%                            | 83%                            |

|                                                  |          |          |          | 8         | 39.375°                 | 63%                            | 77%                            |

| 1                                                | 2        | 3        | 5        | 9         | 45.000°                 | 71%                            | 71%                            |

|                                                  |          |          |          | 10        | 50.625°                 | 77%                            | 63%                            |

|                                                  |          |          | 6        | 11        | 56.250°                 | 83%                            | 56%                            |

|                                                  |          |          |          | 12        | 61.875°                 | 88%                            | 47%                            |

|                                                  |          | 4        | 7        | 13        | 67.500°                 | 92%                            | 38%                            |

|                                                  |          |          |          | 14        | 73.125°                 | 96%                            | 29%                            |

|                                                  |          |          | 8        | 15        | 78.750°                 | 98%                            | 20%                            |

|                                                  |          |          |          | 16        | 84.375°                 | 100%                           | 10%                            |

|                                                  | 3        | 5        | 9        | 17        | 90.000°                 | 100%                           | 0%                             |

|                                                  | _        |          |          | 18        | 95.625°                 | 100%                           | -10%                           |

|                                                  |          |          | 10       | 19        | 101.250°                | 98%                            | -20%                           |

|                                                  |          |          |          | 20        | 106.875°                | 96%                            | -29%                           |

|                                                  |          | 6        | 11       | 21        | 112.500°                | 92%                            | -38%                           |

|                                                  |          |          |          | 22        | 118.125°                | 88%                            | -47%                           |

|                                                  |          |          | 12       | 23        | 123.750°                | 83%                            | -56%                           |

|                                                  |          |          |          | 24        | 129.375°                | 77%                            | -63%                           |

| 2                                                | 4        | 7        | 13       | 25        | 135.000°                | 71%                            | -71%                           |

|                                                  |          | -        |          | 26        | 140.625°                | 63%                            | -77%                           |

|                                                  |          |          | 14       | 27        | 146.250°                | 56%                            | -83%                           |

|                                                  |          |          |          | 28        | 151.875°                | 47%                            | -88%                           |

|                                                  |          | 8        | 15       | 29        | 157.500°                | 38%                            | -92%                           |

|                                                  |          | 0        | 10       | 30        | 163.125°                | 29%                            | -96%                           |

|                                                  |          |          | 16       | 31        | 168.750°                | 20%                            | -98%                           |

|                                                  |          |          | 10       | 32        | 174.375°                | 10%                            | -100%                          |

|                                                  | 5        | 9        | 17       | 33        | 180.000°                | 0%                             | -100%                          |

|                                                  | 5        | 9        | 17       | 34        | 185.625°                |                                | -100%                          |

|                                                  |          |          | 18       | 35        | 191.250°                | -20%                           | -98%                           |

|                                                  |          |          | 10       |           |                         |                                | -98%                           |

|                                                  |          | 10       | 10       | 36        | 196.875°                | -29%                           |                                |

|                                                  |          | 10       | 19       | 37        | 202.500°                | -38%                           | -92%                           |

|                                                  |          |          | 20       | 38        | 208.125°                | -47%                           | -88%                           |

|                                                  |          |          | 20       | 39        | 213.750°                | -56%                           | -83%                           |

| 2                                                | 0        | 44       | 04       | 40        | 219.375°                | -63%                           | -77%                           |

| 3                                                | 6        | 11       | 21       | 41        | 225.000°                | -71%                           | -71%                           |

|                                                  |          |          |          | 42        | 230.625°                | -77%                           | -63%                           |

|                                                  |          |          | 22       | 43        | 236.250°                | -83%                           | -56%                           |

|                                                  |          |          |          | 44        | 241.875°                | -88%                           | -47%                           |

|                                                  |          | 12       | 23       | 45        | 247.500°                | -92%                           | -38%                           |

|                                                  |          |          |          | 46        | 253.125°                | -96%                           | -29%                           |

|                                                  |          |          | 24       | 47        | 258.750°                | -98%                           | -20%                           |

# Table 3. Microstepping Relative Current Per Step

Copyright © 2015–2017, Texas Instruments Incorporated

SLVSD18C – JUNE 2015 – REVISED AUGUST 2017

**DRV8880**

| Table 3. Microstepping Relative Current Per Step (continued) |          |          |          |           |                         |                                |                                |

|--------------------------------------------------------------|----------|----------|----------|-----------|-------------------------|--------------------------------|--------------------------------|

| FULL<br>STEP                                                 | 1/2 STEP | 1/4 STEP | 1/8 STEP | 1/16 STEP | ELECTRICAL ANGLE<br>(°) | AOUT CURRENT<br>(% full-scale) | BOUT CURRENT<br>(% full-scale) |

|                                                              |          |          |          | 48        | 264.375°                | -100%                          | -10%                           |

|                                                              | 7        | 13       | 25       | 49        | 270.000°                | -100%                          | 0%                             |

|                                                              |          |          |          | 50        | 275.625°                | -100%                          | 10%                            |

|                                                              |          |          | 26       | 51        | 281.250°                | -98%                           | 20%                            |

|                                                              |          |          |          | 52        | 286.875°                | -96%                           | 29%                            |

|                                                              |          | 14       | 27       | 53        | 292.500°                | -92%                           | 38%                            |

|                                                              |          |          |          | 54        | 298.125°                | -88%                           | 47%                            |

|                                                              |          |          | 28       | 55        | 303.750°                | -83%                           | 56%                            |

|                                                              |          |          |          | 56        | 309.375°                | -77%                           | 63%                            |

| 4                                                            | 8        | 15       | 29       | 57        | 315.000°                | -71%                           | 71%                            |

|                                                              |          |          |          | 58        | 320.625°                | -63%                           | 77%                            |

|                                                              |          |          | 30       | 59        | 326.250°                | -56%                           | 83%                            |

|                                                              |          |          |          | 60        | 331.875°                | -47%                           | 88%                            |

|                                                              |          | 16       | 31       | 61        | 337.500°                | -38%                           | 92%                            |

|                                                              |          |          |          | 62        | 343.125°                | -29%                           | 96%                            |

|                                                              |          |          | 32       | 63        | 348.750°                | -20%                           | 98%                            |

|                                                              |          |          |          | 64        | 354.375°                | -10%                           | 100%                           |

|                                                              | 1        | 1        | 1        | 1         | 360.000°                | 0%                             | 100%                           |

# Table 3. Microstepping Relative Current Per Step (continued)

Non-circular 1/2–step operation is shown in Table 4. This stepping mode consumes more power than circular 1/2-step operation, but provides a higher torque at high motor rpm.

# Table 4. Non-Circular 1/2-Stepping Current

| NON-CIRCULAR<br>1/2 STEP | ELECTRICAL ANGLE<br>(°) | AOUT CURRENT<br>(% FULL-SCALE) | BOUT CURRENT<br>(% FULL-SCALE) |

|--------------------------|-------------------------|--------------------------------|--------------------------------|

| 1                        | 0°                      | 0                              | 100                            |

| 2                        | 45°                     | 100                            | 100                            |

| 3                        | 90°                     | 100                            | 0                              |

| 4                        | 135°                    | 100                            | -100                           |

| 5                        | 180°                    | 0                              | -100                           |

| 6                        | 225°                    | -100                           | -100                           |

| 7                        | 270°                    | -100                           | 0                              |

| 8                        | 315°                    | -100                           | 100                            |

www.ti.com

#### 7.3.4 Current Regulation

The current through the motor windings is regulated by an adjustable fixed-off-time PWM current regulation circuit. When an H-bridge is enabled, current rises through the winding at a rate dependent on the DC voltage, inductance of the winding, and the magnitude of the back EMF present. After the current hits the current chopping threshold, the bridge enters a decay mode for a fixed period of time to decrease the current, which is configurable between 10 and 30 µs through the tri-level input TOFF. After the off time expires, the bridge is re-enabled, starting another PWM cycle.

| Table | 5. | <b>Off-Time</b> | Settings |

|-------|----|-----------------|----------|

|-------|----|-----------------|----------|

| TOFF | OFF-TIME t <sub>OFF</sub> |

|------|---------------------------|

| 0    | 20 µs                     |

| 1    | 30 µs                     |

| Z    | 10 µs                     |

The PWM chopping current is set by a comparator which compares the voltage across a current sense resistor connected to the xISEN pin with a reference voltage. To generate the reference voltage for the current chopping comparator, the output of a sine lookup table is applied to a sine-weighted DAC, whose full-scale output voltage is set by VREF. This voltage is attenuated by a factor of Av. In addition, the TRQx pins further scale the reference.

Figure 14. Current Regulation Block Diagram

The full-scale (100%) chopping current is calculated as follows:

$$I_{FS} (A) = \frac{VREF (V) \times TRQ (\%)}{A_V \times R_{SENSE} (\Omega)} = \frac{VREF (V) \times TRQ (\%)}{6.6 \times R_{SENSE} (\Omega)}$$

(1)

The TRQx pins are the inputs to a Torque DAC used to scale the output current. The current scalar value for different inputs is shown below.

| TRQ1 | TRQ0 | CURRENT SCALAR<br>(TRQ) | EFFECTIVE<br>ATTENUATION |

|------|------|-------------------------|--------------------------|

| 1    | 1    | 25%                     | 26.4 V/V                 |

| 1    | 0    | 50%                     | 13.2 V/V                 |

| 0    | 1    | 75%                     | 8.8 V/V                  |

| 0    | 0    | 100%                    | 6.6 V/V                  |

| Table | 6. | Torque | DAC | Settings |

|-------|----|--------|-----|----------|

|-------|----|--------|-----|----------|

Table 7 gives the xISEN trip voltage at a given DAC code and TRQ[1:0] setting for 1/16 step mode. In this table, VREF = 3.3 V.

| 1/16 STEP (SINE | TORQUE DAC TRQ[1:0] SETTING |          |          |          |  |  |  |

|-----------------|-----------------------------|----------|----------|----------|--|--|--|

| DAC CODE)       | 00 – 100%                   | 01 – 75% | 10 – 50% | 11 – 25% |  |  |  |

| 16              | 500.0 mV                    | 375.0 mV | 250.0 mV | 125.0 mV |  |  |  |

| 15              | 490.0 mV                    | 367.5 mV | 245.0 mV | 122.5 mV |  |  |  |

| 14              | 480.0 mV                    | 360.0 mV | 240.0 mV | 120.0 mV |  |  |  |

| 13              | 460.0 mV                    | 345.0 mV | 230.0 mV | 115.0 mV |  |  |  |

| 12              | 440.0 mV                    | 330.0 mV | 220.0 mV | 110.0 mV |  |  |  |

| 11              | 415.0 mV                    | 311.3 mV | 207.5 mV | 103.8 mV |  |  |  |

| 10              | 385.0 mV                    | 288.8 mV | 192.5 mV | 96.3 mV  |  |  |  |

| 9               | 355.0 mV                    | 266.3 mV | 177.5 mV | 88.8 mV  |  |  |  |

| 8               | 315.0 mV                    | 236.3 mV | 157.5 mV | 78.8 mV  |  |  |  |

| 7               | 280.0 mV                    | 210.0 mV | 140.0 mV | 70.0 mV  |  |  |  |

| 6               | 235.0 mV                    | 176.3 mV | 117.5 mV | 58.8 mV  |  |  |  |

| 5               | 190.0 mV                    | 142.5 mV | 95.0 mV  | 47.5 mV  |  |  |  |

| 4               | 145.0 mV                    | 108.8 mV | 72.5 mV  | 36.3 mV  |  |  |  |

| 3               | 100.0 mV                    | 75.0 mV  | 50.0 mV  | 25.0 mV  |  |  |  |

| 2               | 50.0 mV                     | 37.5 mV  | 25.0 mV  | 12.5 mV  |  |  |  |

| 1               | 0.0 mV                      | 0.0 mV   | 0.0 mV   | 0.0 mV   |  |  |  |

# Table 7. xISEN Trip Voltages over Torque DAC and Microsteps

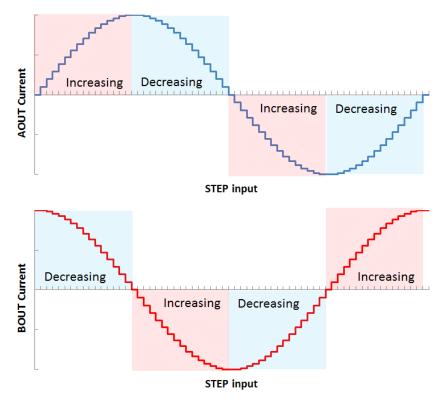

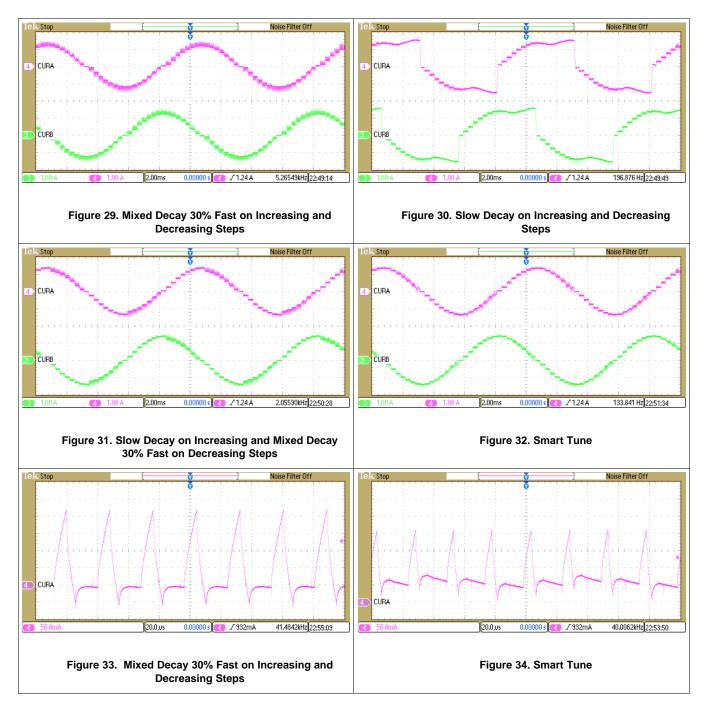

### 7.3.5 Decay Modes

A fixed decay mode is selected by setting the tri-level DECAYx pins as shown in Table 8. Please note that if the ATE pin is logic high, the DECAYx pins are ignored and smart tune is used.

| DECAY1 | DECAY0 | INCREASING STEPS                  | DECREASING STEPS                  |

|--------|--------|-----------------------------------|-----------------------------------|

| 0      | 0      | Slow Decay                        | Slow Decay                        |

| 0      | 1      | Slow Decay                        | Mixed Decay: 2 t <sub>BLANK</sub> |

| 1      | 0      | Slow Decay                        | Mixed Decay: 30% Fast             |

| 1      | 1      | Mixed Decay: 30% Fast             | Mixed Decay: 30% Fast             |

| 0      | Z      | Slow Decay                        | Mixed Decay: 60% Fast             |

| 1      | Z      | Slow Decay                        | Fast Decay                        |

| Z      | 0      | Mixed Decay: 1 t <sub>BLANK</sub> | Mixed Decay: 30% Fast             |

| Z      | 1      | Mixed Decay: 60% Fast             | Mixed Decay: 60% Fast             |

| Z      | Z      | Fast Decay                        | Fast Decay                        |

| Table | 8. | Decay | Mode | Settings |

|-------|----|-------|------|----------|

|-------|----|-------|------|----------|

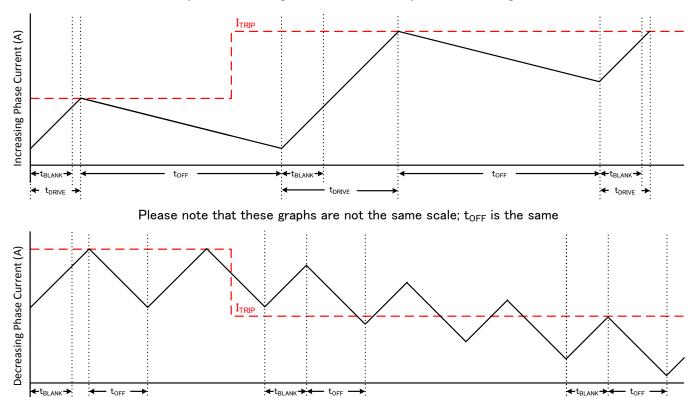

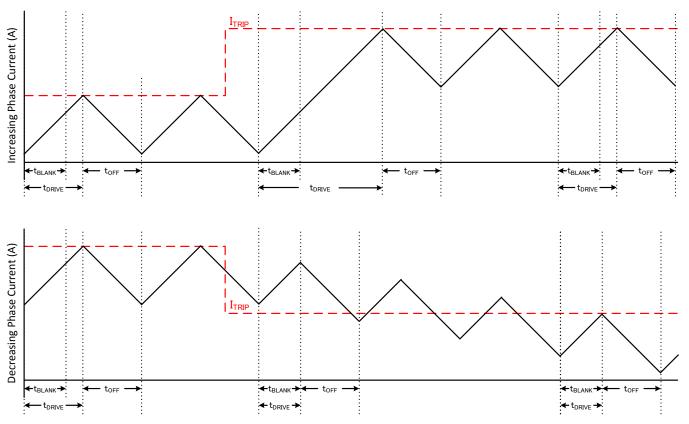

Increasing and decreasing current are defined in the chart below. For the Slow/Mixed decay mode, the decay mode is set as slow during increasing current steps and mixed decay during decreasing current steps. In full step mode, the increasing step decay mode is always used.

Figure 15. Definition of Increasing and Decreasing Steps

NSTRUMENTS

EXAS

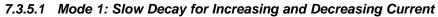

Figure 16. Slow/Slow Decay Mode

During slow decay, both of the low-side FETs of the H-bridge are turned on, allowing the current to be recirculated.

Slow decay exhibits the least current ripple of the decay modes for a given  $t_{OFF}$ . However on decreasing current steps, slow decay will take a long time to settle to the new ITRIP level because the current decreases very slowly.

In cases where current is held for a long time (no input in the STEP pin) or at very low stepping speeds, slow decay may not properly regulate current because no back-EMF is present across the motor windings. In this state, motor current can rise very quickly, and may require a large off-time. In some cases this may cause a loss of current regulation, and a more aggressive decay mode is recommended.

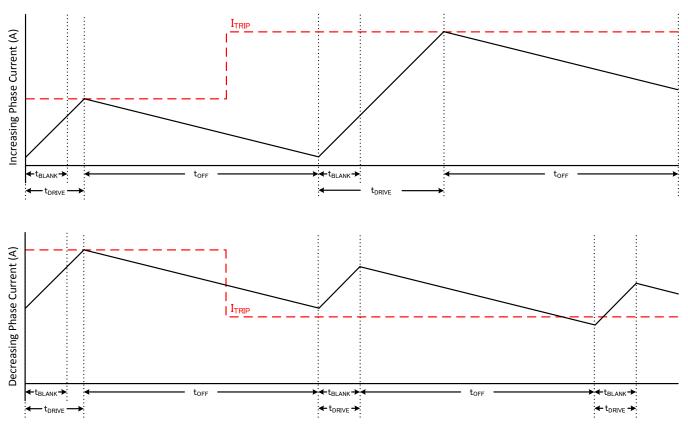

7.3.5.2 Mode 2: Slow Decay for Increasing Current, Mixed Decay for Decreasing current

Figure 17. Slow/Mixed Decay Mode

Mixed decay begins as fast decay for a time, followed by slow decay for the remainder of t<sub>OFF</sub>. In this mode, mixed decay only occurs during decreasing current. Slow decay is used for increasing current.

This mode exhibits the same current ripple as slow decay for increasing current, since for increasing current, only slow decay is used. For decreasing current, the ripple is larger than slow decay, but smaller than fast decay. On decreasing current steps, mixed decay will settle to the new  $I_{TRIP}$  level faster than slow decay.

In cases where current is held for a long time (no input in the STEP pin) or at very low stepping speeds, slow decay may not properly regulate current because no back-EMF is present across the motor windings. In this state, motor current can rise very quickly, and may require a large off-time. In some cases this may cause a loss of current regulation, and a more aggressive decay mode is recommended.

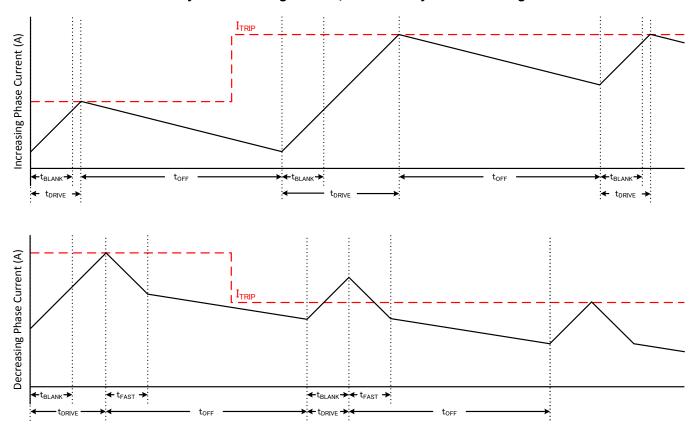

# 7.3.5.3 Mode 3: Mixed Decay for Increasing and Decreasing Current

Figure 18. Mixed/Mixed Decay Mode

Mixed decay begins as fast decay for a time, followed by slow decay for the remainder of t<sub>OFF</sub>. In this mode, mixed decay occurs for both increasing and decreasing current steps.

This mode exhibits ripple larger than slow decay, but smaller than fast decay. On decreasing current steps, mixed decay will settle to the new  $I_{TRIP}$  level faster than slow decay.

In cases where current is held for a long time (no input in the STEP pin) or at very low stepping speeds, slow decay may not properly regulate current because no back-EMF is present across the motor windings. In this state, motor current can rise very quickly, and requires an excessively large off-time. Increasing/decreasing mixed decay mode allows the current level to stay in regulation when no back-EMF is present across the motor windings.

www.ti.com

**NSTRUMENTS**

**EXAS**

t<sub>DRIVE</sub>

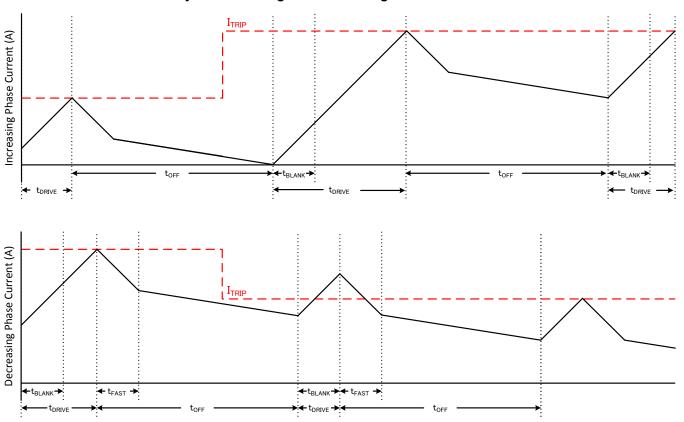

#### 7.3.5.4 Mode 4: Slow Decay for Increasing Current, Fast Decay for Decreasing current

Figure 19. Slow/Fast Decay Mode

← t<sub>DRIVE</sub> →

During fast decay, the polarity of the H-bridge is reversed. The H-bridge will be turned off as current approaches zero in order to prevent current flow in the reverse direction. In this mode, fast decay only occurs during decreasing current. Slow decay is used for increasing current.

Fast decay exhibits the highest current ripple of the decay modes for a given t<sub>OFF</sub>. Transition time on decreasing current steps is much faster than slow decay since the current is allowed to decrease much faster.

← t<sub>DRIVE</sub> →

Instruments

Texas

# 7.3.5.5 Mode 5: Fast Decay for Increasing and Decreasing Current

Figure 20. Fast/Fast Decay Mode

During fast decay, the polarity of the H-bridge is reversed. The H-bridge will be turned off as current approaches zero in order to prevent current flow in the reverse direction.

Fast decay exhibits the highest current ripple of the decay modes for a given t<sub>OFF</sub>. Transition time on decreasing current steps is much faster than slow decay since the current is allowed to decrease much faster.

#### 7.3.6 Smart Tune

To enable the smart tune mode, pull the ATE pin logic high. Ensure the DECAYx pins are logic low. The smart tune mode is registered internally when exiting from sleep mode or the power-up sequence. The ATE pin can be shorted to V3P3 to pull it logic high for this purpose.

Smart tune greatly simplifies the decay mode selection by automatically configuring the decay mode between slow, mixed, and fast decay. In mixed decay, smart tune dynamically adjusts the fast decay percentage of the total mixed decay time. This feature eliminates motor tuning by automatically determining the best decay setting that results in the lowest ripple for the motor.

The decay mode setting is optimized iteratively each PWM cycle. If the motor current overshoots the target trip level, then the decay mode becomes more aggressive (add fast decay percentage) on the next cycle in order to prevent regulation loss. If there is a long drive time to reach the target trip level, the decay mode becomes less aggressive (remove fast decay percentage) on the next cycle in order to operate with less ripple and more efficiently. On falling steps, smart tune will automatically switch to fast decay in order to reach the next step quickly.

Smart tune will automatically adjust the decay scheme based on operating factors like:

- Motor winding resistance and inductance

- Motor aging effects

- Motor dynamic speed and load

- Motor supply voltage variation

- Motor back-EMF difference on rising and falling steps

- Step transitions

- Low-current vs. high-current dl/dt

## 7.3.7 Adaptive Blanking Time

After the current is enabled in an H-bridge, the voltage on the xISEN pin is ignored for a period of time before enabling the current sense circuitry. Note that the blanking time also sets the minimum drive time of the PWM.

The blanking time is automatically scaled so that the drive time is reduced at lower current steps.

The time  $t_{BLANK}$  is determined by the sine DAC code and the torque DAC setting. The timing information for  $t_{BLANK}$  is given in Table 9.

Table 9. Adaptive Blanking Time Settings over Torque DAC and Microsteps

|               | TORQUE DAC TRQ[1:0] SETTING |          |          |          |  |  |

|---------------|-----------------------------|----------|----------|----------|--|--|

| SINE DAC CODE | 00 – 100%                   | 01 – 75% | 10 – 50% | 11 – 25% |  |  |

| 16            | 1.80 µs                     | 1.50 µs  | 1.50 µs  | 1.20 µs  |  |  |

| 15            | 1.80 µs                     | 1.50 µs  | 1.50 µs  | 1.20 µs  |  |  |

| 14            | 1.80 µs                     | 1.50 µs  | 1.50 µs  | 1.20 µs  |  |  |

| 13            | 1.80 µs                     | 1.50 µs  | 1.50 µs  | 1.20 µs  |  |  |

| 12            | 1.80 µs                     | 1.50 µs  | 1.50 µs  | 1.20 µs  |  |  |

| 11            | 1.80 µs                     | 1.50 µs  | 1.50 µs  | 1.20 µs  |  |  |

| 10            | 1.80 µs                     | 1.50 µs  | 1.50 µs  | 1.20 µs  |  |  |