# silicon systems®

### SSI 32D5371/5372

Data Synchronization/1, 7 RLL ENDEC with Write Precompensation

### **Advance Information**

July, 1990

#### DESCRIPTION

The SSI 32D5371/5372 Data Synchronizer/1, 7 RLL ENDEC provides data recovery and data encoding for storage systems which employ a 1, 7 RLL encoding format. Data synchronization is performed with a fully integrated high performance PLL. A zero phase restart technique is used to minimize PLL acquisition time. The SSI 32D5371/5372 has been optimized for operation as a companion device to the SSI 32C452 and AIC 010 controllers. The VCO frequency setting elements are incorporated within the SSI 32D5371/5372 for enhanced performance and reduced board space. Data rate is established with a single external programming resistor. The SSI 32D5371/5372 utilizes an advanced bipolar process technology which affords precise decode window control without the requirement of an accurate 1/3 cell delay or external devices. The SSI 32D5371/5372 requires a single +5V supply.

#### **FEATURES**

- 32D5371 ECL RD Input Option

- 32D5372 TTL RD Input Option

- Data Synchronizer and 1, 7 RLL ENDEC

- 10 to 24 Mbit/s operation Data Rate programmed with a single external resistor

- Optimized for operation with the SSI 32C452 and AIC 010 controllers.

- · Fast acquisition phase lock loop

- Zero phase restart technique

- Fully integrated data separator

- No external delay lines or active devices required

- Programmable write precompensation

- Hard and soft sector operation

- Crystal controlled reference oscillator

- +5V operation

- 28-Pin PLCC & 28-Pin DIP packages

- Test outputs Allow drive margin testing

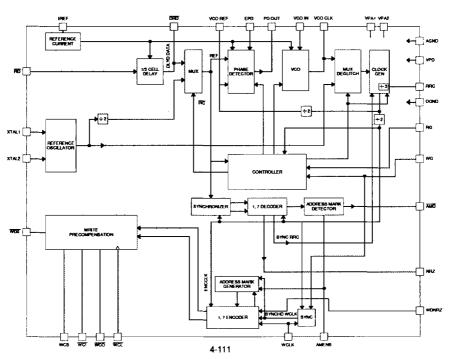

#### **BLOCK DIAGRAM**

#### **OPERATION**

The SSI 32D5371/5372 is designed to perform data recovery and data encoding in rotating memory systems which utilize a 1,7 RLL encoding format. In the Read Mode the SSI 32D5371/5372 performs Data Synchronization, Sync Field Search and Detect, Address Mark Detect, and Data Decoding. In the Write Mode, the SSI 32D5371/5372 converts NRZ data into the 1,7 RLL format described in Table 1, performs Write Precompensation, generates the Preamble Field, and inserts Address Marks as requested. The interface electronics and architecture of the SSI32D5371/5372 have been optimized for use as a companion device to the SSI 32C452 or AIC 010 controllers.

The SSI 32D5371/5372 can operate with data rates ranging from 10 to 24 Mbit/s. This data rate is established by a single 1% external resistor, RR, connected from pin IREF to VPA2. This resistor establishes a reference current which sets the VCO center frequency, the phase detector gain, and the 1/3 cell delay. The value of this resistor is given by:

$$RR = \frac{92.6}{DR} - 1.7 (k\Omega)$$

where: DR = Data Rate in Mbit/s.

An internal crystal reference oscillator, operating at three times the data rate, generates the standby reference for the PLL. A series resonant crystal between XTAL1 and XTAL2 should be selected at three times the Data Rate. If a crystal oscillator is not desired, then either an attenuated external TTL compatible reference or an AC coupled ECL source may be applied to XTAL1, leaving XTAL2 open.

The SSI 32D5371/5372 employs a Dual Mode Phase Detector; Harmonic in the Read Mode and Non Harmonic in Write and Idle Modes. In the Read Mode the Harmonic Phase Detector updates the PLL with each occurrence of a DYLD DATA pulse. In the Write and Idle modes the Non-Harmonic Phase Detector is continuously enabled, thus maintaining both phase and frequency lock. By acquiring both phase and frequency lock to the crystal reference oscillator and utilizing a zero phase restart technique, false lock to DLYD DATA is eliminated.

The phase detector incorporates a charge pump in order to drive the loop filter directly. The polarity and width of the output current pulses correspond to the direction and magnitude of the phase error.

The READ GATE (RG), and WRITE GATE (WG) inputs control the device mode.

RG is an asynchronous input and may be initiated or terminated at any position on the disk. WG is also an asynchronous input, but should not be terminated prior to the last output Write Data pulse.

#### **READ OPERATION**

The Data Synchronizer utilizes a fully integrated fast acquisition PLL to accurately develop the decode window. Read Gate, RG, initiates the PLL locking sequence and selects the PLL reference input; a high level (Read Mode) selects the RD input and a low level selects the crystal reference oscillator.

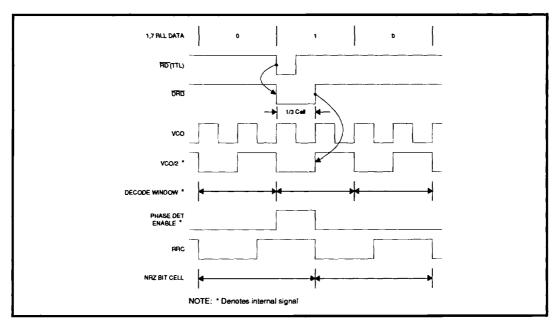

In the Read Mode the falling edge of  $\overline{DRD}$  enables the Phase Detector while the rising edge is phase compared to the rising edge of the VCO/2. As depicted in Figure 1,  $\overline{DRD}$  is a 1/3 cell wide (TVCO) pulse whose leading edge is defined by the leading edge of  $\overline{RD}$ . An accurate and symmetrical decode window is developed from the VCO/2 clock. By utilizing a fully integrated symmetrical VCO running at three times the data rate, the decode window is insured to be accurate and centered symmetrically about the rising edges of  $\overline{DRD}$ . The accuracy of the 1/3 cell delay only affects the retrace angle of the phase detector and does not influence the accuracy of the decode window.

In Non-Read Modes, the PLL is locked to the crystal reference oscillator. This forces the VCO to run at a frequency which is very close to that required for tracking actual data and thus minimizes the associated frequency step during acquisition. When the reference input to the PLL is switched, the VCO is stopped momentarily, then restarted in an accurate phase alignment with the next PLL reference input pulse, and the VCO clock divider is reset. By minimizing the phase alignment in this manner (phase error ≤ 1 rads), the acquisition time is substantially reduced.

4-112 0790 - rev.

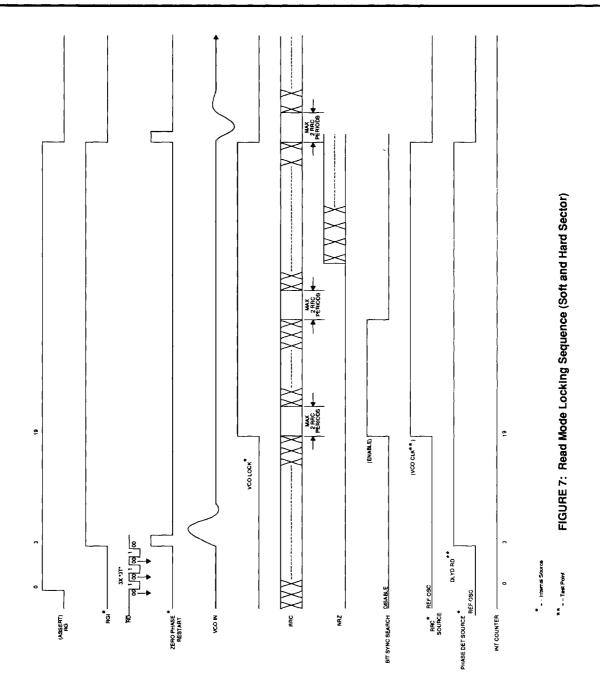

#### SOFT SECTOR OPERATION

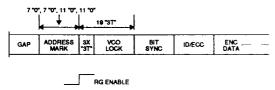

Disk Operation Lock Sequence in Read Mode Soft Sector Operation

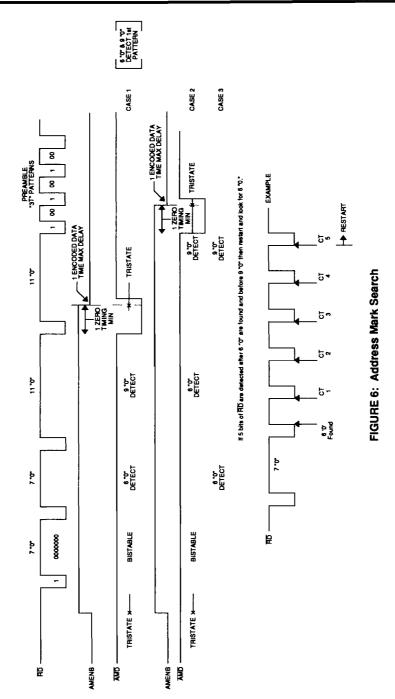

#### ADDRESS MARK DETECT

In Soft Sector Read Operation the SSI 32D5371/5372 must first detect an address mark to be able to initiate the rest of the read lock sequence. An address mark for the SSI 32D5371/5372 consists of two (2) 7 "0" patterns followed by two 11 "0" patterns. To begin the read lock sequence the Address Mark Enable (AMENB) is asserted high by the controller. The SSI32D5371/5372 Address Mark Detect (AMD) circuitry then initiates a search of the read data (RD) for an address mark. First the AMD looks for a set of 6 "0's" within the 7 "0" patterns. Having detected a 6 "0" the AMD then looks for a 9 "0" set within the 11 "0's". If AMD does not detect 9 "0's" within 5 RD bits after detecting 6 "0's" it will restart the Address Mark Detect sequence and look for 6 "0's." When the AMD has acquired a 6 "0," 9 "0" sequence the AMD transitions low. AMD will remain low for the duration of AMENB. When AMENB is released, AMD will be released by the SSI 32D5371/ 5372.

#### PREAMBLE SEARCH

After the Address Mark (AM) has been detected a Read Gate (RG) can be asserted initiating the remainder of the read lock sequence. When RG is asserted an internal counter counts transitions of the incoming Read Data, (positive transitions for RD ECL, negative transitions for  $\overline{\text{RD}}$  TTL. Once the counter reaches count 3 (finds (3) consecutive 3T preamble) the internal read gate enables switching the phase detector from the reference oscillator to the delayed Read Data input ( $\overline{\text{DRD}}$ ); at the same time a zero phase (internal) restart signal restarts the VCO in phase with the  $\overline{\text{DRD}}$ . This prepares the VCO to be synchronized to data when the bit sync circuitry is enabled after VCO lock is established.

#### **VCO LOCK & BIT SYNC ENABLE**

When the internal counter counts 16 more "3T" or a total of 19 read data transitions from RG enable, an internal VCO lock signal enables. The VCO lock signal activates the decoder bit synchronization circuitry to define the proper decode boundaries. Also, at count 19, the RRC source switches from the reference oscillator to the VCO clock signal which is phase locked to  $\overline{DRD}$ . The VCO is assumed locked at this point. A maximum of 2 RRC time periods may occur for the RRC transition, however, no short duration glitches will occur. After the bit sync circuitry sets the proper decode window (VCO in sync with RRC and RRC in sync with data) NRZ is enabled and data is toggled in to be decoded for the duration of the read gate.

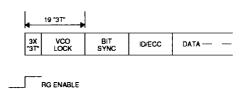

#### HARD SECTOR OPERATION

#### **READ MODE**

In hard sector operation a low AMENB disables the SSI 32D5371/5372's Address Mark Detection circuitry and  $\overline{\text{AMD}}$  remains inactive. A hard sector read operation does not require an address mark search but starts with a preamble search as with soft sector and sequences identically. In all respects, with exception to the address mark search sequence, hard sector read operation is the same as soft sector read.

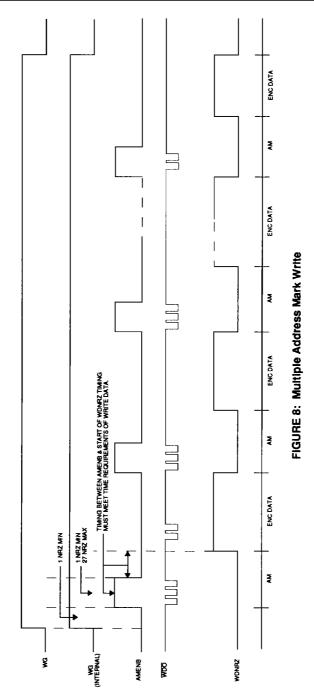

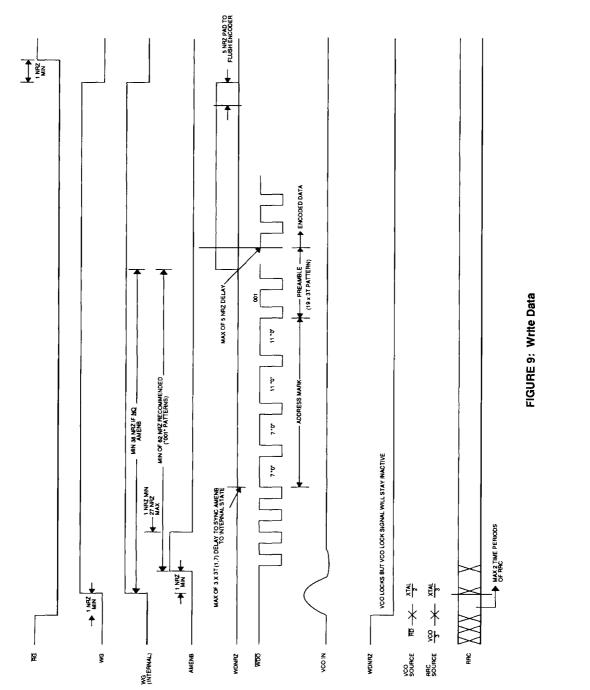

#### WRITE MODE

In the write mode the SSI 32D5371/5372 converts NRZ data from the controller into 1,7 RLL formatted data for storage on the disk. The SSI 32D5371/5372 can operate with a soft or hard sector hard drive.

In soft sector operation the device generates a "7, 7, 11, 11" Address Mark, and a preamble pattern.

In the hard sector operation the device generates a 19 x "3T" preamble pattern but no preceding Address Mark. Serial NRZ data is clocked into the SSI 32D5371/5372 and latched on defined cell boundaries. The NRZ

input data must be synchronous with the rising edges of the WCLK input. The WCLK input is a feature provided for operation in an ESDI application to compensate for large cable delays. In SCSI or ST506 operation, WCLK is connected directly to the RRC output.

Write precompensation circuitry is provided to compensate for media bit shift caused by intersymbol interference. The SSI 32D5371/5372 recognizes specific write data patterns and can add or subtract delays in the time position of write data bits to counteract the read back bit shift. The magnitude of the time shift, TPC, is determined by a combination of the RR value and of an external resistor on the PCS pin.

The SSI 32D5371/5372 performs write precompensation according to the algorithm outlined in Table 3.

#### SOFT SECTOR

In soft sector operation, when Read Gate (RG) transitions low, VCO source and RRC source switch from RD and VCO/3, respectively, to the reference crystal. At the same time the VCO (internal) lock goes inactive but

the VCO is locked to the reference crystal. After a delay of 1 NRZ time period (min) from RG low, the Write Gate (WG) can be enabled while WDNRZ is maintained (NRZ write data) low. The Address Mark Enable (AMENB) is made active (high) a minimum of 1 NRZ time period later. The Address Mark (consisting of 7 "0's," 7 "0's," 11 "0's, "11 "0's") and the 19 x "3T" Preamble is then written by  $\overline{\text{WDO}}$ . WDNRZ goes active at this point and after a delay of 5 NRZ time periods begins to toggle out  $\overline{\text{WDO}}$  encoded data. Finally, at the end of the write cycle, 5 NRZ of blank encoded time passes to insure the encoder is flushed of data; WG then goes low.

#### HARD SECTOR

In hard sector operation, when read gate (RG) transitions low, VCO source and RRC switch references and VCO lock (internal) goes inactive as with soft sector but the AMENB (address mark enable) is kept low.

The SSI 32D5371/5372 then sequences from RG disable to WG enable and WDNRZ active as in soft sector operation.

FIGURE 1: Data Synchronization Waveform

0790 - rev.

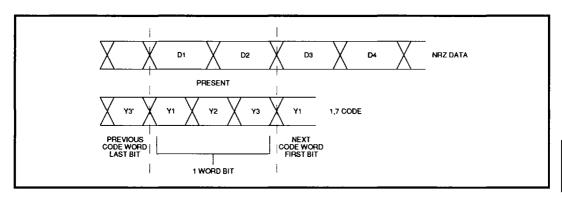

FIGURE 2: NRZ Data Word Comparision to 1, 7 Code Word Bit (See Table 1, for Decode Scheme)

TABLE 1: 1,7 RLL Code Set

| PREVIOUS<br>CODE WORD<br>LAST BITS |                | PRES  | DATA BITS<br>PRESENT NEXT |    | co | CODE BITS |    |            |

|------------------------------------|----------------|-------|---------------------------|----|----|-----------|----|------------|

| Х                                  | 0              | 1     | 0                         | 0  | Х  | 1         | 0  | 1          |

| X                                  | 0              | 1     | 0                         | 1  | Х  | 0_        | 1  | 0          |

| X                                  | 0              | 1     | 1                         | 0  | 0  | 0         | 1  | 0          |

| Х                                  | 0              | 1     | 1                         | *  | *  | 1         | 0  | 0          |

| 1                                  | 0              | 0     | 0                         | 0  | X  | 0         | 0  | 1          |

| 1                                  | _ 0            | 0     | 0_                        | 1  | X  | 0         | 0  | 0          |

| 0                                  | 0              | 0     | 1                         | 0  | Х  | 0         | 0  | 1          |

| 0                                  | 0              | 0     | 1_                        | 1  | Х  | 0         | 0  | 0          |

| Х                                  | 1              | 0     | 0                         | 0  | X  | 0         | 0  | 1          |

| ×                                  | 1              | 0     | 0                         | 1  | Х  | 0         | 1  | 0          |

| Х                                  | 1              | 0     | 1                         | 0  | 0  | 0         | 1  | 0          |

| Х                                  | 1              | 0     | 1                         | *  | *  | 0         | 0  | 0          |

| Y2'                                | Y3'            | D1    | D2                        | D3 | D4 | Y1        | Y2 | <b>Y</b> 3 |

| >                                  | X = Don't care |       |                           |    |    |           |    |            |

|                                    | = Not all      | zeros |                           |    |    |           |    |            |

**TABLE 2: Clock Frequency**

| WG | RG | VCO REF | RRC    | DECCLK | ENCCLK | MODE  |

|----|----|---------|--------|--------|--------|-------|

| 0  | 0  | XTAL/2  | XTAL/3 | XTAL/2 | XTAL/2 | IDLE  |

| 0  | 1  | RD      | VCO/3  | VCO/2  | XTAL/2 | READ  |

| 1  | 0  | XTAL/2  | XTAL/3 | XTAL/2 | XTAL/2 | WRITE |

| 1  | 1  | XTAL/2  | XTAL/3 | XTAL/2 | XTAL/2 | IDLE  |

Note 1: Until the VCO locks to the new source, the VCO/2 entries will be XTAL/2.

2: Until the VCO locks to the new source, the VCO/3 entries will be XTAL/3.

**TABLE 3: Write Precompensation Algorithm**

| BIT | віт | BIT | ВІТ | BIT | COMPENSATION |

|-----|-----|-----|-----|-----|--------------|

| n-2 | n-1 | n   | n+1 | n+2 | BIT n        |

| 1   | 0   | 1   | 0   | 11  | NONE         |

| 0   | 0   | 1   | 0   | 0   | NONE         |

| 1   | 0   | 1   | 0   | 0   | EARLY        |

| 0   | 0   | 1   | 0   | 1   | LATE         |

LATE: Bit n is time shifted (delayed) from its nominal time position towards the bit n+1 time position.

EARLY: Bit n is time shifted (advanced) from its nominal time position towards the bit n-1 time position.

**TABLE 4: Write Precompensation Magnitude**

| WCI | wco | MAGNITUDE (WP) |

|-----|-----|----------------|

| 0   | 0   | 3              |

| 0   | 1   | 2              |

| 1   | 0   | 1              |

| 1   | 1   | 00             |

The nominal magnitude,

TPC = WP x TPC0 is externally set with resistors on pins WCS and IREF.

4-116 0790 - rev.

#### **PIN DESCRIPTION**

#### **INPUT PINS**

| NAME                 | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RD (TTL)<br>RD (ECL) | ı    | READ DATA: Encoded Read Data from the disk drive read channel. The TTL input version (5372) is an active low signal. The ECL input version (5371) is an active high signal.                                                                                                                                                    |  |  |

| RG                   | ļ    | READ GATE: Selects the PLL reference input (REF), see Table 2. Achange in state on RG initiates the PLL synchronization sequence. Pin RG has an internal resistor pullup.                                                                                                                                                      |  |  |

| WG                   | l    | WRITE GATE: Enables the write mode, see Table 2. Pin WG has an internal resistor pullup.                                                                                                                                                                                                                                       |  |  |

| WCLK                 | ı    | WRITE CLOCK: Write Clock input. Must be synchronous with the NRZ Write Data input. For small cable delays, WCLK may be connected directly to pin RRC.                                                                                                                                                                          |  |  |

| EPD                  | I    | ENABLE PHASE DETECTOR: A low level (Coast Mode) disables the phase detector and enables the test mode. This opens the PLL and the VCO will run at the frequency commanded by the voltage on pin VCO IN. In the test mode, functions normally driven by the VCO are switched to XTAL. Pin EPD has an internal resistor pull up. |  |  |

| AMENB                | I    | ADDRESS MARK ENABLE: Used to enable the address mark detection and address mark generation circuitry, active high. Pin AMENB has an internal resistor pullup.                                                                                                                                                                  |  |  |

| WC0, WC1             | I    | WRITE PRECOMPENSATION CONTROL BITS: Pins WC1, and WC0 control the magnitude of the write precompensation, see Table 4. Internal resistor pull ups are provided. If unused, leave pins open or tie high.                                                                                                                        |  |  |

| WCL                  | I    | WRITE PRECOMPENSATION CONTROL LATCH: Used to latch the write precompensation control bits WC1 and WC0 into the internal DAC. An active low level latches the input bits. Pin WCL has an internal resistor pull up. If unused, leave pin open or tie high.                                                                      |  |  |

| WDNRZ                | l    | NRZ WRITE DATA INPUT PIN: This pin can be connected to the NRZ pin to form a bidirectional data port.                                                                                                                                                                                                                          |  |  |

#### **OUTPUT PINS**

| WD0 | 0 | WRITE DATA: Encoded write data output, active low. The data is automatically resynchronized (independent of the delay between RRC and WCLK) to one edge of the XTAL1 input clock.                                                                                               |

|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRC | 0 | READ/REFERENCE CLOCK: A multiplexed clock source used by the controller, see Table 2. During a mode change, no glitches are generated and no more than two lost clock pulses will occur. When RG goes high, RRC is synchronized to the NRZ Read Data after 19 read data pulses. |

| AMD | 0 | ADDRESS MARK DETECT: Tristate output pin that is in its high impedance state when WG is high or AMENB is low. A latched low level output indicates that an address mark has been detected. A low level on pin AMENB resets pin AMD.                                             |

#### **OUTPUT PINS** (Continued)

| NAME    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCO REF | 0    | VCO REFERENCE: An open emitter ECL output test point. The VCO reference input to the phase detector, the positive edges are phase locked to DLYD DATA. The negative edges of this open emitter output signal indicate the edges of the decode window. Two external resistors are required to perform this test, they should be removed during normal operation for reduced power dissipation.                                                                        |

| VCO CLK | 0    | VCO CLOCK: An open emitter ECL output test point. Two external resistors are required to perform this test. They should be removed during normal operation for reduced power dissipation.                                                                                                                                                                                                                                                                            |

| DRD     | 0    | DELAYED READ DATA: An open emitter ECL output test point. The positive edges of this open emitter output signal indicates the data bit position. The positive edges of the DRD and the VCO REF signals can be used to estimate window centering. The time jitter of DRD's positive edge is an indication of media bit shift. Two external resistors are required to perform this test. They should be removed during normal operation for reduced power dissipation. |

| NRZ     | 0    | NRZ READ DATA OUTPUT: Tristate output pin that is enabled when read gate is high. This pin can be connected to the WDNRZ pin to form a bidirectional data port.                                                                                                                                                                                                                                                                                                      |

#### **ANALOG PINS**

| IREF       | l | TIMING PROGRAM PIN: The VCO center frequency and the 1/3 cell delay are a function of the current sourced into pin IREF. The current is set by an external resistor, RR, connected between pin IREF and VPA2.                                                                                                                                                                                                                                                                                                                                                                           |

|------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1, 2   |   | CRYSTAL OSCILLATOR CONNECTIONS: The pin frequency is at three times the data rate. If the crystal oscillator is used, an AC coupled parallel LC circuit must be connected from XTAL1 to ground. If the crystal oscillator is not desired, XTAL1 may be driven either by a direct coupled TTL source or by an AC coupled ECL source, with XTAL2 open. The source duty cycle should be as close to 50% as possible, since its duty cycle will affect the RRC clock duty cycle when XTAL is its source. The additional RRC duty cycle error will be one third the source duty cycle error. |

| PD OUT     | 0 | PHASE DETECTOR OUTPUT: Drives the loop filter input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VCO IN     | 1 | VCO CONTROL INPUT: Driven by the loop filter output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| wcs        | ı | WRITE PRECOMPENSATION SET: Pin for a resistor to program the write precompensation magnitude value. The resistor, RC, is connected between pin PCS and VPA2. If this pin is left open, write precompensation is disabled.                                                                                                                                                                                                                                                                                                                                                               |

| DGND, AGND | ! | Digital and Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VPA1, VPA2 | ŧ | Analog +5V Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VPD        | 1 | Digital +5V Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

4-118 0790 - rev.

#### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

Operation above maximum ratings may damage the device.

| PARAMETER                          | RATING            | UNIT |

|------------------------------------|-------------------|------|

| Storage Temperature                | -65 to + 150      | °C   |

| Junction Operating Temperature, Tj | +150              | °C   |

| Supply Voltage, VPA1, VPA2, VPD    | -0.5 to 7         | V    |

| Voltage Applied to Logic Inputs    | -0.5 to VPD + 0.5 | ٧    |

| Maximum Power Dissipation          | 0.9               | W    |

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                               | RATING            | UNIT |

|-----------------------------------------|-------------------|------|

| Supply Voltage, VPA1 = VPA2 = VPD = VCC | 4.75 < VCC < 5.25 | ٧    |

| Junction Temperature, Tj                | 0 < Tj < 135      | °C   |

| Ambient Temperature, Ta                 | 0 < Ta < 70°      | °C   |

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, 4.75V< VCC <5.25V, 10 MHz< 1/TORC <24 MHz, 30 MHz< 1/TVCO <72 MHz, 0 °C<  $T_{\rm J}$  <135 °C.

| PARAM | METER                        | CONDITIONS                                    | MIN | МОМ | MAX   | UNIT |

|-------|------------------------------|-----------------------------------------------|-----|-----|-------|------|

| VIH   | High Level Input<br>Voltage  |                                               | 2.0 |     |       | V    |

| VIL   | Low Level Input<br>Voltage   |                                               |     |     | 0.8   | V    |

| Œ     | High Level Input<br>Current  | VIH = 2.7V                                    |     |     | 20    | μА   |

| IIL   | Low Level Input<br>Current   | VIL = 0.4V                                    |     |     | -0.36 | mA   |

| VOH   | High Level Output<br>Voltage | IOH = 400 μA                                  | 2.7 |     |       | ٧    |

| VOL   | Low Level Output<br>Voltage  | IOL = 4 mA                                    |     |     | 0.5   | ٧    |

| ICC   | Power Supply Current         | All outputs & test point pins open Tj = 135°C |     |     | 160   | mA   |

| PWR   | Power Dissipation            | All outputs & test point pins open Tj = 135°C |     |     | 0.84  | W    |

#### **ELECTRICAL CHARACTERISTICS** (Continued)

| PARAMETER |                                                    | CONDITIONS                                                              | MIN | MOM   | MAX | UNIT |

|-----------|----------------------------------------------------|-------------------------------------------------------------------------|-----|-------|-----|------|

| VOHT      | Test Point Output High Level DRD, VCO CLK, VCO REF | 262Ω to VPD<br>402Ω to DGND<br>VPD = 5.0V<br>VOHT - VPD                 |     | -0.85 |     | ٧    |

| VOLT      | Test Point Output Low Level DRD, VCO CLK, VCO REF  | 262 $\Omega$ to VPD<br>402 $\Omega$ to DGND<br>VPD = 5.0V<br>VOLT - VPD |     | -1.75 |     | V    |

#### DYNAMIC CHARACTERISTICS AND TIMING

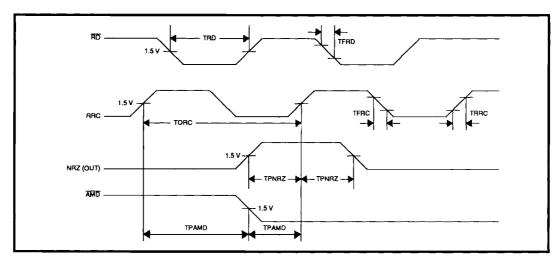

#### **READ MODE** (See Figure 3)

| PARAMETER |                               | CONDITIONS                           | MIN   | МОМ | MAX        | UNIT |  |

|-----------|-------------------------------|--------------------------------------|-------|-----|------------|------|--|

| TRD       | Read Data Pulse Width         |                                      | 12    |     | 4/3TORC-20 | ns   |  |

| TFRD      | Read Data Fall Time           | 2.0V to 0.8V, CL ≤ 15 pF             |       |     | 9          | ns   |  |

| TRRC      | Read Clock Rise Time          | 0.8V to 2.0V, C <sub>L</sub> ≤ 15 pF |       |     | 8          | ns   |  |

| TFRC      | Read Clock Fall Time          | 2.0V to 0.8V, C <sub>L</sub> ≤ 15 pF |       |     | 5          | ns   |  |

| RRC       | Duty Cycle                    | 20 Mbit/s                            | 43    | 50  | 57         | %    |  |

| TPNRZ     | NRZ (out) Set Up/Hold<br>Time | 20 Mbit/s                            | 15.5  |     |            | ns   |  |

| TPAMD     | AMD Propogation Delay         |                                      | 13    |     |            | ns   |  |

|           | 1/3 Cell Delay                | TD = 3.6E-12 (RR+1700)               | 0.8TD |     | 1.2TD      | ns   |  |

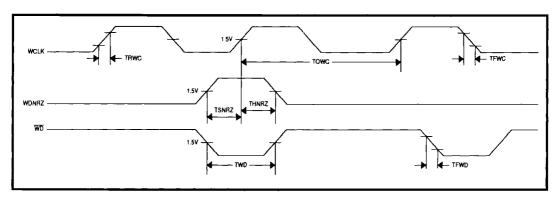

#### WRITE MODE (See Figure 4)

| PARAMETER |                               | CONDITIONS                           | MIN     | NOM | MAX                   | UNIT |

|-----------|-------------------------------|--------------------------------------|---------|-----|-----------------------|------|

| TWD       | Write Data Pulse Width        | C <sub>L</sub> ≤ 15 pF               | 2TOWC/3 |     | 2TOWC/3<br>+TPC<br>+5 | ns   |

| TFWD      | Write Data Fall Time          | 2.0V to 0.8V, C <sub>L</sub> ≤ 15 pF |         |     | 5                     | ns   |

| TRWC      | Write Data Clock<br>Rise Time | 0.8V to 2.0V                         |         |     | 10                    | ns   |

| TFWC      | Write Data Clock<br>Fall Time | 2.0V to 0.8V                         |         |     | 8                     | ns   |

| TSNRZ     | WDNRZ Set up Time             |                                      | 5       |     |                       | ns   |

| THNRZ     | WDNRZ Hold Time               |                                      | 5       |     |                       | ns   |

4-120 0790 - rev.

#### WRITE MODE (Continued)

| PARAMETER |                                                        | CONDITIONS                                                                                                                                                                                                                                                        | MIN | NOM   | MAX | UNIT |

|-----------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| TPC       | Precompensation<br>Time Shift<br>Magnitude<br>Accuracy | $TPCO = 1.12T \times A / (B + 3A)$ $T = XTAL Period$ $A = 0.19 / (Rc + 0.51) + 5.8E-3$ $B = 0.42 / (RR + 0.53) + 1.08E-2$ $RC = \frac{0.19(1 - 2.7S)}{S[\frac{0.38}{RR + 0.53}] + 0.025] - 0.006} -0.51$ $S = TPCO/T; RR, RC in kΩ$ (Rc tied between PCS and +5V) |     |       |     |      |

|           |                                                        | WC0 = 1 WC1 = 1                                                                                                                                                                                                                                                   | 0   | 0     |     | ns   |

|           |                                                        | WC0 = 0 WC1 = 1                                                                                                                                                                                                                                                   |     | TPCO  |     | ns   |

|           |                                                        | WC0 = 1 WC1 = 0                                                                                                                                                                                                                                                   |     | 2TPCO |     | ns   |

|           |                                                        | WC0 = 0 WC1 = 0                                                                                                                                                                                                                                                   |     | 3TPCO |     | ns   |

#### **DATA SYNCHRONIZATION**

| PARAM | METER                               | CONDITIONS                                                                                               | MIN             | MAX    | UNIT    |

|-------|-------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|--------|---------|

| TVCO  | VCO Center<br>Frequency Period      | VCO IN = 2.7V<br>TO = 3.6E-12 (RR + 1700)<br>VCC = 5.0V                                                  | 0.8TO           | 1.2TO  | ns      |

| VCO   | Frequency<br>Dynamic Range          | RR = (92.6/DR) −1.7(kΩ)<br>1V ≤ VCO IN ≤ VCC-0.6V<br>VCC = 5.0                                           | ±25             | ±45    | %       |

| KVCO  | VCO Control Gain                    | ωο = 2π/ΤΟ<br>1V ≤ VCO IN ≤ VCC 0.6V                                                                     | 0.14ωο          | 0.26ωο | rad/s-V |

| KD    | Phase Detector<br>Gain              | KD= 0.22/(RR+530) Read Mode<br>= 0.11/(RR+530) Non-Read Mode<br>VCC= 5V, PLL REF = RD 3T ('100') Pattern | 0.83KD          | 1.17KD | A/rad   |

|       | KVCO x KD Product<br>Accuracy*      |                                                                                                          | -28             | -28    | %       |

|       | VCO Phase<br>Restart Error*         | Referred to RRC                                                                                          | -1              | 1      | rad     |

|       | Decode Window<br>Centering Accuracy |                                                                                                          |                 | ±1.5   | ns      |

|       | Decode Window                       |                                                                                                          | (2TORC/3) - 1.5 |        | ns      |

<sup>\*</sup> Not Directly Testable; Design Characteristic

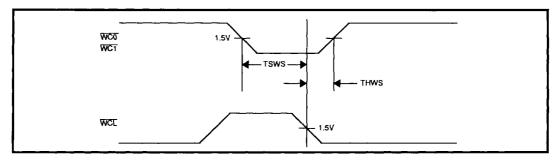

#### **CONTROL CHARACTERISTICS** (See Figure 5)

| PARAMETER |                         | CONDITIONS | MIN | NOM | MAX | UNIT |

|-----------|-------------------------|------------|-----|-----|-----|------|

| TSWS      | WCO, WCT<br>SET UP TIME |            | 7   |     |     | ns   |

| THWS      | WCO, WC1<br>HOLD TIME   |            | 7   |     |     | ns   |

FIGURE 3: Read Timing

FIGURE 4: Write Timing

FIGURE 5: Control Timing

4-122

079C - rev.

#### 7

### SSI 32D5371/5372 Data Synchronization/1, 7 RLL ENDEC with Write Precompensation

## SSI 32D5371/5372 Data Synchronization/1, 7 RLL ENDEC

#### Λ

# SSI 32D5371/5372 Data Synchronization/1, 7 RLL ENDEC with Write Precompensation

#### PACKAGE PIN DESIGNATIONS

(TOP VIEW)

CAUTION: Use handling procedures necessary for a static sensitive component.

28-Pin PLCC 0ja = 65 °C/W

Advance information: Indicates a product still in the design cycle, and any specifications are based on design goals only. Do not use for final design.

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680 (714) 731-7110, FAX (714) 731-5457