# HL-STD-883 COMPLIANT

# BiMOS II 10-BIT SERIAL-INPUT, LATCHED SOURCE DRIVER

Combining low-power CMOS logic with bipolar source drivers, Type UCS5810H will simplify many display-system designs. Primarily intended for use with vacuum-fluorescent displays, this BiMOS 10-bit serial-input, latched driver can also be used with LED and incandescent displays within its output limitations of 60 V and 40 mA per driver.

BiMOS II devices have considerably better data input rates than the original BiMOS circuits. With a 5 V supply, they typically operate above 5 MHz. With a 12 V supply, significantly higher speeds are obtained.

The CMOS 10-bit shift register and associated latches are designed for operation over a 5 V to 15 V supply-voltage range. They cause minimal loading of data lines and are compatible with standard CMOS, PMOS, and NMOS logic. When used with standard TTL or low-speed TTL logic, appropriate pull-up resistors may be required to ensure an input logic high. A CMOS serial-data output allows cascading these devices for interface applications requiring many drive lines (dot matrix, alphanumeric, bargraph).

The 10 bipolar outputs are used as segment or digit drivers in vacuum-fluorescent displays. Under normal operating conditions, these devices will sustain 25 mA per output at 85°C at a duty cycle of 83%. Other combinations of number of conducting outputs and duty cycle are shown in the specifications.

Type UCS5810H, when combined with the UCS5815H, an 8-bit latched source driver, comprises a minimum component display subsystem requiring few, if any, discrete components. The UCS5810H is furnished in an 18-pin hermetic dual in-line side-brazed package. Reverse-bias burn-in and 100% high-reliability screening to MIL-STD-883, Class B, are standard.

# ABSOLUTE MAXIMUM RATINGS at +25°C Free-Air Temperature

LATCHES

REGISTER

REGISTER

LATCHES

CLOCK 4

GROUND 5

STROBE 7

OUTal

LOGIC SUPPLY 6

16 SERIAL DATA OUT

14 SERIAL DATA IN

12 OUT,

11 OUT 2

Dwg. PP-029

13 BLANKING

15 LOAD SUPPLY

|                                               | -   |

|-----------------------------------------------|-----|

| Output Voltage, V <sub>OUT</sub> 6            | 0 V |

| Logic Supply Voltage Range,                   |     |

| V <sub>nn</sub> 4.5 V to 1                    | 5 V |

| Driver Supply Voltage Range,                  |     |

| V <sub>BB</sub> 5.0 V to 6                    | 0 V |

| Input Voltage Range,                          |     |

| V <sub>IN</sub> 0.3 V to V <sub>DD</sub> + 0. | 3 V |

| Continuous Output Current,                    |     |

| Ι <sub>ουτ</sub>                              | mΑ  |

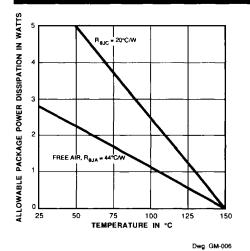

| Package Power Dissipation, Pp 1.67            |     |

| Operating Temperature Range,                  |     |

| T <sub>A</sub> 55°C to +125                   | 5°C |

| Storage Temperature Range,                    |     |

| T <sub>s</sub> 65°C to +150                   | )°C |

| *Derate at 13.3 mW/°C above +25°C             |     |

Caution: This CMOS device has input static protection but is susceptible to damage when exposed to extremely high static electrical charges.

### FEATURES

- 5 MHz Minimum Data Input Rate

- High-Voltage Source Outputs

- CMOS, PMOS, NMOS, TTL Compatible Inputs

- Low-Power CMOS Logic and Latches

- Internal Pull-Down Resistors

- Wide Supply-Voltage Range

- High-Reliability Screening to MIL-STD-883, Class B

- Operating Temperature -55°C to +125°C

Always order by complete number: UCS5810H883

# FUNCTIONAL BLOCK DIAGRAM CLOCK 4 SERIAL BLOCK DIAGRAM DATA OUT STROBE 7 BLANKING BLOCK DIAGRAM SERIAL BLOCK DIAGRAM DATA OUT STROBE 7 BLANKING BLOCK DIAGRAM DATA OUT BLO

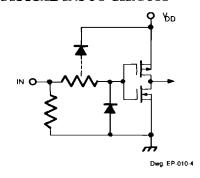

### TYPICAL INPUT CIRCUIT

| Number of<br>Outputs ON<br>(I <sub>OUT</sub> = -25 mA) | Maximum Allowable Duty Cycle<br>at V <sub>DD</sub> = 5 V and T <sub>A</sub> of 85°C |

|--------------------------------------------------------|-------------------------------------------------------------------------------------|

| . 10                                                   | 83%                                                                                 |

| 9                                                      | 93%                                                                                 |

| 8                                                      | 100%                                                                                |

| 7                                                      | 100%                                                                                |

| 6                                                      | 100%                                                                                |

| 5                                                      | 100%                                                                                |

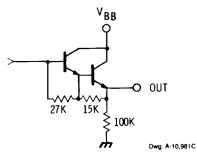

# TYPICAL OUTPUT DRIVER

# ELECTRICAL CHARACTERISTICS at $T_A$ = +25°C, $V_{BB}$ = 60 V, $V_{DD}$ = 5 V to 12 V (unless otherwise noted).

|                          |                    |                                                            |      | Limits |       |  |

|--------------------------|--------------------|------------------------------------------------------------|------|--------|-------|--|

| Characteristic           | Symbol             | Test Conditions                                            | Min. | Max.   | Units |  |

| Output OFF Voltage       | V <sub>OUT</sub>   |                                                            | _    | 1.0    | ٧     |  |

| Output ON Voltage        |                    | I <sub>OUT</sub> = -25 mA                                  | 57.5 |        | V     |  |

| Output Puil-Down Current | l <sub>out</sub>   | V <sub>OUT</sub> = V <sub>BB</sub>                         | 400  | 850    | μА    |  |

| Output Leakage Current   |                    |                                                            |      | -15    | μA    |  |

| Input Voltage            | V <sub>IN(1)</sub> | V <sub>DD</sub> = 5.0 V                                    | 3.5  | _      | v     |  |

|                          |                    | V <sub>DD</sub> = 12 V                                     | 10.5 |        | ٧     |  |

|                          | V <sub>IN(0)</sub> |                                                            | -0.3 | +0.8   | ٧     |  |

| Input Current            | I <sub>IN(1)</sub> | V <sub>DD</sub> = V <sub>IN</sub> = 5.0 V                  | _    | 100    | μА    |  |

|                          |                    | V <sub>DD</sub> = V <sub>IN</sub> = 12 V                   |      | 240    | μА    |  |

| Input Impedance          | Z <sub>IN</sub>    | V <sub>DD</sub> = 5.0 V                                    | 50   |        | kΩ    |  |

| Serial Data              | R <sub>OUT</sub>   | V <sub>DD</sub> = 5.0 V                                    |      | 20     | kΩ    |  |

| Output Resistance        |                    | V <sub>DD</sub> = 12 V *                                   |      | 6.0    | kΩ    |  |

| Supply Current           | I <sub>BB</sub>    | All outputs ON, Outputs open                               |      | 13     | mA    |  |

|                          |                    | All outputs OFF, Outputs open                              | _    | 200    | μА    |  |

|                          | l <sub>DD</sub>    | V <sub>DD</sub> = 5.0 V, All outputs OFF, All inputs = 0 V |      | 100    | μА    |  |

|                          |                    | V <sub>DD</sub> = 12 V, All outputs OFF, All inputs = 0 V  | _    | 200    | μА    |  |

|                          |                    | V <sub>DD</sub> = 5.0 V, One output ON, All inputs = 0 V   |      | 1.0    | mA    |  |

|                          |                    | V <sub>DD</sub> = 12 V, One output ON, All inputs = 0 V    |      | 3.0    | mA    |  |

NOTE: Positive (negative) current is defined as going into (coming out of) the specified device pin.

Operation of this device with standard TTL of DTL may require the use of appropriate pull-up resistors to ensure an input-logic high.

# 5810 10-bit serial-input, latched source driver

# ELECTRICAL CHARACTERISTICS at $T_A$ = -55°C, $V_{BB}$ = 60 V, $V_{DD}$ = 5 V to 12 V (unless otherwise noted).

|                          |                    |                                                          |      | Limits |       |

|--------------------------|--------------------|----------------------------------------------------------|------|--------|-------|

| Characteristic           | Symbol             | Test Conditions                                          | Min. | Max.   | Units |

| Output OFF Voltage       | V <sub>out</sub>   |                                                          | _    | 1.0    | ٧     |

| Output ON Voltage        | 1                  | I <sub>OUT</sub> = -25 mA                                | 57   | _      | ٧     |

| Output Pull-Down Current | l <sub>out</sub>   | V <sub>OUT</sub> = V <sub>BB</sub>                       | 300  | 850    | μА    |

| Output Leakage Current   | 1                  |                                                          |      | -15    | μА    |

| Input Voltage            | V <sub>IN(1)</sub> | V <sub>DD</sub> = 5.0 V                                  | 3.6  |        | V     |

|                          |                    | V <sub>DD</sub> = 12 V                                   | 11.0 |        | ٧     |

|                          | V <sub>IN(0)</sub> |                                                          | -0.3 | +0.8   | ٧     |

| Input Current            | [ <sub>IN(1)</sub> | $V_{DD} = V_{IN} = 5.0 \text{ V}$                        | _    | 145    | μА    |

|                          |                    | V <sub>DD</sub> = V <sub>IN</sub> = 12 V                 | _    | 430    | μА    |

| Input Impedance          | Z <sub>IN</sub>    | V <sub>DO</sub> = 5.0 V                                  | 35   |        | kΩ    |

| Serial Data              | R <sub>out</sub>   | V <sub>DD</sub> = 5.0 V                                  |      | 20     | kΩ    |

| Output Resistance        |                    | V <sub>DD</sub> = 12 V                                   | _    | 6.0    | kΩ    |

| Supply Current           | l <sub>BB</sub>    | All outputs ON, Outputs open                             |      | 13     | mA    |

|                          |                    | All outputs OFF, Outputs open                            | _    | 100    | μА    |

|                          | l <sub>op</sub>    | V <sub>DD</sub> = 5.0 V, Outputs OFF, All Inputs = 0 V   | _    | 100    | μА    |

|                          | ]                  | V <sub>DD</sub> = 12 V, Outputs OFF, All inputs = 0 V    | _    | 200    | μА    |

|                          |                    | V <sub>DD</sub> = 5.0 V, One output ON, All inputs = 0 V | _    | 1.0    | mA    |

|                          |                    | V <sub>DD</sub> = 12 V, One output ON, All inputs = 0 V  |      | 3.0    | mA    |

NOTE: Positive (negative) current is defined as going into (coming out of) the specified device pin.

Operation of this device with standard TTL of DTL may require the use of appropriate pull-up resistors to ensure an input-logic high.

# ELECTRICAL CHARACTERISTICS at $T_A$ = +125°C, $V_{BB}$ = 60 V, $V_{DD}$ = 5 V to 12 V (unless otherwise noted).

|                          |                    |                                                            |      | Limits |       |

|--------------------------|--------------------|------------------------------------------------------------|------|--------|-------|

| Characteristic           | Symbol             | Test Conditions                                            | Min. | Max.   | Units |

| Output OFF Voltage       | V <sub>out</sub>   |                                                            | _    | 1.0    | V     |

| Output ON Voltage        |                    | I <sub>OUT</sub> = -25 mA                                  | 57   | _      | ٧     |

| Output Pull-Down Current | l <sub>out</sub>   | V <sub>OUT</sub> = V <sub>ØB</sub>                         | 400  | 1400   | μА    |

| Output Leakage Current   |                    |                                                            |      | -30    | μА    |

| Input Voltage            | V <sub>IN(1)</sub> | V <sub>DD</sub> = 5.0 V                                    | 3.5  |        | V     |

|                          |                    | V <sub>DD</sub> = 12 V                                     | 10.5 | _      | ٧     |

|                          | V <sub>IN(0)</sub> |                                                            | -0.3 | +0.8   | ٧     |

| Input Current            | I <sub>IN(1)</sub> | $V_{DD} = V_{IN} = 5.0 \text{ V}$                          |      | 100    | μА    |

|                          |                    | V <sub>DD</sub> = V <sub>IN</sub> = 12 V                   | _    | 300    | μА    |

| Input Impedance          | Z <sub>IN</sub>    | $V_{DD} = 5.0 \text{ V}$                                   | 50   | _      | kΩ    |

| Serial Data              | R <sub>out</sub>   | V <sub>DD</sub> = 5.0 V                                    |      | 27     | kΩ    |

| Output Resistance        |                    | V <sub>DD</sub> = 12 V                                     | _    | 8.0    | kΩ    |

| Supply Current           | I <sub>BB</sub>    | All outputs ON, Outputs open                               | _    | 15     | mA    |

|                          |                    | All outputs OFF, Outputs open                              | _    | 100    | μА    |

|                          | l <sub>op</sub>    | V <sub>DD</sub> = 5.0 V, All outputs OFF, All inputs = 0 V | _    | 100    | μА    |

|                          |                    | V <sub>DD</sub> = 12 V, All outputs OFF, All inputs = 0 V  | _    | 200    | μА    |

|                          |                    | V <sub>DD</sub> = 5.0 V, One output ON, All inputs = 0 V   | _    | 1.0    | mA    |

|                          |                    | V <sub>DD</sub> = 12 V, One output ON, All inputs = 0 V    |      | 3.0    | mA    |

NOTE: Positive (negative) current is defined as going into (coming out of) the specified device pin.

Operation of this device with standard TTL of DTL may require the use of appropriate pull-up resistors to ensure an input-logic high.

Dwg. No. A 12,649

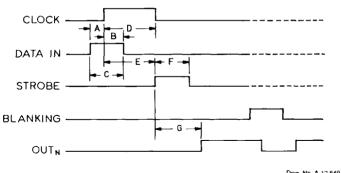

### TIMING CONDITIONS

# $(V_{DD} = 5 \text{ V}, T_{A} = +25^{\circ}\text{C}, \text{ Logic Levels are } V_{DD} \text{ and Ground})$

A. Minimum Data Active Time Before Clock Pulse B. Minimum Data Active Time After Clock Pulse E. Minimum Time Between Clock Activation and Strobe ............... 300 ns G. Typical Time Between Strobe Activation and

Serial Data present at the input is transferred to the shift register on the logic "0" to logic "1" transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.

Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the BLANKING input be high during serial data entry.

When the BLANKING input is high, all of the output buffers are disabled (OFF) without affecting the information stored in the latches or shift register. With the BLANKING input low, the outputs are controlled by the state of the latches.

## TRUTH TABLE

| Serial        | Clock | S  | hift           | Regi           | ister | Cont             | ents             | Serial           |                 |    | Lat            | ch (  | Conte | ents             |                |          |    | Oı             | ıtpu           | t Co | nten             | ts             |

|---------------|-------|----|----------------|----------------|-------|------------------|------------------|------------------|-----------------|----|----------------|-------|-------|------------------|----------------|----------|----|----------------|----------------|------|------------------|----------------|

| Data<br>Input |       | l, | l <sub>2</sub> | l <sub>3</sub> |       | I <sub>N-1</sub> | I <sub>N</sub>   | Data<br>Output   | Strobe<br>Input | l, | l <sub>2</sub> | 13    |       | I <sub>N-1</sub> | I <sub>N</sub> | Blanking | 1, | l <sub>2</sub> | <br> <br> 3    |      | I <sub>N-1</sub> | I <sub>N</sub> |

| Н             | ۲     | Н  | R,             | R <sub>2</sub> |       | R <sub>N-2</sub> | R <sub>N</sub> , | R <sub>N-1</sub> |                 |    |                |       |       |                  |                |          |    |                |                |      |                  |                |

| L             | ۲     | L  | R,             | R <sub>2</sub> |       | R <sub>N-2</sub> | $R_{N-1}$        | R <sub>N-1</sub> | I               |    |                |       |       |                  |                |          |    |                |                |      |                  |                |

| Х             | ı.    | R, | R <sub>2</sub> | R <sub>3</sub> |       | R <sub>N-1</sub> | R <sub>N</sub>   | R <sub>N</sub>   |                 |    |                |       |       |                  |                |          |    |                |                |      |                  |                |

|               |       | Χ  | Х              | Х              |       | Х                | Х                | ×                | L               | R, | R <sub>2</sub> | $R_3$ | •••   | R <sub>N-1</sub> | R <sub>N</sub> |          |    |                |                |      |                  |                |

|               |       | Pı | P <sub>2</sub> | P <sub>3</sub> |       | P <sub>N-1</sub> | P <sub>N</sub>   | P <sub>N</sub>   | Н               | ٦  | P <sub>2</sub> | $P_3$ |       | P <sub>N-1</sub> | P <sub>N</sub> | L        | ΡŤ | P <sub>2</sub> | P <sub>3</sub> |      | P <sub>N-1</sub> | P <sub>N</sub> |

|               |       |    |                |                |       |                  |                  |                  |                 | Х  | Х              | Х     |       | Х                | Х              | н        | L  | L              | L              |      | L                | L              |

L = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous State