# Si7210 I<sup>2</sup>C Hall Effect Magnetic Position and Temperature Sensor Data Sheet

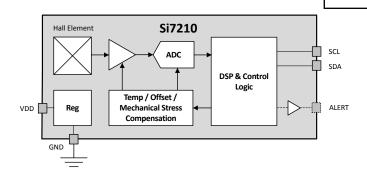

The Si7210 family of Hall effect magnetic sensors from Silicon Labs combines a chopper-stabilized Hall element with a low-noise analog amplifier, 13-bit analog-to-digital converter, and an I<sup>2</sup>C interface. Leveraging Silicon Labs' proven CMOS design techniques, the Si7210 family incorporates digital signal processing to provide precise compensation for temperature and offset drift.

Compared with existing Hall effect sensors, the Si7210 family offers industry-leading sensitivity, which enables use with larger air gaps and smaller magnets. The integrated 13-bit high-precision ADC delivers high output linearity with very low noise for the highest measurement accuracy. For battery-powered applications, the Si7210 family offers very low power consumption to improve operating life.

The Si7210 family supports a bidirectional  $I^2C$  interface which provides full configurability of the Hall effect sensor operate and release points. At any time, the 13-bit magnetic field strength can be read through the  $I^2C$  interface.

# **Applications**

- Mechanical position sensing in consumer, industrial applications

- · Replacement of reed switches

- · Fluid level measurement

- · Speed sensing

- · Utility meters

- · Control knobs and selector switches

# FEATURES

- · High-Sensitivity Hall Effect Sensor

- Adjustable Full Scale (Standard Offerings are ±20mT and ±200 mT Full Scale)

- Integrated Digital Signal Processing for Temperature and Offset Drift Compensation

- · High-Precision 13-bit Signal Path

- · Output Bandwidth up to 20 kHz

- Sensitivity Drift < ±5% over 0-70 °C

- Digital I<sup>2</sup>C Interface

- Four Selectable I2C Addresses

- · Optional Digital Alert Output

- Wide 1.7 to 5.5 V Power Supply Voltage

- Temperature Sensor Data also available by I<sup>2</sup>C (accuracy ±1°C)

- Low 50 nA Sleep Mode Current Consumption

- Industry-Standard Packaging

- Surface-Mount SOT23-5

- 1.4 x 1.6 mm 8-pin DFN package

# **Table of Contents**

| 1. | Electrical Specifications       | . 3                                    |

|----|---------------------------------|----------------------------------------|

| 2. | Functional Description          | . 8                                    |

| 3. | $I^2C$ Interface                | . 9                                    |

| 4. | Register Definitions            | 11                                     |

|    | 4.1.1 Chip ID                   | .11<br>.12<br>.13<br>.14<br>.15<br>.15 |

| 5. | Making Temperature Measurements | 18                                     |

| 6. | Pin Descriptions                | .19                                    |

| 7. | Ordering Information            | . 21                                   |

| 8. | Package Outline                 | .24                                    |

| 9. | Land Patterns                   | .28                                    |

|    | . <b>Top Marking</b>            | .30<br>.31                             |

| 11 | Revision History                | 32                                     |

# 1. Electrical Specifications

Unless otherwise specified, all min/max specifications apply over the recommended operating conditions.

**Table 1.1. Recommended Operating Conditions**

| Parameter    | Temp<br>Grade | Symbol         | Test Condition | Min  | Тур | Max  | Unit |

|--------------|---------------|----------------|----------------|------|-----|------|------|

| Power Supply |               | $V_{DD}$       |                | 1.71 |     | 5.5  | V    |

| Temperature  | I             | T <sub>A</sub> |                | -40  |     | +125 | °C   |

**Table 1.2. General Specifications**

| Parameter           | Symbol            | Test Condition                                                          | Min                   | Тур   | Max                   | Unit |

|---------------------|-------------------|-------------------------------------------------------------------------|-----------------------|-------|-----------------------|------|

| Input Voltage High  | V <sub>IH</sub>   | SCL, SDA pins                                                           | 0.7 x V <sub>DD</sub> | -     | -                     | V    |

| Input Voltage Low   | V <sub>IL</sub>   | SCL, SDA pins                                                           | -                     | -     | 0.3 x V <sub>DD</sub> | V    |

| Input Voltage Range | V <sub>IN</sub>   | SCL, SDA with respect to ground                                         | 0                     |       | V <sub>DD</sub>       | V    |

| Input Leakage       | I <sub>IL</sub>   | SDA, SCL                                                                |                       | < 0.1 | 1                     | μA   |

| Output Voltage Low  | V <sub>OL</sub>   | SCL, SDA I <sub>OL</sub> = 3 mA                                         |                       |       | 0.4                   | V    |

|                     |                   | V <sub>DD</sub> > 2 V                                                   |                       |       |                       |      |

|                     |                   | SCL, SDA I <sub>OL</sub> = 2 mA                                         |                       |       | 0.2                   | V    |

|                     |                   | V <sub>DD</sub> > 1.71 V                                                |                       |       |                       |      |

|                     |                   | SCL, SDA I <sub>OL</sub> = 6 mA                                         |                       |       | 0.6                   | V    |

|                     |                   | V <sub>DD</sub> > 2 V                                                   |                       |       |                       |      |

| Current Consumption | I <sub>DD</sub>   | Sleep timer enabled average at $V_{DD}$ = 3.3 V and 200 msec sleep time |                       | 0.4   |                       | μА   |

|                     |                   | Sleep mode                                                              |                       | 50    |                       |      |

|                     |                   | V <sub>DD</sub> = 3.3 V, T = 25 °C                                      |                       | 00    |                       |      |

|                     |                   | Sleep mode                                                              |                       |       | 1000                  | n ^  |

|                     |                   | V <sub>DD</sub> = 3.3 V, T = 70 °C                                      |                       |       |                       | nA   |

|                     |                   | Sleep mode                                                              |                       |       | 5000                  |      |

|                     |                   | V <sub>DD</sub> = 5.5 V, T = 125 °C                                     |                       |       |                       |      |

|                     |                   | Conversion in progress:                                                 |                       |       |                       | mA   |

|                     |                   | 1.8 V                                                                   |                       | 3.5   | 4.5                   |      |

|                     |                   | 3.3 V                                                                   |                       | 5.0   | 6                     |      |

|                     |                   | 5.0 V                                                                   |                       | 6.8   | 8.5                   |      |

|                     |                   | Idle mode                                                               |                       | 360   | 1000                  | μA   |

| Conversion Time     | T <sub>CONV</sub> | Conversion time for first measurement in a burst                        |                       | 11    |                       | μs   |

|                     |                   | Additional conversions in a burst                                       |                       | 8.8   |                       | μs   |

| Parameter              | Symbol             | Test Condition                                         | Min  | Тур  | Max         | Unit |

|------------------------|--------------------|--------------------------------------------------------|------|------|-------------|------|

| Sleep Time             | T <sub>SLEEP</sub> | Factory configurable from 1 to 200 msec ±20%           |      | -    |             |      |

| Idle Time <sup>1</sup> | T <sub>IDLE</sub>  | slTime = 0x01<br>slFast = 1                            | 11.9 | 13.2 | 14.5<br>227 | μѕ   |

|                        |                    | slTime = 0xFF<br>slFast = 0                            | 185  | 206  | 227         | msec |

| Wake Up Time           | T <sub>WAKE</sub>  | Time from V <sub>DD</sub> > 1.7 V to first measurement |      |      | 1           | msec |

**Table 1.3. Output Pin Specifications**

| Parameter                     | Symbol            | Test Condition          | Min                   | Тур | Max | Unit                 |

|-------------------------------|-------------------|-------------------------|-----------------------|-----|-----|----------------------|

| Output Voltage Low            | V <sub>OL</sub>   | I <sub>OL</sub> = 3 mA  |                       |     | 0.4 | V                    |

| Output Pin Open Drain or Push |                   | V <sub>DD</sub> > 2 V   |                       |     |     |                      |

| Pull                          |                   | I <sub>OL</sub> = 2 mA  |                       |     | 0.2 | V                    |

|                               |                   | V <sub>DD</sub> > 1.7 V |                       |     |     |                      |

|                               |                   | I <sub>OL</sub> = 6 mA  |                       |     | 0.6 | V                    |

|                               |                   | V <sub>DD</sub> > 2 V   |                       |     |     |                      |

| Leakage                       | I <sub>OH</sub>   |                         |                       |     | 1   | μΑ                   |

| Output high                   |                   |                         |                       |     |     |                      |

| Output Pin Open Drain         |                   |                         |                       |     |     |                      |

| Output Voltage High           | V <sub>OH</sub>   | I <sub>OH</sub> = 2 mA  | V <sub>DD</sub> – 0.4 |     |     | V                    |

| Output Pin Push Pull          |                   | V <sub>DD</sub> >2.25 V |                       |     |     |                      |

| Slew Rate                     | T <sub>SLEW</sub> |                         |                       | 5   |     | %V <sub>DD</sub> /ns |

| Digital Output Mode           |                   |                         |                       |     |     |                      |

<sup>1.</sup> Part can go to either idle more or sleep mode between conversions. If part is in idle mode with slTime = 0x00 and slFast = 1 conversion are continuous at 8.8 µsec interval.

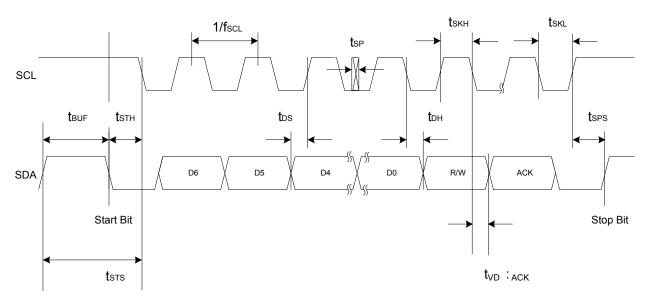

Table 1.4. I<sup>2</sup>C Interface Specification

| Parameter                                                  | Symbol                           | Test Condition                       | Min | Тур | Max | Unit             |

|------------------------------------------------------------|----------------------------------|--------------------------------------|-----|-----|-----|------------------|

| SCL Clock Frequency                                        | f <sub>SCL</sub>                 |                                      | 0   |     | 400 | kHz              |

| Start Condition Hold Time                                  | t <sub>SDH</sub>                 |                                      | 0.6 |     |     | μs               |

| LOW Period of SCL                                          | t <sub>SKL</sub>                 |                                      | 1.3 |     |     | μs               |

| HIGH Period of Clock                                       | tsкн                             |                                      | 0.6 |     |     | μs               |

| Set Up Time for a Repeated Start                           | t <sub>SU</sub> ; <sub>STA</sub> |                                      | 0.6 |     |     | μs               |

| Data Hold Time                                             | t <sub>DH</sub>                  |                                      | 0   |     |     |                  |

| Data Set Up Time                                           | t <sub>DS</sub>                  |                                      | 100 |     |     | ns               |

| Set Up Time for a STOP Condition                           | t <sub>SPS</sub>                 |                                      | 0.6 |     |     | μs               |

| Bus Free Time between STOP and START                       | t <sub>BUF</sub>                 |                                      | 1.3 |     |     | μs               |

| Data Valid Time (SCL Low to Data Valid)                    | t <sub>VD;DAT</sub>              |                                      |     |     | 0.9 | μs               |

| Data Valid Acknowledge Time (time from SCL Low to SDA Low) | t <sub>VD;ACK</sub>              |                                      |     |     | 0.9 | μs               |

| Hysteresis                                                 |                                  | Digital input hysteresis SDA and SCL | 7   |     | 17  | %V <sub>DD</sub> |

| Suppressed Pulse Width <sup>1</sup>                        | t <sub>SP</sub>                  |                                      | 50  |     |     | ns               |

1. Pulses up to and including 50 nsec will be suppressed.

Figure 1.1. I<sup>2</sup>C Interface Timing

Table 1.5. Magnetic Sensor

| Parameter                    | Symbol           | Test Condition                                | Min | Тур  | Max                                    | Unit   |

|------------------------------|------------------|-----------------------------------------------|-----|------|----------------------------------------|--------|

| Offset (Digital Output Mode) | B <sub>OFF</sub> | 20 mT scale SOT23 package                     |     | ±250 | 250 +450,<br>-350<br>350 ±1500<br>±250 | μΤ     |

|                              |                  | Full temperature and V <sub>DD</sub> range    |     |      | -330                                   |        |

|                              |                  | 20 mT scale DFN8 package                      |     | ±350 | ±1500                                  | μΤ     |

|                              |                  | Full temperature and V <sub>DD</sub> range    |     |      |                                        |        |

|                              |                  | 0 - 70°C and 1.71 V to 3.6 V<br>SOT23 package |     |      | ±250                                   | μΤ     |

| Gain Accuracy                |                  | 0 - 70°C                                      |     |      | 5                                      | %      |

|                              |                  | Full temperature range                        |     |      | 10                                     | %      |

| RMS Noise <sup>1</sup>       |                  | Temp = 25 °C, 20 mT range, $V_{DD}$ = 5 V     |     | 30   |                                        | μT rms |

**Table 1.6. Temperature Compensation**

| Parameter                       | Symbol | Test Condition         | Min | Тур       | Max | Unit |

|---------------------------------|--------|------------------------|-----|-----------|-----|------|

| Gain Variation with Temperature |        | Flat Tempco.           |     | < +/-0.05 |     | %/°C |

|                                 |        | 0 - 70°C               |     |           |     |      |

|                                 |        | Neodymium compensation |     | -0.12     |     | %/°C |

|                                 |        | Ceramic compensation   |     | -0.2      |     | %/°C |

Table 1.7. Average Temperature Measurement Error

| Parameter                                   | Symbol | Test Conditon | Min | Тур | Max  | Unit |

|---------------------------------------------|--------|---------------|-----|-----|------|------|

| Average Temperature Measure-                |        | SOT23-5       |     | ±1  | ±1.5 | °C   |

| ment Error After Gain and Offset Correction |        | -10 to +85°C  |     |     |      |      |

|                                             |        | DFN8          |     | ±4  |      | °C   |

|                                             |        | -10 to +85°C  |     |     |      |      |

<sup>1.</sup> For a single conversion. This may be reduced by filtering.

# **Table 1.8. Thermal Characteristics**

| Parameter                            | Symbol          | Test Condition                         | Value | Unit |

|--------------------------------------|-----------------|----------------------------------------|-------|------|

| Junction to Air Thermal Resistance   | $\theta_{JA}$   | JEDEC 4 layer board no airflow SOT23-5 | 212.8 | °C/W |

| Junction to Board Thermal Resistance | $\theta_{JB}$   | JEDEC 4 layer board no airflow SOT23-5 | 45    | °C/W |

| Junction to Air Thermal Resistance   | $\theta_{JA}$   | JEDEC 4 layer board no airflow DFN8    | 107.6 | °C/W |

| Junction to Board Thermal Resistance | $\theta_{JB}$   | JEDEC 4 layer board no airflow DFN8    | 42.6  | °C/W |

| Junction to Case Thermal Resistance  | θ <sub>JC</sub> | JEDEC 4 layer board no airflow DFN8    | 53.6  | °C/W |

# Table 1.9. Absolute Maximum Ratings

| Parameter                             | Symbol | Test Condition | Min  | Тур | Max                  | Unit |

|---------------------------------------|--------|----------------|------|-----|----------------------|------|

| Ambient Temperature Under Bias        |        |                | -55  |     | 125                  | °C   |

| Storage Temperature                   |        |                | -65  |     | 150                  | °C   |

| Voltage on I/O Pins                   |        |                | -0.3 |     | V <sub>DD</sub> +0.3 | V    |

| Voltage on VDD with Respect to Ground |        |                | -0.3 |     | 6                    | V    |

| ESD Tolerance                         |        | НВМ            |      |     | 2                    | kV   |

|                                       |        | CDM            |      |     | 500                  | V    |

# Note:

<sup>1.</sup> Absolute maximum ratings are stress ratings only, operation at or beyond these conditions is not implied and may shorten the life of the device or alter its performance.

# 2. Functional Description

The Si7210 family of parts are I<sup>2</sup>C programmable Hall effect magnetic position sensors. These parts digitize the component of the magnetic field in the z axis of the device (positive field is defined as pointing into the device from the bottom). The parts are normally used to detect the presence or absence of a magnet in security systems, as position sensors or for counting revolutions.

In addition to being able to control the conversion process and read the result of magnetic field conversions by  $I^2C$ , the 5-pin packages offer an output pin. The output pin can act as an alert (push pull or open collector) which goes high or low when the magnetic field crosses a threshold. Alternatively the output pin can be configured as an analog output. The output pin configuration is determined by the type of part ordered (this is not  $I^2C$  configurable).

The parts are preconfigured for the magnetic field measurement range, sleep time, temperature compensation, tamper threshold, and digital filtering, and will wake into the preconfigured mode when first powered. The specific configuration, as well as the I<sup>2</sup>C address and output type (open collector or push pull), are determined by the part number. Magnetic field trip points are typically configured by I<sup>2</sup>C, and the part is allowed to go into its normal sleep and measurement cycle. If the bit Usestore is set to 1, the output pin trip points are retained in sleep mode. Data other than magnetic field trip points is not retained in sleep mode. If there is not a need to go to full sleep mode, the other parameters may be configured, and this data will be kept in idle mode.

Following is a list of I<sup>2</sup>C interface configurable options:

- Measurement range. This is normally set so that after temperature compensation the full scale (15b unsigned) digital output is ±20.47 mT (0.00125 mT/bit) or ±204.7 mT (0.0125 mT/bit). (Note: 1 Gauss = 0.1 mT). For convenience these are referred to as the 20 mT and 200 mT scales.

- *Digital filtering*. To reduce noise in the output (normally 0.03 mT RMS on the 20 mT scale), digital filtering can be applied. The digital filtering can be done to a burst of measurements (FIR filter) or can be configured to average measurements in IIR style. The filtering can be done over a number of samples in powers of 2 (1,2,4,8,...) for up to 2<sup>12</sup> (4096) samples.

- Time between measurements (or measurement bursts for the case of FIR filtering)

- For lowest power, the part can be configured to sleep between measurements. However, remember some configuration data is lost in sleep mode.

- · For faster measurement rates, the part is configured to idle between samples.

- The part can also be configured to take a single measurement on command.

- The digital output pin (for parts that support this option)

- · Threshold at which the digital output will change for increasing field (Bop) and for decreasing field (Brp).

- · The direction in which the output pin goes in response to an increase in field

- There is an option to take the magnitude of the field prior to the comparison so that the polarity is not field dependent

- · The settings will be retained in sleep mode.

- A "tamper threshold". This is intended to signal the presence of a strong magnet, which may indicate tampering. In the case of tamper detection, the output pin will go to its zero field value (which in security systems is normally an indication of door or window open).

- Temperature compensation of the magnetic field response to compensate for the nominal drop in magnetic field output of common magnets with increasing temperature.

- An on chip coil that generates a large enough field to allow self-test of the sensor

- · The coil can be turned on in either polarity

For greater precision in programming the part, a number of calibration data points are stored in memory (OTP).

- The nominal magnetic field output of the on-chip coil normalized to the power supply voltage

- · Coefficients to be used for setting gain and temperature compensation

# 3. I<sup>2</sup>C Interface

The Si7210 complies with "fast" mode I<sup>2</sup>C operation and 7 bit addressing at speeds up to 400 kHz. The I<sup>2</sup>C address is factory programmed to one of 4 values 0x30, 0x31, 0x32, or 0x33 (0110000b through 0110011b).

At power-up the registers are initialized, as will be described in the register definitions, and then they can be read or written in standard fashion for I<sup>2</sup>C devices. A special sequence must be used to read OTP data, as will be described.

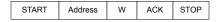

The host command for writing an I<sup>2</sup>C register is:

| START | Address | W | ACK | register | ACK | data | ACK | STOP |

|-------|---------|---|-----|----------|-----|------|-----|------|

|-------|---------|---|-----|----------|-----|------|-----|------|

The host command for reading an I<sup>2</sup>C register is:

|  | START | Address | W | ACK | Register | ACK | Sr | Address | R | Data | NACK* | STOP |  |

|--|-------|---------|---|-----|----------|-----|----|---------|---|------|-------|------|--|

|--|-------|---------|---|-----|----------|-----|----|---------|---|------|-------|------|--|

\*NACK by host

Where:

START is SDA going low with SCL high

Sr is a repeated START

Address is 0x30 up to 0x33

0 indicates a write and 1 indicates a read

ACK is SDA low

Data is the Read or Write data

NACK is SDA high

STOP is SDA going high with SCL high

Writing or Reading of sequential registers can be supported by setting the arautoinc bit of register 0xC5 (see register description). In the case of a read sequence where the arautoinc bit has been set, the data can be ACK'd to allow reading of sequential registers. For example, a two byte read of the conversion data in registers 0xC1 and 0XC2 would be:

| START | Address | W | ACK | 0xC1 | ACK | Sr | Address | ACK | data | ACK* | data | NACK* | STOP |

|-------|---------|---|-----|------|-----|----|---------|-----|------|------|------|-------|------|

|       |         |   | _   |      | _   | _  |         | _   |      | _    |      | _     |      |

<sup>\*</sup> ACK or NACK by host

To wake a part from sleep mode or to interrupt a measurement loop from idle mode, send the sequence:

In this case, if the host continued with a register, the Si7210 would NACK which would be unexpected.

or use:

| START | Address | R | ACK | data | NACK* | STOP |

|-------|---------|---|-----|------|-------|------|

|       |         |   |     | l    |       |      |

\*NACK by host

In this case the Si7210 will produce 0xFF for the data.

Allow 10  $\mu$ sec between the ACK of the address and the next START for the Si7210 to wake from sleep. In most cases this will happen automatically due to the 400 kHz maximum speed of the I<sup>2</sup>C bus.

The sequence will put the part in idle mode with the stop bit set.

Note: It is recommended that the part be put in stop mode prior to changing data that will affect a measurement outcome.

To make a single conversion having woken the part, set the <code>oneburst</code> bit of register 0xC4 to 1 and the <code>stop</code> bit to 0. The <code>stop</code> bit resets to 1 by the time the measurement is complete.

To put the part back to sleep after reading the data, set stop bit to 0. The bit sltimeena is normally factory set to 1, so it does not need to be set. The bit sleep is not set.

To put the part to sleep with no measurements (sleep timer disabled), write the sleep bit to 1 and the stop bit to 0.

If it is desired to re-enable the sleep timer having put the part to sleep with sleeptimer disabled, then wait 500 µsec after setting the sltimeena bit before putting the part to sleep.

# 4. Register Definitions

The Si7210 has 21 registers in locations 0xC0 – 0xE4.

Configuration data is loaded at start up from OTP data and can be modified by I<sup>2</sup>C writes.

**Note:** This data will be reloaded when the part wakes from sleep mode (other than 0xC6 and 0xC7 which are not reloaded if bit Usestore is set).

| ADDR | 7            | 6                      | 5      | 4    | 3            | 2        | 1               | 0            |  |

|------|--------------|------------------------|--------|------|--------------|----------|-----------------|--------------|--|

| 0xC0 |              | chipid (               | RO)    |      |              | re       | evid (RO)       |              |  |

| 0xC1 |              |                        |        | Ds   | spsigm       |          |                 |              |  |

| 0xC2 |              |                        |        | D    | spsigl       |          |                 |              |  |

| 0xC3 |              |                        |        |      |              |          | dspsigse        | el           |  |

| 0xC4 | meas(RO)     |                        |        |      | Usestore     | oneburst | stop            | sleep        |  |

| 0xC5 |              |                        |        |      |              |          |                 | arautoinc    |  |

| 0xC6 | sw_low4field |                        |        |      | sw_op        |          |                 |              |  |

| 0xC7 | sw_field     | sw_fieldpolsel sw_hyst |        |      |              |          |                 |              |  |

| 0xC8 |              | slTime                 |        |      |              |          |                 |              |  |

| 0xC9 |              |                        | sw_tar | nper |              |          | slFast          | slTimeena    |  |

| 0xCA |              |                        |        |      | a0           |          |                 |              |  |

| 0xCB |              |                        |        |      | a1           |          |                 |              |  |

| 0xCC |              |                        |        |      | a2           |          |                 |              |  |

| 0xCD |              | df_burstsize           |        |      | df_bw df_iir |          |                 |              |  |

| 0xCE |              |                        |        |      | a3           |          |                 |              |  |

| 0xCF |              |                        |        |      | a4           |          |                 |              |  |

| 0xD0 |              |                        |        |      | a5           |          |                 |              |  |

| 0xE1 |              | otp_addr               |        |      |              |          |                 |              |  |

| 0xE2 |              | otp_data               |        |      |              |          |                 |              |  |

| 0xE3 |              |                        |        |      |              |          | otp_read_e<br>n | otp_busy(RO) |  |

| 0xE4 |              | tm_fg                  |        |      |              |          |                 | tm_fg        |  |

As can be seen many of the bit fields are not aligned with register boundaries. When writing a particular bit field, it is best to use a read, modify, write procedure to ensure that other bit fields are not unintentionally changed. That is, read the register, modify the bit field of interest while keeping other bits the same, and then write the register back. Unspecified bits should not be changed from the factory configuration.

# 4.1 Field Descriptions

# 4.1.1 Chip ID

chipid (RO) - This ID 0x1 for all Si7210 parts.

revid (RO) — This ID 0x4 for revision B.

### 4.1.2 Fields Associated with Reading DATA

Dspsigm - Bits [6:0] are the most significant byte of the last conversion result. The most significant bit is a "fresh" bit indicating the register has been updated since last read. Reading the Dspsigm register causes the register Dspsig1 to be loaded with the least significant byte of the last conversion result.

Dspsig1 – The least significant byte of the last conversion result. Read Dspsigm first to align the bytes. The complete 15b unsigned result is 256\*Dspsigm[6:0]+Dspsig1[7:0]. A result of 16384 means zero field. More negative results mean negative field, and more positive results mean more positive field. With the normal recommended gain settings, the magnetic field data is scaled to 1 LSB = 0.00125 mT (±20.47 mT full scale) or 1 LSB = 0.0125 mT (±204.7 mT full scale)

Magnetic field is calculated from the formula:

B = (256\*Dspsigm[6:0]+Dspsigl[7:0] -16384)\* (0.00125 or 0.0125)

**Note**: The data for a0 - a5 in registers 0xC9 through 0xD0 is appropriate for the default averaging which is typically 1 sample (df\_burst-size=0). The data in registers 0x21 - 0x44 is appropriate when averaging is turned on (df\_burstsize>0). If using the coefficients in 0x21 - 0x44 (for example, to change the measurement scale) and there is no averaging, then subtract 0.1mT from the calculated B field..

Setting dspsigsel to 0x01 will give the output of an internal temperature sensor. See also 5. Making Temperature Measurements.

meas (RO) — indicates a measurement is in process. In most cases this bit is not needed as the fresh bit of Dspsigm can be used instead.

oneburst – Setting this bit initiates a single conversion. Set stop = 0 when setting oneburst = 1. The oneburst bit will auto clear once the conversion initiates and the stop bit will be set to 1 when the conversion completes.

stop - Setting this bit causes the control state machine measurement loop to pause after the current measurement burst completes. Once set, clearing this bit restarts the measurement loop.

sleep - Setting this bit causes the part to enter sleep mode after the current measurement burst completes. Once set, clearing this bit restarts the measurement loop.

arautoinc - enables auto increment of the I<sup>2</sup>C register address pointer. This bit is not retained in sleep mode

# 4.1.3 Fields Associated with Configuring the Output Pin

Usestore – Setting this bit causes the current state of OTP registers for the sw\_op, sw\_hyst, sw\_low4field, and sw\_fieldpolsel bits to be saved and restored during the next sleep and wakeup sequence instead of using data read from the OTP.

**Note:** Allowing a part to enter sleep mode will result in reloading other parameters, such as the filtering data. This bit will also be retained in sleep mode.

sw\_low4field - selects logic sense; output is low when the field is strong when the bit is set. Output is high when the field is strong when the bit is cleared.

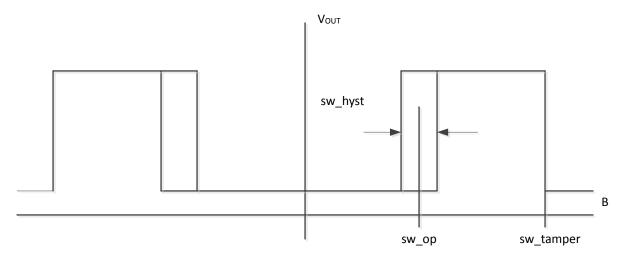

sw\_op - this 7 bit number sets the center point of the decision point for magnetic field high or low. The actual decision point is the center point plus or minus the hysteresis.

The 15b data that can be read from  $I^2C$  is truncated to 13b prior to the logic that makes the decision. The middle of the decision point relative to full scale (13b signed or +/-4096 counts) is:

threshold =

$$(16 + sw op[3:0]) \times 2^{sw_op[6:4]}$$

threshold = 0, when sw\_op = 127

These numbers run from 16 to 3840. On the 20 mT scale each LSB of the 15b number is 0.00125 mT. In 13b representation the LSB is 0.005 mT/bit so the middle of the decision point can be programmed from 0.08 mT to 19.2 mT (16\*0.005 to 3840\*0.005).

Similarly, on the 200 mT scale, the middle point of the decision threshold can be programmed from 0.8 mT to 192 mT.

The special case of sw\_op = 127 is for "latches". A Hall effect latch is like a Hall effect switch except the decision points are generally symmetrical around zero. A Hall effect latch is useful for detecting wide range of motion such as a garage door where there are magnets of opposite polarities at the extremes of travel.

sw\_fieldpolsel

- · 00b: absolute value of the field is taken before comparing to threshold (omnipolar)

- 01b: field is multiplied by -1 before being compared to (positive) threshold (unipolar operating in negative field region)

- 10b: field is multiplied by 1 before being compared to (positive) threshold (unipolar operating in positive field region). Also compatible

with Latch operation.

- 11b: unused

sw\_hyst - the formula for switch hysteresis is:

$$hysteresis = (8 + sw hyst[2:0]) \times 2^{sw_hyst[5:3]}$$

If sw op = 127, (latch mode) the hysteresis is multiplied by 2

When sw hyst = 63, the hysteresis is set to zero.

These numbers can range from 8 to 1792 or 16 to 3584 when the sensor is in "latch" mode with sw op = 127.

On the 20 mT scale this corresponds to ±0.04 mT to ±8.96 mT hysteresis when the part is in switch mode and ±0.08 mT to ±17.92 mT in latch mode. On the 200 mT scale, these numbers are multiplied by 10.

Note that

$$Bop = (threshold + hysteresis) \times \frac{0.05mT}{bit}$$

, or =  $(threshold + hysteresis) \times \frac{0.5mT}{bit}$

And

$$Brp = (threshold - hysteresis) \times \frac{0.05mT}{bit}$$

, or  $= (threshold - hysteresis) \times \frac{0.5mT}{bit}$

So that

Bop - Brp =

$$2 \times hysteresis \times \frac{0.05mT}{bit}$$

, or =  $2 \times hysteresis \times \frac{0.5mT}{bit}$

sw\_tamper – For the Si7210 if there is a strong magnetic field and the tamper threshold is exceeded, the output pin will go to the same value it would have been at if the measured field was zero. For a security application, if someone tried to "fool" the sensor by putting a strong magnet near it, the output indication would be the same as "door open" or low magnetic field indicting possible tampering.

The formula for the tamper threshold is:

$$tamper = (16 + sw_tamper[3:0]) \times 2^{sw_tamper[5:4]+5}$$

The tamper feature is disabled if sw\_tamper = 63

This formula can give numbers ranging from 512 to 7936 (which is greater than the full scale of the part. Generally any setting of switch tamper(5:4) = 3 (11b) effectively disables the tamper feature as well. With switch tamper = 101111b the tamper threshold is 3968 which is 96.895 % of full scale. On the 20 mT scale a setting of 000000b (threshold = 512) gives a tamper threshold of 2.65 mT and a setting of 101111b (threshold = 3968) gives a tamper threshold of 19.84 mT. On the 200 mT scale these numbers are multiplied by 10.

# Example:

Figure 4.1. Omnipolar Switch with Tamper

# 4.1.4 Registers Associated with Control of Idle Time

slTime - Controls duration of sleep or IDLE interval.

**Note:** For the case of sleep between measurements (slTimeena = 1), the sleep time is not user configurable and it is recommended that this register should not be changed. The register will be reloaded every time a measurement is made when the part wakes from sleep.

The idle counter duration is

$$t_{idle} = (32 + s|Time[4:0]) \times \frac{2^{8-6\times s|Fast+s|Time[7:5]}}{10MHz}$$

For the idle counter, slFast =1 and slTime = 0 overrides to mean actual zero idle time. The AFE runs continuously and a new sample is taken every 8.8 µsec.

Idle times are variable from 13.2 µsec to 206 msec nominally. Idle times are ±10%.

s1Fast - When set, causes a reduction in programmed sleep and idle times as in the above equations.

slTimeena – Enables the sleep timer. 0 means the part goes into complete sleep once the sleep bit is set. 1 means the parts will wake a factory set interval between 1 and 200 msec, make a measurement, set the output pin value and return to sleep.

The sleep time is not user configurable. This is determined by the part number ordered and is factory adjustable in the range of 1 to 20 msec ±20%.

# 4.1.5 Registers Associated with Setting the Output Scale

a0,a1,a2,a3,a4,a5 - These parameters are associated with the trimming of the part and setting the analog measurement range. 6 sets of these parameters are stored in OTP for the 2 standard ranges of ±20 mT and ±200 mT and the 3 standard temperature compensations as in Table 1.6 Temperature Compensation on page 6.

Parts are shipped pre-configured for a given output scale. To change the output scale, copy these 5 numbers from OTP to I<sup>2</sup>C memory. (See also section on OTP memory.)

### 4.1.6 Registers Associated with Adding Digital Filtering

df\_burstsize - Rather than taking a single sample, each time the part wakes up, the Si7210 can be configured to take a burst of measurements. The time required to take one measurement is 11 µsec. Each additional measurement takes 8.8 µsec.

The maximum setting of  $df_bw$  is 12. The number of samples to average is  $2^{df_bw}$ . This can be 1,2,4,8,...up to 4096. In FIR mode the number of samples per burst is controlled by df bw

In FIR mode the average is the sum of the samples divided by the number of samples.

$$output(T) = \frac{\sum\limits_{t=T+1-2}^{T} sample(t)}{2^{df\_bw}}$$

df\_iir = 0 means the averaging is done FIR style, 1 means the averaging is done IIR style

In IIR mode, the averaging is done using:

$$output(T) = \frac{\left(2^{df\_bw} - 1\right)}{2^{df\_bw}} \times output(T - 1) + \frac{1}{2^{df\_bw}} \times sample(T)$$

In IIR mode, the number of measurements in a burst is 2<sup>d</sup>f\_burstsize, so this is 1,2,4,8,... up to 128 samples. Normally, in IIR mode df burstsize is set to 0, but it is possible to use burst averaging on each sample and IIR averaging of the bursts.

# 4.1.7 Registers to Read OTP Data

The following are used for reading the OTP data:

otp addr - is the address of the data to read

otp\_data - is the data once read

otp\_read\_en - must be set to 1 to initiate a read; this bit is auto cleared

$otp_busy - indicates$  the OTP is busy. For normal I<sup>2</sup>C reads, the data will be available by the time the read enable bit is set and the data is read, so in most cases this bit is not needed.

The table below is the map for OTP memory. Registers 0x04 - 0x0F correspond to the  $I^2C$  registers and are loaded at power up or wake from sleep. If the bit Usestore is set, then the first two registers are not reloaded on a wake from sleep.

| ОТР ВҮТЕ    | 7                 | 6                                                                                    | 5                | 4               | 3                 | 2             | 1             | 0  |  |

|-------------|-------------------|--------------------------------------------------------------------------------------|------------------|-----------------|-------------------|---------------|---------------|----|--|

| 0x04        | sw_low4field      |                                                                                      |                  |                 | sw_op             |               |               |    |  |

| 0x05        | sw_fiel           | dpolsel                                                                              |                  |                 | sw_h              | ıyst          |               |    |  |

| 0x06        |                   | slTime                                                                               |                  |                 |                   |               |               |    |  |

| 0x08        |                   | sw_tamper slFast slTimeena                                                           |                  |                 |                   |               |               |    |  |

| 0x09        |                   |                                                                                      |                  | power           | up a0             |               |               |    |  |

| 0x0A        |                   |                                                                                      |                  | power           | up a1             |               |               |    |  |

| 0x0B        |                   |                                                                                      |                  | power           | up a2             |               |               |    |  |

| 0x0C        | df_burstsize df_b |                                                                                      |                  |                 | )W                |               | df_iir        |    |  |

| 0x0D        |                   |                                                                                      |                  | power           | up a3             |               |               |    |  |

| 0x0E        |                   | power up a4                                                                          |                  |                 |                   |               |               |    |  |

| 0x0F        |                   | power up a5                                                                          |                  |                 |                   |               |               |    |  |

| 0x14        |                   | Base part number dropping the "Si72", for example 01 for Si7201                      |                  |                 |                   |               |               |    |  |

| 0x15        |                   | Variant according to data sheet represented in hex., for example, variant 50 is 0x32 |                  |                 |                   |               |               |    |  |

| 0x16 - 0x17 |                   |                                                                                      |                  | Rese            | erved             |               |               |    |  |

| 0x18 – 0x1B |                   |                                                                                      |                  | 4 byte ser      | ial number        |               |               |    |  |

| 0x1C        |                   |                                                                                      |                  | Rese            | erved             |               |               |    |  |

| 0x1D        |                   |                                                                                      | Ten              | nperature senso | or offset adjustm | ent           |               |    |  |

| 0x1E        |                   |                                                                                      | Ter              | mperature sens  | or gain adjustme  | ent           |               |    |  |

| 0x20        |                   |                                                                                      |                  | Rese            | erved             |               |               |    |  |

| 0x21 - 0x26 |                   | a0                                                                                   | – a5 for 20 mT   | scale and no m  | nagnet temperat   | ure compensa  | tion          |    |  |

| 0x27 - 0x2C |                   | a0                                                                                   | - a5 for 200 mT  | scale and no n  | nagnet temperat   | ure compensa  | ition         |    |  |

| 0x2D - 0x32 | а                 | 0 – a5 for 20 m                                                                      | nT scale at 25°0 | C -0.12%/°C ma  | ignet temperatu   | re compensati | on (Neodymiun | n) |  |

| 0x33 - 0x38 | a                 | 0 – a5 for 200 r                                                                     | mT scale at 25°  | C -0.12%/°C m   | agnet temperatu   | re compensat  | ion (Neodymiu | m) |  |

| 0x39 - 0x3E |                   | a0 – a5 for 20 mT scale at 25°C -0.2%/°C magnet temperature compensation (Ceramic)   |                  |                 |                   |               |               |    |  |

| 0x3F - 0x44 |                   | a0 – a5 for 200 mT scale at 25°C -0.2%/°C magnet temperature compensation (Ceramic)  |                  |                 |                   |               |               |    |  |

# 4.1.8 Control of On-Chip Test Coil

${\tt tm\_fg} \textbf{ - Test Field Generator Coil}$

| tm_fg         | Current in coil    |  |  |

|---------------|--------------------|--|--|

| 00b (State 0) | None               |  |  |

| 01b (State 1) | Positive direction |  |  |

| 10b (State 2) | Negative direction |  |  |

| 11b (State 3) | None               |  |  |

Avoid transitions between states 1 & 2, due to a possible short term high current spike.

The nominal magnetic field output of the on chip generator varies with coil current. The coil current varies with coil resistance and power supply voltage, so the nominal magnetic field output varies according to

$Bout = BperVnom \times V_{DD}$

BperVnom is 1.16 mT/V

This can be used to calculate the expected magnetic field from the test coil for a given  $V_{DD}$ . This is somewhat temperature dependent so the actual measured field will vary according to the accuracy of the part as well as temperature. Generally, as the coil is turned on and off the measured variation in field should be within  $\pm 25\%$  of expectation based on the calculated field generation.

# 5. Making Temperature Measurements

Every magnetic field conversion has an associated temperature measurement. During magnetic field measurement cycles, this data is used for compensating the hall sensor data to keep the desired temperature coefficient of magnetic field measurement.

The temperature data is available by setting the dspsigsel field of register 0xC3 to 0x01.

Once the dspsigsel field is set, the temperature sensor data is read from registers 0xC1 and 0xC2 as 15b unsigned number (see also 4.1.2 Fields Associated with Reading DATA).

The temperature sensor data can be read after one conversion or after a burst of conversions.

Note: The temperature sensor data is not averaged after performing a burst. Only the magnetic field data is averaged.

The data in 0xc1 and 0xc2 is combined into a 12 bit signed number:

$$value = 32 \times Dspigm[6:0] + (Dspisigl[7:0] > > 3)$$

Temperature\_raw =

$$-3.83 \times 10^{-6} \times value^2 + 0.16094 \times value - 279.80$$

The data read in this way does not have offset and gain correction applied. The offset and gain correction is stored in registers 0x1D and 0x1E which are read as signed integers.

$$Offset = \frac{signed\_value(0x1D)}{16}$$

$$Gain = 1 + \frac{signed\_value(0x1E)}{2048}$$

And finally

Temperature =  $gain \times (Temperature\_raw) + offset - (0.222 \times VDD)$

If VDD is not known, then use VDD = 3.3 V.

Typically, the gain and offset terms are calculated only once and then are saved. The temperature measurement circuit has noise and quantization errors of approximately ±0.3 °C. Adding averaging to the calculated temperature will reduce these errors.

# 6. Pin Descriptions

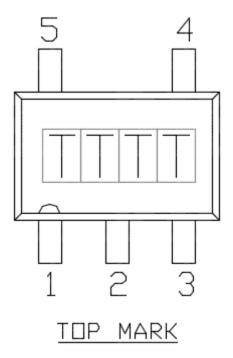

# 6.1 SOT-23 Pin Description

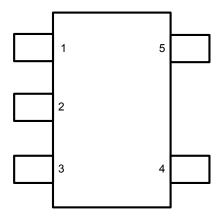

SOT-23, 5-Pin Top View

Figure 6.1. Pin Assignments

Table 6.1. 5-Pin SOT23-5 Package

| Pin Name        | Pin Number | Description            |

|-----------------|------------|------------------------|

| SDA             | 1          | I <sup>2</sup> C data  |

| GND             | 2          | Ground                 |

| SCL             | 3          | I <sup>2</sup> C clock |

| V <sub>DD</sub> | 4          | Power +1.7 to +5.5 V   |

| ALERT           | 5          | Digital ouput          |

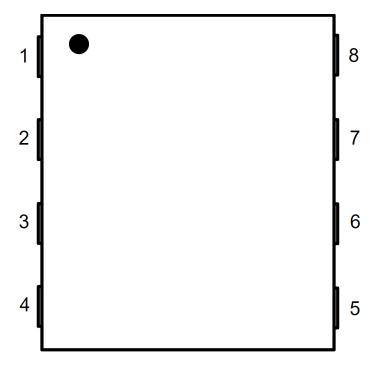

# 6.2 DFN Pin Description

Figure 6.2. 8-Pin DFN, Top View

Table 6.2. Pin Descriptions

| Pin | Name | Туре          | Description |

|-----|------|---------------|-------------|

| 1   | GND  | Ground        | Ground      |

| 2   | SCL  | -             | I2C Clock   |

| 3   | NC   | -             | No connect  |

| 4   | SDA  | -             | I2C Data    |

| 5   | GND  | Ground        | Ground      |

| 6   | Out  | Bidirectional | Output      |

| 7   | NC   | -             | No connect  |

| 8   | Vdd  | Power         | Vdd         |

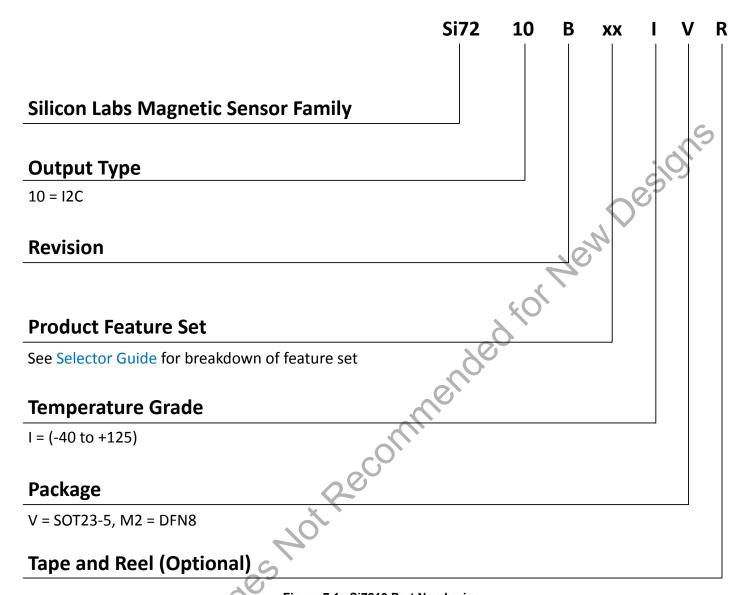

# 7. Ordering Information

Figure 7.1. Si7210 Part Numbering

**Table 7.1. Product Selection Guide**

| Part No.              | Default Brp and<br>Bop                                    | Default Output<br>Polarity (High<br>Field) | Default Scale | I2C Address | Package | Other               |

|-----------------------|-----------------------------------------------------------|--------------------------------------------|---------------|-------------|---------|---------------------|

|                       | - 5.5 V, I <sub>DD</sub> = 0.4 μΑ<br>g = None, Sleep/Idle |                                            |               |             |         |                     |

| Si7210-B-00-<br>IV(R) | Bop = ±1.1 mT<br>(max)                                    | High (push-pull)                           | 20 mT         | 0x30        | SOT23-5 | Tamper @19.84<br>mT |

|                       | Brp = ±0.2 mT<br>(min)                                    |                                            |               |             |         |                     |

|                       | Bop - Brp  = 0.4<br>mT (typ)                              |                                            |               |             |         |                     |

| Part No.               | Default Brp and<br>Bop       | Default Output<br>Polarity (High<br>Field) | Default Scale | I2C Address | Package | Other               |

|------------------------|------------------------------|--------------------------------------------|---------------|-------------|---------|---------------------|

| Si7210-B-01-<br>IV(R)  | Bop = ±1.1 mT<br>(max)       | Low (open drain)                           | 20 mT         | 0x30        | SOT23-5 | Tamper @19.84<br>mT |

|                        | Brp = ±0.2 mT<br>(min)       |                                            |               |             |         |                     |

|                        | Bop - Brp  = 0.4<br>mT (typ) |                                            |               |             |         | S                   |

| Si7210-B-02-<br>IV(R)  | Bop = ±1.1 mT<br>(max)       | Low (push-pull)                            | 20 mT         | 0x31        | SOT23-5 | Tamper @19.84<br>mT |

|                        | Brp = ±0.2 mT<br>(min)       |                                            |               |             | 0       | 2                   |

|                        | Bop - Brp  = 0.4<br>mT (typ) |                                            |               |             | NO.     |                     |

| Si7210-B-03-<br>IV(R)  | Bop = ±1.1 mT<br>(max)       | Low (push-pull)                            | 20 mT         | 0x32        | SOT23-5 |                     |

|                        | Brp = ±0.2 mT<br>(min)       |                                            |               | 100         | `       |                     |

|                        | Bop - Brp  = 0.4<br>mT (typ  |                                            |               | 2960        |         |                     |

| Si7210-B-04-<br>IV(R)  | Bop = ±1.1 mT<br>(max)       | Low (push-pull)                            | 20 mT         | 0x33        | SOT23-5 |                     |

|                        | Brp = ±0.2 mT<br>(min)       |                                            | Olli          |             |         |                     |

|                        | Bop - Brp  = 0.4<br>mT (typ) |                                            | 200           |             |         |                     |

| Si7210-B-05-<br>IV(R)  | Bop = ±2.15 mT (max)         | Low (push-pull)                            | 200 mT        | 0x33        | SOT23-5 |                     |

|                        | Brp = ±0.35 mT<br>(min)      | SMO                                        |               |             |         |                     |

|                        | Bop - Brp  = 0.8<br>mT (typ) | 000                                        |               |             |         |                     |

| Si7210-B-10-<br>IM2(R) | Bop = ±7 mT (max)            | High (push-pull)                           | 20 mT         | 0x30        | DFN8    | Tamper @19.84<br>mT |

|                        | Brp = ±4 mT<br>(min)         |                                            |               |             |         |                     |

|                        | Bop - Brp  = 1<br>mT (typ)   |                                            |               |             |         |                     |

| Si7210-B-11-<br>IM2(R) | Bop = ±7 mT<br>(max)         | Low (open-drain)                           | 20 mT         | 0x30        | DFN8    | Tamper @19.84<br>mT |

| 9                      | Brp = ±4 mT<br>(min)         |                                            |               |             |         |                     |

|                        | Bop - Brp  = 1<br>mT (typ)   |                                            |               |             |         |                     |

| Part No.               | Default Brp and<br>Bop                                                      | Default Output<br>Polarity (High<br>Field) | Default Scale | I2C Address | Package | Other |

|------------------------|-----------------------------------------------------------------------------|--------------------------------------------|---------------|-------------|---------|-------|

| Si7210-B-12-<br>IM2(R) | Bop = ±7 mT<br>(max)<br>Brp = ±4 mT<br>(min)<br> Bop - Brp  = 1<br>mT (typ) | Low (push-pull)                            | 20 mT         | 0x31        | DFN8    | S     |

| Si7210-B-13-<br>IM2(R) | Bop = ±7 mT<br>(max)<br>Brp = ±4 mT<br>(min)<br> Bop - Brp  = 1<br>mT (typ) | Low (push-pull)                            | 20 mT         | 0x32        | DFN8    | Sign  |

| Si7210-B-14-<br>IM2(R) | Bop = ±7 mT<br>(max)<br>Brp = ±4 mT<br>(min)<br> Bop - Brp  = 1<br>mT (typ) | Low (push-pull)                            | 20 mT         | 0x33        | DFN8    |       |

| Si7210-B-15-<br>IM2(R) | Bop = ±7 mT<br>(max)<br>Brp = ±4 mT<br>(min)<br> Bop - Brp  = 1<br>mT (typ) | Low (push-pull)                            | 200 mT        | 0x33        | DFN8    |       |

# **Additional Information**

For information on the below specifications for each OPN, refer to the Magnetic Sensors Selector Guide:

- Default B Release Point (Brp)

- · Default B Operate Point (Bop)

- · Tamper threshold

- · Temperature sensor accuracy

Factory configuration options include:

- · The I2C address

- · The output pin can be open drain or push pull

In sleep mode, the operate and release point setting are saved if the bit Usestore is set. Other parameters for sleep timer operation are factory configured:

- · The tamper indication point

- The sample rate

- Samples per measurement burst (FIR mode only)

- · Measurement scale and temperature compensation

**Note:** North pole of a magnet at the bottom of an SOT23-5 package and top of a DFN 8 package (coming soon) is defined as positive field.

# 8. Package Outline

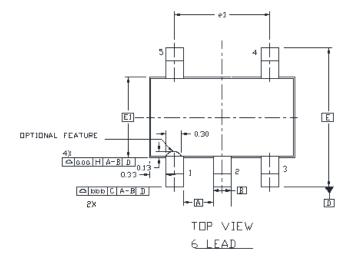

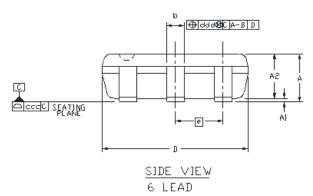

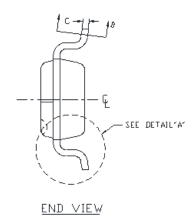

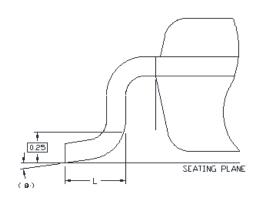

# 8.1 SOT23-5 5-Pin Package

DETAIL "A"

Table 8.1. SOT23-5 5-Pin Package Dimensions

| Dimension | Min      | Max  |  |  |  |  |

|-----------|----------|------|--|--|--|--|

| А         |          | 1.25 |  |  |  |  |

| A1        | 0.00     | 0.10 |  |  |  |  |

| A2        | 0.85     | 1.15 |  |  |  |  |

| b         | 0.30     | 0.50 |  |  |  |  |

| С         | 0.10     | 0.20 |  |  |  |  |

| D         | 2.90 BSC |      |  |  |  |  |

| E         | 2.75 BSC |      |  |  |  |  |

| E1        | 1.60 BSC |      |  |  |  |  |

| е         | 0.95 BSC |      |  |  |  |  |

| e1        | 1.90     | BSC  |  |  |  |  |

| L         | 0.30     | 0.60 |  |  |  |  |

| L2        | 0.25     | BSC  |  |  |  |  |

| θ         | 0°       | 8°   |  |  |  |  |

| aaa       | 0.       | 15   |  |  |  |  |

| bbb       | 0.20     |      |  |  |  |  |

| ссс       | 0.10     |      |  |  |  |  |

| ddd       | 0.       | 20   |  |  |  |  |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Solid State Outline MO-193, Variation AB.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020D specification for Small Body Components.

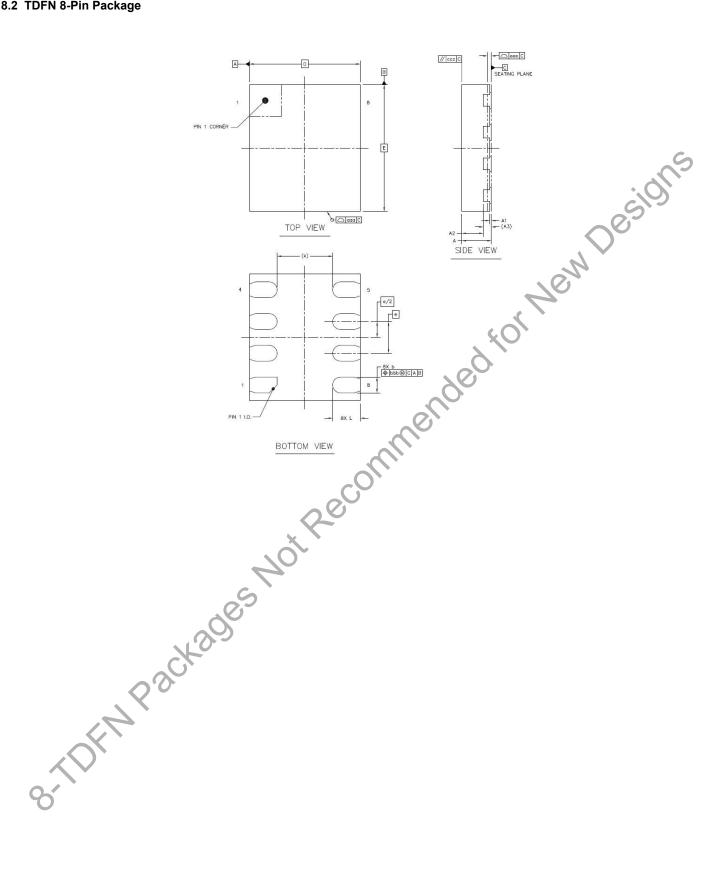

# 8.2 TDFN 8-Pin Package

Table 8.2. DFN 8-Pin Package Dimensions

| Dimension | MIN        | NOM      | MAX  |  |

|-----------|------------|----------|------|--|

| A         | 0.32       | 0.37     | 0.40 |  |

| A1        | 0.00       | 0.02     | 0.05 |  |

| A2        | 0.27       |          |      |  |

| A3        | 0.102 REF. |          |      |  |

| b         | 0.15       | 0.20     | 0.25 |  |

| D         | 1.40 BSC   |          |      |  |

| E         | 1.60 BSC   |          |      |  |

| е         |            | 0.40 BSC |      |  |

| L         | 0.30       | 0.35     | 0.40 |  |

| K         | 0.70 REF.  |          |      |  |

| aaa       | 0.10       |          |      |  |

| bbb       | 0.07       |          |      |  |

| ccc       | 0.10       |          |      |  |

| eee       | 0.05       |          |      |  |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 9. Land Patterns

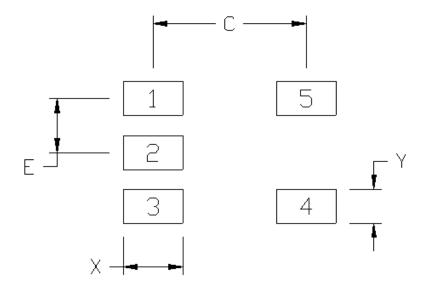

# 9.1 SOT23-5 5-Pin PCB Land Pattern

| Dimension | (mm) |

|-----------|------|

| С         | 2.70 |

| E         | 0.95 |

| X         | 1.05 |

| Y         | 0.60 |

# Note:

# General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

## **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020D specification for Small Body Components.

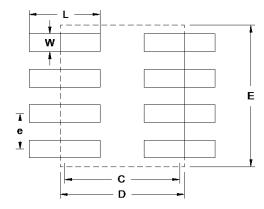

| Dimension | mm   |

|-----------|------|

| D         | 1.40 |

| E         | 1.60 |

| С         | 1.30 |

| L         | 0.80 |

| W         | 0.20 |

| е         | 0.40 |

### General

- 1. All dimensions shown are in millimeters (mm).

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

# Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 m minimum, all the way around the pad.

# Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 4. A 2x1 array of 0.55 mm square openings on a 0.90 mm pitch should be used for the center ground pad.

# **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Above notes and stencil design are shared as recommendations only. A customer or user may find it necessary to use different parameters and fine tune their SMT process as required for their application and tooling.

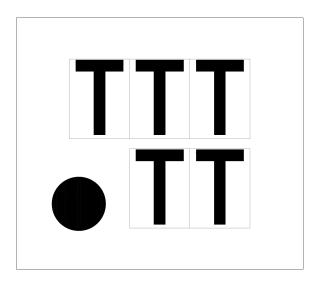

# 10. Top Marking

# 10.1 SOT23-5 5-Pin Top Marking

Note: TTTT is a manufacturing code.

# 10.2 TDFN 8-Pin Top Mark

Table 10.1. Top Marking Package Details

| Mark Method:       | Laser                                 |                                                                                         |  |

|--------------------|---------------------------------------|-----------------------------------------------------------------------------------------|--|

| Pin 1 Mark         | 0.30 mm Diameter (Bottom-Left Corner) | 0.30 mm Diameter (Bottom-Left Corner)                                                   |  |

| Font Size          | 0.4 mm Right-justified                |                                                                                         |  |

| Line 1 Mark Format | TTT = Mfg Code                        | First three characters of the Manufacturing Code from the Assembly Purchase Order form. |  |

| Line 2 Mark Format | TT = Mfg Code (Continued)             | Last two characters of the Manufacturing Code from the Assembly Purchase Order form.    |  |

# 11. Revision History

# Revision 1.2

November 2019

- · Added DFN8 package to specification, feature list, and ordering guide

- · Added DFN8 package pin description, package outline, and landing pattern

### **Revision 1.1**

March 2019

Removed all mention of AEC-Q100 qualification in product description and feature list.

# **Revision 1.0**

April 2018

- · Updated power numbers to be consistent with production test limits.

- · Moved detailed ordering guide to a separate selection guide.

- · Updated detailed description to be clearer and more accurate.

- · Added Default Bop, Brp column to Ording Guide.

### Revision 0.9

June 30, 2017

- · Updated 1. Electrical Specifications.

- · Updated 7. Ordering Information.

- · Minor typo corrections.

# Revision 0.1

February 1, 2016

· Initial release.

Products www.silabs.com/products

Quality www.silabs.com/quality

Support and Community community.silabs.com

### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the information supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required or Life Support Systems without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Labs p

### Trademark Information

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, ClockBuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadio®, EZRadioPRO®, Gecko OS, Gecko OS Studio, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri, the Zentri logo and Zentri DMS, Z-Wave®, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA