# TMC2340 Digital Synthesizer

Dual 16-Bit, 25 MOPS

## **Description**

The TMC2340 performs waveform synthesis, modulation, and demodulation. When presented with a TTL clock signal and user-selected 15-bit amplitude and 32-bit phase increment values, the TMC2340 automatically generates quadrature-matched pairs of 16-bit sine and cosine waves in DAC-compatible 16-bit offset binary format. If desired, these waveforms are easily phase or frequency-modulated on-chip, and the amplitude input facilitates gain adjustment or amplitude modulation. Digital output frequencies are restricted only by the Nyquist limit of clock rate/2, with frequency resolution of 0.006 Hz at the guaranteed maximum 25 MHz clock rate.

A new data word pair is available at the output every clock cycle. All input and output data ports are registered, with a user-configurable phase accumulator structure and input clock enables to simplify interfacing. The phase data range over a full 2∏ radians. All signals are TTL compatible.

Fabricated in Raytheon Semiconductor's OMICRON-CTM one-micron CMOS process, the TMC2340 operates at the 25 MHz maximum clock rate over the full commercial temperature (0 to 70°C) and supply (4.75 to 5.25V) voltage ranges, and is available in a low-cost 120 pin plastic pin grid array. The MIL-STD-883 version, the TMC2340L5V, is housed in a ceramic chip carrier and is specified over the full extended (-55°C to 125°C) case temperature range.

## **Features**

- User-configurable phase accumulator for waveform synthesis, frequency modulation or phase modulation

- Amplitude input for gain adjustment and amplitude modulation

- ◆ Guaranteed 25 Msps pipelined data throughput rate

- ◆ 15-bit magnitude, 32-bit phase data input precision

- 16-bit offset binary or 15-bit unsigned magnitude output data format

- Input register clock enables simplify interfacing

- ◆ Low power consumption CMOS process

- ♦ Single +5V power supply

- Available in a 120-pin plastic pin grid array package

- ◆ Compliant with MIL-STD-883B in a 132-leaded CERQUAD

# **Applications**

- Digital waveform synthesis, including quadrature functions

- Digital modulation and demodulation

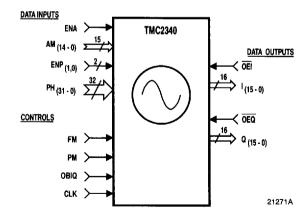

## TMC2340 Logic Symbol

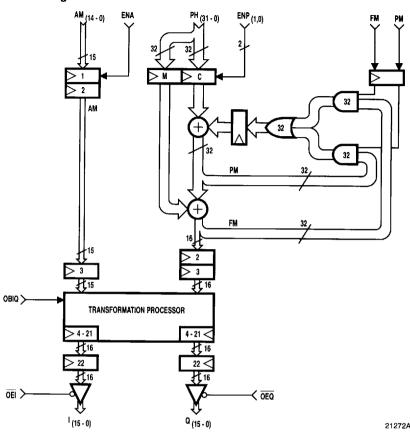

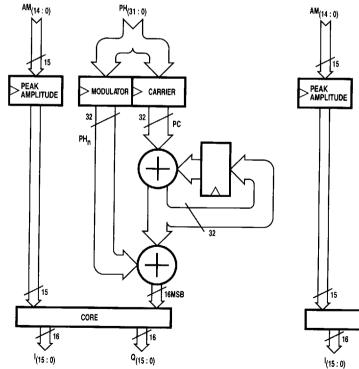

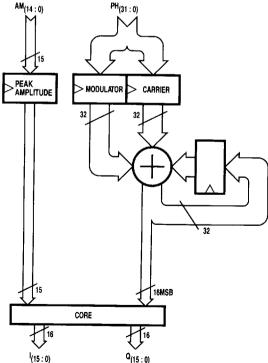

## **Functional Block Diagram**

## **Functional Description**

#### **General Information**

The TMC2340 converts Polar (Phase and Magnitude) data into Rectangular (Cartesian) format. The first transformed result is available at the outputs 22 clock cycles after startup, with new output data available every 40ns. All input and output data ports are registered, with input clock enables to simplify system bus connections.

The input ports accept 15-bit amplitude and 32-bit phase data, and the output ports produce 16-bit Rectangular data words in either 16-bit offset binary or 15-bit unsigned magnitude format. The 32-bit phase accumulator handles high-accuracy (0.006Hz at the maximum clock rate) phase increment values with minimal accumulation error. The flexible input phase accumulator structure supports frequency or phase

modulation, as determined by the input register clock enable ENYP<sub>1, 0</sub> and accumulator controls FM and PM. The 16 MSBs (Most Significant Bits) of phase data are used in the transformation itself.

## Signal Definitions

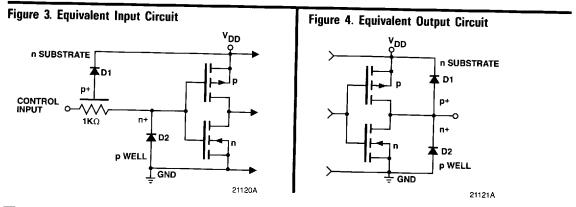

#### Power

V<sub>DD</sub>, GND The TMC2340 operates from a single +5V supply. All power and ground pins must be connected.

### Clock CLK

The TMC2340 operates from a single clock. All enabled registers are strobed on the rising edge of CLK, which is the reference for all timing specifications.

#### Inputs/Outputs

| AM <sub>14-0</sub> | $AM_{14-0}$ is the registered peak amplitude 15-bit input data port. $AM_{14}$ is the MSB.                                                                                                                                                          |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PH <sub>31-0</sub> | PH <sub>31-0</sub> is the registered Phase angle increment 32-bit input data port. The input phase accumulators are fed through this port in conjunction with the input enable select ENP <sub>1</sub> , 0. PH <sub>31</sub> is the MSB.            |

| <sup>1</sup> 15-0  | $I_{15-0}$ is the registered X-coordinate 16-bit output data port. This output is forced into the high-impedance state when $\overline{\text{OEI}} = \text{HIGH}$ . $I_0$ is the LSB. $I_{15}$ will be "stuck at" logic HIGH if $\text{OBIQ} = 0$ . |

| Q <sub>15-0</sub>  | Q <sub>15-0</sub> is the registered Cartesian                                                                                                                                                                                                       |

#### **Controls**

11

| ENA                 | Data presented to the input port AM are latched into the input registers on the current clock when ENA is HIGH. When ENA is LOW, the data stored in the register remains unchanged. |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENP <sub>1, 0</sub> | The value presented to the PH input port is latched into the phase accumulator input                                                                                                |

Y-coordinate 16-bit output data port. This

Q<sub>15</sub> will remain at logic HIGH if OBIQ=0.

output is forced to the high-impedance state when  $\overline{OEQ}$  = HIGH.  $Q_{\Pi}$  is the LSB.

registers on the current clock, as deter-

mined by the control inputs ENP1 0, as

M register set to 0, C register input enabled

| where C is the Carrier register and M is the Modulation register, and $0 = LOW$ , |

|-----------------------------------------------------------------------------------|

| 1 = HIGH. See the <i>Functional Block Diagram</i> .                               |

FM, PM

The user determines the internal phase

Accumulator structure implemented on the

next clock by setting the accumulator

control word FM, PM, as shown below:

| FM, PM | Instruction                           |

|--------|---------------------------------------|

| 00     | No accumulation performed             |

| 01     | PM accumulator path enabled           |

| 10     | FM accumulator path enabled           |

| 11     | (Nonsensical) logical OR of PM and FM |

where 0=LOW, 1=HIGH. See the Functional Block Diagram.

The accumulator will roll over correctly when full-scale is exceeded, allowing the user to perform continuous phase accumulation through  $2\pi$  radians, or 360 degrees.

OBIQ The format select control sets the numeric format of the Rectangular data: offset binary format when HIGH, and unsigned when LOW. This is a static input. See the *Timing Diagram*.

OEI, OEO

Data in the output registers are available at the outputs of the device when the respective asynchronous Output Enables are LOW.

When OEX or OEY is HIGH, the respective

output port is in the high-impedance state.

**Raytheon Semiconductor**

#### **Package Interconnections**

| Signal<br>Type | Signal<br>Name     | Function              | H5 Package Pins                                                                                                                              | L5 Package Pins                                                                                                                |

|----------------|--------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Power          | V <sub>DD</sub>    | Supply Voltage        | C3, E3, H3, L4, L6, L8, L11, F11, E11, C11, C8, C6                                                                                           | 1, 9, 21, 37, 45, 53, 67, 87, 91, 99, 112, 120                                                                                 |

|                | GND                | Ground                | D3, E2, E1, F2, G3, K3, L3, L7, K11, J11, G11, F12, E12, D11, C10, C9, B7, C7, C5, C4                                                        | 5, 11, 12, 14, 17, 29, 33, 49, 75,<br>83, 86, 89, 95, 104, 108, 115, 116,<br>124, 129                                          |

| Clock          | CLK                | System Clock          | F3                                                                                                                                           | 13                                                                                                                             |

| Inputs         | AM <sub>14-0</sub> | Radius Data           | F13, G13, G12, H13, H12, H11, J13, J12,<br>K13, K12, L13, L12, M13, M12, N13                                                                 | 85, 84, 82, 81, 80, 79, 78, 77, 76, 74, 73, 71, 69, 68, 66                                                                     |

|                | PH <sub>31-0</sub> | Phase Data            | L10, N12, N11, M10, L9, N10, M9, N9,<br>M8, N8, N7, M7, N6, M6, N5, M5, N4,<br>L5, M4, N3, M3, N2, M2, N1, L2, M1,<br>L1, K2, J3, K1, J2, J1 | 61, 60, 59, 58, 57, 56, 55, 54, 52, 51, 50, 48, 47, 46, 44, 43, 42, 41, 40, 39, 38, 36, 34, 31, 30, 28, 27, 26, 25, 24, 23, 22 |

| Outputs        | <sup>[</sup> 15-0  | l Data                | D13, D12, C13, B13, C12, A13, B12, A12, B11, A11, B10, A10, B9, A9, B8, A8                                                                   | 90, 92, 93, 94, 96, 97, 100, 102,<br>105, 106, 107, 109, 110, 111, 113,<br>114                                                 |

|                | α <sub>15-0</sub>  | Q Data                | A7, A6, B6, A5, B5, A4, B4, A3, A2, B3,<br>A1, B2, B1, C2, C1, D2                                                                            | 117, 118, 119, 121, 122, 123, 125, 126, 127, 130, 132, 3, 4, 6, 7, 8                                                           |

| Controls       | ENR                | Radius In Enable      | M11                                                                                                                                          | 63                                                                                                                             |

|                | ENP <sub>1,0</sub> | Phase In Enable       | G1, G2                                                                                                                                       | 18, 16                                                                                                                         |

|                | FM, PM             | Modulation            | H2, H1                                                                                                                                       | 20, 19                                                                                                                         |

|                | OBIQ               | Cartesian Data Format | F1                                                                                                                                           | 15                                                                                                                             |

|                | ŌEI                | I Out Enable          | E13                                                                                                                                          | 88                                                                                                                             |

|                | 0EQ                | Q Out Enable          | D1                                                                                                                                           | 10                                                                                                                             |

| No Connect     | NC                 | No Cannect Pins       | _                                                                                                                                            | 2, 32, 35, 62, 64, 65, 72, 98, 101, 103, 128, 131                                                                              |

|                | l                  | Index Pin             | D4                                                                                                                                           | -                                                                                                                              |

#### Static Control Input

OBIQ determines the numeric format of the output data: offset binary if HIGH and unsigned magnitude if LOW. This control acts with 2-cycle latency on the chip's

22-cycle data path and is normally hardwired to a system-specific state.

Table 1. Data Input/Output Formats — Integer Format

|      | 0010 | 0.4  | 20  | 20  |   |   | Bit # | 16   | 15              | 14   |  |   | 0                | Format   |

|------|------|------|-----|-----|---|---|-------|------|-----------------|------|--|---|------------------|----------|

| Port | OBIQ | 31   | 30  | 29  | • | • |       | 16   | 19              | 14   |  | • |                  | Tormat   |

| AM   | Х    |      |     |     |   |   |       |      |                 | 214  |  |   | 2 <sup>0</sup> . | U        |

| PH   | X    | + 20 | 2-1 | 2-2 |   |   |       | 2-15 | 2-16            | 2-17 |  |   | <sub>2</sub> -31 | (xπ) T/U |

| 1    | 0    | _    |     |     |   |   |       |      |                 | 214  |  |   | 2 <sup>0</sup> . | U        |

| i    | 1    |      |     |     |   |   |       |      | 2 <sup>15</sup> | 214  |  |   | 20.              | В        |

| a    | 0    |      |     |     |   |   |       |      |                 | 214  |  |   | 2 <sup>0</sup> . | U        |

| ū    | 1    |      |     |     |   |   |       |      | 215             | 214  |  |   | 2 <sup>0</sup> . | В        |

#### Notes:

- ±2<sup>0</sup> denotes two's complement sign or highest magnitude bit - since phase angles are module 2π and phase accumulator is module 2<sup>32</sup>, this bit may be regarded as ±π.

- 2. All phase angles are in terms of  $\pi$  radians, hence notation "x $\pi$ "

- A sign-and-magnitude "Q" output is obtained by appending the input bit PH<sub>31</sub> as a sign bit to the corresponding (i.e., delayed 22 cycles) Q<sub>14-0</sub>.

- A sign-and-magnitude "I" output is obtained by appending the exclusive OR of PH<sub>31</sub> and PH<sub>30</sub> as a sign bit to the corresponding I<sub>14-0</sub>.

- When OBIQ=0, outputs I<sub>15</sub> and Q<sub>15</sub> become "do not connects" and will stay logic HIGH. (They may be wired to V<sub>DD</sub>, left open, or connected to any logic input without damage to the part or excessive power consumption.)

#### 6. Formats:

T/U=Two's Complement/Unsigned Magnitude 32 Bits

U=Unsigned Magnitude 15 Bits

B=Offset Binary 16 Bits

|      | AM, I, Q |         |                      | PH                  |

|------|----------|---------|----------------------|---------------------|

| HEX  | U        | В       | T                    | U                   |

| FFFF |          | 32767   | $-\pi \cdot 2^{-15}$ | $\pi(2-2^{-15})$    |

|      |          |         |                      |                     |

| 8001 |          | 1       | $-\pi(1-2^{-15})$    | $\pi(1+2^{-15})$    |

| 8000 |          | 0       | - π                  | $\pi$               |

| 7FFF | 32767    | -1      | $\pi(1-2^{-15})$     | $\pi(1-2^{-15})$    |

|      |          |         |                      |                     |

| 0001 | 1        | - 32767 | $\pi \cdot 2^{-15}$  | $\pi \cdot 2^{-15}$ |

| 0000 | 0        | - 32768 | 0                    | 0                   |

"Hex" column contains the 16 MSBs of the 32-bit phase input (16 LSBs are 0), the 15 bits of the amplitude input or the 16 bits of the offset binary output.

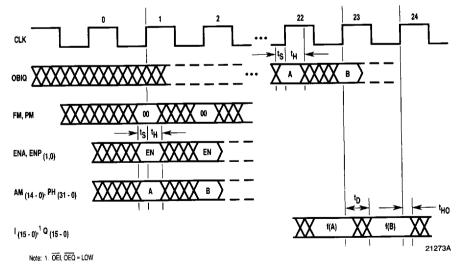

Figure 1. Timing Diagram, Operating Conditions

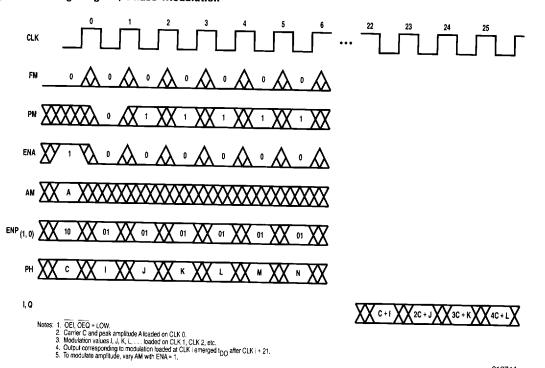

Figure 2. Timing Diagram, Phase Modulation

21274A

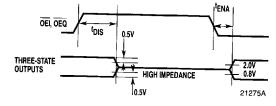

Figure 5. Transition Levels for Three-State Measurements

Absolute maximum ratings (beyond which the device may be damaged) 1

| Input Vol | age                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Vo |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Temperat  | ure       -60 to +130°C         Operating, case       -60 to +130°C         junction       175°C         Lead, soldering (10 seconds)       300°C         Storage       -65 to +150°C                                                                                                                                                                                                                                                                                             |

| Notes:    | <ol> <li>Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.</li> <li>Applied voltage must be current limited to specified range, and measured with respect to GND.</li> <li>Forcing voltage must be limited to specified range.</li> <li>Current is specified as conventional current flowing into the device.</li> </ol> |

### **Operating conditions**

|                 |                                |                      |      | Temperature Range |     |       |       |  |  |

|-----------------|--------------------------------|----------------------|------|-------------------|-----|-------|-------|--|--|

|                 |                                |                      | Sta  | ndard             | Ext | ended | 1     |  |  |

| Parame          | ter                            | Test Conditions      | Min  | Max               | Min | Max   | Units |  |  |

| V <sub>DD</sub> | Supply Voltage                 |                      | 4.75 | 5.25              | 4.5 | 5.5   | ٧     |  |  |

| VIL             | Input Voltage, Logic LOW       |                      |      | 0.8               |     | 0.8   | V     |  |  |

| VIH             | Input Voltage, Logic HIGH      |                      | 2.0  |                   | 2.0 |       | V     |  |  |

| OL              | Output Current, Logic LOW      |                      |      | 8.0               |     | 8.0   | mA    |  |  |

| IOH             | Output Current, Logic HIGH     |                      |      | -4.0              |     | -4.0  | mA    |  |  |

| tcy             | Cycle Time                     | V <sub>DD</sub> =Min |      | 50                |     | 55    | ns    |  |  |

| -01             | • •                            | TMC2340-1            |      | 40                | ł   | 45    | ns    |  |  |

| tpwL            | Clock Pulse Width, LOW         | V <sub>DD</sub> =Min | 10   |                   | 11  |       | ns    |  |  |

| 7716            | •                              | TMC2340-1            | 8    |                   | 8   |       | ns    |  |  |

| tpwH            | Clock Pulse Width, HIGH        | V <sub>DD</sub> =Min | 8    |                   | 8   |       | ns    |  |  |

| 4 0011          | •                              | TMC2340-1            | 6    |                   | 6   | ļ.    | ns    |  |  |

| ts              | Input Setup Time               |                      | 12   |                   | 13  |       | ns    |  |  |

| -3              |                                | TMC2340-1            | 10   | Ì                 | 11  | 1     | ns    |  |  |

| tH              | Input Hold Time                |                      | 1    | 1                 | 2   |       | ns    |  |  |

| 71              | ···                            | TMC2340-1            | 1    |                   | 2   | 1     | ns    |  |  |

| TA              | Ambient Temperature, Still Air |                      | 0    | 70                | 1   |       | €     |  |  |

| TC              | Case Temperature               |                      |      |                   | -55 | 125   | ٠     |  |  |

# **TMC2340**

# RAYTHEON/ SEMICONDUCTOR

## Electrical characteristics within specified operating conditions <sup>1</sup>

|                  |                                          |                                                | · ·      | Temperature Range |                                                  |       |       |  |

|------------------|------------------------------------------|------------------------------------------------|----------|-------------------|--------------------------------------------------|-------|-------|--|

|                  |                                          |                                                | Sta      | ndard             | Ext                                              | ended | 1     |  |

| Para             | meter                                    | Test Conditions                                | Min      | Мах               | Min Max                                          |       | Units |  |

| <sub>l</sub> ppa | Supply Current, Quiescent                | V <sub>DD</sub> =Max, V <sub>IN</sub> =0V      |          | 10                |                                                  | 10    | mA    |  |

| <sup>I</sup> DDU | Supply Current, Unloaded                 | V <sub>DD</sub> = Max, f = 20MHz               |          |                   | <del>                                     </del> | 1     |       |  |

|                  |                                          | OEI and OEQ = V <sub>DD</sub>                  |          | 160               | l                                                | 160   | mA    |  |

| l <sub>fL</sub>  | Input Current, Logic LOW                 | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V    |          | 10                |                                                  | -10   | μΑ    |  |

| IH               | Input Current, Logic HIGH                | $V_{DD} = Max, V_{IN} = V_{DD}$                | <u> </u> | 10                |                                                  | 10    | μА    |  |

| νΟΓ              | Output Voltage, Logic LOW                | V <sub>DD</sub> =Min, I <sub>OL</sub> =Max     |          | 0.4               |                                                  | 0.4   | V     |  |

| $v_{OH}$         | Output Voltage, Logic HIGH               | V <sub>DD</sub> =Min, I <sub>OH</sub> =Max     | 2.4      |                   | 2.4                                              | - "   | ٧     |  |

| OZL              | Hi-Z Output Leakage Current, Output LOW  | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V    |          | -40               |                                                  | -40   | μА    |  |

| OZH              | Hi-Z Output Leakage Current, Output HIGH | $V_{DD} = Max, V_{IN} = V_{DD}$                | <u> </u> | 40                |                                                  | 40    | μA    |  |

| os               | Short-Circuit Output Current             | V <sub>DD</sub> = Max, Output HIGH, one pin to | -20      | -100              | - 20                                             | - 100 | μA    |  |

|                  |                                          | ground, one second duration max.               |          |                   |                                                  |       |       |  |

| Ci               | Input Capacitance                        | T <sub>A</sub> = 25°C, f = 1MHz                |          | 10                |                                                  | 10    | pF    |  |

| $\overline{c_0}$ | Output Capacitance                       | $T_A = 25$ °C, $f = 1$ MHz                     |          | 10                |                                                  | 10    | pF    |  |

Note: 1. Actual test conditions may vary from those shown, but specified operation is guaranteed.

## Switching characteristics within specified operating conditions

|                  |                      |                                                 |      | Temperature Range |      |      |       |  |  |

|------------------|----------------------|-------------------------------------------------|------|-------------------|------|------|-------|--|--|

| _                |                      | 1                                               | Star | dard              | Exte | nded |       |  |  |

| Paran            | neter                | Test Conditions                                 | Min  | Max               | Min  | Max  | Units |  |  |

| tD               | Output Delay         | $V_{DD} = Min, C_{LOAD} = 40pF$                 |      | 22                |      | 25   | ns    |  |  |

|                  |                      | TMC2340-1                                       |      | 20                |      | 23   | ns    |  |  |

| t <sub>HO</sub>  | Output Hold Time     | V <sub>DD</sub> =Max, C <sub>LOAD</sub> =40pF   |      | 4                 |      | 4    | ns    |  |  |

|                  |                      | TMC2340-1                                       |      | 4                 |      | 4    | ns    |  |  |

| <sup>t</sup> ENA | Output Enable Delay  | V <sub>DD</sub> = Min, C <sub>LOAD</sub> = 40pF |      | 13                |      | 17   | ns    |  |  |

|                  |                      | TMC2340-1                                       |      | 12                |      | 15   | ns    |  |  |

| <sup>t</sup> DIS | Output Disable Delay | V <sub>DD</sub> =Min, C <sub>LOAD</sub> =40pF   |      | 14                |      | 14   | ns    |  |  |

|                  |                      | TMC2340-1                                       |      | 13                |      | 13   | пѕ    |  |  |

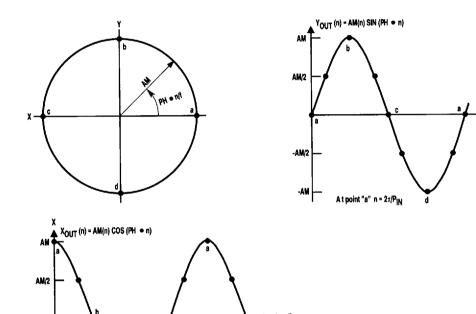

# Phase/Amplitude to Sine/Cosine Conversion Geometry

#### Polar-To-Rectangular Conversion Geometry

The TMC2340 performs a coordinate-space transformation according to the familiar trigonometic relationships shown in *Figure 6*.

With constant amplitude and phase increment values and either FM or PM HIGH, the TMC2340 will output a series of complex number pairs representing the horizontal and vertical projections of a vector rotating about the origin, i.e., a cosine wave and a sine wave.

Figure 6. Input to Output Relationship for Sinusoid Generation

21276A

t = n/I<sub>CLK</sub>

-AM/2

### **Digital Waveform Synthesis**

#### Waveform Generation and Modulation

Utilizing the internal phase accumlators in a TMC2340, users can easily generate high-accuracy digital quadrature sinusoidal waveforms with minimal support. The 32-bit data path ensures negligible cumulative error in most applications, and the accuracy of the transform is limited only by the truncation of the result to 16 bits prior to the Transform Processor and the  $\pm 1$  LSB maximum error of the transform algorithm. Amplitude Modulation is of course performed simply by varying the amplitude input. Either Frequency (phase angle shifted by the cumulative sum of the modulation input) or Phase (phase angle shifted by the instantaneous modulation input) Modulation can be realized by configuring the TMC2340 as shown in Figures 7 and 8.

In *Figure 7*, the output valid during clock rising edge m+22 is:

$$I_{m+22} = AM_{m}cos(PH_{m} + mPC)$$

$Q_{m+22} = AM_{m}sin(PH_{m} + mPC)$

where  $PH_m$  and  $AM_m$  are the chip inputs at rising edge m, PC is the (constant) carrier phase increment,  $PM_1 = 0$ ,  $PM_2 = 1$ , and  $PM_{1-m} = 0$ .

Expressed in terms of time instead of clock cycles.

$$I(m+22)/f_{clk} = AM_m/f_{clk}cos(PH_m/f_{clk})$$

where  $f_{\text{ClK}}$  is the frequency of the square wave applied to CLK.

Figure 7. Performing Phase Modulation

Figure 8. Performing Frequency Modulation

21277A

21278A

In Figure 8, the output valid during clock rising edge n+22 is:

$$I_{m+22} = AM_m \cos \left( \sum_{m=1}^{n} PH_m + nPC \right)$$

$$m = 1$$

$$Q_{n+22} = AM_m \sin \left( \sum_{m=1}^{n} PH_m + nPC \right)$$

$$m = 1$$

where  $\text{PH}_m$  and  $\text{AM}_m$  are the chip inputs at rising edge AM, PC is the (constant) carrier phase increment,  $FM_1 = 0$ ,  $FM_2 = 1$ , and PM = 0.

Expressed in terms of time instead of clock cycles,

$$I_{(n+22)/fclk} = AM_{m/fclk} \cos \left( \sum_{m-1}^{n} PH_{m/fclk} + PC \cdot m/fclk \right)$$

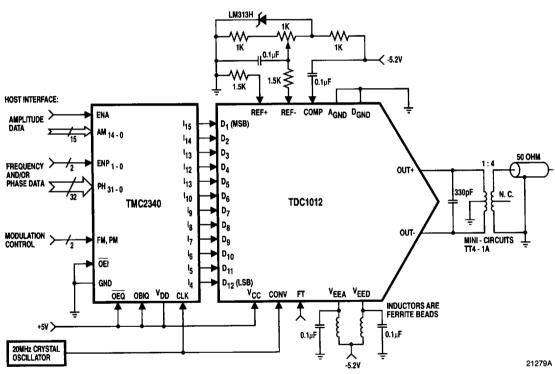

#### Digital Synthesizer with TDC1012 D/A Converter

Connection of the TMC2340 to the TDC1012 D/A converter is straightforward. As shown in Figure 9, the TDC1012 data lines are connected to either the I or Q outputs. Both outputs may be used, with two TDC1012's for quadrature synthesis.

Figure 9. Frequency Synthesizer

Raytheon Semiconductor

Note: To use two TDC1012's in quadrature, connect second TDC1012 to Q<sub>15</sub> (MSB) to Q<sub>4</sub> and ground OEQ.

Signal Synthesis

# **TMC2340**

#### RAYTHEON/ SEMICONDUCTOR

#### Control of the TMC2340

The TMC2340 needs to be initialized to tell it what frequency and amplitude sinusoid to generate. To initialize amplitude, apply the desired full-scale amplitude to the AM input port of the TMC2340 (AM14 through AM0) and pull ENA HIGH for one clock cycle. This will load the amplitude. If ENA is held HIGH, then the amplitude will follow the inputs on the AM port. If the user assumes an implied binary point before the MSB of the AM port, the input range will be 0 to just under 1, and the outputs will fall between 0 and 2, with binary points after  $1_{15}$  and  $0_{15}$ .

To set the frequency, the C register must be loaded with a value which is the phase increment per clock cycle. If the binary point is considered to be just left of the MSB (input range is 0 to almost 1) then the output frequency is the TMC2340 clock frequency multiplied by the number loaded into C. Since C is 32 bits wide, with a 20MHz clock, one LSB represents a frequency increment of 0.005Hz.

To load the C register, set  $ENYP_1=1$  and  $ENYP_0=0$ ; the data presented at the PH port will be loaded on the next clock rising edge.

At this point the TMC2340 has been initialized and can be put into one of three modes depending upon the states of FM and PM:

Mode 0 FM=0, PM=0

In this mode the chip is in standby. The unchanging output corresponds to AM cos(PM) on the I outputs with PM being the phase increment.

Mode 1 FM=1, PM=0

Frequency Modulation Mode. The chip generates an output signal of peak amplitude AM and frequency determined by accumulating the sum of the phase

increment values in the C and M registers (more about the M register in a later section).

Mode 2 FM=0, PM=1

Phase Modulation Mode. The TMC2340

generates a sinusoid of the frequency

represented in the C register and the peak

amplitude in the AM register. On each

clock cycle, the phase of the signal is offset

by the value in the M register.

#### Modulation

The output of the TMC2340 can be phase (Mode 2) or frequency (Mode 1) modulated. An unmodulated sinusoid results if the contents of registers C and M are held constant. Its frequency is set by C (Mode 2) or C+M (Mode 1). Since the state of the M register is not defined at power up, the M register should be loaded or cleared to begin operation.

If the signal is to be frequency modulated then the modulation signal is loaded into the M register. The format for the frequency is the same as that for the C register. If  $ENYP_1$ , 0=0, 1 then the data that is presented at the PH port is automatically loaded on each clock rising edge.

For phase modulation, the phase deviation is loaded into the M register (same manner as for frequency modulation). The units of the phase offset are cycles and full-scale is just under one output cycle per TMC2340 clock cycle. The MSB represents a phase of 180°, and the LSB a phase of about  $8 \times 10^{-8}$  degrees (eight one-hundred-millionths of a degree), or  $\pi/2^{31}$  radians.

To synchronize two TMC2340s, first load them with their respective data in mode 0, then switch them simultaneously to either Mode 1 or Mode 2.

#### Calculating Frequency, Amplitude, and Phase Input Values for the TMC2340

This Application Brief discusses equations which simplify the calculation of register values which control the TMC2340. These values allow the generation of output carrier frequency, frequency or phase modulation, and output amplitude.

The results of the equations are converted to binary register values and should be rounded to the resolution of the applicable register (32 or 15-bits). For negative values of phase or frequency modulation, use these equations for positive values and see Table 1 of the TMC2340 data sheet to convert them to negative values.

The TMC2340 operates by continuously incrementing a register (phase accumulator) that rolls over when it becomes full. For example, if the next increment to the phase accumulator causes it to overflow by 47 LSBs, the phase accumulator retains the value 47. The value present in the carrier register (C) is the amount by which the phase accumulator is incremented each system clock cycle. As the value of the carrier register is increased, the value with which the the phase accumulator is incremented each clock cycle is increased, resulting in an increased carrier frequency.

The magnitude of the carrier is determined or modulated by the value loaded in the AM register. Phase modulation is accomplished by adding the value of the phase accumulator to the value of the modulation (M) register. This adds an offset to the phase of the carrier. This does not affect the increment value of the phase accumulator and therefore only effects the phase of the carrier, leaving the frequency constant.

Adding the value of the modulation register to the phase accumulator along with the value of the carrier register on each clock cycle results in a shift in frequency. This is because the phase accumulator is incremented by a different amount each clock cycle.

Frequency or phase modulation is selected with the FM and PM input pins which configure the TMC2340. The equations presented herein are useful for setting carrier frequency and phase. output amplitude, and frequency and phase modulation. To modulate the carrier with an external signal, the signal must be digitized and those values loaded into the modulation inputs of the TMC2340.

The carrier and modulation registers are loaded through the PH<sub>31-0</sub> inputs. The ENP<sub>1.0</sub> inputs select the desired register. The amplitude register is loaded through the AM14.0 inputs.

#### **CARRIER FREQUENCY:**

#### **AMPLITUDE AND AMPLITUDE MODULATION:**

#### FREQUENCY MODULATION:

#### PHASE MODULATION:

Modulation Register (M) Value =

$$\frac{\text{Desired Change in Phase in radians (degrees)}}{2\pi \text{ (360°)}} \times 2^{32}$$

### **EXAMPLE 1:** Set carrier frequency to 3.579545 MHz with a system clock of 20MHz.

$$C = 0.17897725 X 4,294,967,296 = 768,701,436 = 2DD1 73FBh$$

= 0010 1101 1101 0001 0111 0011 1111 1011 =  $PH_{31-0}$

#### **EXAMPLE 2:** Set output amplitude to be 12.2% of full-scale.

$$AM = 3,998 = 0F9Eh = 0001 1111 0011 1100 = AM_{14-0}$$

## EXAMPLE 3: Change carrier frequency by 10kHz with a system clock of 3 MHz.

$$M = \frac{10 \times 10^{3}}{3 \times 10^{6}} \times 2^{32} = 14,316,558 = 00DA 740Eh$$

$M = 0000\ 0000\ 1101\ 1010\ 0111\ 0100\ 0000\ 1110\ = PH_{31-0}$

#### **EXAMPLE 4:** Shift the phase of any carrier frequency by 12°.

$$M = 0.033333 \ X \ 2^{32} = 143,165,577 = 0888 8889h$$

= 0000 1000 1000 1000 1000 1000 1001 =  $PH_{31-0}$

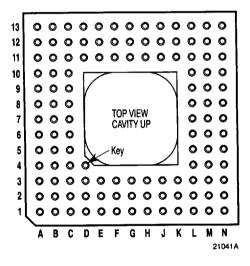

## Pin Assignments — 121-Pin Plastic Pin Grid Array, H5 Package; 120-Pin Ceramic PGA, G1 Package

| Pin        | Name             | Pin | Name            | Pin | Name            | Pin | Name             | Pin | Name             | Pin | Name             | Pin | Name             | Pin | Name             |

|------------|------------------|-----|-----------------|-----|-----------------|-----|------------------|-----|------------------|-----|------------------|-----|------------------|-----|------------------|

| A1         | Q <sub>5</sub>   | В3  | $\sigma^{e}$    | C5  | GND             | E1  | GND              | G11 | GND              | K1  | PH <sub>2</sub>  | L10 | PH <sub>31</sub> | M12 | AM <sub>1</sub>  |

| A2         | Q <sub>7</sub>   | B4  | αg              | C6  | V <sub>DD</sub> | E2  | GND              | G12 | AM <sub>12</sub> | K2  | PH <sub>4</sub>  | L11 | $V_{DD}$         | M13 | AM <sub>2</sub>  |

| A3         | α <mark>s</mark> | B5  | a <sub>11</sub> | C7  | GND             | E3  | V <sub>DD</sub>  | G13 | AM <sub>13</sub> | К3  | GND              | L12 | AM <sub>3</sub>  | N1  | PH <sub>8</sub>  |

| Α4         | α <sub>10</sub>  | B6  | 0 <sub>13</sub> | C8  | V <sub>DD</sub> | E11 | V <sub>DD</sub>  | ,H1 | PM               | K11 | GND              | L13 | AM <sub>4</sub>  | N2  | PH <sub>10</sub> |

| A5         | a <sub>12</sub>  | B7  | GND             | C9  | GND             | E12 | GND              | H2  | FM               | K12 | AM <sub>5</sub>  | M1  | PH <sub>6</sub>  | N3  | PH <sub>12</sub> |

| A6         | 0 <sub>14</sub>  | B8  | l <sub>1</sub>  | C10 | GND             | E13 | OEI              | Н3  | V <sub>DD</sub>  | K13 | AM <sub>6</sub>  | M2  | PHg              | N4  | PH <sub>15</sub> |

| A7         | Q <sub>15</sub>  | B9  | 13              | C11 | $v_{DD}$        | F1  | OBłQ             | H11 | AM <sub>9</sub>  | L1  | PH <sub>5</sub>  | M3  | PH <sub>11</sub> | N5  | PH <sub>17</sub> |

| A8         | 10               | B10 | l <sub>5</sub>  | C12 | 111             | F2  | GND              | H12 | AM <sub>10</sub> | L2  | PH <sub>7</sub>  | M4  | PH <sub>13</sub> | N6  | PH <sub>19</sub> |

| A9         | 12               | B11 | 17              | C13 | 113             | F3  | CLK              | H13 | AM <sub>11</sub> | L3  | GND              | M5  | PH <sub>16</sub> | N7  | PH <sub>21</sub> |

| A10        | 14               | B12 | وا              | D1  | ŌΕΩ             | F11 | ν <sub>DD</sub>  | J1  | PH <sub>O</sub>  | L4  | VDD              | M6  | PH <sub>18</sub> | N8  | PH <sub>22</sub> |

| A11        | i <sub>6</sub>   | B13 | 112             | D2  | $a_0$           | F12 | GND              | J2  | PH <sub>1</sub>  | L5  | PH <sub>14</sub> | M7  | PH <sub>20</sub> | N9  | PH <sub>24</sub> |

| A12        | lg<br>lg         | C1  | a <sub>1</sub>  | D3  | GND             | F13 | AM <sub>14</sub> | J3  | PH <sub>3</sub>  | L6  | V <sub>DD</sub>  | M8  | PH <sub>23</sub> | N10 | PH <sub>26</sub> |

| A13        | 110              | C2  | $a_2$           | D11 | GND             | G1  | ENP <sub>1</sub> | J11 | GND              | L7  | GND              | М9  | PH <sub>25</sub> | N11 | PH <sub>29</sub> |

| <b>B</b> 1 | 03               | C3  | V <sub>DD</sub> | D12 | 114             | G2  | ENP <sub>0</sub> | J12 | AM <sub>7</sub>  | L8  | V <sub>DD</sub>  | M10 | PH <sub>28</sub> | N12 | PH <sub>30</sub> |

| B2         | 04               | C4  | GND             | D13 | 1 <sub>15</sub> | G3  | GND              | J13 | AM <sub>8</sub>  | L9  | PH <sub>27</sub> | M11 | ENA              | N13 | AM <sub>0</sub>  |

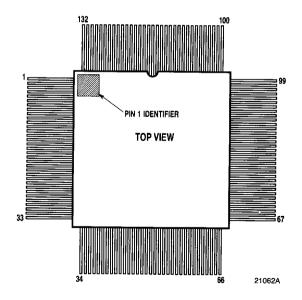

Pin Assignments — 132 Leaded CERQUAD, L5 Package

| Pin | Name             | Pin | Name             | Pin | Name             | Pin | Name             | Pin | Name            | Pin | Name            |

|-----|------------------|-----|------------------|-----|------------------|-----|------------------|-----|-----------------|-----|-----------------|

| 1   | v <sub>DD</sub>  | 23  | PH <sub>1</sub>  | 45  | v <sub>DD</sub>  | 67  | v <sub>DD</sub>  | 89  | GND             | 111 | l <sub>2</sub>  |

| 2   | NC               | 24  | PH <sub>2</sub>  | 46  | PH <sub>18</sub> | 68  | AM1              | 90  | I <sub>15</sub> | 112 | VDD             |

| 3   | $0_4$            | 25  | PH <sub>3</sub>  | 47  | PH <sub>19</sub> | 69  | AM2              | 91  | v <sub>DD</sub> | 113 | 11              |

| 4   | $a_3$            | 26  | PH <sub>4</sub>  | 48  | PH <sub>20</sub> | 70  | GND              | 92  | 114             | 114 | 10              |

| 5   | GND              | 27  | PH <sub>5</sub>  | 49  | GND              | 71  | AM <sub>3</sub>  | 93  | 113             | 115 | GND             |

| 6   | $\mathfrak{a}_2$ | 28  | PH <sub>6</sub>  | 50  | PH <sub>21</sub> | 72  | NC               | 94  | 112             | 116 | GND             |

| 7   | $a_1$            | 29  | GND              | 51  | PH <sub>22</sub> | 73  | AM <sub>4</sub>  | 95  | GND             | 117 | Q <sub>15</sub> |

| 8   | $\sigma_0$       | 30  | PH <sub>7</sub>  | 52  | PH <sub>23</sub> | 74  | AM <sub>5</sub>  | 96  | I <sub>11</sub> | 118 | a <sub>14</sub> |

| 9   | v <sub>DD</sub>  | 31  | РН <sub>8</sub>  | 53  | $v_{DD}$         | 75  | GND              | 97  | I <sub>10</sub> | 119 | a <sub>13</sub> |

| 10  | <u>DEQ</u>       | 32  | NC               | 54  | PH <sub>24</sub> | 76  | AM <sub>6</sub>  | 98  | NČ              | 120 | v <sub>DD</sub> |

| 11  | GND              | 33  | GND              | 55  | PH <sub>25</sub> | 77  | AM <sub>7</sub>  | 99  | ν <sub>oo</sub> | 121 | α <sub>12</sub> |

| 12  | GND              | 34  | PH <sub>9</sub>  | 56  | PH <sub>26</sub> | 78  | AM <sub>8</sub>  | 100 | lg l            | 122 | Q <sub>11</sub> |

| 13  | CLK              | 35  | NC               | 57  | PH <sub>27</sub> | 79  | AM <sub>9</sub>  | 101 | ŇC              | 123 | α <sub>10</sub> |

| 14  | GND              | 36  | PH <sub>10</sub> | 58  | PH <sub>28</sub> | 80  | AM <sub>10</sub> | 102 | 18              | 124 | GND             |

| 15  | OBIQ             | 37  | ∨ <sub>DD</sub>  | 59  | PH <sub>29</sub> | 81  | AM <sub>11</sub> | 103 | ŇC              | 125 | $a_9$           |

| 16  | ENP <sub>0</sub> | 38  | PH <sub>11</sub> | 60  | PH <sub>30</sub> | 82  | AM <sub>12</sub> | 104 | GND             | 126 | $\sigma_8$      |

| 17  | GND              | 39  | PH <sub>12</sub> | 61  | PH <sub>31</sub> | 83  | GND              | 105 | 17              | 127 | α <sub>7</sub>  |

| 18  | ENP <sub>1</sub> | 40  | PH <sub>13</sub> | 62  | NC               | 84  | AM <sub>13</sub> | 106 | 16              | 128 | NC              |

| 19  | PM               | 41  | PH <sub>14</sub> | 63  | ENA              | 85  | AM <sub>14</sub> | 107 | 15              | 129 | GND             |

| 20  | FM               | 42  | PH <sub>15</sub> | 64  | NC               | 86  | GND              | 108 | GND             | 130 | $0_6$           |

| 21  | $v_{DD}$         | 43  | PH <sub>16</sub> | 65  | NC               | 87  | $v_{DD}$         | 109 | 14              | 131 | NC              |

| 22  | PH <sub>0</sub>  | 44  | PH <sub>17</sub> | 66  | $AM_0$           | 88  | OEI              | 110 | 13              | 132 | 0 <sub>5</sub>  |

# **Ordering Information**

| Product<br>Number | Temperature Range                    | Screening    | Package                        | Pakcage<br>Marking |

|-------------------|--------------------------------------|--------------|--------------------------------|--------------------|

| TMC2340H5C1       | STD: T <sub>A</sub> = 0 to 70℃       | Commercial   | 121-Pin Plastic Pin Grid Array | 2340H5C1           |

| TMC2340H5C        | STD: T <sub>A</sub> = 0 to 70°C      | Commercial   | 121-Pin Plastic Pin Grid Array | 2340H5C            |

| TMC2340L5V1       | EXT: T <sub>C</sub> = -55°C to 125°C | MIL-STD-883B | 132-Leaded CERQUAD             | 2340L5V1           |

| TMC2340L5V        | EXT: T <sub>C</sub> = -55°C to 125°C | MIL-STD-883B | 132-Leaded CERQUAD             | 2340L5V            |

| TMC2340G1V1       | EXT: T <sub>C</sub> = -55°C to 125°C | MIL-STD-883B | 120-Pin Ceramic PGA            | 2340G1V1           |

| TMC2340G1V        | EXT: T <sub>C</sub> = -55°C to 125°C | MIL-STD-883B | 120-Pin Ceramic PGA            | 2340G1V            |

40G06720 Rev B 8/93