## Am9338 8-Bit Multiple Port Register

#### inctive Characteristics:

word x 1 bit simultaneous read-write three ddress register.

ccess time of 48 ns typical.

lave enable allows scanning of memory contents.

- 100% reliability assurance testing in compliance with MIL STD 883

- Electrically tested and optically inspected die for the assemblers of hybrid products

- Mixing privileges for obtaining price discounts.

Refer to price list

- Available in highly reliable molded. hermetic dual in-line or hermetic flat package

#### FUNCTIONAL DESCRIPTION

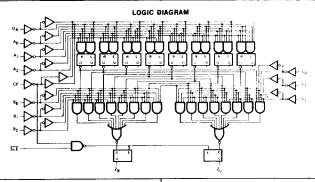

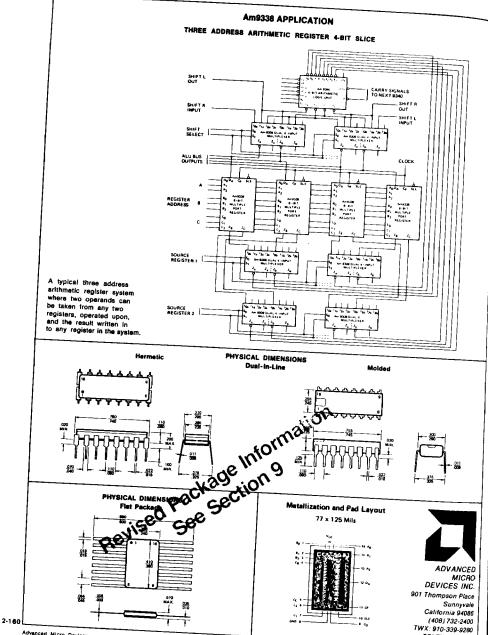

The Am9338 is a three-address eight-bit register organized as eight words of one bit per word. The register is designed for high-speed memory applications and is particularly suitable as the high-speed scratch pad memory in military and commercial three-address computers. Data can be written into one location and simultaneously read from any two locations.

The register is organized in a master slave arrangement where there are eight master latches and Iwo slave latches. Data on the D. Input is stored in the master latch selected by the write address field A during the clock LOW time. Data from the eight masters is then selected by the two independent read address fields B, C and stored in the two slave latches during the clock HIGH time. This eight master we slave arrangement makes the register indistinguishable from an eight master eight slave system and allows both the two read addresses B and C and the write address A to be simultaneously applied to the register at the start of a clock cycle. A slave enable is provided which if held LOW continuously enables the two slave latches and immediately transfers information from the master latches to the outputs so that the memory contents can be scanned asynchronously.

##

#### Amesse ORDERING INFORMATION

Temperature 10717011011

Rappe Package Coc to Hizage Number Type H6M933859X Molded DIP Hermetic DECO 0°G to +75°C -55°C to +125°C U7B933859X Hermund DIP U7B933851X -55°C to +125°C U4L933851X Hermetic Flat Pak Dice Note UXX9338XXD

Note: The dice supplied will contain units which meet both 0°C to +75°C and +55°C to +125°C temperature ranges.

## CONNECTION DIAGRAM Top View

NOTE: PIN 1 is marked for orientation

| MAXIMUM R. 3S (Above which the useful life may be impaired)     |                  |  |

|-----------------------------------------------------------------|------------------|--|

| Storage Temperature                                             | 0000             |  |

| Temperature (Ambient) Under Bias                                | -65°C to +       |  |

| Supply Voltage to Ground Potential (Pin 16 to Pin 8) Continuous | 55°C to +125°    |  |

| DC Voltage Applied to Outputs for High Output State             | 0.5 V to +7      |  |

| DC Input Voltage                                                |                  |  |

| Output Current, Into Outputs                                    | -0.5 V to +5.51  |  |

| DC Input Current                                                | 30 n             |  |

|                                                                 | -30 mA to +5.0 m |  |

## ELECTRICAL CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (Unless Otherwise Noted)

Am833859X  $T_A = 0^{\circ}\text{C to } + 75^{\circ}\text{C}$   $V_{CC} = 5.0 \text{ V} \pm 5\%$  $T_A = -55^{\circ}\text{C to } + 125^{\circ}\text{C}$   $V_{CC} = 5.0 \text{ V} \pm 18\%$

| arameters Description    |                                       | Test Conditions Min.                                                                 |     | Typ. (Note 1) | Max. | Units |

|--------------------------|---------------------------------------|--------------------------------------------------------------------------------------|-----|---------------|------|-------|

| V <sub>OH</sub>          | Output HIGH Voltage                   | $V_{CC} = MIN., I_{OH} = -0.8 \text{ mA}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$    | 2.4 | 3.6           |      | Volt  |

| VoL                      | Output LOW Voltage                    | $V_{CC} = MiN.$ , $I_{OL} = 16.0 \text{ mA}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$ |     | 0.2           | 0.4  | Vot   |

| V <sub>IH</sub>          | Input HIGH Level                      | Guaranteed Input logical HiGH voltage for all inputs                                 | 2.0 |               |      | Vol   |

| V <sub>IL</sub>          | Input LOW Level                       | Guaranteed input logical LOW voltage for all inputs                                  |     |               | 0.8  | Vol   |

| I <sub>IL</sub> (Note 2) | Unit Load<br>Input LOW Current        | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 0.4 V                                      |     | -1.0          | -1.6 | mA    |

| I <sub>IH</sub> (Note 2) | Unit Load<br>Input HIGH Current       | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 2.4 V                                      |     | 4.0           | 40   | μΑ    |

|                          | Input HIGH Current                    | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 5.5 V                                      |     |               |      |       |

| Isc                      | Output Short Circuit Current          | V <sub>CC</sub> = MAX., V <sub>OUX</sub> = 0.0 V                                     | -10 |               | 1.0  | mA    |

| lcc                      | Power Supply Current                  | V <sub>CC</sub> = MAX.                                                               | -10 | -35           | 70   | mA    |

|                          | limits are at Voc = 5.0 V 25°C ambies |                                                                                      |     | 64            | 99   | mA    |

Notes: 1) Typical limits are at V<sub>CC</sub> = 5.0 V, 25°C ambient and maximum loading.

## SWITCHING CHARACTERISTICS (T<sub>A</sub> = 25°C) (V<sub>CC</sub> = 5.0 V, C<sub>L</sub> = 15 $\mu$ F)

| Parameters                            |                                  | Test Conditions                   | Min         | Тур         | Max           | Unit |

|---------------------------------------|----------------------------------|-----------------------------------|-------------|-------------|---------------|------|

| l <sub>pd+</sub>                      | Turn Off Delay CP to Output      | $A_{0+2} = B_{0,1,2} = C_{0,1,2}$ | 12          | 24          | 42            |      |

| Լա-                                   | Turn On Delay CP to Output       | SLE = H                           | 10          | <del></del> | <del></del> - | ns   |

| t <sub>pd+</sub> (D <sub>A</sub> -Z)  | Turn Off Delay Data to Output    |                                   | <del></del> | 19          | 40            | ns   |

| I <sub>pd</sub> _ (D <sub>A</sub> -Z) | Turn On Delay Data to Output     | SLE = L. C, = L                   | 17          | 35          | 75            | ns   |

| t <sub>pd+</sub> (B,C-Z)              | Turn Off Delay Address to Output |                                   | 20          | 42          | 68            | ns   |

| t <sub>pd</sub> _ (B,C-Z)             |                                  | C <sub>p</sub> = H                | 13          | 26          | 43            | ns   |

|                                       | Turn On Delay Address to Output  |                                   | 24          | 48          | 81            | ns   |

| I <sub>st</sub> (D <sub>A</sub> )     | Set Up Time HIGH Date            |                                   | 7           | 15          |               |      |

| I <sub>st</sub> (D <sub>A</sub> )     | Set Up Time LOW Data             |                                   | <u> </u>    |             | 23            | ns   |

| I, (A)                                | Set Up Time, Address Inputs      | <del></del>                       | 3           | 8           | 13            |      |

| CP, 'L'                               | Minimum LOW Clock Pulse Width    |                                   | 3           | 10          | 23            | ns   |

| CP, 'H'                               | Minimum HIGH Clock Pulse Width   |                                   |             | 11          | 16            |      |

|                                       | Clock Pulse Width                | 1                                 |             | 10          | 15            | ns   |

<sup>21</sup> Actual input currents are obtained by multiplying unit load current by input load factor (see Loading Rules).

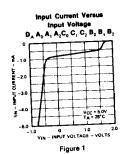

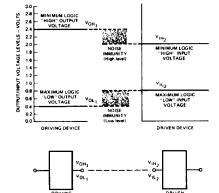

## TYPICAL INPUT AND OUTPUT CHARACTERISTICS

Figure 3

#### EFINITION OF TERMS

#### WASCRIPT TERMS:

If HIGH, applying to a HIGH logic level or when used with  $V_{\text{CC}}$  $\mathbf{b}$  indicate high  $\mathbf{V}_{\mathrm{CC}}$  value.

L LOW, applying to LOW logic level or when used with  $V_{\mathcal{CC}}$  to indicate low V<sub>CC</sub> value.

Output.

#### FUNCTIONAL TERMS:

$\mathbf{A}_{\mathbf{8}_{-2}}$  Write address field. Data on  $\mathbf{D}_{\mathsf{A}}$  is written into the location specified by the A address field.

$\mathbf{B}_{\mathbf{q}_{-2}}$  Read address field. Data stored in the master latch specified by the B Read Address Field is transferred to the B slave latch and appears at the  $Z_{\rm B}$  output when the clock pulse goes from a LOW logic level to a HIGH logic level.

$\mathbf{C}_{\mathbf{e}_{-2}}$  Read Address Field. Data stored in the master latch specifled by the C Read Address Field is transferred to the C slave latch and appears at the  $\mathbf{Z}_{\mathbf{C}}$  output when the clock pulse goes from a LOW logic level to a HIGH logic level.

CP Clock Pulse. On going from a HIGH logic level to a LOW logic level the information on the D, input is stored in the master latch specified by the Write A Address Field. When the clock pulse goes from a LOW logic level to a HIGH logic level information from the master latch or latches specified by the B and C Read Address Fields are stored in the two slave latches and appears at the out-

DA Information on the DA input is written into the master latch specified by the A Address Field when the clock goes from a HIGH logic level to a LOW logic level.

Fan-Out The logic HIGH or LOW output drive capability in terms of Input Unit Loads.

Input Unit Load One T'L gate input load. In the HIGH state it is equal to  $I_{\rm H}$  and in the LOW state it is equal to  $I_{\rm R}$  .

SLE Slave Enable. When LOW continuously allows information from the master latch addressed by the two read fields B, C to appear at the outputs  $Z_B$ ,  $Z_C$ .

Z. The B read address output.

Z<sub>C</sub> The C read address output.

#### OPERATIONAL TERMS:

in Forward input load current.

$I_{OH}^-$  Output HIGH current, forced out of output in  $V_{OH}$  test.

$\mathbf{I}_{\mathrm{OL}}$ . Output LOW current, forced into the output in  $\mathbf{V}_{\mathrm{OL}}$  test.

$I_{\rm CC}$  The current drawn by the device from  $V_{\rm CC}$  power supply with input and output terminals open.

Reverse input load current.

Negative Current | Current flowing out of the device.

Positive Current Current flowing into the device.

V<sub>IH</sub> Minimum logic HIGH input voltage.

VIL Maximum logic LOW input voltage

Input voltage applied in  $\mathbf{I}_{\mathrm{IL}}$ ,  $\mathbf{I}_{\mathrm{IH}}$  tests.

V<sub>OH</sub> Minimum logic HIGH output voltage with output HIGH current lost flowing out of output.

${f V}_{\rm OL}$  Maximum logic LOW output voltage with output LOW current  ${f I}_{\rm OL}$  flowing into output

#### SWITCHING TERMS

The propagation delay from the clock input LOW to HIGH transition to the Z output LOW to HiGH transition. Refer to Figure 4. The propagation delay from the clock input HIGH to LOW

transition to the Z output HiGH to LOW transition. Refer to Figure 4.  $\mathbf{t}_{\mathrm{cl}}\left(\mathbf{D}_{\mathbf{A}}\right)$  . The time required for a LOW logic level to be present at the DA input prior to the clock input transition from LOW to HIGH in order for the master latch to retain a LOW logic level. Refer to Figure 7. LOW data must be present at all times between t<sub>st</sub> max. and t<sub>er</sub> min.

$\mathbf{t}_{H}\left(\mathbf{D}_{\mathbf{A}}\right)$  . The time required for a HIGH logic level to be present at the  $D_{\rm A}$  input prior to the clock input transition from LOW to HIGH in order for the master latch to retain a HIGH logic level. Refer to Figure 7. HIGH data must be present at all times between  $t_{\rm 3H}$  max. and t<sub>st</sub> min.

1.(A) The time, relative to either clock edge, required for the device to respond to changes on the A address inputs.

$\mathbf{t}_{\mathrm{od}_+}(\mathbf{D}_{\mathtt{A}})$  The propagation delay from the data input LOW to HiGH transition to the Z output LOW to HIGH transition. Refer to Figure 5.

$_{

m sd_{-}}$  (D $_{

m A}$ ). The propagation delay from the data input HIGH to LOW transition to the Z output HiGH to LOW transition. Refer to Figure 5. t<sub>bd+</sub>(B,C-Z) The propagation delay from the B or C address input transition to the Z output LOW to HIGH transition. Refer to Figure 6.

$t_{pd}$  (B,C-Z) The propagation delay from the B, C address input transition to the Z output HIGH to LOW transition. Refer to Figure 6.

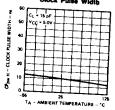

CP L' The minimum LOW clock pulse width required to write data into the master latch. Refer to Figure 8.

CP ... 'H' The minimum HiGH clock pulse width required to store information into the slave latch. Refer to Figure 9. 2-157

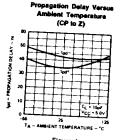

## TYPICAL SWITCHING TIME CHARACTERISTICS

All inputs and outputs loaded with 15 pF capacitance only. Output capacitance is referred to as  $C_{

m L}$

**Propagation Delay Versus Ambient Temperature** (D, to Z)

Propagation Delay Versus Ambient Temperature

Figure 4

Figure 5

Figure 6

Minimum LOW Clock Pulse Width

Minimum HIGH Clock Pulse Width

Figure 7

Figure 8

Figure 9

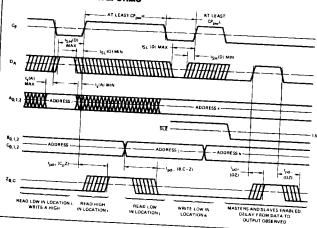

## SWITCHING TIME WAVEFORMS

#### KEY TO TIMING DIAGRAM

#### MSI INTERFACING RULES

| Interfacing                             | Equivalent<br>Input Unit Load |     |  |

|-----------------------------------------|-------------------------------|-----|--|

| Digital Family                          | HIGH                          | LOW |  |

| Advanced Micro Devices 9300/2500 Series | 1                             | 1   |  |

| FSC Series 9300                         | 1                             | 1   |  |

| Advanced Micro Devices 54/7400          | 1                             | 1   |  |

| Ti Series 54/7400                       | 1                             | 1   |  |

| Signetics Series 8200                   | 2                             | 2   |  |

| National Series DM 75/85                | 1                             | 1   |  |

| DTL Series 930                          | 12                            | 1   |  |

#### Am9338 LOADING RULES (in unit loads)

| input/Output    | Pin<br>No.'s | Input<br>Unit Load | Outpu<br>HIGH | l Drive<br>LOW |

|-----------------|--------------|--------------------|---------------|----------------|

| B <sub>o</sub>  | 1            | 0.625              |               | _              |

| В               | 2            | 0.625              |               | _              |

| B <sub>2</sub>  | 3            | 0.625              |               |                |

| Z <sub>e</sub>  | 4            |                    | 20            | 10             |

| z <sub>c</sub>  | 5            |                    | 20            | 10             |

| C,              | 6            | 0.625              |               | _              |

| C,              | 7            | 0.625              |               |                |

| GND             | 8            | _                  |               |                |

| C <sub>o</sub>  | 9            | 0.625              | _             | _              |

| SLE             | 10           | 0.625              |               |                |

| CP              | 11           | 0.625              |               | _              |

| DA              | 12           | 0.625              |               |                |

| A <sub>2</sub>  | 13           | 0.625              |               |                |

| A,              | 14           | 0.625              |               |                |

| <b>A</b> ₀      | 15           | 0.625              |               | _              |

| v <sub>cc</sub> | 16           |                    |               |                |

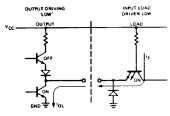

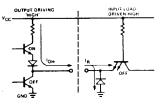

#### INPUT/OUTPUT INTERFACE CONDITIONS

#### Voltage Interface Conditions — LOW & HIGH

#### Current Interface Conditions - LOW

#### Current Interface Conditions — HIGH

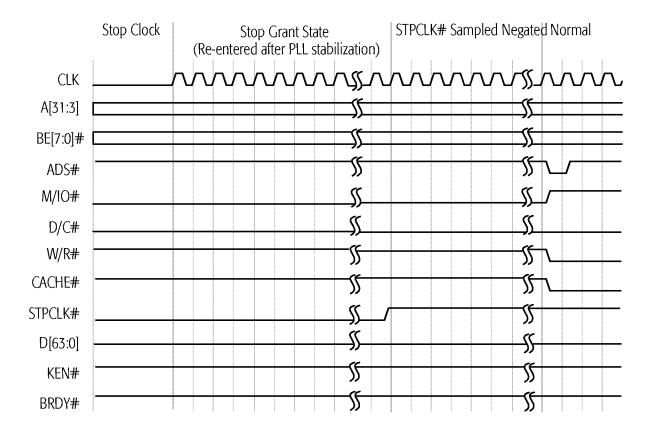

Figure 75. Stop Grant and Stop Clock Modes, Part 2

21850E/0-November 1998

# INIT-Initiated Transition from Protected Mode to Real Mode

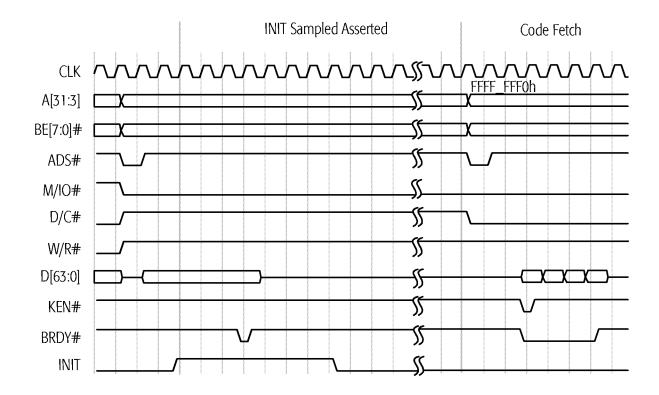

INIT is typically asserted in response to a BIOS interrupt that writes to an I/O port. This interrupt is often in response to a Ctrl-Alt-Del keyboard input. The BIOS writes to a port (similar to port 64h in the keyboard controller) that asserts INIT. INIT is also used to support 80286 software that must return to Real mode after accessing extended memory in Protected mode.

The assertion of INIT causes the processor to empty its pipelines, initialize most of its internal state, and branch to address FFFF\_FFF0h—the same instruction execution starting point used after RESET. Unlike RESET, the processor preserves the contents of its caches, the floating-point state, the MMX state, Model-Specific Registers (MSRs), the CD and NW bits of the CR0 register, the time stamp counter, and other specific internal resources.

Figure 76 shows an example in which the operating system writes to an I/O port, causing the system logic to assert INIT. The sampling of INIT asserted starts an extended microcode sequence that terminates with a code fetch from FFFF\_FFFOh, the reset location. INIT is sampled on every clock edge but is not recognized until the next instruction boundary. During an I/O write cycle, it must be sampled asserted a minimum of three clock edges before BRDY# is sampled asserted if it is to be recognized on the boundary between the I/O write instruction and the following instruction. If INIT is asserted synchronously, it can be asserted for a minimum of one clock. If it is asserted asynchronously, it must have been negated for a minimum of two clocks, followed by an assertion of a minimum of two clocks.

Figure 76. INIT-Initiated Transition from Protected Mode to Real Mode

21850E/0-November 1998

## **6** Power-on Configuration and Initialization

On power-on the system logic must reset the AMD-K6-2 processor by asserting the RESET signal. When the processor samples RESET asserted, it immediately flushes and initializes all internal resources and its internal state, including its pipelines and caches, the floating-point state, the MMX and 3DNow! states, and all registers. Then the processor jumps to address FFFF FFF0h to start instruction execution.

## 6.1 Signals Sampled During the Falling Transition of RESET

FLUSH#

FLUSH# is sampled on the falling transition of RESET to determine if the processor begins normal instruction execution or enters Tri-State Test mode. If FLUSH# is High during the falling transition of RESET, the processor unconditionally runs its Built-In Self Test (BIST), performs the normal reset functions, then jumps to address FFFF\_FFF0h to start instruction execution. (See "Built-In Self-Test (BIST)" on page 217 for more details.) If FLUSH# is Low during the falling transition of RESET, the processor enters Tri-State Test mode. (See "Tri-State Test Mode" on page 218 and "FLUSH# (Cache Flush)" on page 103 for more details.)

**BF[2:0]**

The internal operating frequency of the processor is determined by the state of the bus frequency signals BF[2:0] when they are sampled during the falling transition of RESET. The frequency of the CLK input signal is multiplied internally by a ratio defined by BF[2:0]. (See "BF[2:0] (Bus Frequency)" on page 92 for the processor-clock to bus-clock ratios.)

**BRDYC#**

BRDYC# is sampled on the falling transition of RESET to configure the drive strength of A[20:3], ADS#, HITM#, and W/R#. If BRDYC# is Low during the fall of RESET, these outputs are configured using higher drive strengths than the standard strength. If BRDYC# is High during the fall of RESET, the standard strength is selected. (See "BRDYC# (Burst Ready Copy)" on page 95 for more details.)

21850E/0-November 1998

## **6.2 RESET Requirements**

During the initial power-on reset of the processor, RESET must remain asserted for a minimum of 1.0 ms after CLK and  $V_{CC}$  reach specification. (See "CLK Switching Characteristics" on page 255 for clock specifications. See "Electrical Data" on page 247 for  $V_{CC}$  specifications.)

During a warm reset while CLK and  $V_{\rm CC}$  are within specification, RESET must remain asserted for a minimum of 15 clocks prior to its negation.

## 6.3 State of Processor After RESET

### **Output Signals**

Table 31 shows the state of all processor outputs and bidirectional signals immediately after RESET is sampled asserted.

**Table 31. Output Signal State After RESET**

| Signal           | State    | Signal   | State    |

|------------------|----------|----------|----------|

| A[31:3], AP      | Floating | LOCK#    | High     |

| ADS#, ADSC#      | High     | M/IO#    | Low      |

| APCHK#           | High     | PCD      | Low      |

| BE[7:0]#         | Floating | PCHK#    | High     |

| BREQ             | Low      | PWT      | Low      |

| CACHE#           | High     | SCYC     | Low      |

| D/C#             | Low      | SMIACT#  | High     |

| D[63:0], DP[7:0] | Floating | TDO      | Floating |

| FERR#            | High     | VCC2DET  | Low      |

| HIT#             | High     | VCC2H/L# | Low      |

| HITM#            | High     | W/R#     | Low      |

| HLDA             | Low      | _        | _        |

### **Registers**

Table 32 on page 175 shows the state of all architecture registers and Model-Specific Registers (MSRs) after the processor has completed its initialization due to the recognition of the assertion of RESET.