# 256K Dynamic RAM Controller/Driver

# SN74S409-2/DP8409A-2 SN74S409/DP8409A

#### Features/Benefits

- All DRAM drive functions on one chip have on-chip highcapacitance load drivers (specified up to 88 DRAMs)

- Drives directly all 16K, 64K and 256K DRAMs; capable of addressing up to 1M words

- Propagation delays of 25 nsec typical at 500 pF load

- Supports READ, WRITE and READ-MODIFY-WRITE cycles

- Eight modes of operation support externally-controlled and automatic access and refresh, as well as special memory initialization access

- On-chip 9-bit refresh counter with selectable End-of-Count (127, 255 or 511)

- Direct replacement for National DP8409, DP8409A

# **Operating Modes**

| 0  | Externally-controlled fresh            |

|----|----------------------------------------|

| 1  | Auto refresh – forced                  |

| 2  | Automatic burst refresh                |

| 3a | All-RAS auto write                     |

| 3b | Externally-controlled All-RAS write    |

| 4  | Externally-controlled access           |

| 5  | Auto access, slow tRAH, hidden refresh |

| 6  | Auto access, fast tRAH                 |

| 7  | Set end of count                       |

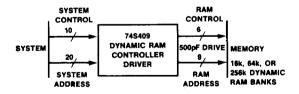

Interface Between System and DRAM Banks

## **Ordering Information**

| PART NUMBER | PACKAGE | TEMPERATURE       |

|-------------|---------|-------------------|

| SN74S409    | 48 N, D | Com               |

| SN74S409-2  | 48 N, D | Com, Speed Option |

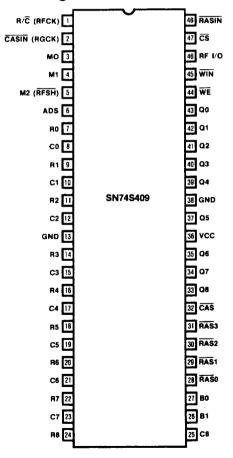

# Pin Configuration

Portions of this Data Sheet are reprinted courtesy of National Semiconductor Corporation.

Monolithic MM Memories

## **Block Diagram**

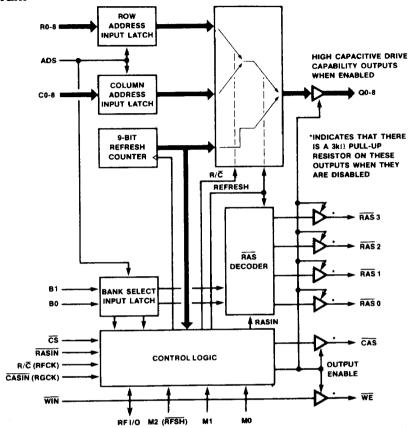

Figure 1. 74S409 Functional Block Diagram

# Description

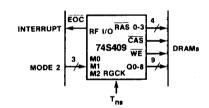

The 74S409 is a Multi-Mode Dynamic RAM Controller/Driver capable of directly driving up to 88 DRAMs. 20 address lines to the 74S409 allow it to address up to 1M words and it can drive 16K, 64K and 256K DRAMs. Since the 74S409 is a one-chip solution (including capacitive-load drivers), it minimizes propagation delay skews, and saves board space.

The 74S409's 8 operating modes offer externally-controlled or on-chip automatic access and refresh. An on-chip refresh counter makes refreshing (either externally or automatically controlled) less complicated; and automatic memory initialization is both simple and fast.

The 74S409 is a 48-pin DRAM Controller/Driver with 9 multiplexed address outputs and 6 control signals. It consists of two 9-bit address latches, a 9-bit refresh counter, and control logic. The 74S409 timing parameters are specified when driving the typical load capitance of 88 DRAMs, including trace capacitance.

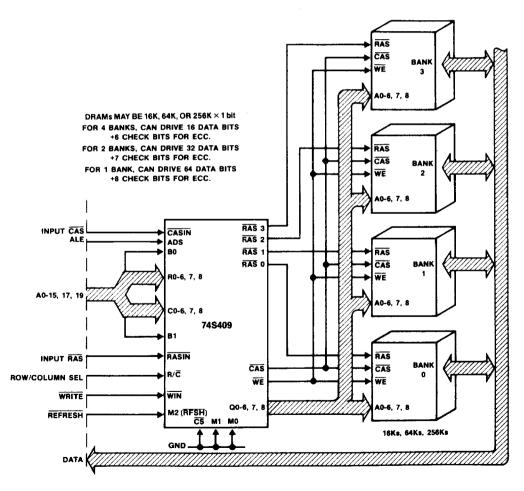

The 74S409 can drive up to 4 banks of DRAMs, with each bank comprised of 16Ks, 64Ks or 256Ks. Control signal outputs  $\overline{CAS}$  and  $\overline{WE}$  are provided with the same driving capability. Each  $\overline{RAS}$  output drives one bank of DRAMs so that the four  $\overline{RAS}$  outputs are used to select the banks, while  $\overline{CAS}$ ,  $\overline{WE}$  and the multiplexed addresses can be connected to all the banks of DRAMs. This leaves the non-selected banks in the standby mode (less than one tenth of the operating power) with the respective data outputs in three-state. Only the bank with its associated  $\overline{RAS}$  low will be written to or read from, except in mode 3 where all  $\overline{RAS}$  signals go low to allow fast memory initialization.

#### Pin Definitions

$V_{CC}$  GND, GND –  $V_{CC}$  = 5V ± 5%. The three supply pins have been assigned to the center of the package to reduce voltage drops, both DC and AC. There are also two ground pins to reduce the low level noise. The second ground pin is located two pins from  $V_{CC}$ , so that decoupling capacitors can be inserted directly next to these pins. It is important to adequately decouple this device, due to the high switching currents that will occur when all 9 address bits change in the same direction simultaneously. A recommended solution is a  $1-\mu$ F multilayer ceramic capacitor in parallel with a low-voltage tantalum capacitor, both connected close to pins 36 and 38 to reduce lead inductance.

R0-R8: Row Address Inputs.

C0-C8: Column Address Inputs.

**B0, B1: Bank Select Inputs**—Strobed by ADS. Decoded to enable one of the RAS outputs when RASIN goes low, in modes 4-6. In mode 7 B0, B1 are used to define End-of-Count (see table 3), and select mode 3a or 3b.

Q0-Q8: Multiplexed Address Outputs — Selected from the Row Address Input Latch, the Column Address Input Latch, or the Refresh Counter.

RASIN: Row Address Strobe Input — Enables selected RAS<sub>n</sub> output when M2 (RFSH) is high (modes 4-6), and all RAS<sub>n</sub> outputs in modes 0 and 3. RASIN input is disabled in modes 1 and 2.

R/C (RFCK)—In Auto-Refresh Mode this pin is the external Refresh Clock Input: one refresh cycle has to be performed each clock period. In all other modes it is Row/Column Select Input, selecting either the row or column address input latch onto the output bus.

CASIN (RGCK) — In modes 1, 2 and 3a, this pin is the RAS Generator Clock input. In all other modes it is CASIN (Column Address Strobe Input), which inhibits CAS output when high in Modes 3b and 4. In Mode 6 it can be used to prolong CAS output.

ADS: Address (Latch) Strobe Input—Strobes Input Row Address, Column Address, and Bank Select Inputs into respective latches when high; latches on High-to-Low transition.

CS: Chip Select Input—three-state's the Address Outputs and puts the control signal into a high-impedance logic "1" state when high (unless refreshing in one of the Refresh Modes). Enables all outputs when low.

M0, M1, M2 (RFSH): Mode Control Inputs — These 3 control pins determine the 8 major modes of operation of the 74S409 as depicted in Table 2.

RF I/O RFRQ — This I/O pin functions as a Reset Counter Input when set low from an external open-collector gate, or as a flag output. The flag goes active-low in Modes 0, 2 and

|      | SELECT<br>D BY ADS) | ENABLED RAS      |  |  |  |  |  |

|------|---------------------|------------------|--|--|--|--|--|

| B1 - | В0                  |                  |  |  |  |  |  |

| 0    | 0                   | RASO             |  |  |  |  |  |

| 0    | 1                   | RAS <sub>1</sub> |  |  |  |  |  |

| 1    | 0                   | RAS <sub>2</sub> |  |  |  |  |  |

| 1    | 1                   | RAS <sub>3</sub> |  |  |  |  |  |

Table 1. Memory Bank Decode

3a when the End-of-Count output is at 127, 255, or 511 (see Table 3). In Auto-Refresh Mode (mode 5) it is the Refresh Request (RFRQ) output.

WIN: Write Enable Input.

WE: Write Enable Output - Buffered output from WIN.

CAS: Column Address Strobe Output—In Modes 3a, 5, and 6, CAS transitions low following valid column address. In Modes 3b and 4, it goes low after R/C goes low, or follows CASIN going low if R/C is already low. CAS is high during refresh

RAS 0-3: Row Address Strobe Outputs — When M2(RFSH) is high (modes 4-6), the selected row address strobe output (decoded from signals B0, B1) follows the RASIN input. When M2 (RFSH) is low (modes 0-3) all RASn outputs go low together following RASIN going low in modes 0 and 3 and automatically in modes 1 and 2.

#### Input Addressing

The address block consists of a row-address latch, a column-address latch, and a resettable refresh counter.

The address latches are fall-through when ADS is high and latch when ADS goes low. If the address bus contains valid address until after the valid address time, ADS can be permanently high. Otherwise ADS must go low while the address is still valid.

In normal memory-access operation,  $\overline{\text{RASIN}}$  and  $\overline{\text{R/C}}$  are initially high. When the address inputs are enabled into the address latches (modes 3-6) the row addresses appear on the Q outputs. The Address Strobe also inputs the bank-select address, (B0 and B1). If  $\overline{\text{CS}}$  is low, all outputs are enabled. When  $\overline{\text{CS}}$  goes high, the address outputs go three-state and the control outputs first go high through a low impedance, and then are held by an on-chip high impedance. This allows output paralleling with other 74S409s for multi-addressing. All outputs go active about 50ns after the chip is selected again. If  $\overline{\text{CS}}$  is high, and a refresh cycle begins, all the outputs become active until the end of the refresh cycle.

# **Drive Capability**

The 74S409 has timing parameters that are specified with up to 600pF loads for  $\overline{CAS}$  and  $\overline{WE}$ , 500pF loads for  $Q_0$ - $Q_0$ , and 150pF loads for  $\overline{RAS}_n$  outputs. In a typical memory system this is equivalent to about 88 5V-only DRAMs, with trace lengths kept to a minimum. Therefore, the chip can drive four banks each of 16 or 22 bits, or two banks of 32 or 39 bits, or one bank of 64 or 72 bits.

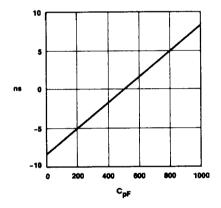

Less loading will slightly reduce the timing parameters, and more loading will increase the timing parameters, according to the graph of Figure 14. The AC performance parameters are specified with the typical load capacitance of 88 DRAMs. This graph can be used to extrapolate the variations expected with other loading.

# 74S409 Driving Any 16K, 64K or 256K DRAMs

The 74S409 can drive any 16K, 64K, or 256K DRAMs. The on-chip 9-bit counter with selectable End-of-Count can support refresh of 128, 256 and 512 rows, while the 9 address and 4  $\overline{\text{RAS}}_{\text{n}}$  outputs can address 4 banks of 16K, 64K or 256K DRAMs.

# Read, Write, and Read-Modify-Write Cycles

The output signal,  $\overline{WE}$ , determines what type of memory access cycle the memory will perform. If  $\overline{WE}$  is kept high white  $\overline{CAS}$  goes low, a read cycle occurs. If  $\overline{WE}$  goes low

before  $\overline{\text{CAS}}$  goes low, a write cycle occurs and data at DI (DRAM input data) is written into the DRAM as  $\overline{\text{CAS}}$  goes low. If  $\overline{\text{WE}}$  goes low later than tCWD after  $\overline{\text{CAS}}$  goes low, first a read occurs and DO (DRAM output data) becomes valid; then data DI is written into the same address in the DRAM when  $\overline{\text{WE}}$  goes low. In this read-modify-write case. DI and DO cannot be linked together. The type of cycle is therefore controlled by  $\overline{\text{WE}}$ , which follows  $\overline{\text{WiN}}$ .

# **Power-Up Initialize**

When V<sub>CC</sub> is first applied to the 74S409, an internal pulse clears the refresh counter, the internal control flip-flops, and sets the End-of-Count of the refresh counter to 127 (which may be changed via Mode 7). As V<sub>CC</sub> increases to about 2.3 volts, it holds the output control signals at a level of one Schottky diode-drop below V<sub>CC</sub>, and the output address to three-state. As V<sub>CC</sub> increases above 2.3 volts, control of these outputs is granted to the system.

# 74S409 Functional Modes Description

The 74S409 operates in 8 different functional modes selected by signals  $M_0, M_1, M_2$ . Mode 3 splits further to modes 3a and 3b determined by signals  $B_0, B_1$  in mode 7.

Mode 0 and mode 1 are generally used as Refresh modes for mode 4 and mode 5 respectively, and therefore will be described as mode-pairs 0,4 and 1,5.

Mode 6 is a fast access made for very fast DRAMs and mode 7 is used only to determine choice of mode 3a or 3b and for setting End-of-Count for the refresh modes.

| MODE           | (RFSH)<br>M2 | M1  | МО | MODE OF OPERATION                          | CONDITIONS                      |

|----------------|--------------|-----|----|--------------------------------------------|---------------------------------|

| 0              | 0            | 0   | 0  | Externally-controlled refresh              | RF I/O = EOC                    |

| _ <del>_</del> | 0            | 0   | 1  | Auto refresh – forced                      | RF I/O = Refresh request (RFRQ) |

|                | 0            | 1   | 0  | Automatic burst refresh                    | RF I/O = EOC                    |

| 3a*            | 0            | 1   | 1  | All-RAS auto write                         | RF I/O = EOC; all RAS active    |

| 3b*            | 0            | 1   | 1  | Externally-controlled All-RAS write        | All-RAS active                  |

| 4              | 1            | 0   | 0  | Externally-controlled access               | Active RAS defined by Table 2   |

| 5              | 1            | 0   | 1  | Auto access, slow tRAH, hidden refresh     | Active RAS defined by Table 2   |

| 6              | 1            | + 1 | 0  | Auto access, fast tRAH                     | Active RAS defined by Table 2   |

| 7              | 1            | 1   | 1  | Set end of count; determines mode 3a or 3b | See Table 3 for Mode 7          |

<sup>\*</sup>Mode 3a is selected by setting B<sub>0</sub>,B<sub>3</sub> to 01, 00, or 10 in mode 7.

\*Mode 3b is selected by setting B<sub>1</sub>,B<sub>0</sub> to 11 in mode 7.

Table 2. 74S409 Mode Select Options

# Mode 0 — Externally-Controlled Refresh Mode 4 — Externally-Controlled Access

Modes 0 and 4 facilitate external control of all timing parameters associated with the DRAMs. These modes are independent modes of operation though generally used together in the same application as shown in Figure 2.

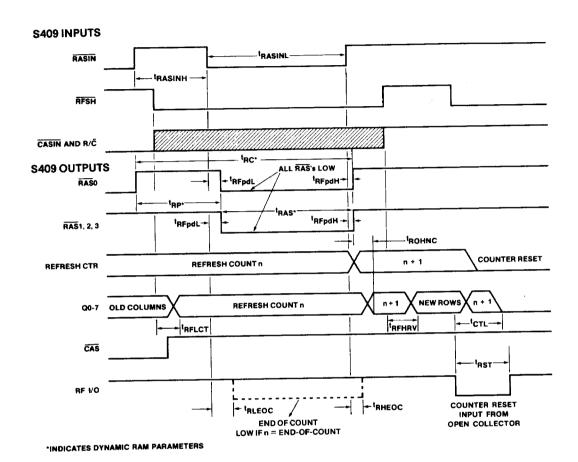

## **Mode 0—Externally-Controlled Refresh**

In this mode the input address latches are disabled from the address outputs and the refresh counter is enabled. All  $\overline{\mathsf{RAS}}$  outputs go low following  $\overline{\mathsf{RASIN}}$  and refresh the enabled row in all four banks.  $\overline{\mathsf{CASIN}}$  and  $\overline{\mathsf{R/C}}$  inputs are not used and  $\overline{\mathsf{CAS}}$  is inhibited. The refresh counter increments when either  $\overline{\mathsf{RASIN}}$  or  $\overline{\mathsf{M2}}$  ( $\overline{\mathsf{RFSH}}$ ) switch high while the other is still low.

RF I/O goes low when the count equals End-of-Count (as set in mode 7), and RASIN is low. The 9-bit counter will always roll-over to zero at 512, regardless of End-of-Count. However, the counter can be reset at any time by driving RF I/O low through an external open-collector.

During refresh, RASIN and M2 (RFSH) can transition low simultaneously because the refresh counter becomes valid on the output bus tRFLCT after RFSH goes low, which is a shorter time than tRFPDL. This means the counter address is valid on the Q outputs before RAS occurs on all RAS outputs, strobing the counter address into that row of all the DRAMs (see Figure 2.). To perform externally-controlled burst refresh, RFSH initially can again have the same edge as RASIN, but then maintains a low state, since RASIN going low-to-high increments the counter (performing the burst refresh).

Figure 2. Typical Application of 74S409 Using Externally-Controlled Access and Refresh in Modes 0 and 4

Figure 3. External Control Refresh Cycle (Mode 0)

# 9

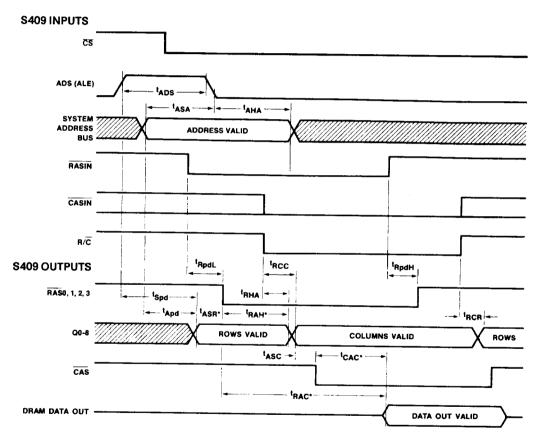

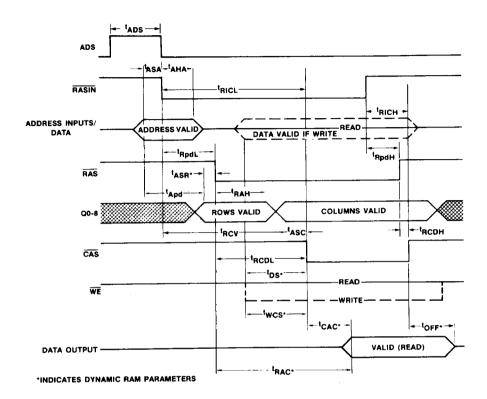

# **Mode 4** — Externally-Controlled Access

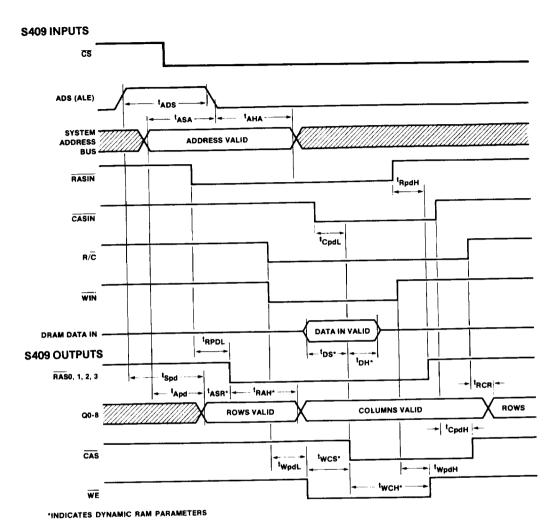

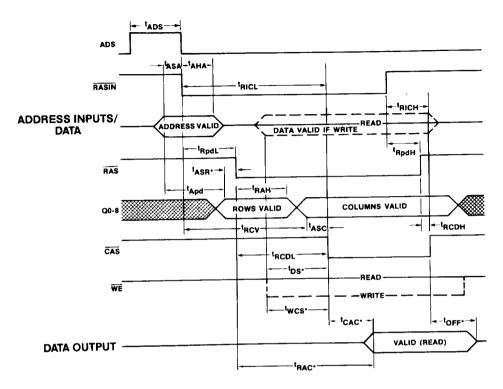

This mode facilitates externally controlling all access-timing parameters associated with the DRAMs. Figures 4 and 5 show the timing for read and write cycles.

# **Output Address Selection**

In this mode  $\overline{CS}$  has to be low at least 50 nsec before the outputs will be valid. With R/ $\overline{C}$  high, the row address latch

contents are transfered to the multiplexed address bus output Q0-Q8.  $\overline{\text{RASIN}}$  can go low after the row addresses have been set up on Q0-Q8, and enables one  $\overline{\text{RAS}}$  output selected by signals B0. B1 to strobe the Q outputs into the desired bank of memory. After the row-address hold-time of the DRAMs,  $R/\overline{C}$  can go low so that about 40 nsec later, the column address appears on the Q output.

\*INDICATES DYNAMIC RAM PARAMETERS

Figure 4. Read Cycle Timing (Mode 4)

Figure 5. Write Cycle Timing (Mode 4)

# **Automatic CAS Generation**

In a normal memory access cycle  $\overline{CAS}$  can be derived from inputs  $\overline{CASIN}$  or  $R/\overline{C}$ . If  $\overline{CASIN}$  is high, then  $R/\overline{C}$  going low switches the address output drivers from rows to columns.  $\overline{CASIN}$  then going low causes  $\overline{CAS}$  to go low approximately 40 ns later, allowing  $\overline{CAS}$  to occur at a predictable time (see Figure 5). For maximum system speed,  $\overline{CASIN}$  can be kept low, since  $\overline{CAS}$  will automatically occur approximately 60 ns after  $R/\overline{C}$  goes low (see Figure 4). Most DRAMs have a column address set-up time before  $\overline{CAS}$  (tASC) of 0 ns or -10 ns. In other words, a tASC greater than 0 ns is safe. This

feature reduces timing-skew problems, thereby improving access time of the system.

# **Fast Memory Access**

For faster access time, R/ $\overline{C}$  can go low a time delay (tRPDL + tRAH - tRHA) after  $\overline{RASIN}$  goes low, where tRAH is the Row-Address hold-time of the DRAM, and  $\overline{CASIN}$  can go low tRCC - tCPOL + tASC (min.) after R/ $\overline{C}$  goes low (see tDiF1, tDiF2 switching characteristics).

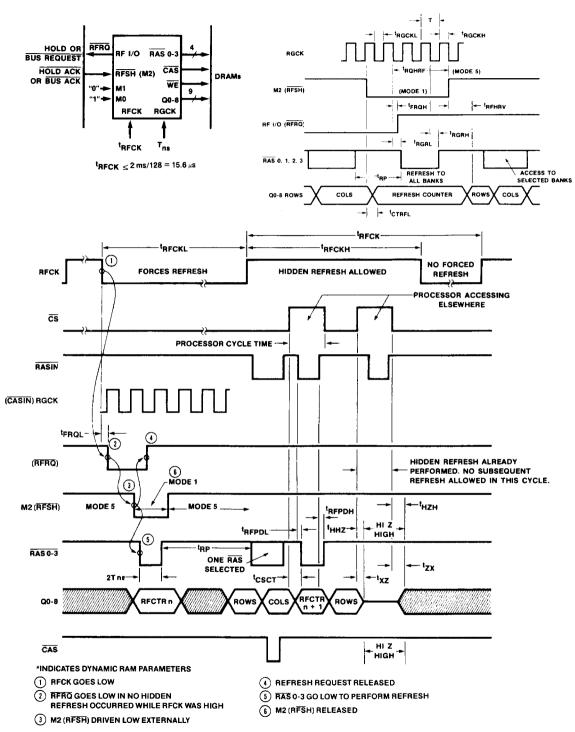

## Mode 1 — Automatic Forced Refresh Mode 5 — Automatic Access with Hidden Refresh

Mode 1 and Mode 5 are generally used together incorporating the advantages of the "hidden refresh" performed in mode 5 with the possibility to force a refresh by changing to mode 1. An advantage of the Automatic Access over the Externally-Controlled Access is the reduced memory access time, due to the fact that the output control signals are derived internally from one input signal (RASIN).

#### **Hidden and Forced Refresh**

Hidden Refresh is a term describing memory refresh performed when the system does not access the portion of memory controlled by the 74S409 ( $\overline{CS}=1$ ). A hidden refresh will occur once per Refresh Clock (RFCK) cycle provided  $\overline{CS}$  went high and  $\overline{RASIN}$  went low. If no hidden refresh occurred while RFCK was high, the RF I/O ( $\overline{RFRQ}$ ) goes low immediately after RFCK goes low, indicating to the system when a forced refresh is required. The system must allow a forced refresh to take place while RFCK is low by driving M2 ( $\overline{RFSH}$ ) low, thereby changing mode of operation to Mode 1.

The Refresh Request on RF I/O (RFRQ) is terminated as soon as RAS goes low, indicating to the system that the foced refresh has been done. The system should then drive M2 (RFSH) high, changing the mode of operation back to Mode 5 (see Figure 6).

#### Mode 1 — Automatic Forced Refresh

In Mode 1, the R/ $\overline{C}$  (RFCK) pin functions as RFCK (refresh cycle clock) instead of R/ $\overline{C}$ , and  $\overline{CAS}$  remains high. If RFCK is kept permanently high then whenever M2 ( $\overline{RFSH}$ ) goes

low, an externally-controlled refresh will occur and all  $\overline{\text{RAS}}$  outputs will follow  $\overline{\text{RASIN}}$ , strobing the refresh counter contents to the DRAMs. The RF I/O pin will always output high, but can be set low externally through an open-collector driver, to reset the refresh counter.

If RFCK is an input clock, one and only one refresh cycle must take place every RFCK cycle. If a hidden refresh does not occur while RFCK is high, in Mode 5, then RF I/O (Refresh Request) goes low immediately after RFCK goes low, indicating to the system that a forced refresh is required. The system must allow a forced refresh to take place while RFCK is low The Refresh Request signal on RF I/O may be connected to a Hold or Bus Request input to the system. The system acknowledges the Hold or Bus Request when ready, and outputs Hold Acknowledge or Bus Request Acknowledge. If this is connected to the M2 (RFSH) pin, a forced-refresh cycle will be initiated by the S409, and RAS will be internally generated on all four RAS outputs, strobing the refresh counter contents on the address oututs into all the DRAMs, An external RAS Generator Clock (RGCK) is required for this function. It is fed to the CASIN (RGCK) pin. and may be up to 10 MHz. Whenever M2 goes low (inducing a forced refresh). RAS remains high for one to two periods of RGCK, depending on when M2 goes low relative to the highto-low triggering edge of RGCK; RAS then goes low for two periods, performing a refresh on all banks. In order to obtain the minimum delay from M2 going low to RAS going low, M2 should go low tRESRG before the next falling edge of RGCK. The Refresh Request on RF I/O is terminated as RAS begins. so that by the time the system has acknowledged the removal of the request and disabled its Acknowledge, (i.e., M2 goes high). Refresh RAS will have ended, and normal operations can begin again in the Automatic Access mode (Mode 5). If it is desired that Refresh RAS end in less than 2 periods of RGCK from the time RAS went low, then M2 may go high earlier than terch after RF I/O goes high and RAS will go high tREBH after M2.

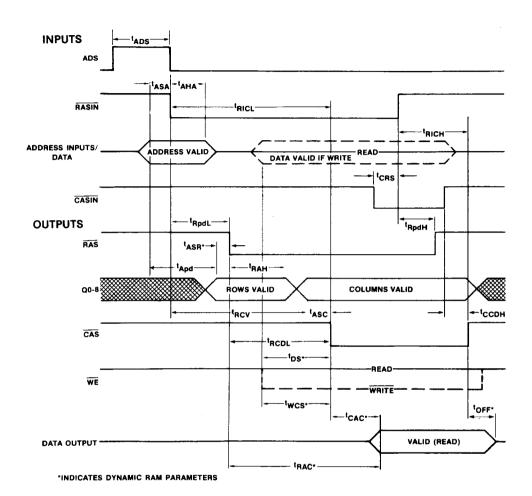

# Mode 5 — Automatic Access with Hidden Refresh

In this mode all address outputs, RAS and CAS are initiated from RASIN making the DRAM access appear similar to static RAM access. The hidden refresh feature enables DRAM refresh accomplished with no time-loss to the system.

Provided the input address is valid as ADS goes low, RASIN can go low any time after ADS. This is because the selected RAS occurs typically 27 ns later, by which time the row address is already valid on the address output of the 74S409. The Address Set-Up time (tASR), is 0 ns on most DRAMS. The 74S409 in this mode (with ADS and RASIN edges simultaneously applied) produces a minimum tASR of 0 ns. This is true provided the input address was valid tASR before ADS went low (see Figure 7).

Next, the row address is disabled that after  $\overline{RAS}$  goes low (30 ns minimum); in most DRAMs, that minimum is less than 30 ns. The column address is then set up and (tabc later.)  $\overline{CAS}$  occurs. The only other control input required is  $\overline{WIN}$ . When a write cycle is required,  $\overline{WIN}$  must go low at least 30 ns before  $\overline{CAS}$  is output low.

This gives a total typical delay from: input address valid to RASIN (15 ns); to RAS (27 ns); to rows held (50 ns); to columns valid (25 ns); to CAS (23 ns) = 140 ns (that is, 125 ns from RASIN). All of these typical figures are for heavy capacitive loading, of approximately 88 DRAMs.

# Refreshing

In this mode R/C (RFCK) functions as Refresh Clock and CASIN (RGCK) functions as RAS Generator Clock.

One refresh cycle must occur during each refresh clock period, and then the refresh address must be incremented before the next refresh-cycle. As long as 128 rows are refreshed every 2 ms (one row every 16  $\mu$ s), all 16K and 64K DRAMs will be correctly refreshed. The cycle time of RFCK must, therefore, be less than 16  $\mu$ s. RFCK going high sets an internal refresh-request flipflop. First the 74S409 will attempt to perform a hidden refresh so that the system thruput will not be affected. If, during the time RFCK

is high,  $\overline{CS}$  on the 74S409 goes high and  $\overline{RASIN}$  occurs, a hidden refresh will occur. In this case,  $\overline{RASIN}$  should be considered a common read/write strobe. In other words, if the processor is accessing elsewhere (other than the DRAMs) while RFCK is high, the 74S409 will perform a refresh. The refresh counter is enabled to the address outputs whenever  $\overline{CS}$  goes high with RFCK high, and all  $\overline{RAS}$  outputs follow  $\overline{RASIN}$ . If a hidden refresh is taking place as RFCK goes low, the refresh continues. At the start of the hidden refresh, the refresh-request flipflop is reset so on further refresh can occur until the next RFCK period starts with the positive-going edge of RFCK (see Figure 6).  $\overline{RASIN}$  should go low at least 20 ns before RFCK goes low, to ensure occurrence of the hidden refresh.

To determine the probability of a hidden refresh occurring, goes low, (and the internal-request flipflop has not been for  $8\mu s$ , then the system has 20 chances to not select the 74S409. If during this time a hidden refresh did not occur, then the 74S409 forces a refresh while RFCK is low, but the system chooses when the refresh takes place. After RFCK goes low, (and the internal-request flip-flop has not been reset), RF I/O goes low indicating that a refresh is requested to the system. Only when the system acknowledges this request by setting M2 (RFSH) low does the 74S409 initiate a forced refresh (which is performed automatically). Refer to Mode 1, and Figure 6. The internal refresh request flipflop is then reset.

Figure 6 illustrates the refresh alternatives in Mode 5. If a hidden refresh has occurred and CS again goes high before RFCK goes low, the chip is deselected. All the control signals go high-impedance high (logic "1") and the address outputs go three-state until CS again goes low. This mode (combined with Mode 1) allows very fast access, and automatic refreshing (possibly not even slowing down the system), with no extra ICs. Careful system design can, and should, provide a higher probability of hidden refresh occurring. The duty cycle of RFCK need not be 50 percent; in fact, the low-time should be designed to be a minimum. This is determined by the worst-case time (required by the system) to respond to the 74S409's forced-refresh request.

Figure 6. Hidden Refreshing (Mode 5) and Forced Refreshing (Mode 1) Timing

'INDICATES DYNAMIC RAM PARAMETERS

Figure 7. Mode 5 Timing

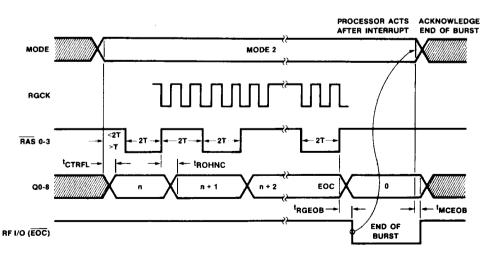

#### Mode 2 — Automatic Burst Refresh

This mode is normally used before and/or after a DMA operation to ensure that all rows remain refreshed, provided the DMA transfer takes less than 2 ms (see Figure 8). When the 74S409 enters this mode, CASIN (RGCK) becomes the RAS Generator Clock (RGCK), and RASIN is disabled. CAS remains high, and RF I/O goes low when the refresh counter has reached the selected End-of-Count and the last RAS has ended. RF I/O then remains low until the Auto-Burst Refresh mode is terminated. RF I/O can therefore be used as an interrupt to indicate the End-of-Burst condition.

The signal on all four  $\overline{RAS}$  outputs is just a divide-by-four of RGCK; in other words, if RGCK has a 100 ns period,  $\overline{RAS}$  is high and low for 200 ns each cycle. The refresh counter increments at the end of each  $\overline{RAS}$ , starting from the count it contained when the mode was entered. If this was zero then for a RGCK with a 100 ns period with End-of Count set to 127, RF I/O will go low after  $128 \times 0.4 \mu s$ , or  $51.2 \mu s$ . During this time, the system may be performing operations that do not involve DRAM. If all rows need to be burst refreshed, the refresh counter may be cleared by setting RF I/O low externally before the burst begins.

Burst-mode refreshing is also useful when powering down systems for long periods of time, but with data retention still required while the DRAMs are in standby. To maintain valid refreshing, power can be applied to the 74S409 (set to Mode 2), causing it to perform a complete burst refresh. When end-of-bust occurs (after  $26~\mu s$ ), power can then be removed from the 74S409 for 2 ms, consuming an average power of 1.3% of normal operating power. No control signal glitches occur when switching power to the 74S409.

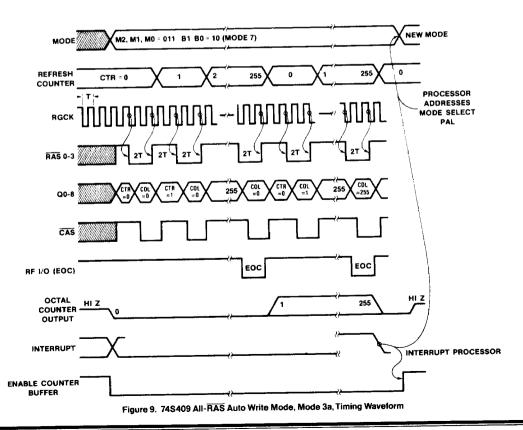

#### Mode 3a - All-RAS Automatic Write

Mode 3a is useful at system initialization, when the memory is being cleared (i.e., with all-zeroes in the data field and the corresponding check bits for error detection and correction). This requires writing the same data to each location of memory (every row of each column of each bank). All RAS outputs are activated, as in refresh, and so are CAS and WE. To write to all four banks simultaneously, every row is strobed in each column, in sequence, until data has been written to all locations. The refresh counter is used to address the rows, and RAS is low for two RGCK cycles and high for two cycles.

Figure 8. Auto-Burst Mode, Mode 2

To select this mode, B1 and B0 must have previously been set to 00, 01, or 10 in Mode 7, depending on the DRAM size. For example, for 16K DRAMs, B1 and B0 are 00. For 64K DRAMs, B1 and B0 are 01.

In this mode, R/ $\overline{C}$  is disabled,  $\overline{WE}$  is permanently enabled low, and  $\overline{CASIN}$  (RGCK) becomes RGCK. RF I/O goes low whenever the refresh counter is 127, 255, or 511 (as set by End-of-Count in Mode 7), and the  $\overline{RAS}$  outputs are active.

74S409 Extra Circuitry Required for All-RAS Auto Write Mode, Mode 3a

# Mode 3b — Externally-Controlled All-RAS Write

To select this mode, B1 and B0 must first have been set to 11 in Mode 7. This mode is useful at system initialization, but under processor control. The memory address is provided by the processor, which also performs the incrementing. All four RAS outputs follow RASIN (supplied by the processor), strobing the row address into the DRAMs. R/C can now go low, while CASIN may be used to control CAS (as in the Externally-Controlled Access mode), so that CAS strobes the column address contents into the DRAMs. At this time WE should be low, causing the data to be written into all four banks of DRAMs. At the end of the write cycle, the input address is incremented and latched by the 74S409 for the next write cycle. This method is slower than Mode 3a, since the processor must perform the incrementing and accessing. Thus the processor is occupied during RAM initialization, and is not free for other initialization operations. However, initialization sequence timing is under system control, which may provide some system advantage.

# Mode 4 — Externally-Controlled Access

Mode 4 is described in with mode 0 in section "Mode 0 and Mode 4."

#### Mode 5 — Automatic Access with Hidden Refresh

See description of mode 0 and mode 5.

#### Mode 6 - Fast Automatic Access

The Fast Automatic Access mode can only be used with fast DRAMs which have transfer of 10 nsec-15nsec. The typical RASIN to CAS delay is 105nsec. In this mode CAS can be extended after RAS goes high to extend the data output alid time. This feature is useful in applications with short cycles where RAS has to be terminated as soon as possible to meet the precharge (transfer of the DRAM.

Mode 6 timing is illustrated in Figures 10 and 11. Provided that the input address is valid as ADS goes low, RASIN can go low any time after ADS. This is because the selected RAS occurs typically 27 ns later, by which time the row address is already valid on the address output of the 74S409. The Address

Set-Up time ( $t_{ASR}$ ), is 0 ns on most DRAMs. The 74S409 in this mode (with ADS and  $\overline{RASIN}$  edges simultaneously applied) produces a minimum  $t_{ASR}$  of 0 ns. This is true provided the input address was valid  $t_{ASA}$  before ADS went low (see Figure 10).

Next, the row address is disabled t<sub>RAH</sub> after RAS goes low (20 ns minimum); the column address is then set up and t<sub>ASC</sub> later, CAS occurs. The only other control input required is WIN. When a write cycle is required, WIN must go low at least 30 ns before CAS is output low.

This gives a total typical delay from: input address valid to RASIN (15 ns); to RAS (27 ns): to rows valid (50 ns); to columns valid (25 ns); to CAS (23 ns) = 140 ns (that is, 125 ns from RASIN). All of these typical figures are for heavy capacitive loading, of approximately 88 DRAMs.

This mode is therefore extremely fast. The external timing is greatly simplified for the memory system designer: the only system signal required is RASIN.

In this mode, the R/C (RFCK) pin is not used, but CASIN (RGCK) is used as CASIN to allow an extended CAS after RAS has already terminated. Refer to Figure 11.

# Mode 7 - Set End-of-Count (3a, 3b select)

The End-of-Count can be externally selected in Mode 7, using ADS to strobe in the respective value of B1 and B0 (see Table 3). With B1 and B0 the same  $\overline{EOC}$  is 127; with B1 = 0 and B0 = 1,  $\overline{EOC}$  is 255; and with B1 = 1 and B0 = 0,  $\overline{EOC}$  is 511. This selected value of  $\overline{EOC}$  will be used until the next Mode 7 selection. At power-up the  $\overline{EOC}$  is automatically set to 127 (B1 and B0 set to 11).

When  $B_1$ ,  $B_2$  are set to 11 in mode 7, mode 3b will be selected if mode 3 is selected ( $M_2$ ,  $M_1$ ,  $M_0=0$ , 1, 1). If  $B_1$ ,  $B_2$  is set to 00, 01 or 10 then mode 3a will be selected.

|    | SELECT<br>D BY ADS) | END OF COUNT |  |  |  |  |  |

|----|---------------------|--------------|--|--|--|--|--|

| B1 | В0                  | 127<br>255   |  |  |  |  |  |

| 0  | 0                   | 127          |  |  |  |  |  |

| 0  | 1                   | 255          |  |  |  |  |  |

| 1  | 0                   | 511          |  |  |  |  |  |

| 1  | 1                   | 127          |  |  |  |  |  |

Table 3. Mode 7

Figure 10. Mode 6 Timing (CASIN High)

Figure 11. Mode 6 Timing, Extended CAS

# SN74S409/-2 Specifications:

# Absolute Maximum Ratings (Note 1)

| Supply voltage V <sub>CC</sub> -0.5 V to 7.0 V |

|------------------------------------------------|

| Storage temperature range65° to +150° C        |

| Input voltage                                  |

| Output current                                 |

| Output current.                                |

| Lead temperature (soldering, 10 seconds)       |

NOTE 1: "Absolute Maximum Ratings" are the values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of operating conditions provides conditions for actual device operation.

# **Operating Conditions**

| SYMBOL             | PARAMETER                            | FIGURE                  | S409<br>MIN TYP | MAX  | MIN  | S409-2<br>TYP | MAX  | UNIT |

|--------------------|--------------------------------------|-------------------------|-----------------|------|------|---------------|------|------|

| VCC                | Supply voltage                       |                         | 4.75            | 5.25 | 4.75 |               | 5.25 | ٧    |

| TA                 | Operating free-air temperature       |                         | 0               | 75   | 0    |               | 75   | °C   |

| †ASA               | Address setup time to ADS            | Figures 4, 5, 7, 10, 11 | 15              |      | 15   |               |      | ns   |

| t <sub>AHA</sub>   | Address hold time from ADS           | Figures 4, 5, 7, 10, 11 | 15              |      | 15   |               |      | ns   |

| t <sub>ADS</sub>   | Address strobe pulse width           | Figures 4, 5, 7, 10, 11 | 30              |      | 30   |               |      | ns   |

| tRASINL.H          | Pulse width of RASIN during refresh  | Figure 3                | 50              |      | 50   |               |      | ns   |

| tRST               | Counter reset pulse width            | Figure 3                | 70              |      | 70   |               |      | ns   |

| tRFCKL,H           | Minimum pulse width of RFCK          | Figure 6                | 100             |      | 100  |               |      | ns   |

| T                  | Period of RAS generator clock        | Figure 6                | 100             |      | 100  |               |      | ns   |

| †RGCKL             | Minimum pulse width low of RGCK      | Figure 6                | 35              |      | 35   |               |      | ns   |

| †RGCKH             | Minimum pulse width high of RGCK     | Figure 6                | 35              |      | 35   |               |      | ns   |

| tCSRL              | CS low to access RASIN low           | See Mode 5 description  | 10              |      | 10   |               |      | ns   |

| <sup>t</sup> RFSRG | RFSH low set-up to RGCK low (Mode 1) | See Mode 1 description  | 35              |      | 35   |               |      | ns   |

| tRQHRF             | RFSH hold time from RFRQ (RF I/O)    | Figure 6                | 2T              |      | 2T   |               |      | ns   |

# **Electrical Characteristics:** V<sub>CC</sub> = 5.0V ± 5.0%, 0°C ≤ T<sub>A</sub> ≤ 75°C Typicals are for V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

| SYMBOL             | PARAMETER                                          | TEST CONDITIONS                                      | MIN | TYP   | MAX  | UNIT |

|--------------------|----------------------------------------------------|------------------------------------------------------|-----|-------|------|------|

| ٧c                 | Input clamp voltage                                | $V_{CC} = MIN, I_C = -12mA$                          |     | -0.8  | -1.2 | ٧    |

| l <sub>l</sub> H1  | Input high current for ADS, R/C only               | V <sub>IN</sub> = 2.5V                               |     | 2.0   | 100  | μА   |

| I <sub>IH2</sub>   | Input high current for other inputs, except RF I/O | V <sub>IN</sub> = 2.5V                               |     | 1.0   | 50   | μΑ   |

| I <sub>I</sub> RSI | Output load current for RF I/O                     | V <sub>IN</sub> = 0.5V, output high                  |     | -1.5  | -2.5 | mAV  |

| I <sub>I</sub> CTL | Output load current for RAS, CAS, WE               | V <sub>IN</sub> = 0.5V, chip deselct                 |     | -1.5  | -2.5 | mA   |

| IIL1               | Input low current for ADS, R/C only                | V <sub>IN</sub> = 0.5V                               |     | -0.1  | -1.0 | mA   |

| 1IL2               | Input low current for other inputs, except RF I/O  | V <sub>IN</sub> = 0.5V                               |     | -0.05 | -0.5 | mA   |

| V <sub>IL</sub> ** | Input low threshold                                |                                                      |     |       | 0.8  | V    |

| VIH**              | Input high threshold                               |                                                      | 2.0 |       |      | V    |

| VOL1               | Output low voltage, except RF I/O                  | IOL = 20mA                                           |     | 0.3   | 0.5  | V    |

| V <sub>OL2</sub>   | Output low voltage for RF I/O                      | IOL = 10mA                                           |     | 0.3   | 0.5  | ٧    |

| VOH1               | Output high voltage, except RF I/O                 | I <sub>OH</sub> = -1mA                               | 2.4 | 3.5   |      | ٧    |

| VOH2               | Output high voltage for RF I/O                     | IOH = -100μA                                         | 2.4 | 3.5   |      | ٧    |

| <sup>I</sup> 1D    | Output high drive current, except RF I/O           | V <sub>OUT</sub> = 0.8V (Note 3)                     |     | -200  |      | mA   |

| lop                | Output low drive current, except RF I/O            | V <sub>OUT</sub> = 2.7V (Note 3)                     |     | 200   |      | mA   |

| loz                | Three-state output current (address outputs)       | 0.4V ≤ V <sub>OUT</sub> ≤ 2.7V,<br>CS = 2.0V, Mode 4 | -50 | 1.0   | 50   | μΑ   |

| Icc                | Supply current                                     | V <sub>CC</sub> = MAX                                |     | 250   | 325  | mA   |

| CIN                | Input capacitance ADS, R/C                         | T <sub>A</sub> = 25°C                                |     | 8     |      | pF   |

| CIN                | Input capacitance all other inputs                 | T <sub>A</sub> = 25°C                                |     | 5     |      | pF   |

<sup>\*\*</sup> These are absolute voltages with respect to pins 13 or 38 on the device and include all overshoots due to system or tester noise. Do not attempt to test these values without suitable equipment.

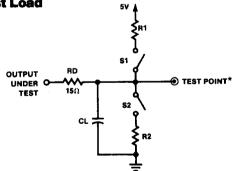

**Switching Characteristics:**  $V_{CC} = 5.0V \pm 5.0\%$ ,  $0^{\circ}C \le T_{A} \le 75^{\circ}C$  See Figure 12 for test load (switches S1 and S2 are closed unless otherwise specified) typicals are for  $V_{CC} = 5V$ ,  $T_{A} = 25^{\circ}C$ .

| SYMBOL            | ACCESS PARAMETER                                         | FIGURE                  | MIN | 'S409<br>TYP | MAX | MIN | 'S409-2<br>TYP | MAX | UNIT |

|-------------------|----------------------------------------------------------|-------------------------|-----|--------------|-----|-----|----------------|-----|------|

| t <sub>RHA</sub>  | Row address held from column select                      | Figure 4                | 10  |              |     | 10  |                |     | ns   |

| †RICL             | RASIN to CAS output delay (Mode 5)                       | Figures 7, 10           | 95  | 125          | 160 | 75  | 100            | 130 | ns   |

| tRICL             | RASIN to CAS output delay (Mode 6)                       | Figures 7, 10, 11       | 80  | 105          | 140 | 65  | 90             | 115 | ns   |

| †RICH             | RASIN to CAS output delay (Mode 5)                       | Figures 7, 10           | 50  | 63           | 80  | 50  | 63             | 80  | ns   |

| tRICH             | RASIN to CAS output delay (Mode 6)                       | Figures 7, 10, 11       | 40  | 48           | 60  | 40  | 48             | 60  | ns   |

| tRCDL             | RAS to CAS output delay (Mode 5)                         | Figures 7, 10           |     | 98           | 125 |     | 75             | 100 | ns   |

| tRCDL             | RAS to CAS output delay (Mode 6)                         | Figures 7, 10, 11       |     | 78           | 105 |     | 65             | 85  | ns   |

| tRCDH             | RAS to CAS output delay (Mode 5)                         | Figures 7, 10           |     | 27           | 40  |     | 27             | 40  | ns   |

| <sup>t</sup> RCDH | RAS to CAS output delay (Mode 6)                         | Figures 7, 10           |     | 40           | 65  |     | 40             | 65  | ns   |

| <sup>t</sup> CCDH | CASIN to CAS output delay Mode 6)                        | Figure 11               | 40  | 54           | 70  | 40  | 54             | 70  | ns   |

| tRCV              | RASIN to column address valid (Mode 5)                   | Figures 7, 10           |     | 90           | 120 |     | 80             | 105 | ns   |

| tRCV              | RASIN to column address valid (Mode 6)                   | Figures 7, 10, 11       |     | 75           | 105 |     | 70             | 90  | ns   |

| †RPDL             | RASIN to RAS delay                                       | Figures 4, 5, 7, 10, 11 | 20  | 27           | 35  | 20  | 27             | 35  | ns   |

| tRPDH             | RASIN to RAS delay                                       | Figures 4, 5, 7, 10, 11 | 15  | 23           | 32  | 15  | 23             | 32  | ns   |

| †APDL             | Address input to output low delay                        | Figures 4, 5, 7, 10, 11 |     | 25           | 40  |     | 25             | 40  | ns   |

| <sup>†</sup> APDH | Address input to output high delay                       | Figures 4, 5, 7, 10, 11 |     | 25           | 40  |     | 25             | 40  | ns   |

| †SPDL             | Address strobe to address output low                     | Figures 4, 5            |     | 40           | 60  |     | 40             | 60  | ns   |

| tSPDH             | Address strobe to address output high                    | Figures 4, 5            |     | 40           | 60  | l   | 40             | 60  | ns   |

| tWPDL             | WIN to WE output delay                                   | Figure 5                | 15  | 25           | 30  | 15  | 25             | 30  | ns   |

| tWPDH             | WIN to WE output delay                                   | Figure 5                | 15  | 30           | 60  | 15  | 30             | 60  | ns   |

| tcrs              | CASIN setup time to RASIN high (Mode 6)                  | Figure 11               | 35  |              |     | 35  |                |     | ns   |

| tCPDL             | CASIN to CAS delay (R/C low in Mode 4)                   | Figure 5                | 32  | 41           | 58  | 32  | 41             | 58  | ns   |

| tCPDH             | CASIN to CAS delay                                       | Figure 5                | 25  | 39           | 50  | 25  | 39             | 50  | ns   |

| tRCC              | Column select to column address valid                    | Figure 4                |     | 40           | 58  |     | 40             | 58  | ns   |

| tRCR              | Row select to row address valid                          | Figures 4, 5            |     | 40           | 58  |     | 40             | 58  | ns   |

| <sup>t</sup> RAH  | Row address hold time (Mode 5)                           | Figures 7, 10           | 30  |              |     | 20  |                |     | ns   |

| tRAH              | Row address hold time (Mode 6)                           | Figures 7, 10, 11       | 20  |              |     | 12  |                |     | ns   |

| tASC              | Column address setup time (Mode 5)                       | Figures 7, 10           | 8   |              |     | 3   |                |     | ns   |

| tASC              | Column address setup time (Mode 6)                       | Figures 7, 10, 11       | 6   |              |     | 3   |                |     | ns   |

| <sup>t</sup> DiF1 | Maximum (trpDL - trhA) (Mode 4)                          |                         |     |              | 15  | ļ   |                | 15  | ns   |

| tDiF2             | Maximum (t <sub>RCC</sub> - t <sub>CPDL</sub> ) (Mode 4) |                         | 1   |              | 15  |     |                | 15  | ns   |

| SYMBOL             | REFRESH PARAMETER                               | TEST CONDITIONS                  | MIN | 'S409<br>TYP | MAX | MIN | 'S409-2<br>TYP | MAX | UNIT |

|--------------------|-------------------------------------------------|----------------------------------|-----|--------------|-----|-----|----------------|-----|------|

| tFRQL              | RFCK low to forced RFRQ low                     | C <sub>L</sub> = 50 pF, Figure 6 |     | 20           | 30  |     | 20             | 30  | ns   |

| tFRQH              | RGCK low to force RFRQ high                     | C <sub>L</sub> = 50pF, Figure 6  |     | 50           | 75  |     | 50             | 75  | ns   |

| tRGRL              | RGCK low to RAS low                             | Figure 6                         | 50  | 65           | 95  | 50  | 65             | 95  | ns   |

| tRGRH              | RGCK low to RAS high                            | Figure 6                         | 40  | 60           | 85  | 40  | 60             | 85  | ns   |

| tRFRH              | RFSH high to RAS high<br>(encoding forced RFSH) | See Mode 1<br>description        | 55  | 80           | 110 | 55  | 80             | 110 | ns   |

| tcsct              | CS high to RFSH counter valid                   | Figure 6                         |     | 55           | 70  |     | 55             | 70  | ns   |

| <sup>t</sup> CTL   | RF I/O low to counter outputs all low           | Figure 3                         |     |              | 100 |     |                | 100 | ns   |

| †RFPDL             | RASIN to RAS delay during refresh               | Figures 3, 6                     | 35  | 50           | 70  | 35  | 50             | 70  | ns   |

| <sup>t</sup> RFPDH | RASIN to RAS delay during refresh               | Figures 3, 6                     | 30  | 40           | 55  | 30  | 40             | 55  | ns   |

| †RFLCT             | RFSH low to counter address valid               | CS = X, Figures 3, 6, 8          |     | 47           | 60  |     | 47             | 60  | ns   |

| tREHRV             | RFSH high to row address valid                  | Figures 3, 6                     |     | 45           | 60  |     | 45             | 60  | ns   |

| †ROHNC             | RAS high to new count valid                     | Figures 3, 8                     |     | 30           | 55  |     | 30             | 55  | ns   |

| tRLEOC             | RASIN low to end-of-count low                   | C <sub>L</sub> = 50pF, Figure 3  |     |              | 80  |     |                | 80  | ns   |

| †RHEOC             | RASIN high to end-of-count high                 | C <sub>L</sub> = 50pF, Figure 3  |     |              | 80  |     |                | 80  | ns   |

| tRGEOB             | RGCK low to end-of-burst low                    | C <sub>L</sub> = 50pF, Figure 8  |     |              | 95  |     |                | 95  | ns   |

| tMCEOB             | Mode change to end-of-burst high                | C <sub>L</sub> = 50pF, Figure 8  |     |              | 75  |     | -              | 75  | กร   |

# Switching Characteristics: (Cont'd)

| SYMBOL          | ACCESS PARAMETER                                                 | TEST CONDITIONS                                         | MIN | S409<br>TYP | MAX | MIN | '\$409-2<br>TYP | MAX | UNIT |

|-----------------|------------------------------------------------------------------|---------------------------------------------------------|-----|-------------|-----|-----|-----------------|-----|------|

|                 | THREE-STATE PARAMETER                                            |                                                         |     |             |     |     |                 |     |      |

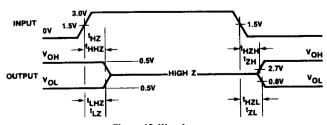

| tzH             | CS low to address output high from Hi                            | Figures 6, 12<br>R1 = 3.5k, R2 = 1.5k                   |     | 35          | 60  |     | 35              | 60  | ns   |

| tHZ             | CS high to address output Hi-Z from high                         | C <sub>L</sub> = 15pF, Figures 6,12<br>R2 = 1k, S1 Open |     | 20          | 40  |     | 20              | 40  | ns   |

| tZL             | CS low to address output low from Hi-Z                           | Figures 6, 12<br>R1 = 3.5k, R2 = 1.5k                   |     | 35          | 60  |     | 35              | 60  | ns   |

| t <sub>LZ</sub> | CS high to address output Hi-Z from low                          | C <sub>L</sub> = 15pF, Figures 6,13<br>R1 = 1k, S2 Open |     | 25          | 50  |     | 25              | 50  | ns   |

| tHZH            | CS low to control output (WE, CAS, (RASO-3) high from Hi-Z high  | Figures 6,12<br>R2 = 750Ω, S1 open                      |     | 50          | 80  |     | 50              | 80  | ns   |

| tHHZ            | CS high to control output (WE, CAS, (RASO-3) Hi-Z high from high | $C_L = 15pF$<br>R2 = 750 $\Omega$ , S1 open             |     | 40          | 75  | -   | 40              | 75  | ns   |

| tHZL            | CS low to control output (WE, CAS, (RASO-3) low from Hi-Z high   | Figure 12<br>S1, S2 Open                                |     | 45          | 75  |     | 45              | 75  | ns   |

| tLHZ            | CS high to control output (WE, CAS, (RASO-3) Hi-Z high from low  | C <sub>L</sub> = 15pF, Figure 12<br>R2 = 750Ω, S1 open  |     | 50          | 80  |     | 50              | 80  | ns   |

\*Internally the device contains a 3K resistor in series with a Schottky Diode to VCC

Note 1: Output load capacitance is typical for 4 banks of 22 DRAMs or 88 DRAMs including trace capacitance. These values are: Q0-Q8.  $C_L=500 pF;$  RAS0-RAS3,  $C_L=150 pF;$  CAS  $C_L=600 pF$  unless otherwise noted.

Note 2: All typical values are for  $T_A = 25^{\circ}C$  and  $V_{CC} = 5.0V$ .

Note 3: This test is provided as a monitor of Driver output source and sink current capability. Caution should be exercised in testing this parameter. In testing these parameters, a 15Ω resistor should be placed in series with each output under test. One output should be tested at a time and test time should not exceed 1 second.

Note 4: Input pulse 0V to 3.0V,  $t_R=t_F=2.5$  ns, f=2.5 MHz.  $t_{PW}=200$  ns. Input reference point on AC measurements is 1.5V. Output reference points are 2.7V for High and 0.8V for Low

R1, R2 = 4.7K EXCEPT AS SPECIFIED.

\* The "TEST POINT" is driven by the output under test, and observed by instrumentation.

Figure 12. Waveform

Figure 13. Change in Propagation Delay vs Loading

Capacitance Relative to a 500 pF Load

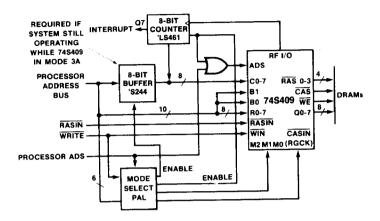

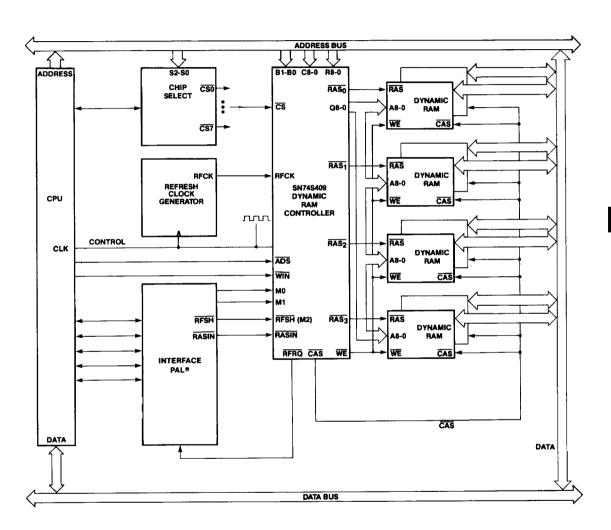

## **Applications**

The 74S409 Dynamic RAM Controller provides all the address and control signals necessary to access and refresh dynamic RAMs. Since the 74S409 is not compatible with a specific bus or microprocessor, an interface is often necessary between the 74S409 and the system. A general application using PAL to implement the interface and two additional

chips to provide refresh clock and chip select is shown in Figure 14.

The 74S409 operating modes may vary from application to application. For efficient refresh it is recommended to use mode 1 and mode 5 to take advantage of the hidden (transparent) refresh with forced refresh backup.

Figure 14. 74S409 in General Application