# SCAN182374A Serially Controlled Access Network D Flip-Flop with 25 $\Omega$ Series Resistor Outputs

# **General Description**

The SCAN182374A is a high performance BiCMOS D-type flip-flop featuring separate D-type inputs organized into dual 9-bit bytes with byte-oriented clock and output enable control signals. This device is compilant with IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture with the incorporation of the defined boundary-scan test logic and test access port consisting of Test Data Input (TDI), Test Data Out (TDO), Test Mode Select (TMS), and Test Clock (TCK).

# **Features**

- High performance BiCMOS technology

- lacksquare 25 $\Omega$  series resistor outputs eliminate need for external terminating resistors

- Buffered positive edge-triggered clock

- TRI-STATE® outputs for bus-oriented applications

- 25 mil pitch SSOP (Shrink Small Outline Package)

- IEEE 1149.1 (JTAG) Compliant

- Includes CLAMP, IDCODE and HIGHZ instructions

- Additional instructions SAMPLE-IN, SAMPLE-OUT and EXTEST-OUT

- Power up TRI-STATE for hot insert

- Member of National's SCAN Products

Ordering Code: See Section 10

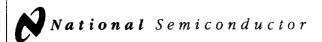

# **Connection Diagram**

| Pin Names                                 | Description        |

|-------------------------------------------|--------------------|

| Al <sub>(0-8)</sub> , Bl <sub>(0-8)</sub> | Data inputs        |

| ACP, BCP                                  | Clock Pulse Inputs |

| AOE <sub>1</sub> , BOE <sub>1</sub>       | TRI-STATE Output   |

|                                           | Enable inputs      |

| AO <sub>(0-8)</sub> , BO <sub>(0-8)</sub> | TRI-STATE Outputs  |

| Order Number    | Description           |

|-----------------|-----------------------|

| SCAN182374ASSC  | SSOP in Tubes         |

| SCAN182374ASSCX | SSOP in Tape and Reel |

| SCAN182374AFMQB | Military Flatpak      |

TL/F/11545-1

# 7

# **Truth Tables**

|     | Inputs            |         | AO <sub>(0-8)</sub> |

|-----|-------------------|---------|---------------------|

| ACP | †AOE <sub>1</sub> | Ai(0-8) | 70(0-8)             |

| X   | Н                 | X       | z                   |

| /   | L                 | Ł       | L                   |

|     | L                 | н       | Н                   |

|     | Inputs |                     | BO <sub>(0-8)</sub> |

|-----|--------|---------------------|---------------------|

| ВСР | †BOE 1 | BI <sub>(0-8)</sub> | 20(0-8)             |

| Х   | Н      | Х                   | Z                   |

| ~   | L      | L '                 | L                   |

| _   | L      | I                   | Η                   |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

✓ = L-to-H Transition

= Inactive-to-active transition must occur to enable outputs upon power-up.

# **Logic Diagram**

**Functional Description**

the flip-flops.

The SCAN182374A consists of two sets of nine edge-triggered flip-flops with individual D-type inputs and TRI-STATE true outputs. The buffered clock and buffered Output Enable pins are common to all flip-flops. Each set of the nine flip-flops will store the state of their individual D inputs that meet the setup and hold time requirements on the LOW-to-HIGH Clock (ACP or BCP) transition. With the Output Enable (AOE $_1$  or BOE $_1$ ) LOW, the contents of the nine flip-flops are available at the outputs. When the Output Enable is HIGH, the outputs go to the high impedance state. Operation of the Output Enable input does not affect the state of

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

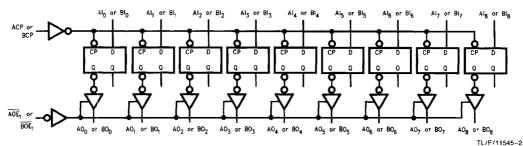

# **Block Diagrams**

Note: BSR stands for Boundary Scan Register

# Block Diagrams (Continued)

# Tap Controller To BSR [4+] FROM BSP [0] FROM BSP [0] FROM BSP [0] TO BSR [4+] FROM BSP [0] FR

TL/F/11545-4

TL/F/11545-5

Byte-B

TYPE1

BSR

18-26

NON-INVERTING

FLIP-FLOP

NON-INVERTING

BSP

0-8

BOE

TYPE1

INSTRUCTION TRI-STATE

BOE

37

TYPE1

BSR

36

BSR

36

Note: BSR stands for BOUNDARY-SCAN Register

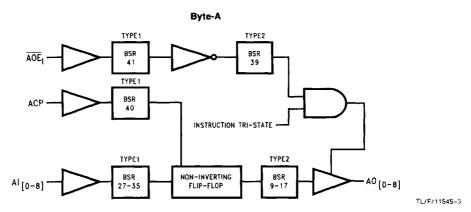

# SCAN-ABT Live Insertion and Power Cycling Characteristics

SCAN-ABT is intended to serve in Live Insertion backplane applications. It provides 2nd Level Isolation¹ which indicates that while external circuitry to control the output enable pin is unnecessary, there may be a need to implement differential length backplane connector pins for V<sub>CC</sub> and GND. As well, pre-bias circuitry for backplane pins may be necessary to avoid capacitive loading effects during live insertion.

SCAN-ABT provides control of output enable pins during power cycling via the circuit in *Figure A*. It essentially controls the  $\overline{G_n}$  pin until  $V_{CC}$  reaches a known level.

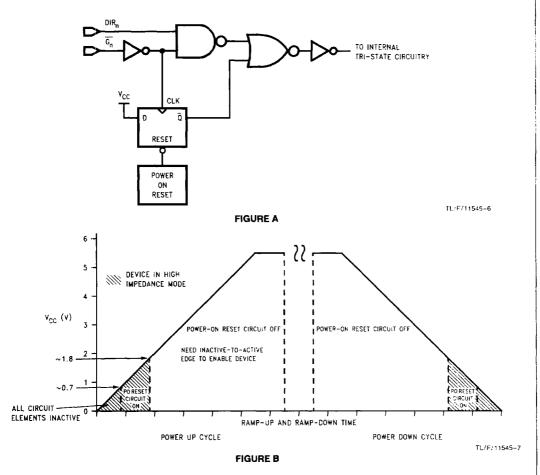

During power-up, when  $V_{CC}$  ramps through the 0.0V to 0.7V range, all internal device circuitry is inactive, leaving output and I/O pins of the device in high impedance. From approximately 0.8V to 1.8V  $V_{CC}$ , the Power-On-Reset circuitry, (POR), in Figure A becomes active and maintains device high impedance mode. The POR does this by providing a low from its output that resets the flip-flop The output,  $\overline{Q}$ , of the flip-flop then goes high and disables the NOR gate from an incidental low input on the  $\overline{Q}_{n}$  pin. After 1.8V  $V_{CC}$ , the POR circuitry becomes inactive and ceases to control the

flip-flop. To bring the device out of high impedance, the  $\overline{G_n}$  input must receive an inactive-to-active transition, a high-to-low transition on  $\overline{G_n}$  in this case to change the state of the flip-flop. With a low on the  $\overline{Q}$  output of the flip-flop, the NOR gate is free to allow propagation of a  $\overline{G_n}$  signal.

During power-down, the Power-On-Reset circuitry will become active and reset the flip-flop at approximately 1.8V V<sub>CC</sub>. Again, the  $\overline{Q}$  output of the flip-flop returns to a high and disables the NOR gate from inputs from the  $\overline{G}_n$  pin. The device will then remain in high impedance for the remaining ramp down from 1.8V to 0.0V V<sub>CC</sub>.

Some suggestions to help the designer with live insertion issues:

- The Gn pin can float during power-up until the Power-On-Reset circuitry becomes inactive.

- The Gn pin can float on power-down only after the Power-On-Reset has become active.

The description of the functionality of the Power-On-Reset circuitry can best be described in the diagram of Figure B.

<sup>1</sup>Advanced BiCMOS Logic Databook, National Semiconductor, 1994 Edition, p. 4-3.

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Storage Temperature  $-65^{\circ}\text{C to} + 150^{\circ}\text{C}$ Ambient Temperature under Bias  $-55^{\circ}\text{C to} + 125^{\circ}\text{C}$

Junction Temperature under Bias

Ceramic

- 55°C to + 175°C

Plastic

- 55°C to + 150°C

V<sub>CC</sub> Pin Potential to Ground Pin

Input Voltage (Note 2) -0.5V to +7.0V

Input Current (Note 2) -30 mA to +5.0 mA

-0.5V to  $\pm 7.0V$

Voltage Applied to Any Output

in the Disabled or

Current Applied to Output

in LOW State (Max) Twice the Rated I<sub>OL</sub> (mA)

DC Latchup Source Current

Commercial -500 mA Military -300 mA

Over Voltage Latchup (I/O) 10V

ESD (HBM) Min. 2000V

Note 1: Absolute maximum ratings are values beyond which the device may

Note: 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

# Recommended Operating Conditions

Free Air Ambient Temperature

Military

−55°C to +125°C

Commercial

−40°C to +85°C

Supply Voltage

Military + 4.5V to + 5.5V Commercial + 4.5V to + 5.5V

Minimum Input Edge Rate $(\Delta V/\Delta t)$ Data Input50 mV/nsEnable Input20 mV/ns

# **DC Electrical Characteristics**

| Symbol                             | Paramete                                  | -                   | Vcc | Min  | Тур | Max  | Units | Conditions                                          |

|------------------------------------|-------------------------------------------|---------------------|-----|------|-----|------|-------|-----------------------------------------------------|

| VIH                                | Input HIGH Voltage                        |                     |     | 2.0  |     |      | V     | Recognized HIGH Signal                              |

| VIL                                | Input LOW Voltage                         |                     |     |      |     | 0.8  | V     | Recognized LOW Signal                               |

| V <sub>CD</sub>                    | Input Clamp Diode Volt                    | age                 | Min |      |     | 1.2  | V     | I <sub>IN</sub> = -18 mA                            |

| V <sub>OH</sub>                    | Output HIGH Voltage                       |                     | Min | 2.5  |     |      | V     | I <sub>OH</sub> = -3 mA                             |

|                                    |                                           | Mil                 | Min | 2.0  |     |      |       | I <sub>OH</sub> = -24 mA                            |

|                                    |                                           | Comm                | Min | 2.0  |     |      | V     | I <sub>OH</sub> = -32 mA                            |

| VOL                                | Output LOW Voltage                        |                     |     |      |     |      |       |                                                     |

|                                    |                                           | Mil                 | Min | ļ    |     | 0.8  | V     | I <sub>OL</sub> = 12 mA                             |

|                                    |                                           | Comm                | Min |      |     | 0.8  | V     | I <sub>OL</sub> = 15 mA                             |

| 1 <sub>IH</sub>                    | Input HIGH Current                        | All Others          | Max |      |     | 5    | μА    | V <sub>IN</sub> = 2.7V (Note 1)                     |

|                                    |                                           | All Others          | Max |      |     | 5    | μА    | V <sub>IN</sub> = V <sub>CC</sub>                   |

|                                    |                                           | TMS, TDI            | Max |      |     | 5    | μА    | $V_{1N} = V_{CC}$                                   |

| I <sub>BVI</sub>                   | Input HIGH Current<br>Breakdown Test      |                     | Max |      |     | 7    | μΑ    | V <sub>IN</sub> = 7.0V                              |

| I <sub>BVIT</sub>                  | Input HIGH Current<br>Breakdown Test(I/O) | altro y communicati | Max |      |     | 100  | μА    | V <sub>IN</sub> = 5.5V                              |

| !IL                                | Input LOW Current                         | 40.00               | Max |      |     | -5   | μА    | V <sub>IN</sub> = 0.5V (Note 1)                     |

|                                    |                                           | All Others          | Max |      |     | 5    | μΑ    | V <sub>IN</sub> = 0.0V                              |

|                                    |                                           | TMS, TDI            | Max |      |     | -385 | μΑ    | V <sub>IN</sub> = 0.0V                              |

| V <sub>ID</sub>                    | Input Leakage Test                        | The second          | 0.0 | 4.75 | _   |      | V     | I <sub>ID</sub> = 1.9 μA<br>All Other Pins Grounded |

| I <sub>iH</sub> + I <sub>OZH</sub> | Output Leakage Currer                     | it                  | Max |      | _   | 50   | μΑ    | V <sub>OUT</sub> = 2.7V                             |

| I <sub>IL</sub> - I <sub>OZL</sub> | Output Leakage Currer                     | t                   | Max | !    |     | -50  | μΑ    | V <sub>OUT</sub> = 0.5V                             |

| lozh                               | Output Leakage Currer                     | nt .                | Мах |      |     | 50   | μА    | V <sub>OUT</sub> = 2.7V                             |

| lozL                               | Output Leakage Currer                     | it                  | Max |      |     | -50  | μА    | V <sub>OUT</sub> = 0.5V                             |

Note 1: Guaranteed not tested.

# DC Electrical Characteristics (Continued)

| Symbol | Parameter                                          | Vcc | Min  | Тур | Max  | Units      | Conditions                                         |

|--------|----------------------------------------------------|-----|------|-----|------|------------|----------------------------------------------------|

| los    | Output Short-Circuit Current                       | Max | -100 |     | ~275 | mA         | V <sub>OUT</sub> = 0.0V                            |

| ICEX   | Output High Leakage Current                        | Max |      |     | 50   | μА         | $V_{OUT} = V_{CC}$                                 |

| IZZ    | Bus Drainage Test                                  | 0.0 |      |     | 100  | μА         | V <sub>OUT</sub> = 5.5V<br>All Others Grounded     |

| Іссн   | Power Supply Current                               | Max |      |     | 250  | μА         | $V_{OUT} = V_{CC}$ ; TDI, TMS = $V_{CC}$           |

|        |                                                    | Max |      |     | 1.0  | mA         | $V_{OUT} = V_{CC}$ ; TDI, TMS = GND                |

| ICCL   | Power Supply Current                               | Max |      |     | 60   | mA         | V <sub>OUT</sub> ≈ LOW; TDI, TMS = V <sub>CC</sub> |

|        |                                                    | Max |      |     | 60.8 | mA         | V <sub>OUT</sub> = LOW; TDI, TMS = GND             |

| lccz   | Power Supply Current                               | Max |      |     | 250  | μΑ         | TDI, TMS = V <sub>CC</sub>                         |

|        |                                                    | Max |      |     | 1.0  | mA         | TDI, TMS == GND                                    |

| ICCT   | Additional I <sub>CC</sub> /Input All Other Inputs | Max |      |     | 2.9  | mA         | $V_{IN} = V_{CC} - 2.1V$                           |

|        | TDI, TMS Inputs                                    | Max |      |     | 3    | mA         | $V_{IN} = V_{CC} - 2.1V$                           |

| ICCD   | Dynamic I <sub>CC</sub> No Load                    | Max |      |     | 0.2  | mA/<br>MHz | Outputs Open<br>One Bit Toggling, 50% Duty Cycle   |

# AC Electrical Characteristics Normal Operation

|                                      |                              |                          |       | Military                                                    |     | l          | Commercial                          | ·          |       |             |

|--------------------------------------|------------------------------|--------------------------|-------|-------------------------------------------------------------|-----|------------|-------------------------------------|------------|-------|-------------|

| Symbol                               | Parameter                    | V <sub>CC</sub> *<br>(V) | • • • | T <sub>A</sub> = -55°C to + 125°C<br>C <sub>L</sub> = 50 pF |     |            | 40°C to +<br>C <sub>L</sub> = 50 pF |            | Units | Fig.<br>No. |

|                                      |                              |                          | Min   | Тур                                                         | Max | Min        | Тур                                 | Max        | ]     |             |

| t <sub>PLH</sub>                     | Propagation Delay<br>CP to Q | 5.0                      |       |                                                             |     | 1.4<br>2.1 | 4.6<br>4.9                          | 6.1<br>6.8 | ns    | 1, 2        |

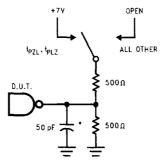

| t <sub>PLZ</sub>                     | Disable Time                 | 5.0                      |       |                                                             |     | 1.9<br>1.8 | 4.6<br>4.8                          | 8.0<br>8.7 | ns    | 3, 4        |

| t <sub>PZL</sub><br>t <sub>PZH</sub> | Enable Time                  | 5.0                      |       |                                                             |     | 2.0<br>1.4 | 6.7<br>6.0                          | 9.4<br>8.2 | ns    | 3, 4        |

<sup>\*</sup>Voltage Range 5.0V ±0.5V

# AC Operating Requirements Normal Operation

|                  |                                    |                          | Military                                                                    | Commercial                                                                 |       |             |

|------------------|------------------------------------|--------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|-------|-------------|

| Symbol           | Parameter                          | V <sub>CC</sub> *<br>(V) | $T_A = -55^{\circ}\text{C to } + 125^{\circ}\text{C}$ $C_L = 50 \text{ pF}$ | $T_A = -40^{\circ}\text{C to } + 85^{\circ}\text{C}$ $C_L = 50 \text{ pF}$ | Units | Fig.<br>No. |

|                  |                                    |                          | Guarantee                                                                   | d Minimum                                                                  |       |             |

| ts               | Setup Time, H or L<br>Data to CP   | 5.0                      |                                                                             | 2.8                                                                        | ns    | 5           |

| t <sub>H</sub>   | Hold Time, H or L<br>CP to Data    | 5.0                      |                                                                             | 2.4                                                                        | ns    | 5           |

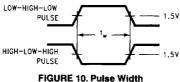

| t <sub>W</sub>   | CP Pulse Width                     | 5.0                      |                                                                             | 0.0                                                                        | ns    | 10          |

| f <sub>max</sub> | Maximum ACP/BCP<br>Clock Frequency | 5.0                      |                                                                             | 50                                                                         | MHz   |             |

<sup>\*</sup>Voltage Range 5.0 is 5.0V ±0.5V.

# AC Electrical Characteristics Scan Test Operation

|                                      |                                                                          |                          |                  | Military  |     |            | Commercia                            | ı            |       |           |

|--------------------------------------|--------------------------------------------------------------------------|--------------------------|------------------|-----------|-----|------------|--------------------------------------|--------------|-------|-----------|

| Symbol                               | Parameter                                                                | V <sub>CC</sub> *<br>(V) | T <sub>A</sub> = | 55°C to + |     |            | -40°C to -<br>C <sub>L</sub> = 50 pF |              | Units | Fig<br>No |

|                                      |                                                                          |                          | Min              | Тур       | Max | Min        | Тур                                  | Max          |       |           |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>TCK to TDO                                          | 5.0                      |                  |           |     | 2.9<br>4.0 | 5.8<br>7.3                           | 9.5<br>11.5  | ns    | 6         |

| t <sub>PLZ</sub><br>t <sub>PHZ</sub> | Disable Time<br>1 CK to TDO                                              | 5.0                      |                  |           |     | 1.9<br>3.0 | 5.6<br>7.1                           | 10.0<br>12.1 | ns    | 7, E      |

| t <sub>PZL</sub><br>t <sub>PZH</sub> | Enable Time<br>TCK to TDO                                                | 5.0                      |                  |           |     | 4.4<br>2.7 | 8.4<br>6.4                           | 13.2<br>10.9 | ns    | 7, 8      |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Fropagation Delay<br>TCK to Data Out<br>during Update-DR State           | 5.0                      |                  |           |     | 3.4<br>4.3 | 6.5<br>8.1                           | 10.5<br>12.7 | ns    | 6         |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>TCK to Data Out<br>during Update-IR State           | 5.0                      |                  |           |     | 3.9<br>4.7 | 7.8<br>9.1                           | 12.8<br>14.5 | ns    | 6         |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay<br>TCK to Data Out<br>during Test Logic<br>Reset State | 5.0                      |                  |           |     | 4.7<br>5.6 | 9.5<br>10.9                          | 15.6<br>17.4 | ns    | 6         |

| t <sub>PLZ</sub><br>t <sub>PHZ</sub> | Disable Time<br>TCK to Data Out<br>during Update-DR State                | 5.0                      |                  |           |     | 3.2<br>3.9 | 7.8<br>8.5                           | 13.6<br>14.2 | ns    | 7, 8      |

| t <sub>PLZ</sub><br>t <sub>PHZ</sub> | Disable Time<br>TCK to Data Out<br>during Update-IR State                | 5.0                      |                  |           |     | 3.2<br>3.8 | 8.6<br>9.3                           | 15.0<br>15.6 | ns    | 7, 8      |

| t <sub>PLZ</sub><br>t <sub>PHZ</sub> | Disable Time<br>TCK to Data Out<br>during Test Logic<br>Reset State      | 5.0                      |                  |           |     | 4.2<br>5.0 | 10.2<br>11.0                         | 18.0<br>18.5 | ns    | 7, 8      |

| t <sub>PZL</sub><br>t <sub>PZH</sub> | Enable Time<br>TCK to Data Out<br>during Update-DR State                 | 5.0                      |                  |           |     | 5.0<br>3.7 | 9.6<br>7.7                           | 15.3<br>13.0 | ns    | 7, 8      |

| t <sub>PZL</sub><br>t <sub>PZH</sub> | Enable Time<br>TCK to Data Out<br>during Update-IR State                 | 5.0                      |                  |           |     | 5.3<br>4.0 | 10.8<br>9.0                          | 17.4<br>15.1 | ns    | 7, 8      |

| t <sub>PZL</sub><br>t <sub>PZH</sub> | Enable Time TCK to Data Out during Test Logic Reset State                | 5.0                      |                  |           |     | 6.2<br>4.7 | 12.6<br>10.7                         | 20.4<br>18.1 | ns    | 7, 8      |

<sup>\*</sup>Voltage Range 5.6V - 0.5V

# AC Operating Requirements Scan Test Operation

|                  |                                                                           |                          | Military                                                    | Commercial                                                                |       |             |

|------------------|---------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|-------|-------------|

| Symbol           | Parameter                                                                 | V <sub>CC</sub> *<br>(V) | T <sub>A</sub> = -55°C to + 125°C<br>C <sub>L</sub> = 50 pF | $T_A = -40^{\circ}\text{C to} + 85^{\circ}\text{C}$ $C_L = 50 \text{ pF}$ | Units | Fig.<br>No. |

|                  |                                                                           |                          | Guarantee                                                   | d Minimum                                                                 | 1     |             |

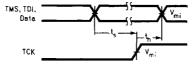

| ts               | Setup Time<br>Data to TCK (Note 2)                                        | 5.0                      |                                                             | 2.7                                                                       | ns    | 9           |

| t <sub>H</sub>   | Hold Time<br>Data to TCK (Note 2)                                         | 5.0                      |                                                             | 3.1                                                                       | ns    | 9           |

| ts               | Setup Time, H or L<br>AOE <sub>1</sub> , BOE <sub>1</sub> to TCK (Note 1) | 5.0                      |                                                             | 5.0                                                                       | ns    | 9           |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to AOE <sub>1</sub> , BOE <sub>1</sub> (Note 1)  | 5.0                      |                                                             | 1.8                                                                       | ns    | 9           |

| ts               | Setup Time, H or L<br>Internal AOE, BOE to TCK (Note 3)                   | 5.0                      |                                                             | 3.6                                                                       | ns    | 9           |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to Internal AOE, BOE (Note 3)                    | 5.0                      |                                                             | 2.1                                                                       | ns    | 9           |

| ts               | Setup Time<br>ACP, BCP (Note 4) to TCK                                    | 5.0                      |                                                             | 3.4                                                                       | ns    | 9           |

| t <sub>H</sub>   | Hold Time<br>TCK to ACP, EICP (Note 4)                                    | 5.0                      |                                                             | 1.8                                                                       | ns    | 9           |

| ts               | Setup Time, H or L<br>TMS to TCK                                          | 5.0                      |                                                             | 8.7                                                                       | ns    | 9           |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to TMS                                           | 5.0                      |                                                             | 1.8                                                                       | ns    | 9           |

| ts               | Setup Time, H or L<br>TDI to TCK                                          | 5.0                      |                                                             | 6.4                                                                       | ns    | 9           |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to TDI                                           | 5.0                      |                                                             | 3.2                                                                       | ns    | 9           |

| t <sub>W</sub>   | Pulse Width TCK H                                                         | 5.0                      |                                                             | 8.2<br>11.2                                                               | ns    | 10          |

| f <sub>max</sub> | Maximum TCK<br>Clock Frequency                                            | 5.0                      |                                                             | 50                                                                        | MHz   |             |

| t <sub>PU</sub>  | Wait Time, Power Up to TCK                                                | 5.0                      |                                                             | 100                                                                       | ns    |             |

| t <sub>DN</sub>  | Power Down Delay                                                          | 0.0                      |                                                             | 100                                                                       | ms    |             |

<sup>\*</sup>Voltage Range 5.0V ±0.5V

All Input Timing Delays involving TCK are measured from the rising edge of TCK

Note 1: Timing pertains to BSR 38 and 41 only.

Note 2: This delay represents the timing relationship between the data input and TCK at the associated scan cells numbered 0-8, 9-17, 18-26 and 27-35.

Note 3: This delay represents the timing relationship between AOE/BOE and TCK for scan cells 36 and 39 only.

Note 4: Timing pertains to BSR 37 and 40 only.

# Capacitance TA = 25°C

| Symbol                    | Parameter          | Тур  | Units | Conditions             |

|---------------------------|--------------------|------|-------|------------------------|

| C <sub>IN</sub>           | Input Capacitance  | 5.8  | pF    | $V_{CC} = 0.0V$        |

| C <sub>OUT</sub> (Note 1) | Output Capacitance | 13.8 | pF    | V <sub>CC</sub> = 5.0V |

Note 1:  $C_{OUT}$  is measured at frequency f = 1 MHz, per MIL-STD-883B, Method 3012.

# Waveforms

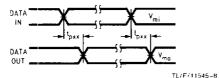

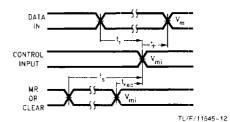

FIGURE 1. Waveform for Inverting and Non-Inverting Functions

FIGURE 2. Propagation Delay, Pulse Width and t<sub>rec</sub> Waveforms

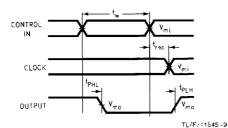

FIGURE 3. TRI-STATE Output High Enable and Disable Times

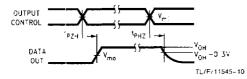

FIGURE 4. TRI-STATE Output Low Enable and Disable Times

FIGURE 5. Setup Time, Hold Time and Recovery Time

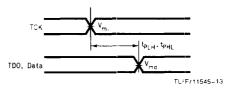

FIGURE 6. Propagation Delay

$V_{mi} = 1.5V$  $V_{mc} = 1.5V$

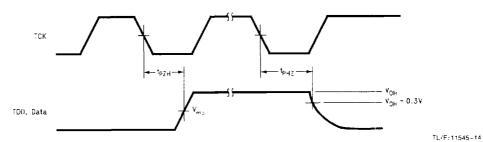

FIGURE 7. TRI-STATE Output High Enable and Disable Times

Note: Input pulses have the following characteristics: f  $\approx$  1 MHz, t,  $\approx$  2.5 ns, t<sub>f</sub>  $\approx$  2.5 ns, amplitude  $\approx$  3.0 v.

# Waveforms (Continued)

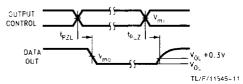

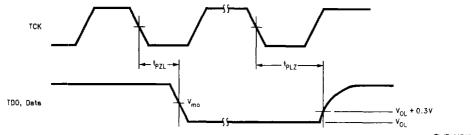

FIGURE 8. TRI-STATE Output Low Enable and Disable Times

TL/F/11545-15

FIGURE 9. Setup Time, Hold Time

$V_{mi} = 1.5V$  $V_{mo} = 1.5V$

TL/F/11545~17

TL/F/11545~18

TL/F/11545-16

\*Includes jig and probe capacitance.

FIGURE 11. Standard AC Test Load

Note: Input pulses have the following characteristics: f=1 MHz,  $t_{\rm f}=2.5$  ns,  $t_{\rm f}=2.5$  ns, amplitude = 3.0V.

7

# **Description of BOUNDARY-SCAN Circuitry**

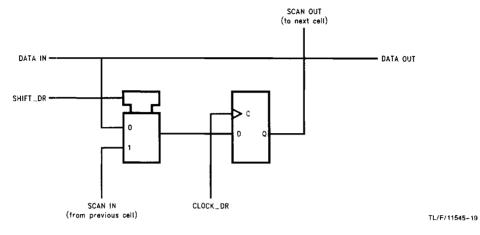

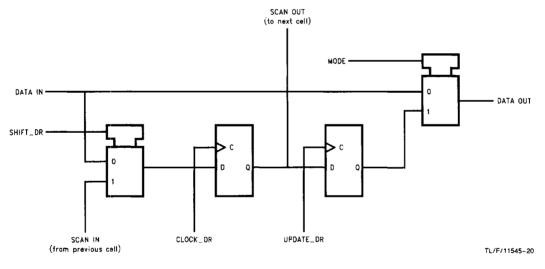

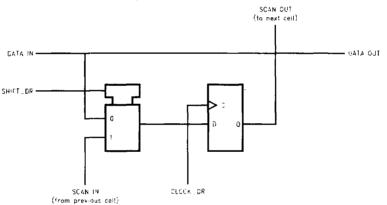

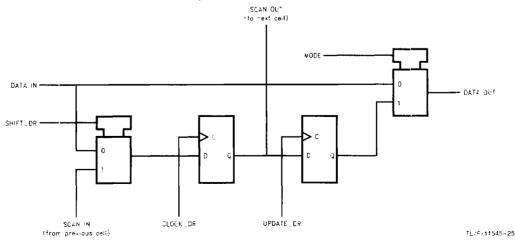

The scan cells used in the BOUNDARY-SCAN register are one of the following two types depending upon their location. Scan cell TYPE1 is intended to solely observe system data, while TYFE2 has the additional ability to control system data. (See IEEE Standard 1149.1 Figure 10–11 for a further description of scan cell TYPE1 and Figure 10–12 for a further description of scan cell TYPE2.)

Scan cell TYPE1 is located on each system input pin while scan cell TYPE2 is located at each system output pin as well as at each of the two internal active-high output enable signals. AOE controls the activity of the A-outputs while BOE controls the activity of the B-outputs. Each will activate their respective outputs by loading a logic high.

The BYPASS register is a single bit shift register stage identical to scan cell TYPE1. It captures a fixed logic low.

# Bypass Register Scan Chain Definition Logic 0

TL/F:11546-67

# SCAN182374A Product IDCODE (32-Bit Code per IEEE 1149.1)

| Version | Entity | Part<br>Number | Manufacturer<br>ID | Required<br>by 1149.1 |

|---------|--------|----------------|--------------------|-----------------------|

| 0000    | 111111 | 0000000111     | 00000001111        | 1                     |

MSB LSB

The INSTRUCTION register is an 8-bit register which captures the default value of 10000001 (SAMPLE/PRELOAD) during the CAPTURE-IR instruction command. The benefit of capturing SAMPLE/PRELOAD as the default instruction during CAPTURE-IR is that the user is no longer required to shift in the 8-bit instruction for SAMPLE/PRELOAD. The sequence of: CAPTURE-IR → EX T1-IR → UPDATE-IR will update the SAMPLE/PRELOAD instruction. For more information refer to the section on instruction definitions.

# Instruction Register Scan Chain Definition The state and the state are state as the state and the state are state as the state and the state are state as the state are state are state as the state are state are state as the state are state are state as the state are state as the state are state are state are state are state are state as the state are state are state are state as the state are sta

MSB → LSB

| Instruction Code | Instruction    |  |

|------------------|----------------|--|

| 00000000         | EXTEST         |  |

| 10000001         | SAMPLE/PRELOAD |  |

| 10000010         | CLAMP          |  |

| 00000011         | HIGH-Z         |  |

| 01000001         | SAMPLE-IN:     |  |

| 01000010         | SAMPLE-OUT     |  |

| 00100010         | EXTEST-OUT     |  |

| 10101010         | IDCODE         |  |

| 11111111         | BYPASS         |  |

| All Others       | BYPASS         |  |

# Scan Cell TYPE1

# Scan Cell TYPE2

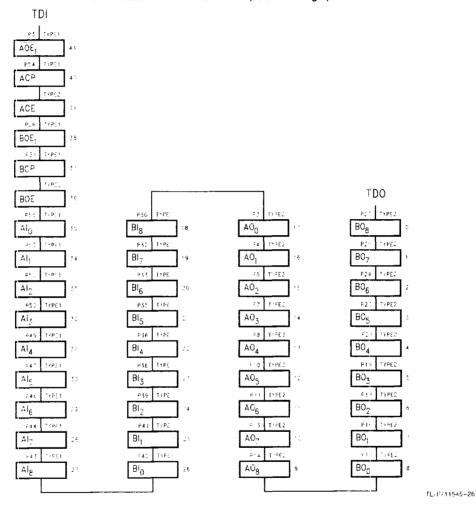

# BOUNDARY-SCAN Register SCAN182374 Scan Chain Definition (42 Bits in Length)

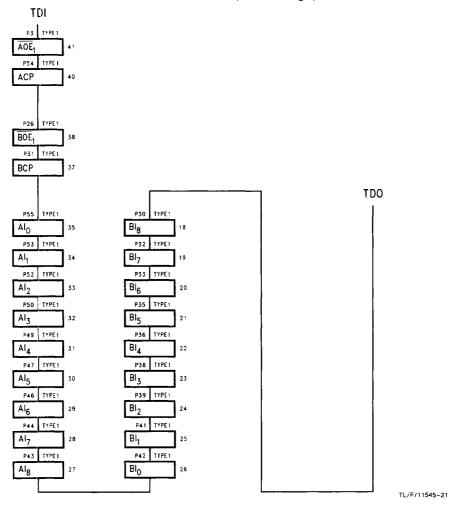

# Input BOUNDARY-SCAN Register SCAN182374 Scan Chain Definition (22 Bits in Length)

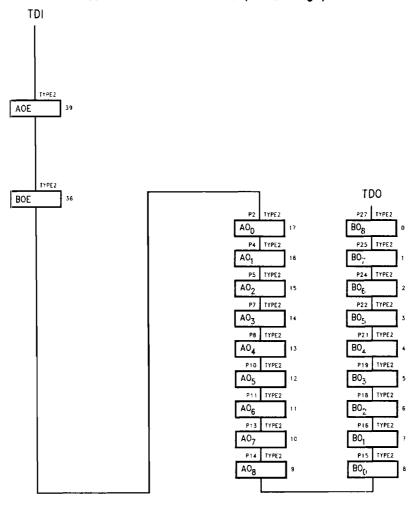

# Output BOUNDARY-SCAN Register SCAN 182374 Scan Chain Definition (20 Bits in Length)

TL/F/11545-22

# **BOUNDARY-SCAN Register Definition Index**

| Bit No. | Pin Name         | Pin No. | Pin Type | Scan C | ell Type |

|---------|------------------|---------|----------|--------|----------|

| 41      | AOE <sub>1</sub> | 3       | Input    | TYPE1  |          |

| 40      | ACP              | 54      | Input    | TYPE1  |          |

| 39      | AOE              |         | internal | TYPE2  | Control  |

| 38      | BOE <sub>1</sub> | 26      | Input    | TYPE1  | Signals  |

| 37      | BCP              | 31      | Input    | TYPE1  |          |

| 36      | BOE              |         | Internal | TYPE2  | <u></u>  |

| 35      | Al <sub>0</sub>  | 55      | Input    | TYPE1  |          |

| 34      | Al <sub>1</sub>  | 53      | Input    | TYPE1  |          |

| 33      | Al <sub>2</sub>  | 52      | Input    | TYPE1  |          |

| 32      | Al <sub>3</sub>  | 50      | Input    | TYPE1  |          |

| 31      | Al <sub>4</sub>  | 49      | Input    | TYPE1  | A-in     |

| 30      | Al <sub>5</sub>  | 47      | Input    | TYPE1  |          |

| 29      | Al <sub>6</sub>  | 46      | Input    | TYPE1  |          |

| 28      | Al <sub>7</sub>  | 44      | Input    | TYPE1  |          |

| 27      | Al <sub>B</sub>  | 43      | Input    | TYPE1  |          |

| 26      | BI <sub>0</sub>  | 42      | Input    | TYPE1  |          |

| 25      | Bi <sub>1</sub>  | 41      | Input    | TYPE1  |          |

| 24      | Bl <sub>2</sub>  | 39      | Input    | TYPE1  |          |

| 23      | Bl <sub>3</sub>  | 38      | Input    | TYPE1  |          |

| 22      | Bl₄              | 36      | Input    | TYPE1  | B-in     |

| 21      | BI <sub>5</sub>  | 35      | Input    | TYPE1  |          |

| 20      | BI <sub>6</sub>  | 33      | Input    | TYPE1  |          |

| 19      | Bi <sub>7</sub>  | 32      | Input    | TYPE1  |          |

| 18      | Bl <sub>8</sub>  | 30      | Input    | TYPE1  |          |

| 17      | $AO_0$           | 2       | Output   | TYPE2  |          |

| 16      | AO <sub>1</sub>  | 4       | Output   | TYPE2  |          |

| 15      | AO <sub>2</sub>  | 5       | Output   | TYPE2  |          |

| 14      | $AO_3$           | 7       | Output   | TYPE2  |          |

| 13      | AO <sub>4</sub>  | 8       | Output   | TYPE2  | A-out    |

| 12      | AO <sub>5</sub>  | 10      | Output   | TYPE2  |          |

| 11      | AO <sub>6</sub>  | 11      | Output   | TYPE2  | !        |

| 10      | AO <sub>7</sub>  | 13      | Output   | TYPE2  |          |

| 9       | AO <sub>8</sub>  | 14      | Output   | TYPE2  | ļ        |

| 8       | BO <sub>0</sub>  | 15      | Output   | TYPE2  |          |

| 7       | BO <sub>1</sub>  | 16      | Output   | TYPE2  |          |

| 6       | BO <sub>2</sub>  | 18      | Output   | TYPE2  |          |

| 5       | BO <sub>3</sub>  | 19      | Output   | TYPE2  | _        |

| 4       | BO <sub>4</sub>  | 21      | Output   | TYPE2  | B-out    |

| 3       | BO <sub>5</sub>  | 22      | Output   | TYPE2  |          |

| 2       | BO <sub>6</sub>  | 24      | Output   | TYPE2  |          |

| 1       | BO <sub>7</sub>  | 25      | Output   | TYPE2  |          |

| 0       | BO <sub>8</sub>  | 27      | Output   | TYPE2  |          |

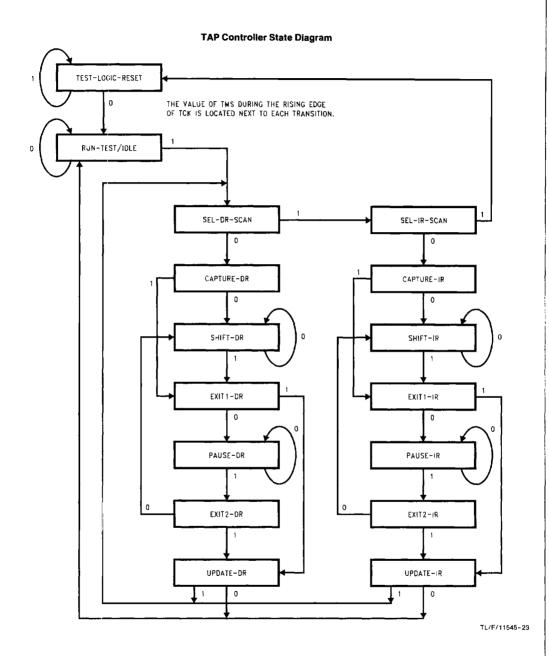

# **TEST ACCESS PORT (TAP)**

The Test Access Port (TAP) consists of four pins dedicated solely to the operation of the test logic. The four pins include TMS (Test Mode Select). TDI (Test Data In), TDO (Test Data Out), and TCK (Test Clock). These products contain a power-up reset function in lieu of adding the TRST pin. The motivation of this option is to save package size and hence customer board space, thus making the decision to implement JTAG less costly to the system designer.

TCK: This input provides the test clock for the test logic defined by the 1149.1 Standard. In accordance with the standard requirements, all test logic will retain its state indefinitely upon stopping TCK at a logic low, or 0. Additionally, the same retention may occur upon stopping TCK at a logic high, or 1, which is a permission granted by the standard. The motivation for TCK to be a dedicated test input is 1) to insure that it can be used independently of system clocks running at different frequencies, 2) that it permits shifting of test data without altering any system logic state when undertaking on-line system monitoring tasks, and 3) that it can be used to test all board interconnect even when that interconnect transfers clock signals from one device to another.

TMS: This input is the command signal to control system operation modes. Its value is accepted into the test logic upon the rising edge of TCK. This input has a pull-up resistor to implement a logic high for an undriven input. The requirement that an unforced TMS input produce a logic high is to ensure that the normal operation of the design can continue without interference from the test logic by guaranteeing that an undriven TMS input can put the TAP Controller into the Test Logic Reset state.

TDI: This signal provides the serial data input of test instructions and data to the test logic. Its value is accepted into the test logic upon the rising edge of TCK. This input has a pull-up resistor to implement a logic high for an undriven input. Test data will arrive at TDO without inversion after the appropriate number of clock cycles as determined by the length of the register currently connected between TDI and TDO. The requirement that an unforced TDI input produce a logic high is to assist in the determination of manufacturing defects in the test scan chain interconnect. A consistent field of 1's in shifting out the data registers can indicate where a break in the scan chain interconnect occurred.

**TDO:** This signal provides the serial data output of test instructions and data from the test logic. Changes in the logic state and drive activity for this output occur upon the falling edge of TCK. This is to avoid a race condition when TDO is connected to TD' of the next chip in the scan chain which is sampled on the rising edge. This output shall remain inactive except when the scanning of data is in progress. This is to permit the ability to multiplex scan chains on the board without causing signal contention between multiple TDO outputs connected together to form parallel scan chains

# TAP STATE DESCRIPTIONS

Changes in the state of the TAP Controller are solely a response to the value of TMS upon the rising edge of TCK, or upon power-up (or the application of a logic low to the optional TRST input which is not included in the products re-

ferring to this document). In any given state actions of the test logic taken in that state occur on the falling or risingedge of TCK following the rising edge of TCK which caused the TAP Controller to enter the state initially.

Note: It may happen that actions to occur in one state happen on the same rising edge of TCK that cause the TAP Controller to enter the next state.

**Test Logic Reset:** The test logic is disabled during this state such that normal operation of the system logic may proceed uninhibited.

Two features of the state diagram are realized in this state. First it can be noted that independent of what state the TAP Controller is currently in, it will enter the Test Logic Reset state after, at most, five clock cycles of TCK with the TMS input high. Secondly, if a temporary glitch should occur on the TMS input during a rising edge of TCK, the TAP Controller will enter the Run-Test/Idle state then return to the Test Logic Reset state via the Select-DR state and Select-IR state provided that TMS returns to its logic high value for rising edge clocks following the gitch. The TAP Controller will also be forced into the Test Logic Reset state upon a low assertion of the TRST pin or, in the case of the products referencing this article, upon power-up.

Run-Test/Idle: In this state activity in the test logic occurs according to the instruction present. None of the mandatory instructions undertake any test logic activity during this state. During the description above regarding recovery from a glitch on the TMS input the current instruction is the BY-PASS instruction and as a result no activity occurs in this state with that instruction present. This state is designed to provide the capability of performing built-in test functions during optional instructions. For instructions that do not activate test logic during this state, all test data registers retain their current state, i.e., remain idle.

**SELECT-DR Scan:** This is a temporary state in which all test data registers retain their previous values.

Capture-DR: In this controller state data may be parallel loaded into the data register selected by the current instruction; otherwise, it retains its previous values.

SHIFT-DR: In this state the test data register selected between TDI and TDO by the current instruction will shift one stage at each rising edge of TCK. TDO is active during this state. Test data registers not selected by the current instruction maintain their previous values.

Exit1-DR: This is a temporary state in which all test data registers retain their previous values

PAUSE-DR: This is a temporary state in which all data registers retain their previous values. This state is intended to temporarily halt the shifting of test data into the data register selected while retaining the ability to keep TCK running; TCK may be a free-running clock.

**Exit2-DR:** This is a temporary state in which all test data registers retain their previous values.

**UPDATE-DR:** The parallel output register of the selected test data register may be updated on the falling edge of TCK in this state, provided the test data register has such a parallel output register. The intent of the parallel output register is to provide the ability to apply the contents of the test data

registers to the test logic simultaneously rather than applying it as it is being shifted in. All test data registers not selected by the current instruction retain their previous values.

**SELECT-IR Scan:** This is a temporary state in which the INSTRUCTION register retains its previous value.

Capture-IR: In this controller state data must be parallel loaded into the INSTRUCTION register. The only restriction on what that data may be is that its least significant bit must be a logic high, cr 1, and its second least significant bit must be a logic low, or 0. These opposite state bits can be used to check the correct operation of the scan chain on the board by forcing a bit toggle when the instructions are shifted

**SHIFT-IR:** In this state the INSTRUCTION register selected between TDI and TDO will shift one stage at each rising edge of TCK. TDO is active during this state.

**Exit1-IR:** This is a temporary state in which the INSTRUCTION register retains its previous value.

PAUSE-IR: This is a temporary state in which the INSTRUC-TION register retains its previous value. This state is intended to temporarily halt the shifting of test data into the IN-STRUCTION register while retaining the ability to keep TCK running.

**Exit2-IR:** This is a temporary state in which the INSTRUCTION register retains its previous value.

UPDATE-IR: The parallel output register of the INSTRUCTION register will be updated on the falling edge of TCK in this state. The intent of the parallel output register is to provide the ability to apply the contents of the INSTRUCTION register to the test logic simultaneously rather than applying it as it is being snifted in.

## TDO OUTPUT ACTIVITY

Control of the TIDO output buffer follows the table outlined

| Controller<br>State | Register Selected<br>between<br>TDI and TDO | TDO<br>Driver |

|---------------------|---------------------------------------------|---------------|

| Test Logic Reset    | BYPASS                                      | Inactive      |

| Run Test/Id e       | BYPASS                                      | Inactive      |

| SELECT-DR Scan      | **                                          | Inactive      |

| SELECT-IR Scan      | INSTRUCTION                                 | Inactive      |

| Capture-IR          | INSTRUCTION                                 | Inactive      |

| SHIFT-IR            | INSTRUCTION                                 | ACTIVE        |

| Exit1-IR            | INSTRUCTION                                 | Inactive      |

| PAUSE-IR            | INSTRUCTION                                 | Inactive      |

| Exit2-IR            | INSTRUCTION                                 | Inactive      |

| UPDATE-IF:          | INSTRUCTION                                 | Inactive      |

| Capture-DF          | **                                          | Inactive      |

| SHIFT-DR            | TEST DATA                                   | ACT:VE        |

| Exit1-DR            | **                                          | Inactive      |

| PAUSE-DR            | ••                                          | Inactive      |

| Exit2-DR            | **                                          | Inactive      |

| UPDATE-DR           | **                                          | Inactive      |

Note: \*\* > Data register selected depends on currently active instruction

# FEATURES OF THE TAP CONTROLLER

The TAP Controller will not be init alized by the operation of any system pin such as a system reset. The TAP Controller will be initialized into the Test Logic Reset state upon power-up. This requirement is intended to avoid bus signal contention upon system power-up by disabling the test logic which allows the system logic to operate normally and hence be controlled to avoid any contention. (The TAP Controller will return to the Test Logic Reset state after, at most, five clock cycles of TCK with TMS high; but the time required to enact that operation may not be sufficient to avoid contention.)

Note that the TAP Controller has been defined such that six of the sixteen states have the ability to maintain their state provided that TMS remains at the same value it had when entering the state. Those states include Test Logic Reset to hold off the test logic during normal system operation, Run Test/Idle to undertake multi-cycle self tests, SHIFT-DR and SHIFT-IR to maintain the data shifting process for an extended period, and PAUSE-DR and PAUSE-IR to halt the shifting process while some other activity is performed such as retrieving test data from additional memory. This feature is available in any/all states where multiple clock cycles may be required to achieve the desired outcome or where activity is to be halted but still provide the ability to make TCK a free-running clock.

### INSTRUCTION REGISTER

The INSTRUCTION register permits specific commands to be shifted into the design to select a particular test data register and/or a specific test function. Additionally, the capture sequence of the INSTRUCTION register permits design specific data to be examined.

The INSTRUCTION register must be at least two bits long, the specific INSTRUCTION register included into the devices which reference this document is eight bits long, and the two least significant bits must capture the value "01". The significance of the two bit minimum length is two fold. First it permits the ability to supply unique codes for at least each of the three mandatory instructions required by the standard. Secondly, the bit value "01" in the least significant locations can be used to check the connectivity of the scan chain by forcing a bit toggle at each instruction during a scan of the INSTRUCTION registers. This technique not only assists in determining the correct connectivity of the scan chain about the board, but also assists in pir-pointing the location of any break in the scan chain.

The six most significant bits will contain device specific codes which can be used to differentiate them from each other when being interrogated through the bouncary-scan ring. On these products the DEVICE IDENTIFICATION register was not incorporated in order to minimize any cost and/or performance impact to the customer. As a result of that decision the operation of the test logic may be precisely identical in several of the functions. The different codes captured into the INSTRUCTION register is a means of distinguishing the products in order to supply a method of evaluating the correct board placement of the products when an interrogation is performed through the scan chain only.

The order of scan through the INSTRUCTION register must be least-to-most; that is, the least significant bit is closest to TDO for a loaded instruction. During the SHIFT-IR state the instruction shifts one bit between TDI and TDO upon each

rising edge of TCK and appears without inversion at TDO following the appropriate number of TCK cycles depending on the fixed length of the INSTRUCTION register. A latched parallel output register accompanies each bit of the INSTRUCTION register such that the instruction can be updated or applied to the test logic simultaneously, rather than during the shift sequence. This latched parallel output changes upon the falling edge of TCK in the Update-IR state as well as upon the falling edge of TCK during the Test Logic Reset state. (It changes asynchronously upon the low assertion of the TRST input or upon power-up.)

Each instruction will identify a particular test data register to be connected between TDI and TDO when in the Shift-DR state along with defining any particular test actions to occur to that test data register and/or any others.

### INSTRUCTION DEFINITIONS

The required instructions include the BYPASS, EXTEST, and SAMPLE/PRELOAD instructions. The optional instructions of HIGH-Z, CLAMP and IDCODE, as well as the additional instructions SAMPLE-IN, SAMPLE-OUT and EXTEST-OUT have also been incorporated into the specific devices which reference this document. The optional INTEST instruction was not incorporated due to the additional propagation delay penalty to the system logic which would result from gating that logic in order to provide controllability as well as observability. In the following descriptions each instruction will identify the test data register to be connected between TDI and TDO during the SHIFT-DR state, any restrictions on the binary codes used to implement the instruction, and what test data registers are used in undertaking the actions of the instruction.

- 1. EXTEST. This instruction allows circuitry external to the component package, typically the board interconnect, to be tested. BOUNDARY-SCAN register cells at the output pins are used to apply test stimuli, while those at the input pins capture test results. When this instruction is selected, the states of all signals on the system input pins will be loaded into the BOUNDARY-SCAN register upon the rising edge of TCK in the Capture-DR state and the contents of the BOUNDARY-SCAN register will solely define the state of the system outputs upon the falling edge of TCK in the UPDATE-DR state. This instruction is mandatory under the guidelines of IEEE Standard 1149.1. The 000. . . 0 instruction binary code must invoke the EXTEST instruction. During this instruction the BOUNDARY-SCAN register is connected between TDI and TDO in the SHIFT-DR state. Additional binary codes for this instruction are permitted.

- 2. SAMPLE/PRELOAD. This instruction allows a "snapshot" of the normal operation of the component to be taken and examined. It also allows data values to be loaded onto the latched parallel outputs of the BOUNDARY-SCAN SHIFT register prior to selection of another BOUNDARY-SCAN test instruction. During this instruction the BOUNDARY-SCAN register is connected between TDI and TDO in the SHIFT-DR state. When this instruction is selected, the states of all signals on the system pins will be loaded into the BOUNDARY-SCAN register upon the rising edge of TCK in the CAPTURE-DR state and the contents of the BOUNDARY-SCAN register will be loaded into the parallel output register included with the BOUNDARY-SCAN register bits upon the falling edge of TCK in the UPDATE-DR state.

- Note that by interfacing these two actions through the Exit1-DR state, the current state of the system pins can be captured into the BOUNDARY-SCAN register and stored into its parallel output registers for later application back onto those same pins. When the SAMPLE/PRELOAD instruction is selected, the test logic shall have no impact upon the system logic in performing its system function. This instruction is mandatory under the guidelines of IEEE Standard 1149.1, but the binary code may be device specific.

- 3. BYPASS. This instruction allows rapid movement of test data to and from other components on a board that are required to perform test operations by selecting the BYPASS register, a single-bit shift-register stage, between TDI and TDO in the SHIFT-DR state to provide a minimum-length serial scan path. This instruction is mandatory under the guidelines of IEEE Standard 1149.1. The 111...1 instruction binary code must invoke the BYPASS instruction. This specific opcode, along with the requirement that an undriven TDI input produce a logic high value, is intended to load the BYPASS instruction during an instruction-scan cycle if the scan chain is broken. In such a case all instructions following the break in the scan chain will be loaded with the BYPASS instruction and hence have no impact upon the system's normal functional operation. Additional binary codes for this instruction are permitted. When the BYPASS instruction is selected, the test logic shall have no impact upon the system logic in performing its system function. When the optional IDCODE register is not included, this instruction is loaded into the INSTRUCTION register in the Test Logic Reset state.

- 4. CLAMP. This instruction allows fixed guarding values to be placed on signals that control the operation of logic not involved in the test, but does not require that the BOUNDARY-SCAN register be part of the serial scan path as in the EXTEST instruction. The contents of the BOUNDARY-SCAN register will solely define the state of the system outputs upon the falling edge of TCK in the UPDATE-IR state for this instruction. The BYPASS register is connected between TDI and TDO in the SHIFT-DR state. This instruction is optional under the guidelines of IEEE Standard 1149.1 and therefore the binary code/s may be device specific.

- 5. HIGHZ. This instruction allows all of a components system outputs to be placed in an inactive drive state to permit its outputs to be safely backdriven during testing of other integrated circuits on the printed circuit board. All outputs of the device will become inactive even if during their normal system function they are two-state outputs. The BYPASS register is connected between TDI and TDO in the SHIFT-DR state. This instruction is optional under the guidelines of IEEE Standard 1149.1 and therefore the binary code/s may be device specific.

- IDCODE. This instruction allows a blind interrogation of an identification code that is unique to this device type. During this instruction the IDCODE register is connected between TDI and TDO in the SHIFT-DR state.

- 7. SAMPLE-IN. This instruction is analogous to SAMPLE/ PRELOAD but shortens the SCAN chain to include only the input and control pin cells (see Input BOUNDARY-SCAN register definition diagram). During this instruction only the Input BOUNDARY-SCAN register is connected between TDI and TDO in the SHIFT-DR state.

- 8. SAMPLE-OUT. This instruction is analogous to SAM-PLE/PRELOAD but shortens the SCAN chain to include only the output and internal TRI-STATE control cells (see Output BOUNDARY-SCAN register definition diagram). During this instruction only the Output BOUNDARY-SCAN register is connected between TDI and TDO in the SHIFT-DR state.

- 9. EXTEST-OUT. This instruction is analogous to EXTEST but shortens the SCAN chain to include only the output and internal TRI-STATE control cells (see Output BOUNDARY-SCAN register definition diagram). During this instruction only the Output BOUNDARY-SCAN register is connected between TDI and TDO in the SHIFT-DR state.

Each of the previously defined instructions fully indicates which data registers may operate or interact with the system logic while the instruction is current. Test data registers that are not selected by the current instruction must be controlled such that they do not interfere with the system logic or the operation of the test data registers currently selected. While a given instruction may lead to operation of more than one test data register, only one test data register may be connected between TDI and TDO during the SHIFT-DR state for the given instruction.

### **BOUNDARY-SCAN REGISTER**

The BOUNDARY-SCAN register permits testing of printed circuit board interconnects such as opens and shorts while also providing access to the components inputs and outputs when testing or monitoring its system logic. This register, as with all test data registers included in a 1149.1-compliant device, must be of fixed length. Data applied at the TDI input must appear without inversion at TDO during the SHIFT-DR state following the appropriate number of TCK cycles determined by the specific fixed length. This test data

TL+F/\*1545~24

# **Input BOUNDARY-SCAN Cell**

# **Output BOUNDARY-SCAN Cell**

register will shift one stage toward TDO at each rising edge of TCK in the SHIFT-DR state when selected by the current instruction. Data will be parallel loaded into the BOUNDARY-SCAN register upon a rising edge of TCK in the Capture-DR state and the parallel register stages of the BOUNDARY-SCAN register will be latched upon the falling edge of TCK in the UPDATE-DR state provided that it is selected by the current instruction; otherwise, no change to its contents shall occur.

The shift register stages used in the make-up of the BOUNDARY-SCAN register may or may not be required to incorporate a parallel output register as well as its shift register stage. This requirement depends on the function of the system logic pin with which it is associated as well as the operational requirements of that pin during certain instructions defined for the device. The Input and Output Boundary-Scan cells demonstrate the parallel register stage, or lack thereof. The first cell can be used on system input pins where only observability of its logic state is necessary while the second scan cell can be used at system outputs where observability and control ability are required. Note that in the input scan cell there is no multiplexer directly in the data path while one does exist in the output scan cell. It is the logic gating of the data path that results in the performance penalty of the data path when controlling test logic is added. It is for this reason that the optional INTEST instruction was not included as one of the available features on the products which specifically reference this document. It was deemed unnecessary to pay the performance cost in exchange for the limited functional extension of controlling inputs as well.

If INTEST capability is desired, the system logic of the products referencing this document can be considered an extension of the EXTEST capability. All 1149.1-compliant devices require that the input and output data path scan cells be placed at logically equivalent locations to the system pin. As a result of that action the input/output buffers and voltage level translators are already tested as an extension of interconnect tests. If these interconnect tests are combined with the triggering of a 374 flip-flop clock input, as an example, the internal logic of the device can be evaluated as an extension of the EXTEST capability. Because the National SCAN products currently offered have easily manipulated system logic, the 1149.1 user can logically extend the internal system logic to the EXTEST function. This feature is available during the EXTEST instructions for these products because the state of the outputs is captured along with the state of the inputs during the rising edge of TCK in the CAPTURE-DR state. Note that this is contrary to a recommendation of capturing fixed values on the outputs during EXTEST, but it provides for a feature that would otherwise not exist.

While these cells are sufficient to observe the logic state of the signal in which they are placed, they have a limitation in observing the activity of such a signal as in the specific case of a three-stated output. To determine the activity as well as the logic state of such an output, two such scan cells are required. One in the data signal path and another in the output enable signal path. By observing at both locations

the drive activity and/or logic value can be inferred. In the case of a single output enable signal controlling more than one output data path, the output enable signal may be observable and controllable at a single location rather than at each specific output without loss of functional intent provided that the specific location retain control over all the data outputs in unison. This provision is included to reduce the hardware overhead as in the case of a device where such output enable signals are organized byte-wide.

The order of the required scan cells in the BOUNDARY-SCAN register is undefined by the 1149.1 Standard and hence can be device specific even if the system function of that device be identical to another 1149.1-compliant device. In other words, even if two identical system function devices are 1149.1-compliant there is no guarantee that such devices will be identical in the structure of the BOUNDARY-SCAN register.

### **BYPASS REGISTER**

The BYPASS register is also a test data register and therefore must comply with the definitions surrounding test data register operation; but its advantage is in its size, not necessarily in its function. The BYPASS register consists of a single shift register stage in order to shorten the board-level serial scan chain by bypassing some devices while accessing others. This feature is intended to reduce the software overhead in applying and retrieving serial test data by permitting a shortcut between TDI and TDO of any given integrated circuit in order to expedite access to others.

The BYPASS register must capture a logic low value upon the rising edge of TCK in the SHIFT-DR state provided that it is selected by the current instruction. This feature is designed to accompany those devices which incorporate the 32-bit device identification register. (The BYPASS register is a test data register whose least significant bit is a fixed logic high.) Upon an initial scan of the data registers connected across the board, all devices will either connect the BY-PASS register or the optional device IDENTIFICATION register in its test data register scan path between TDI and TDO while in the SHIFT-DR state. (This condition is a result of power-up or a logic low assertion to TRST to initialize each 1149.1 device on board.) By shifting the data registers the retrieval of each logic zero indicates a BYPASS register connection until the first logic high is read. The logic high will be the framing bit of a device IDENTIFICATION register which would then indicate that the following thirty-one bits are identifiers to the specific device at that location of the scan chain. The requirement that the BYPASS register capture a logic low value is intended to form the background for the device IDENTIFICATION register framing bit. Additionally, the logic low value is opposite the value to be produced in the case of an undriven TDI input pin.

# INPUT BOUNDARY-SCAN REGISTER

The Input BOUNDARY-SCAN register operates in a manner analogous to the full length BOUNDARY-SCAN register.

### **OUTPUT BOUNDARY-SCAN REGISTER**

The Output BOUNDARY-SCAN register operates in a manner analogous to the full length BOUNDARY-SCAN register.