# SIEMENS

# **ICs for Communications**

Segmentation and Reassembly Element SARE

PXB 4110 Version 1.1

Preliminary Data Sheet 01.97

T4110-XV11-P2-7600

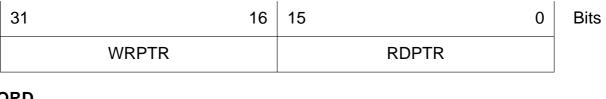

| PXB 4110<br>Revision His               | story:                                                       | Current Version: 01.97                                                                                                                                                                                                                 |  |  |  |

|----------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Previous Ver                           | Previous Version: Preliminary Data Sheet 08.95 (Version 1.1) |                                                                                                                                                                                                                                        |  |  |  |

| Page (in<br>previous<br>Version)       | Page<br>(in new<br>Version)                                  | Subjects (changes since last revision)                                                                                                                                                                                                 |  |  |  |

| 9-10,<br>25-29,<br>32-37, 40,<br>54-56 | 10-11,<br>24-28,<br>31-36, 39,<br>55-57                      | Up to 32 simultaneous connections/links changed to typically 60 (or at least 32) simultaneous virtual connections/links throughout document.                                                                                           |  |  |  |

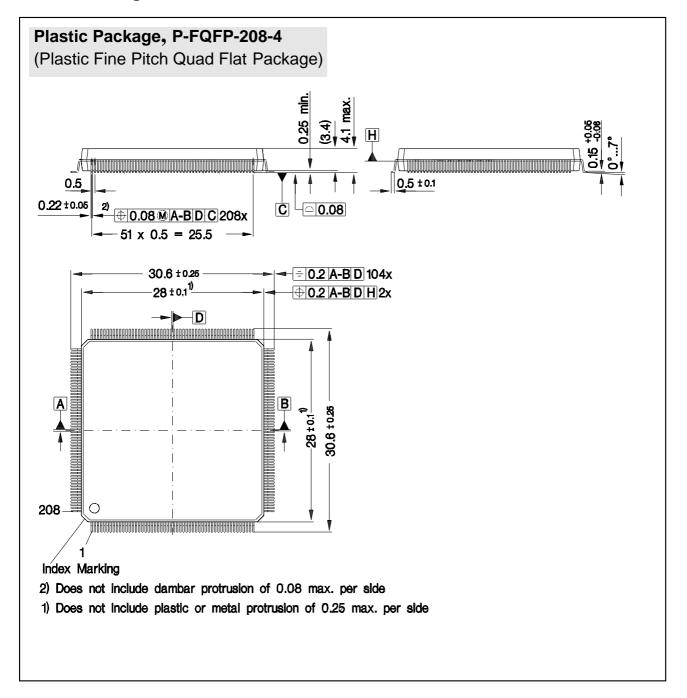

| 10-11, 13,<br>142                      | 10-13, 144                                                   | Package changed from P-FQFP-208-2 to P-FQFP-208-4.                                                                                                                                                                                     |  |  |  |

| 12-13, 17,<br>21, 24                   | 13, 19, 23                                                   | UCMOD added to UTOPIA Interface, Pin 31 changed from NC.<br>UTOPIA Master/Slave, M/S, inverted high/low, Pin 187.                                                                                                                      |  |  |  |

| 13, 26                                 | 13, 25                                                       | Pin 147, PINT, changed to PINT.                                                                                                                                                                                                        |  |  |  |

| 18                                     | 17                                                           | Pin 32, PERR, changed from Output (O) to Open Drain (OD).                                                                                                                                                                              |  |  |  |

| 19                                     | 18                                                           | Max. clock frequency changed from 33 (66) MHz to 33 MHz.                                                                                                                                                                               |  |  |  |

| 9, 30                                  | 11, 30                                                       | ATM NIC application: deleted reference to UTPT.                                                                                                                                                                                        |  |  |  |

| 36                                     | 35                                                           | "With or without CRC32/Multiplexilng PDUs" moved from AAL5 to AAL3/4.                                                                                                                                                                  |  |  |  |

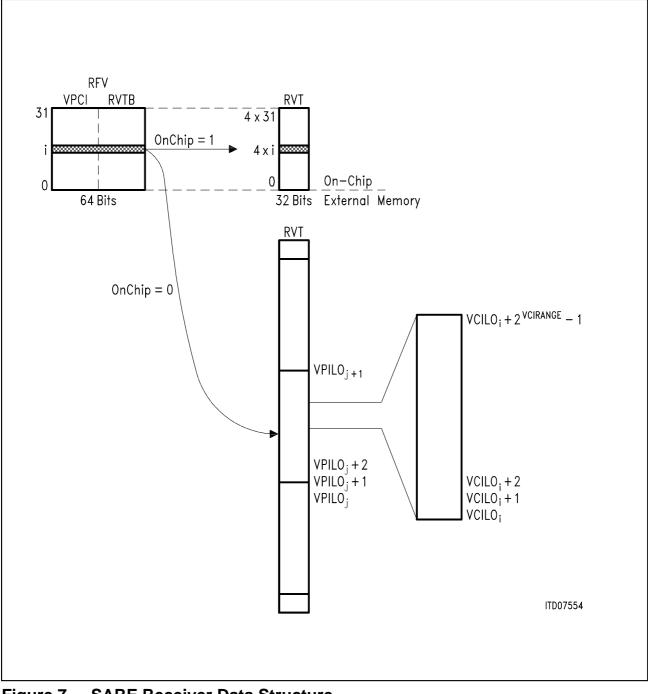

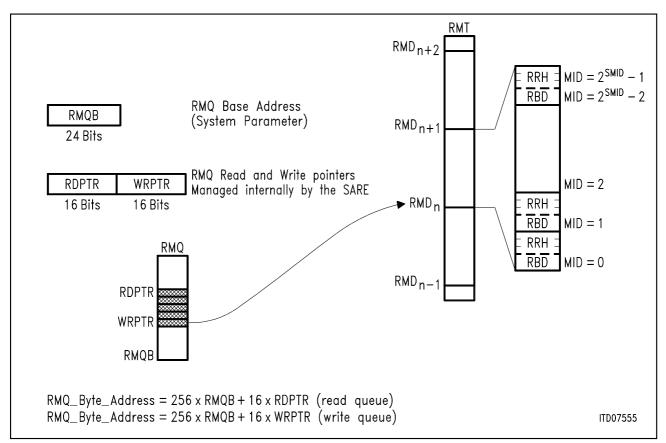

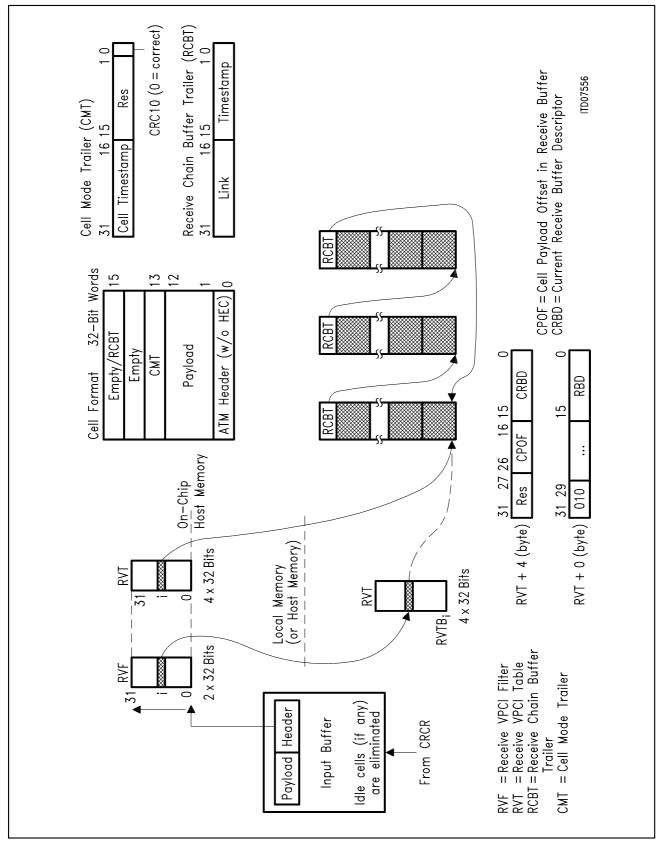

| 38-41, 98                              | 37-41, 95                                                    | Correction and clarification of RVF registers, VPCI and RVTB, including text, tables, equations, and figures.                                                                                                                          |  |  |  |

| 43, 58, 85,<br>112-114                 | 43, 58, 86,<br>110-112                                       | Timestamp changed to Reserved or reference to Timestamp removed.                                                                                                                                                                       |  |  |  |

| 63                                     | 64                                                           | Bit rate of virtual channel changed from r = 155.52 Mbit/s $\times$ TiK0/TiL to 8 $\times$ (frequency of UTOPIA TxCLK) $\times$ TiK0/TiL.                                                                                              |  |  |  |

| 76                                     | 76                                                           | External local memory address access was changed from AD(19-0) to AD(21-0).                                                                                                                                                            |  |  |  |

| 81                                     | 80                                                           | Additional description regarding location of control data for proper device operation.                                                                                                                                                 |  |  |  |

| 88, 89                                 | 87                                                           | Table 31: Vector ID reset value changed from $1029_{H}$ to $110A_{H}$ ;<br>Interrupt line reset value changed from $00_{H}$ to $FF_{H}$ ; Interrupt pin reset<br>value changed from $00_{H}$ to $01_{H}$ ; Min_Lat changed to Max_Lat. |  |  |  |

| 91                                     | 88                                                           | TmK0 Access from SARE changed from R/W to R.                                                                                                                                                                                           |  |  |  |

| 109-111                                | 104-109                                                      | Table 35: C_TCKMOD changed to Reserved; C_TCKDIV description updated; DELCON function removed; C_BPARK added.                                                                                                                          |  |  |  |

| 126-127                                | 123-125                                                      | Ambient temperature changed from 0 to 70 $^{\circ}$ C to – 40 to + 85 $^{\circ}$ C;<br>Supply voltage, 3 V, changed from – 0.5 to 4.125 V.                                                                                             |  |  |  |

| 126-127                                | 124-125                                                      | Added DC characteristics: High-Level output voltage for PCI pins;<br>Power consumption on $V_{\text{DD3}}$ and $V_{\text{DD5}}$ ; Input and output leakage current for PIC pins.                                                       |  |  |  |

| 134-135                                | 133                                                          | UTOPIA Interface signal characteristics: Delay time values updated.                                                                                                                                                                    |  |  |  |

| PXB 4110<br>Revision History:                    |                | Current Version: 01.97                                                                                |

|--------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------|

| Previous V                                       | ersion: Prelim | inary Data Sheet 08.95 (Version 1.1)                                                                  |

| Page (in<br>previousPage<br>(in new<br>Version)S |                | Subjects (changes since last revision)                                                                |

|                                                  |                | Table 42: CLK to signal valid delay values changed; Input setup time values changed.                  |

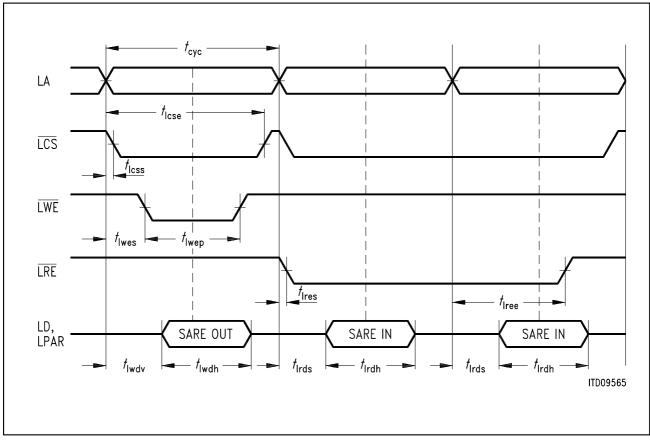

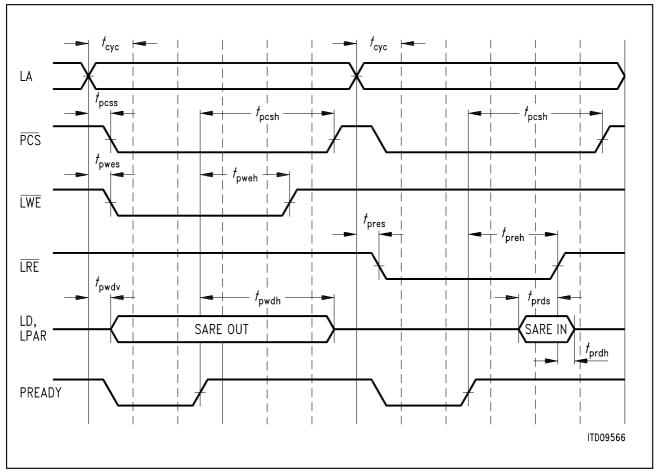

| 140-141                                          | 140-141        | Local Memory/Control Interface Timing: figure 31 and table 44 replaced; figure 32 and table 44 added. |

#### Edition 01.97

This edition was realized using FrameMaker<sup>®</sup> and Designer software.

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

<sup>©</sup> Siemens AG 1997. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

Page

#### **Table of Contents**

|                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| $1 \\ 1.1 \\ 1.2 \\ 1.3 \\ 1.4 \\ 1.4.1 \\ 1.4.2 \\ 1.4.3 \\ 1.4.4 \\ 1.4.5 \\ 1.5 \\ 1.6 \\ 1.6.1 \\ 1.6.2$              | OverviewFeaturesLogic SymbolPin ConfigurationPin Definitions and FunctionsParallel Host InterfaceUTOPIA InterfaceLocal Memory/Control InterfaceTest InterfacePower Supply InterfaceFunctional Block DiagramSystem IntegrationATM Network Interface CardsApplications in ATM Switches/Hubs                                                                                                                                                                   | .10<br>.12<br>.13<br>.14<br>.14<br>.24<br>.26<br>.26<br>.26<br>.27<br>.28<br>.29 |

| 2<br>2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.4<br>2.2.4.1<br>2.3<br>2.3.1<br>2.3.2                          | Functional DescriptionBlock DiagramInterfacesUTOPIA InterfaceSystem Bus InterfaceLocal Memory InterfaceBoundary Scan and Test InterfaceAdditional Test CapabilitiesFunctional OverviewFunctions in Receive DirectionFunctions in Transmit Direction                                                                                                                                                                                                         | .30<br>.30<br>.31<br>.31<br>.31<br>.32<br>.32<br>.32                             |

| 3<br>3.1<br>3.1.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.3<br>3.3.1<br>3.3.1<br>3.3.2 | Receive Data StructuresReceive Procedure SummaryReceive Procedure ExampleGeneral Description of Receive Data Structures (AAL5)Initialization of the Reassembly for a PDUInitialization of the Receive VPCI Table (RVT)Receive VPCI Filter (RVF)Context Information During ReassemblyReceive BufferReceive Ready Queues (RRQ)Streaming Mode OperationOther Modes of ReceptionReassembly on Virtual Connections According to AAL3/4Transparent Mode Reception | .35<br>.36<br>.37<br>.37<br>.37<br>.39<br>.41<br>.42<br>.43<br>.45<br>.46        |

| 3.3.3<br>3.3.3.1                                                                                                          | Reception in Cell FIFO Mode                                                                                                                                                                                                                                                                                                                                                                                                                                 | .48                                                                              |

| Table o | of Contents                                        | Page |

|---------|----------------------------------------------------|------|

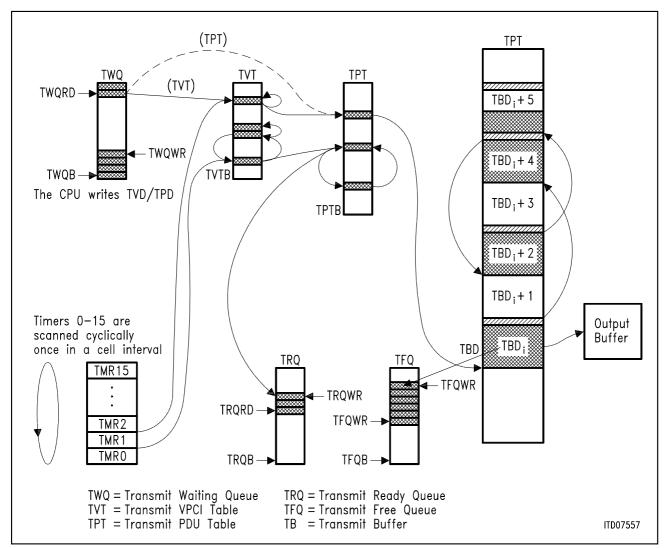

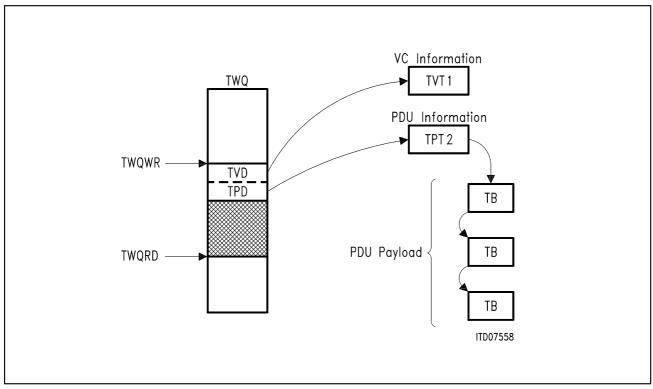

| 4       | Transmit Data Structures                           | 51   |

| 4.1     | Transmit Procedure Summary                         | 51   |

| 4.2     | Modes of Segmentation                              | 54   |

| 4.3     | General Description of Transmit Data Structures    | 54   |

| 4.3.1   | Transmit VCI Table (TVT)                           | 55   |

| 4.3.2   | Transmit PDU Table (TPT)                           | 57   |

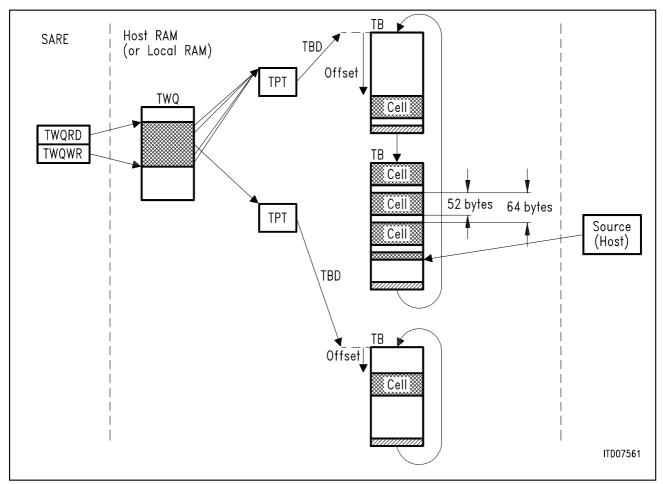

| 4.3.3   | Transmit Buffers (TBs)                             | 59   |

| 4.3.4   | Transmit Waiting Queue (TWQ)                       | 60   |

| 4.3.5   | Transmit Ready Queue (TRQ)                         | 60   |

| 4.4     | Operation of the Credit Manager                    | 61   |

| 4.5     | Description of the Specific Modes of Segmentation  | 65   |

| 4.5.1   | AAL5                                               | 65   |

| 4.5.2   | AAL3/4                                             | 66   |

| 4.5.3   | SMDS                                               | 66   |

| 4.5.4   | OAM                                                | 67   |

| 4.5.5   | Transparent Mode                                   | 67   |

| 4.5.6   | Cell FIFO Mode                                     | 67   |

| 4.5.7   | Additional Functions                               | 71   |

| 4.5.7.1 | Generation of an Incorrect HEC (for testing)       | 71   |

| 4.5.7.2 | Empty Cell Generation                              | 71   |

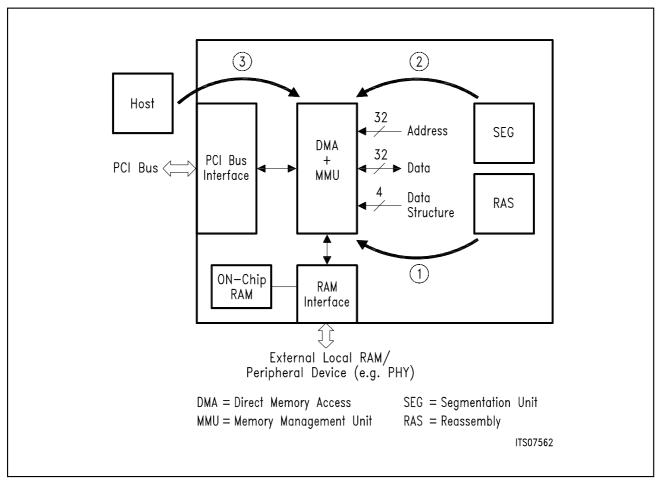

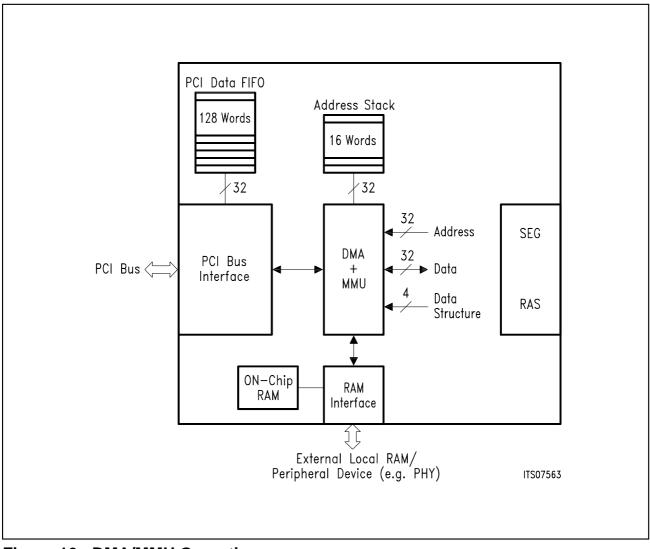

| 5       | System Interface and Operational Description       | 72   |

| 5.1     | DMA Controller and Memory Management Unit          |      |

| 5.1.1   | General Structure                                  |      |

| 5.1.2   | DMA Operation                                      | 73   |

| 5.1.2.1 | DMA Controller Write                               |      |

| 5.1.2.2 | DMA Controller Read                                | 75   |

| 5.2     | Host Accesses                                      | 75   |

| 5.3     | Memory Requirements                                | 78   |

| 5.4     | Operational Description of Reassembly Procedures   | 82   |

| 5.4.1   |                                                    | 82   |

| 5.4.2   | Setting up a Virtual Connection                    | 83   |

| 5.4.3   | PDU Receive                                        |      |

| 5.4.4   | Tearing Down a Virtual Connection                  | 83   |

| 5.5     | Operational Description of Segmentation Procedures | 84   |

| 5.5.1   | Initialization                                     |      |

| 5.5.2   | Setting up a Virtual Connection                    | 84   |

| 5.5.3   | PDU send                                           |      |

| 5.5.4   | End of PDU Segmentation                            |      |

| 5.5.5   | Tearing Down a Virtual Connection                  |      |

| Table o                                                                                                                                                                | f Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

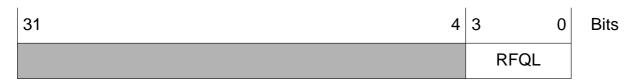

| 6<br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>6.2.8<br>6.2.9<br>6.2.10<br>6.2.11<br>6.2.12<br>6.2.13<br>6.2.13<br>6.2.14<br>6.2.15 | Register Descriptions         PCI Interface Registers         Configuration, Control and Status Registers         Credit Manager Timer Registers         Receive VPCI Filter Registers         Empty (Idle) Cell Registers         OAM-F5 Cell FIFO Descriptor         Base Addresses for Receive Data Structures         Buffer Size and MID Table Size Registers         Receive Queue Management Registers         Configuration Register         CRC Registers         Interrupt Registers         Statistics Registers         Base Addresses for Transmit Data Structures         Data Structures         Statistics Registers         Statistics Register         Statistics Register         Statistics Register         Statistics Register | 86<br>88<br>93<br>95<br>96<br>97<br>97<br>97<br>.100<br>.101<br>.104<br>.104<br>.109<br>.110<br>.113<br>.115<br>.117<br>.121 |

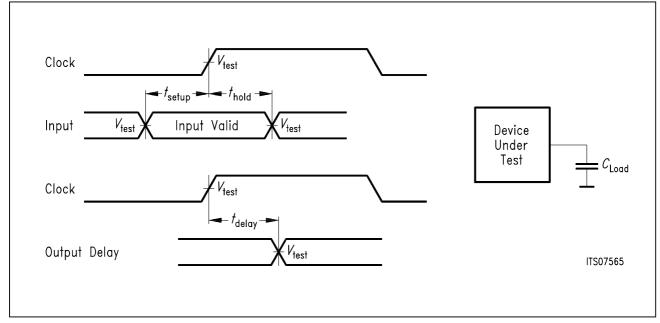

| 7<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.5.1<br>7.5.2<br>7.5.2.1<br>7.5.2.2<br>7.6<br>7.6.1<br>7.6.1.1<br>7.6.1.2<br>7.6.2<br>7.6.3                                   | Electrical Characteristics<br>Absolute Maximum Ratings<br>Recommended Operating Conditions<br>DC Characteristics<br>Capacitance<br>AC Characteristics<br>AC Measurement Conditions<br>UTOPIA Interface Timing<br>Transmit Handshake Protocol Timing<br>Receive Handshake Protocol Timing<br>UTOPIA Interface Signal Characteristics<br>PCI Interface Timing<br>PCI Read Transaction<br>PCI Write Transaction<br>Local Memory/Control Interface Timing<br>Peripheral Device Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .123<br>.123<br>.124<br>.125<br>.126<br>.126<br>.126<br>.126<br>.128<br>.131<br>.133<br>.134<br>.135<br>.137<br>.140         |

| 8                                                                                                                                                                      | Package Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .144                                                                                                                         |

| 9<br>9.1<br>9.2<br>9.3<br>9.4                                                                                                                                          | Appendix         General ATM Acronyms         Data Structure Acronyms         Parameter/Variable Acronyms         Register Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .145<br>.147<br>.147                                                                                                         |

## SIEMENS

| List of Fig | jures Page                                                          |

|-------------|---------------------------------------------------------------------|

| Figure 1:   | PXB 4110 Segmentation and Reassembly Element Logic Symbol12         |

| Figure 2:   | SARE Pin Configuration                                              |

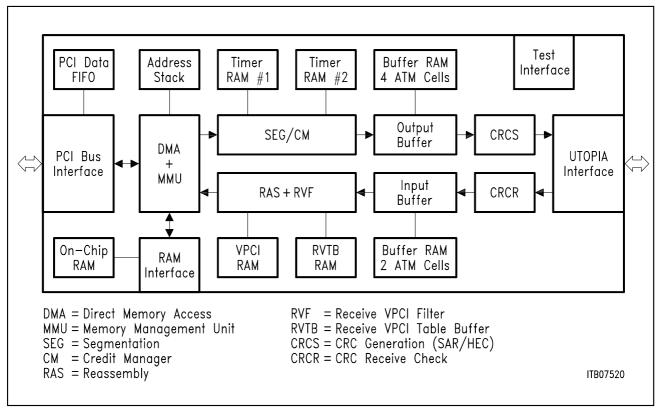

| Figure 3:   | SARE Block Diagram                                                  |

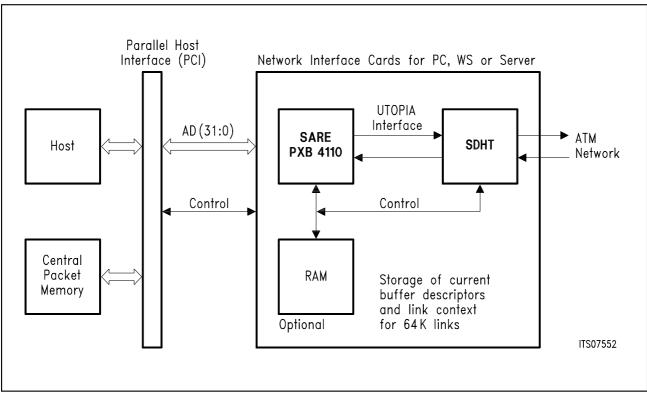

| -           | Network Interface Card (NIC) Architecture                           |

| -           | SARE Function Block Diagram                                         |

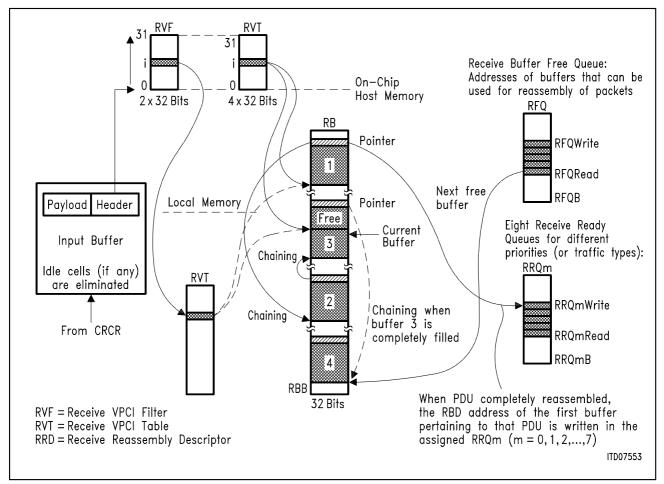

| •           | AAL5 Receive Procedure                                              |

| -           | SARE Receiver Data Structure40                                      |

| •           | Receive MID Table                                                   |

| •           | Cell FIFO Mode Receive                                              |

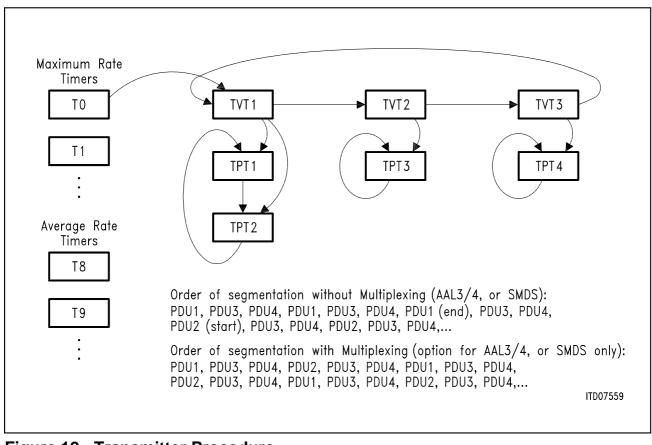

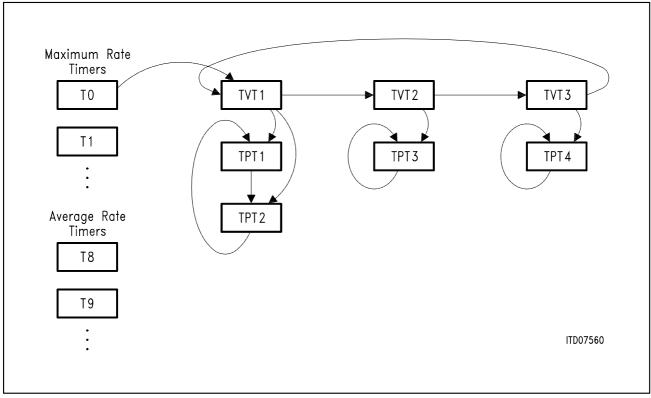

| -           | Transmitter Procedure                                               |

| 0           | Transmitter Procedure                                               |

| 0           | Transmitter Procedure                                               |

| -           | Credit Manager's Two-Dimensional Chained Data Structure             |

| -           | Cell FIFO Operation Principle                                       |

| •           | DMA/MMU Connections                                                 |

|             | DMA/MMU Operation                                                   |

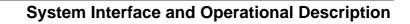

|             | Configuration Options                                               |

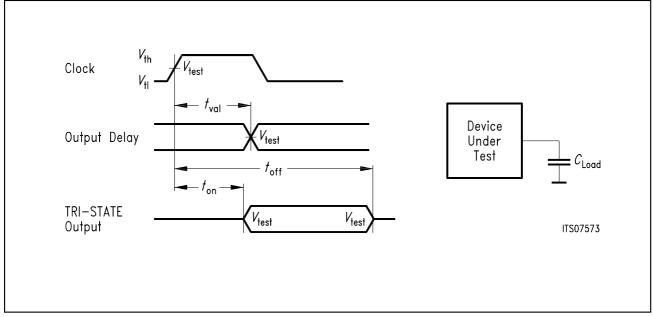

| •           | UTOPIA Interface Timing Measurement Waveforms                       |

| •           | Significance of SARE Pins in Master and Slave Modes                 |

|             | Connections in Master and Slave Modes                               |

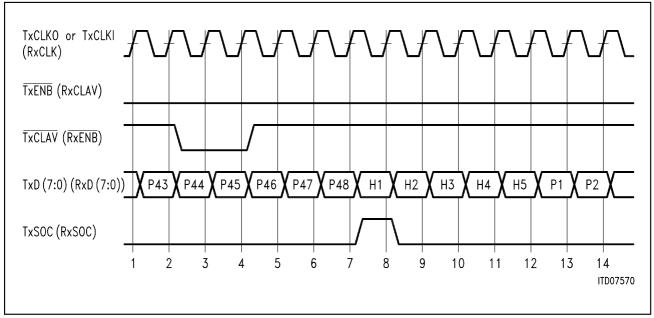

| -           | UTOPIA I/F Transmit Handshake Protocol (Master Mode), Example 2 130 |

| •           | UTOPIA I/F Transmit Handshake Protocol (Master Mode), Example 2 130 |

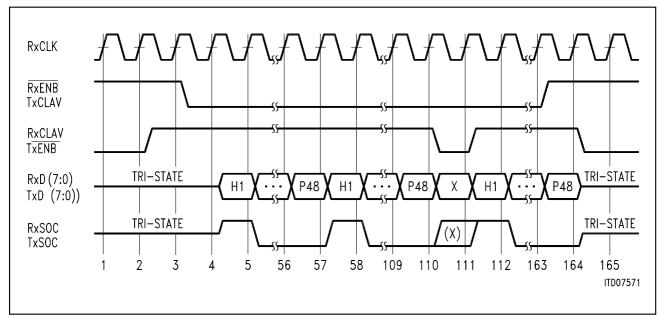

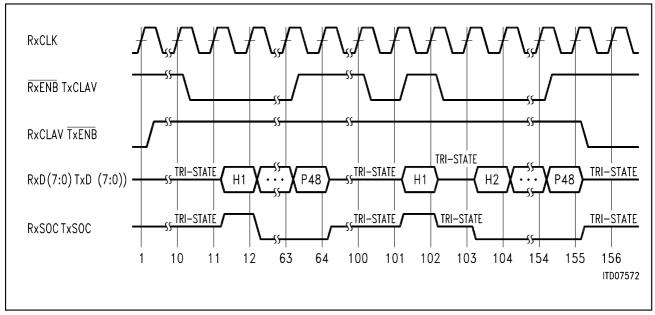

| -           | UTOPIA Interface Receive Handshake Protocol, Example 1              |

| •           | UTOPIA Interface Receive Handshake Protocol, Example 1              |

| •           | PCI Output Timing Measurement Waveforms                             |

| -           | PCI Input Timing Measurement Waveforms                              |

| 0           | PCI Read Transaction                                                |

| -           | PCI Write Transaction                                               |

|             | PCI Clock Specification                                             |

| -           | Local Memory/Control Interface Timing                               |

| -           | Peripheral Device Access Timing                                     |

|             |                                                                     |

| List of Ta | ıbles                                                    | Page |

|------------|----------------------------------------------------------|------|

| Table 1:   | Parallel Host Interface                                  | 14   |

| Table 2:   | UTOPIA Interface                                         | 19   |

| Table 3:   | Local Memory and Control Interface                       |      |

| Table 4:   | Test Interface                                           |      |

| Table 5:   | Power Supply Interface                                   | 26   |

| Table 6:   | Loopback and UTOPIA Mode Descriptions                    | 32   |

| Table 7:   | Receive Connection Types Implemented in the SARE         | 35   |

| Table 8:   | Available Buffer Sizes                                   | 42   |

| Table 9:   | Receive Ready Queue Error Codes                          |      |

| Table 10:  | Modes of Segmentation                                    | 54   |

| Table 11:  | Transmit Data Structures                                 | 54   |

| Table 12:  | Transmit VCI Table                                       | 55   |

|            | Segmentation Throttle Factor                             |      |

| Table 14:  | Transmit PDU Table                                       | 57   |

| Table 15:  | TPT Initialization Setup by Host                         | 58   |

|            | Buffer Size                                              |      |

|            | Transmit Waiting Queue                                   |      |

|            | Transmit Ready Queue                                     |      |

|            | Potential States of a Virtual Connection                 |      |

|            | TWQ in Cell FIFO Mode                                    |      |

|            | TPT in Cell FIFO Mode                                    |      |

|            | CRC Generation Characteristics                           |      |

|            | Host Access Types                                        |      |

|            | Access Type Nomenclature                                 |      |

|            | Variables Used in Calculation of Required Storage Space  |      |

|            | Storage Space Required by Each Data Structure            |      |

|            | Buffer Size (RB and TB) = 64 Bytes                       |      |

|            | Buffer Size (RB and TB) = 256 Bytes                      |      |

|            | Buffer Size (RB and TB) = 2048 Bytes                     |      |

|            | PCI Interface Register Descriptions                      |      |

|            | PCI Interface Register Specifications                    |      |

|            | Configuration, Control, and Status Register Descriptions |      |

|            | Credit Manager Timer Register Summary                    |      |

|            | Buffer Sizes                                             |      |

|            | CONF Register Bit Descriptions                           |      |

|            | Interrupt Register Bit Descriptions                      |      |

|            | Summary of Statistic Registers                           |      |

|            | STRUCT Register Bit Descriptions                         |      |

|            | UTOPIA Interface Timing Measurement Conditions           |      |

|            | PCI Input and Output Measurement Conditions              |      |

|            | PCI Clock Characteristics                                |      |

|            | PCI Interface Signal Characteristics                     |      |

|            | Local Memory/Control Interface Timing Characteristics    |      |

| i able 44: | Peripheral Device Access Timing Characteristics          | 143  |

#### 1 Overview

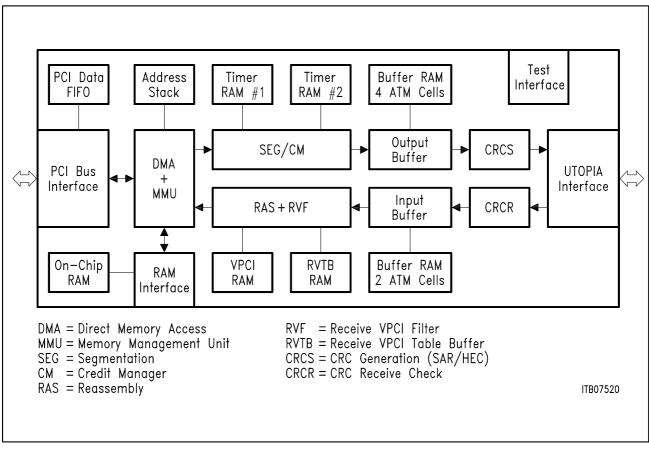

The Segmentation And Reassembly Element SARE PXB 4110 is a member of the Siemens ATM chip set. Following the modular chip concept, the SARE has the UTOPIA industry-standard interface which is also used by other components of the ATM chip set, including SDHT (PXB 4240), IWE (PXB 4220), ASP-up (PXB 43201) and ASP-down (PXB 43202).

The SARE conforms to the most advanced architectural requirements in equipment that terminates AAL connections in ATM networks. It supports processing of the Segmentation/Reassembly and ATM Adaptation Layers for up to 64K simultaneous connections. The type of AAL (either AAL5, AAL3/4, SMDS, OAM cell mode or transparent mode; or cell FIFO mode for constant bit rate) is individually programmable per Virtual Connection. The interface to the system is formed by a shared packet memory via the on-chip PCI compliant interface.

For packets to be segmented, the integrated DMA controller autonomously transfers user data from the central shared packet memory to its internal segmentation unit on a cell-by-cell basis. Received cells are checked for correctness and likewise transferred to the central memory by DMA via the PCI Interface.

For optimum usage of memory space, the on-chip DMA controller implements scatter/ gather data storage using linked list data buffers, with programmable buffer length. The descriptors of the data buffers in segmentation/reassembly are stored locally for each active virtual connection. Typically, at least 60 simultaneously active virtual connections are supported without external local memory, because the active descriptors and link context data are stored in on-chip memory. In the case of more than 60 simultaneously active virtual connections, the buffer descriptors and link context data for up to 64K connections can be resident in a local RAM connected to the SARE through a separate 32-bit parallel bus.

The interface of the SARE to the ATM Physical Layer is a UTOPIA Level 1 Interface, with 8-bit data buses. In the case where the SARE is used in an ATM Switch/Hub, it can be configured to operate as a clock slave with respect to the UTOPIA Interface (instead of master, as in ATM network attachment applications) to directly connect to an ATM Switch Preprocessor (ASP).

Direct access to SARE internal registers is provided via the PCI Interface. The SARE directly provides the interface to control and monitor other devices (like PHY devices) from the PCI Interface without the need of a separate control bus, thus minimizing the component cost in particular in Network Interface Card applications. For testing purposes and for applications with local packet memory, access to local memory from the PCI is also possible via the SARE.

Overall, because of these features, the SARE enables the implementation of glueless, cost-optimized solutions for AAL terminating equipment in ATM networks.

# SIEMENS

# Segmentation and Reassembly Element SARE

Version 1.1

## 1.1 Features

## General Features

- Processing of ATM Adaptation Layer

Segmentation/Reassembly and Convergence

Sublayer protocols

- Programmable for AAL5, AAL3/4, transparent and Cell FIFO mode (for CBR support) on a connection-by-connection basis

- Implementation of segmentation/reassembly for at least 60 (typical) simultaneous virtual connections without external RAM

- Implementation of segmentation/reassembly for up to 64K simultaneous virtual connections with additional external local RAM

- Optimized load-sharing between local memory bus (for context and overhead data) and PCI system bus (only payload data)

- Random VPI/VCI values for 32 virtual connections without external RAM (or 64K virtual connections with external RAM)

- CRC-32 calculation/check programmable on a connection-by-connection basis

- Cell rate shaping with priorities, up to 8 (dual) leaky buckets

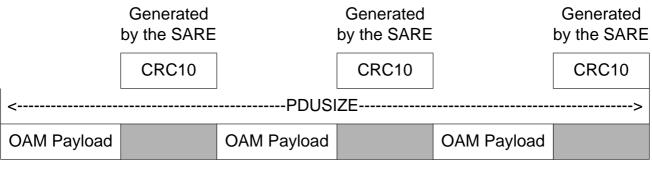

- VC level OAM cell detection and CRC-10 calculation

- Transmission and reception of ATM cells with bit rate up to 155 Mbit/s

- Interfaces

- UTOPIA Interface (Master/Slave modes) Level 1 according to newest standards; output buffer of 4 ATM cell depth in transmit direction for UTOPIA cell level handshake

- PCI bus interface to central packet memory/host

- 32-bit optional bus interface for local memory and/or for control of peripheral (e.g. PHY) devices

- Programmable clock frequency (maximum operating frequency 33 MHz)

| Туре     | Ordering Code | Package      |

|----------|---------------|--------------|

| PXB 4110 | Q67101-H6589  | P-FQFP-208-4 |

10

**CMOS**

## • System Bus Interface

- 32-bit PCI bus

- Output buffer for 128 double words for compensation of PCI bus latency ( $\approx$  27 µs)

- On-chip bus master DMA controller with packet scatter/gather capability for up to 64K simultaneous virtual connections

- Flexible linked list buffer structures with programmable buffer length

- Control Functions

- Control via PCI bus (Master/Slave modes)

## • Miscellaneous

- JTAG boundary scan according to IEEE 1149.1

- Built-in data path loop for test

- P-FQFP-208-4 package

- Low power, 3.3 V 0.5  $\mu$  CMOS technology

- 5 V PCI Interface

- 3.3 V UTOPIA Interface (5 V tolerant for 5 V environment)

- All other interfaces: 3.3 V compatible

## • Applications

- ATM End User equipment

- Motherboards for Multimedia PCs and Workstations

- Network Interface Cards (NICs) for Workstations/PCs and Servers

- Routers and Gateways; SMDS networks

- ATM Hubs and Switches

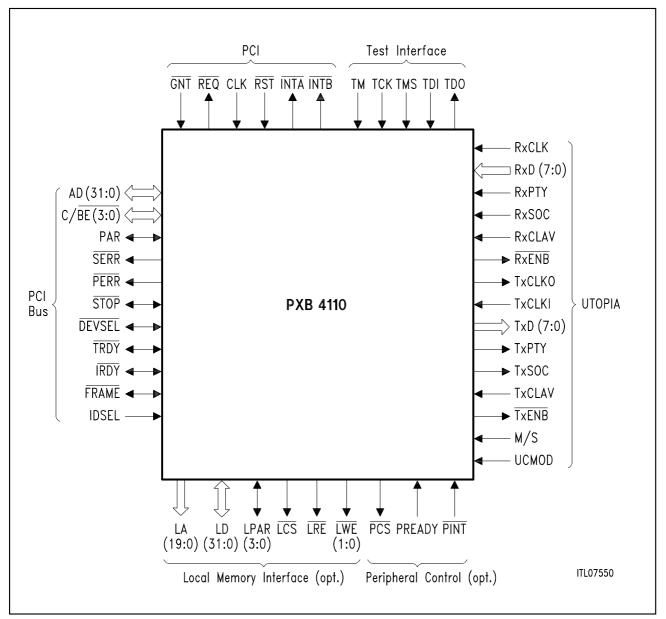

## 1.2 Logic Symbol

Figure 1 PXB 4110 Segmentation and Reassembly Element Logic Symbol

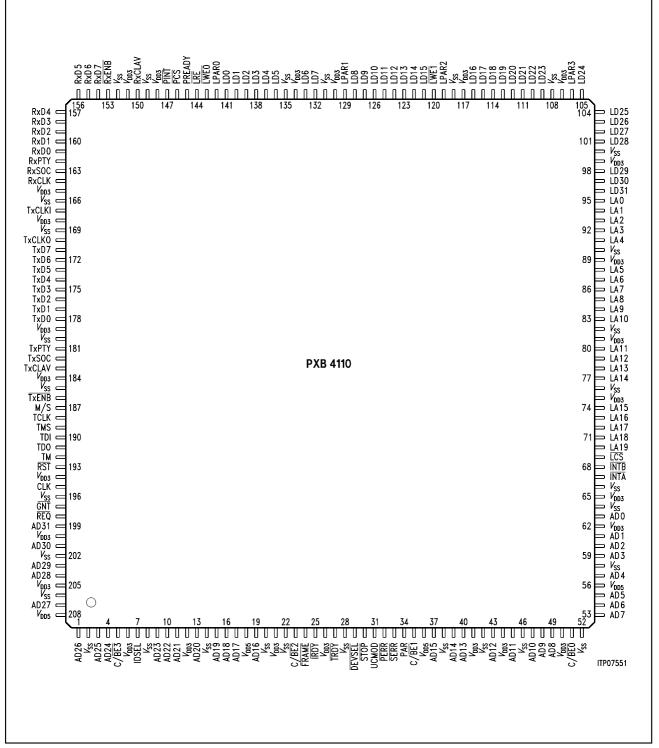

#### 1.3 Pin Configuration

(top view)

Figure 2 SARE Pin Configuration

### 1.4 Pin Definitions and Functions

#### **1.4.1** Parallel Host Interface

In **table 1**: The terms "Master" (M) and "Slave" (S) are sometimes used interchangeably with "initiator" or "target" respectively to refer to the SARE's role in a bus transaction; and (OD) in the Input/Output column indicates an Open Drain signal.

| Pin No.                                                                                                                                                                                                                                                 | Symbol                                                                                                                                                                                                                                           | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63, 61,         60, 59,         57, 55,         54, 53,         49, 48,         47, 45,         43, 40,         39, 37,         19, 17,         16, 15,         13, 11,         10, 9,         4, 3,         1, 207,         204, 203,         201, 199 | AD0, AD1,<br>AD2, AD3,<br>AD4, AD5,<br>AD6, AD7,<br>AD8, AD9,<br>AD10, AD11,<br>AD12, AD13,<br>AD14, AD15,<br>AD16, AD17,<br>AD18, AD19,<br>AD20, AD21,<br>AD20, AD21,<br>AD22, AD23,<br>AD24, AD25,<br>AD26, AD27,<br>AD28, AD29,<br>AD30, AD31 | I/O                     | Address/Data Bus<br>A bus transaction consists of an address<br>phase followed by one or more data phases<br>When SARE is Master, AD(31:0) are outputs<br>in the address phase of a transaction. During<br>the data phase, AD(31:0) remain outputs for<br>write transactions, and become inputs for<br>read transactions.When SARE is Slave,<br>AD(31:0) are inputs in the address phase of<br>a transaction. During the data phase,<br>AD(31:0) remain inputs for write<br>transactions, and become outputs for read<br>transactions. AD(31:0) are updated and<br>sampled on the rising edge of CLK. |

| 51,<br>35,<br>23,<br>5                                                                                                                                                                                                                                  | C/BE0,<br>C/BE1,<br>C/BE2,<br>C/BE3                                                                                                                                                                                                              | I/O                     | Command/Byte Enable<br>During the address phase of a transaction,<br>C/BE(3:0) define the bus command. During<br>the data phase C/BE(3:0) are used as Byte<br>Enables. The Byte Enables are valid for the<br>entire data phase and determine which byte<br>lanes carry meaningful data. C/BE0 applies<br>to byte 0 (lsb) and C/BE3 applies to byte 3<br>(msb).<br>When SARE is Master, C/BE(3:0) are<br>outputs. When SARE is Slave, C/BE(3:0) are<br>inputs.<br>C/BE(3:0) are updated and sampled on the<br>rising edge of CLK.                                                                      |

Table 1

Parallel Host Interface

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34      | PAR    | I/O                     | Parity<br>PAR is even parity across AD(31:0) and<br>C/BE(3:0). PAR is stable and valid one clock<br>after the address phase. PAR has the same<br>timing as AD(31:0) but is delayed by one<br>clock.<br>When SARE is Master, PAR is output during<br>address phase and write data phases. When<br>SARE is Slave, PAR is output during read<br>data phases.<br>Parity errors detected by the SARE are<br>indicated on PERR output.<br>PAR is updated and sampled on the rising<br>edge of CLK. |

| 24      | FRAME  | I/O                     | <b>Cycle Frame</b><br>FRAME indicates the beginning and duration<br>of an access. FRAME is asserted to indicate<br>a bus transaction is beginning. While<br>FRAME is asserted, data transfers continue.<br>When FRAME is deasserted, the transaction<br>is in the final phase.<br>When SARE is Master, FRAME is an output.<br>When SARE is Slave, FRAME is an input.<br>FRAME is updated and sampled on the<br>rising edge of CLK.                                                           |

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25      | IRDY   | I/O                     | Initiator Ready<br>IRDY indicates the bus master's ability to<br>complete the current data phase of the<br>transaction. It is used in conjunction with<br>TRDY. A data phase is completed on any<br>clock where both IRDY and TRDY are<br>sampled asserted. During a write, IRDY<br>indicates that valid data is present on<br>AD(31:0). During a read, it indicates the<br>master is prepared to accept data. Wait<br>cycles are inserted until both IRDY and<br>TRDY are asserted together.<br>When SARE is Master, IRDY is an output.<br>When SARE is Slave, IRDY is an input.<br>IRDY is updated and sampled on the rising<br>edge of CLK. |

| 27      | TRDY   | I/O                     | Target ReadyTRDY indicates a Slave's ability to completethe current data phase of the transaction.During a read, TRDY indicates that validdata is present on AD(31:0). During a write,it indicates the target is prepared to acceptdata.When SARE is Master, TRDY is an input.When SARE is Slave, TRDY is an output.TRDY is updated and sampled on the risingedge of CLK.                                                                                                                                                                                                                                                                      |

| 30      | STOP   | I/O                     | <b>STOP</b><br>STOP is used by a Slave to request the current Master to stop the on-going bus transaction.<br>When SARE is Master, STOP is an input.<br>When SARE is Slave, STOP is an output.<br>STOP is updated and sampled on the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                       |

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | IDSEL  |                         | Initialization Device Select<br>When SARE is Slave in a transaction, if<br>IDSEL is active in the address phase and<br>C/BE(3:0) indicates a register read or write,<br>the SARE assumes a read or write to a<br>configuration register. In response, the<br>SARE asserts DEVSEL in the subsequent<br>CLK period.<br>IDSEL is sampled on the rising edge of CLK.                                                                                                                                                                                                                      |

| 29      | DEVSEL | I/O                     | Device Select<br>When activated by a Slave, indicates to the<br>current bus master that the Slave has<br>decoded its address as the target of the<br>current transaction, i.e. that the address is<br>valid. If no bus slave activates DEVSEL<br>within six bus clock cycles, the Master<br>should abort the transaction.<br>When SARE is Master, DEVSEL is input. If<br>DEVSEL is not activated within six clock<br>cycles after an address is output on<br>AD(31:0), the SARE aborts the transaction<br>and generates an interrupt status.<br>When SARE is Slave, DEVSEL is output. |

| 32      | PERR   | O (OD)                  | Parity Error<br>When activated, indicates a parity error over<br>the AD(31:0) and C/BE(3:0) signals when<br>compared to the PAR input. It has a delay of<br>two CLK cycles with respect to AD and<br>C/BE, i.e. it is activated for the cycle<br>immediately following the corresponding<br>PAR cycle.<br>PERR is activated on the rising edge of CLK.                                                                                                                                                                                                                                |

| 33      | SERR   | O (OD)                  | <b>System Error</b><br>The SARE activates this signal for indicating<br>a fatal system error.<br>SERR is activated on the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 198     | REQ    | 0                       | <b>Request</b><br>This signal is used by the SARE to request<br>control of the PCI bus.<br>REQ is activated on the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                |

| 197     | GNT    |                         | <b>Grant</b><br>This signal is activated to grant control of the<br>PCI to the SARE in response to a bus<br>request via REQ. After GNT is activated, the<br>SARE may begin a bus transaction only after<br>FRAME has been deactivated.<br>GNT is sampled on the rising edge of CLK.                                                                                                                                                                                                   |

| 195     | CLK    | I                       | <b>Clock</b><br>Provides timing for all PCI transactions, the<br>DMA controller and the AAL processor.<br>Generally, all PCI signals are sampled and<br>output on the rising edge of CLK. The<br>maximum CLK frequency is 33 MHz.                                                                                                                                                                                                                                                     |

| 193     | RST    | I                       | <b>Reset</b><br>An active $\overline{RST}$ signal brings all PCI registers,<br>sequencers and signals into a consistent<br>state. All PCI output signals are driven to<br>their begin state.                                                                                                                                                                                                                                                                                          |

| 67      | INTA   | O (OD)                  | Interrupt Request A<br>When an interrupt status is active and the<br>interrupt source is unmasked, the SARE<br>activates this open-drain output. Examples<br>of interrupt sources are alarms, or events<br>pertaining to the DMA controller. SARE<br>deactivates INTA when the interrupt status is<br>acknowledged via an appropriate action<br>(e.g. specific register read) and no other<br>unmasked interrupt statuses are active.<br>INTA is activated on the rising edge of CLK. |

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 68      | ĪNTB   | O (OD)                  | Interrupt Request B<br>See above. The possible interrupt sources<br>(statuses) of the SARE may be programmed<br>to generate an interrupt on either INTA or<br>INTB (or none). This feature can be used to<br>assign interrupt sources e.g. in two groups of<br>different priorities (INTA: higher priority<br>interrupts; INTB: lower priority interrupts), as<br>determined via the software requirements.<br>INTB is activated on the rising edge of CLK. |

#### Table 1 Parallel Host Interface (cont'd)

### 1.4.2 UTOPIA Interface

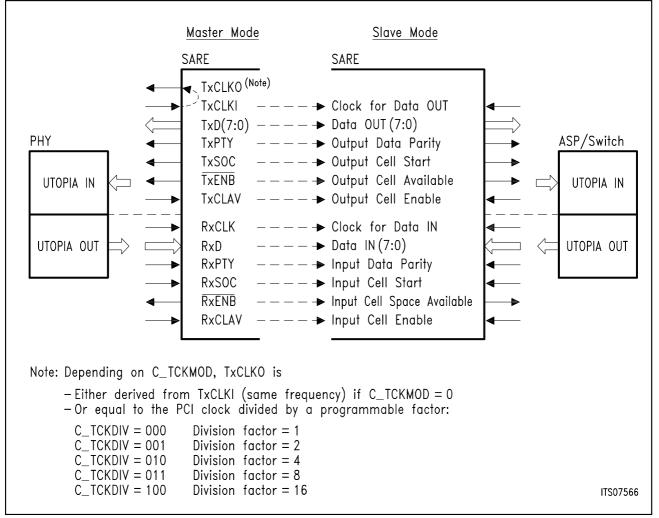

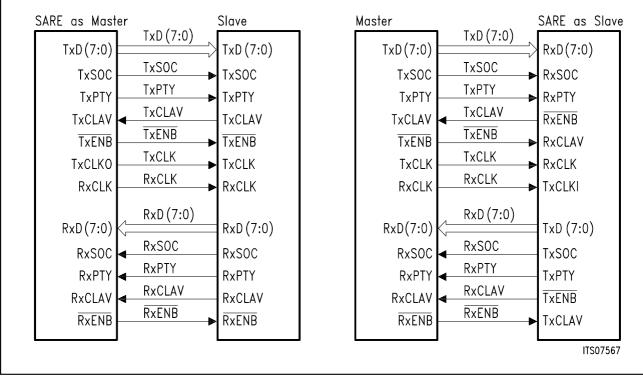

For the sake of convenience, the signals on the UTOPIA Interface are named according to their significance in the Master mode (NIC applications, i.e. the SARE is connected to a PHY device). In the case of the Slave mode (Switch/Hub) applications, the UTOPIA Interface should be configured (via the M/S pin) as a Slave with respect to clocking. Then the significance of the pins changes as follows:

| Master mode (signal name) | Function in Slave mode        |

|---------------------------|-------------------------------|

| RxCLAV                    | Transmit Enable               |

| RxENB                     | Transmit Cell Space Available |

| TxCLAV                    | Receive Enable                |

| TxENB                     | Receive Cell Available.       |

|                           |                               |

See table 2 for a description of the pins on the UTOPIA Interface.

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31      | UCMOD  | 1                       | In the case where the SARE operates as a<br>UTOPIA interface clock master, UCMOD<br>determines the mode of generation of the<br>UTOPIA TxCLK clock as follows:<br>If UCMOD is "low", the clock (TxCLKO output)<br>is derived from TxCLKI input (same<br>frequency). If UCMOD is "high", the clock<br>(TxCLKO output) is derived from the PCI clock<br>by division by a programmable factor. |

Table 2 UTOPIA Interface

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 167     | TxCLKI |                         | Transmit Clock In<br>Used to clock the UTOPIA Interface output<br>bus when the SARE operates as a UTOPIA<br>Interface Slave, e.g. when the SARE is<br>connected to an ATM Switch Preprocessor<br>ASP (hub applications). In the case where the<br>SARE operates as a UTOPIA Interface<br>Master, the master transmit clock on TxCLKO<br>may optionally be derived from the signal<br>provided on TxCLKI (e.g. this may be<br>connected externally to RxCLK). The signals<br>of the interface are evaluated with the rising<br>edge of this clock. |

| 170     | TxCLKO | 0                       | <b>Transmit Clock Out</b><br>Used to clock the UTOPIA Interface output<br>bus when the SARE operates as a UTOPIA<br>Interface Master (NIC applications). TxCLKO<br>is either derived from TxCLKI (with the same<br>frequency), or from the PCI clock (divided by a<br>programmable factor equal to 1, 2, 4, 8 or 16).<br>The signals of the interface are evaluated with<br>the rising edge of this clock.                                                                                                                                        |

| 164     | RxCLK  |                         | Receive Clock<br>Used to clock the UTOPIA Interface input bus.<br>It should be connected to the RxCLK line of<br>the UTOPIA Interface (according to UTOPIA<br>nomenclature) when the SARE operates as a<br>UTOPIA Interface Master (e.g. in NIC<br>applications). It should be connected to the<br>UTOPIA TxCLK line when the SARE operates<br>as a UTOPIA Interface Slave. Its maximum<br>frequency is 33 MHz.<br>The signals of the interface are evaluated with<br>the rising edge of this clock.                                              |

## Table 2 UTOPIA Interface (cont'd)

| Pin No.                                                     | Symbol                                                                       | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 161,<br>160,<br>159,<br>158,<br>157,<br>156,<br>155,<br>154 | RxD0,<br>RxD1,<br>RxD2,<br>RxD3,<br>RxD4,<br>RxD5,<br>RxD6,<br>RxD6,<br>RxD7 | 1                       | Receive Data<br>In NIC applications, this bus delivers the cells<br>from a PHY level device according to the<br>UTOPIA Interface specification. RxD(7) is the<br>most significant bit. (It is the first bit received<br>on an ATM serial interface.)<br>In ATM Switch/Hub applications, this bus<br>carries the cells from the switch (TxD bus<br>according to UTOPIA nomenclature).                                                                                                                                                                    |

| 162                                                         | RxPTY                                                                        | 1                       | <b>Receive Parity</b><br>Optional parity bit for RxD(7:0) bus. If used, it<br>delivers a bit value to complement the bits on<br>RxD(7:0) to an odd parity. Checking of parity<br>via the SARE may be disabled by software.                                                                                                                                                                                                                                                                                                                              |

| 163                                                         | RxSOC                                                                        | 1                       | <b>Receive Start of Cell</b><br>This signal is set to "high" when the first octet<br>of a cell is present on RxD(7:0) and "low"<br>otherwise.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 150                                                         | RxCLAV                                                                       |                         | Receive Cell Available<br>When the SARE operates as a UTOPIA<br>Interface Master (NIC applications). It is<br>influenced by two events. If the SARE enables<br>cell transfer by asserting RxENB and cells are<br>available, RxCLAV is asserted and transfer of<br>cells on RxD(7:0) is started. If no valid cells are<br>available, the RxCLAV is deactivated by the<br>PHY layer device.<br>Transmit Enable (TxENB, according to<br>UTOPIA nomenclature)<br>When the SARE operates as a UTOPIA<br>Interface Slave (in ATM Switch/Hub<br>applications). |

| Pin No.                                                     | Symbol                                                              | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------------------------------------------|---------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 153                                                         | RxENB                                                               | 0                       | Receive Enable<br>When the SARE operates as a UTOPIA<br>Interface Master (NIC applications). This<br>signal is deasserted by the SARE if it is not<br>ready to accept more data. In this case the<br>other device should stop data transfer on<br>RxD(7:0) after a delay of one clock cycle.<br>Transmit Cell Space Available (TxCLAV,<br>according to UTOPIA nomenclature)<br>When the SARE operates as a UTOPIA<br>Interface Slave (in ATM Switch/Hub<br>applications). |  |

| 178,<br>177,<br>176,<br>175,<br>174,<br>173,<br>172,<br>171 | TxD0,<br>TxD1,<br>TxD2,<br>TxD3,<br>TxD4,<br>TxD5,<br>TxD6,<br>TxD7 | 0                       | Transmit Data<br>In NIC applications, this bus delivers the cells<br>from SARE to a PHY level device according to<br>the UTOPIA interface specification. TxD(7) is<br>the most significant bit. (It is the first bit<br>transmitted on an ATM serial interface.)<br>In ATM Switch/Hub applications, this bus<br>carries the cells towards the switch (RxD bus<br>according to UTOPIA nomenclature).                                                                       |  |

| 181                                                         | TxPTY                                                               | 0                       | <b>Transmit Parity</b><br>Parity bit for $TxD(7:0)$ bus. It delivers a bit<br>value to complement the bits on $TxD(7:0)$ to<br>an odd parity.                                                                                                                                                                                                                                                                                                                             |  |

| 182                                                         | TxSOC                                                               | 0                       | <b>Transmit Start of Cell</b><br>This signal is set to "high" when the first octet<br>of a cell is present on TxD(7:0) and "low"<br>otherwise.                                                                                                                                                                                                                                                                                                                            |  |

## Table 2 UTOPIA Interface (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

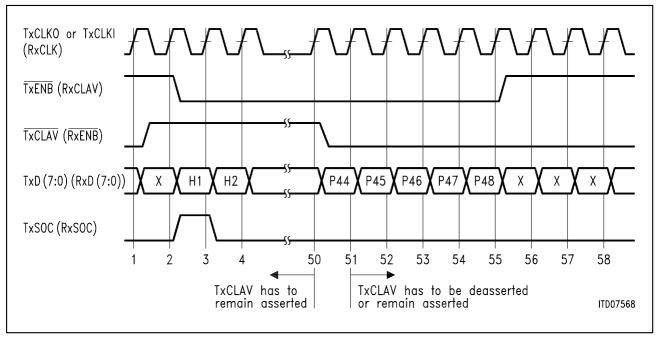

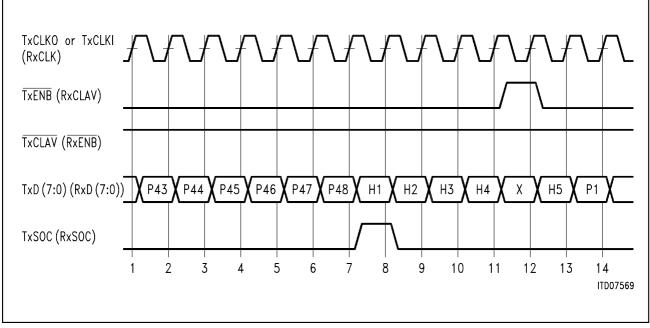

| 183     | TxCLAV |                         | Transmit Cell Space Available<br>When the SARE operates as a UTOPIA<br>Interface Master (NIC applications). In cell<br>level handshake this signal is activated by the<br>device that receives TxD(7:0) if there is<br>enough storage space for a whole cell. Then<br>the SARE transfers a whole cell in 53 cycles<br>without a break. If the receiving device cannot<br>accept a subsequent cell, it should deassert<br>TxCLAV at the latest 4 cycles before the end<br>of the cell (with the clock edge that outputs the<br>44th octet). Otherwise the SARE is allowed to<br>send the next cell without pause (back-to-back<br>cell transmission).<br>Receive Enable (RxENB, according to<br>UTOPIA nomenclature)<br>When the SARE operates as a UTOPIA<br>Interface Slave (in ATM Switch/Hub<br>applications). |

| 186     | TxENB  | 0                       | Transmit EnableWhen the SARE operates as a UTOPIAInterface Master (NIC applications). It isasserted if valid data is transferred onTxD(7:0).Receive Cell Available (RxCLAV, accordingto UTOPIA nomenclature)When the SARE operates as a UTOPIAInterface Slave (in ATM Switch/Hubapplications).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 187     | M/S    | 1                       | Master/Slave<br>When M/S is "low", the SARE operates as a<br>UTOPIA Interface Master (NIC applications).<br>When M/S is "high", the SARE operates as a<br>UTOPIA interface Slave (in ATM Switch/Hub<br>applications).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## Table 2 UTOPIA Interface (cont'd)

#### 1.4.3 Local Memory/Control Interface

The Local Memory Interface is used by the SARE to store and retrieve descriptors and context data of the currently active virtual connections when their number exceeds the internal storage capacity of the SARE (typically, 60 links in segmentation and reassembly). The SARE operates as the bus master.

The Local Memory Interface can also be used to control peripheral devices via the PCI Interface, such as PHY devices. This allows for the implementation of NIC applications without a local controller on the NIC.

See table 3 for Local Memory and Control Interface pin descriptions.

| Pin No.                                                                                                                                                                                                                                                           | Symbol                                                                                                                                                                                                                                           | Input (I)<br>Output (O) | Function          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------|

| 95, 94, 93,<br>92, 91, 88,<br>87, 86, 85,<br>84, 83, 80,<br>79, 78, 77,<br>74, 73, 72,<br>71, 70                                                                                                                                                                  | LA0, LA1, LA2,<br>LA3, LA4, LA5,<br>LA6, LA7, LA8,<br>LA9, LA10, LA11,<br>LA12, LA13, LA14,<br>LA15, LA16, LA17,<br>LA18, LA19                                                                                                                   | 0                       | Local Address Bus |

| 141, 140,         139, 138,         137, 136,         133, 132,         128, 127,         126, 125,         124, 123,         122, 121,         116, 115,         114, 113,         112, 111,         105, 104,         103, 102,         101, 98,         97, 96 | LD0, LD1,<br>LD2, LD3,<br>LD4, LD5,<br>LD6, LD7,<br>LD8, LD9,<br>LD10, LD11,<br>LD12, LD13,<br>LD14, LD15,<br>LD16, LD17,<br>LD16, LD17,<br>LD20, LD21,<br>LD20, LD21,<br>LD22, LD23,<br>LD24, LD25,<br>LD26, LD27,<br>LD28, LD29,<br>LD30, LD31 | I/O                     | Local Data Bus    |

Table 3Local Memory and Control Interface

## SIEMENS

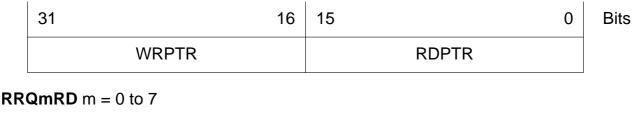

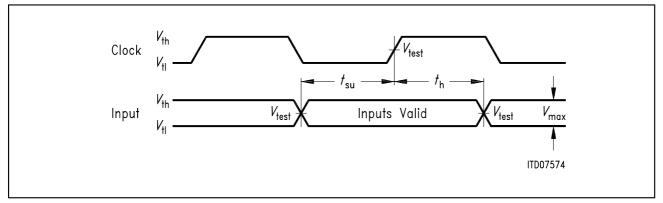

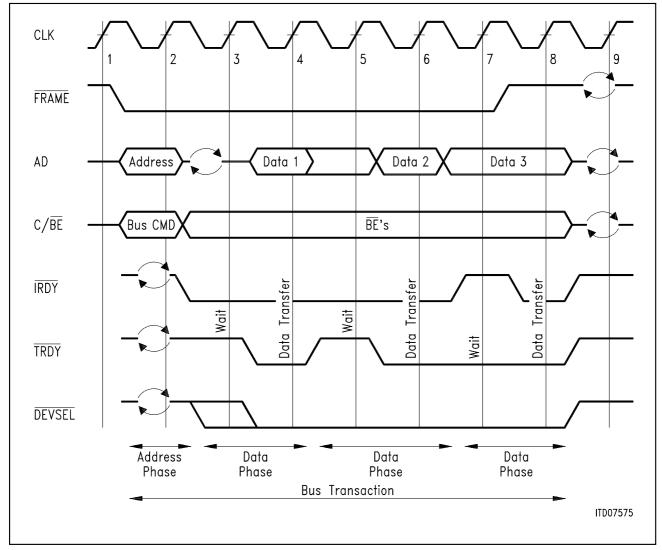

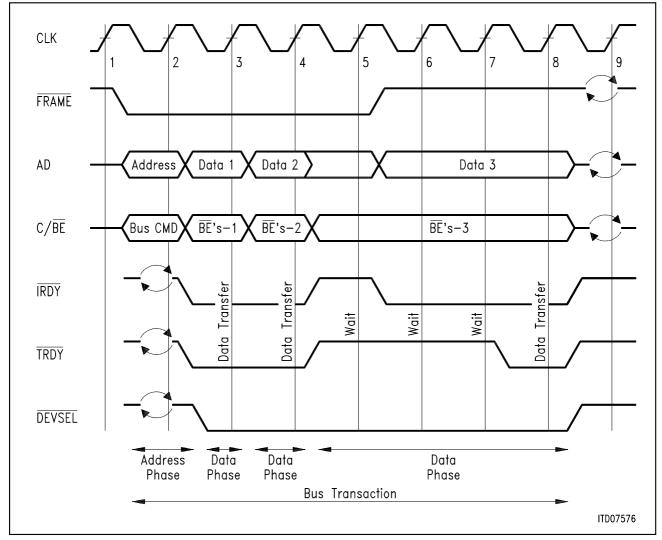

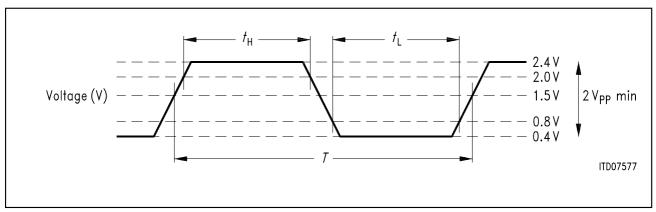

#### Overview