# Four Digit Counter / Display Drivers

#### **FEATURES**

- Minimum interface required to drive most common types of LED, fluorescent, seven segment displays

- Large output current capability on seven segment outputs, typically 25mA with 1V drop

- Fully synchronous up/down counting operation

- Look ahead carry for error free outputs when reversing count direction

- Internal oscillator needing no external components for operating the digit select counter

- Four digit select outputs with inversion control for display driving flexibility

- Multiplexed BCD outputs and serial output from storage register is available

- TTL/DTL compatible on inputs and outputs

- Blanking action of Reset Input

- Counting rate up to 600 kHz

# DESCRIPTION

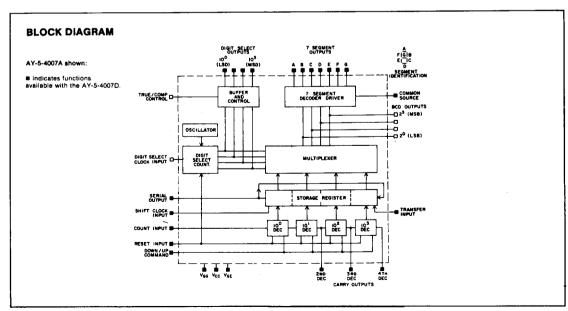

The Four Digit Counter Display Driver is an LSI subsystem designed for application in counting display systems such as frequency counters, digital voltmeters, digital timers, event counters using 7 segment numeric displays. It contains a 4 decade up/down synchronous BCD counter, a storage register, multiplexing circuits, internal oscillator for digit selection and 7 segment decoder to count and display up to 9999.

Built-in control circuits provide flexibility of use with a minimum of external components.

The device is constructed on a single monolithic chip using

MTNS P-channel enhancement mode transistors.

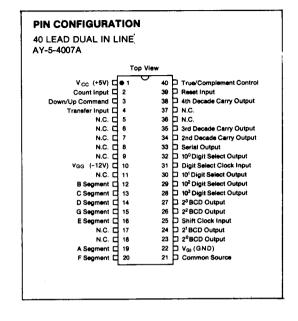

AY-5-4007A, available in 40 Lead Dual In Line package, allows for all available functions.

The AY-5-4007 and AY-5-4007D incorporate the most commonly used features in 24 Lead Dual in Line packages.

#### PIN CONFIGURATIONS 24 LEAD DUAL IN LINE 24 LEAD DUAL IN LINE AY-5-4007 AY-5-4007D Top View Top View V<sub>CC</sub> (+5V) □ 1 Count Input □ 2 Down/Up Command □ 3 Transfer Input □ 4 V<sub>GC</sub> (-12V) □ 5 B Segment □ 6 C Segment □ 7 V<sub>CC</sub> (+5V) □ ●1 Count Input □ 2 Down/Up Command □ 3 24 Reset Input 23 4th Decade Carry Output 22 3rd Decade Carry Output 24 True/Complement Control 23 Reset Input 22 4th Decade Carry Output Transfer Input 4 V<sub>GG</sub> (-12V) 5 B Segment 6 C Segment 7 21 10º Digit Select Output 20 10º Digit Select Output 21 2 2nd Decade Carry Output 20 3 Serial Output 19 10<sup>2</sup> Digit Select Output 18 10<sup>3</sup> Digit Select Output 19 100 Digit Select Output 18 101 Digit Select Output C Segment 7 D Segment 8 G Segment 9 E Segment 10 A Segment 11 F Segment 12 17 23 BCD Output D Segment 8 17 102 Digit Select Output G Segment 9 E Segment 10 A Segment 11 F Segment 12 16 10<sup>3</sup> Digit Select Output 15 Shift Clock Input 16 22 BCD Output 15 2 BCD Output 14 2ºBCD Output 13 V<sub>GI</sub> (GND) 14 V<sub>G</sub> (GND) 13 Common Source NOTE: For AY-5-4007D, True/Complement control is internally connected to logic "0" level.

# **PIN FUNCTIONS**

| Name                                                                                                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| COUNT INPUT                                                                                                 | Count Input operates the decade counters synchronously on the positive going edges (logic '0' to '1' transitions).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| RESET INPUT                                                                                                 | When this input goes to a logic '1' it resets the decade counters to 0000, forces the digit select counter to the MSD position and the Digit Select Outputs to 'not active' logic levels to blank the display. It must be present for a minimum of 10 usec.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| DOWN/UP COMMAND                                                                                             | The count direction depends upon the logic level on the DOWN/UP Command input.  Logic '0' = Count UP. Logic '1' = Count DOWN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

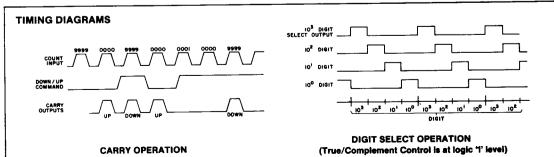

| 2ND DECADE CARRY OUTPUT   3RD DECADE CARRY OUTPUT   4TH DECADE CARRY OUTPUT                                 | Normally the Carry Outputs are at a logic '0' level; when activated a positive pulse is generated on the output line, which is identical with the Count Input causing the carry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| TRANSFER INPUT                                                                                              | Placing the Transfer Input at a logic '1' allows transfer of data from the decade counters to the storage register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| SHIFT CLOCK INPUT                                                                                           | This input is used to apply clock pulses to the storage register for serial shift operation. Normally Shift Clock is maintained at a Logic '1' and negative pulses are necessary to perform shift operation. Actual shifting of storage register data is done on the second edge (positive going) of each clock pulse. A Pull-up resistor is internally provided for the Shift Clock Input so that this line, if not used, may be left floating. Since the storage register is quasi-static in serial shift operation the width of negative pulses (at logic '0') has to be limited to 20 µsec. During serial shift operation the Transfer input must be at a logic '0'. |  |  |  |  |  |  |  |

| SERIAL OUTPUT                                                                                               | This is the serial output of the storage register. When serial shift operation is not performed the Serial Output is the least significant bit of the least significant digit of the storage register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 10º DIGIT SELECT OUTPUT (LSD) 10¹ DIGIT SELECT OUTPUT 10² DIGIT SELECT OUTPUT 10³ DIGIT SELECT OUTPUT (MSD) | These outputs provide sequentially an active logic level (logic '1' if the True/Complement Control is at a logic '1'; logic '0' if the True/Comlement Control is at a logic '0'), to specify which of the corresponding digits is selected and displayed, the remaining 3 Outputs being 'not active'. All the Digit Select Outputs are forced to a 'not active' logic level as long as the Reset Input is active.                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 2º BCD OUTPUT(LSB) 2¹ BCD OUTPUT 2² BCD OUTPUT 2³ BCD OUTPUT(MSB)                                           | These outputs provide the Binary Coded Decimal representation of the digit being selected and displayed by the multiplexer. The truth table shows BCD Codification of these outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

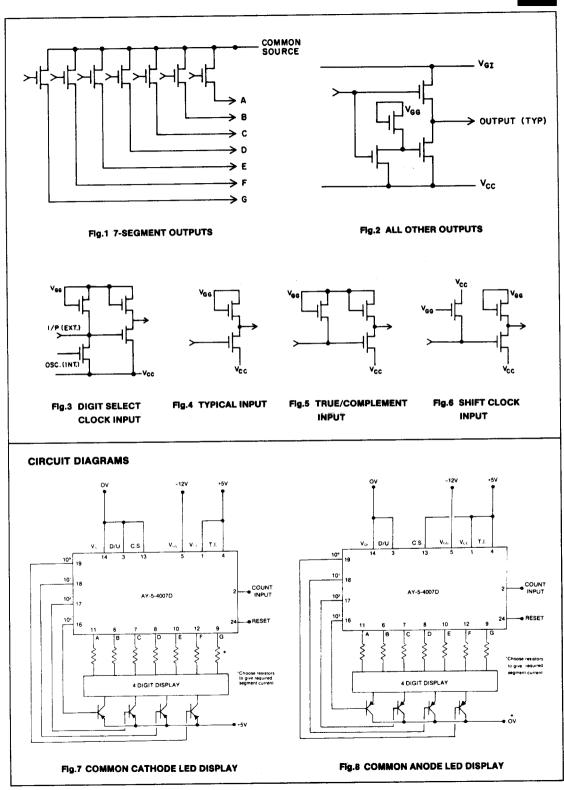

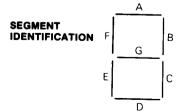

| "A" TO "G" SEGMENT                                                                                          | These outputs are programmed according to the truth table. Each output terminal is actually connected to the drain of the corresponding output transistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| COMMON SOURCE                                                                                               | This is the common of the seven segment output transistors. When not externally available the corresponding terminal is internally tied to Vgi (0V) line. It may be connected to any voltage between Vss and VDD according to requirements.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| TRUE/COMPLEMENT CONTROL                                                                                     | This input controls the polarity of the Digit Select Outputs active logic level. When the TRUE/COMPLEMENT Control is at a logic '1', active level for the Digit Select Outputs is a logic '1', when at a logic '0' active level is a logic '0'.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| DIGIT SELECT CLOCK INPUT                                                                                    | An external signal applied to this terminal overrides the internal oscillator. When the internal oscillator is used, this terminal must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

# **ELECTRICAL CHARACTERISTICS**

# Maximum Ratings \*

Voltage on any pin with respect to Vcc. -20 to +0.3V Storage temperature range. -65°C to +150°C Ambient operating temperature range 0°C to +70°C

# Standard Conditions (unless otherwise noted)

$V_{\rm CC} = +5.0 \pm 0.5 V$   $V_{\rm GG} = -12 V \pm 1 V \text{ OR } -7.0 V \pm 0.5 V$

$V_{GI} = 0V$  Operating Temperature (T<sub>A</sub>) 0°C to +70°C

\*Exceeding these ratings could cause permanent damage. Functional operation of this device at these conditions is not implied—operating ranges are specified below.

|                                                                                    | $V_{GG} = -12V \pm 1V$                                      |                              |                                                         | $V_{GG} = -7V \pm 0.5V$                                     |                                   |                                                          |                                |                                                                                                                                                 |  |

|------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------|---------------------------------------------------------|-------------------------------------------------------------|-----------------------------------|----------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Characteristic                                                                     | Min                                                         | Тур Мах                      |                                                         | Min                                                         | Тур**                             | Max                                                      | Units                          | Conditions                                                                                                                                      |  |

| Inputs Logic '0' Logic '1' Capacitance Leakage Repetition Rate Pulse Width Tr & Tf | V <sub>GG</sub><br>V <sub>cc</sub> =1.5<br>-<br>D.C.<br>0.7 |                              | +0.8<br>V <sub>cc</sub> +0.3<br>10.0<br>5.0<br>600<br>- | V <sub>GG</sub><br>V <sub>CC</sub> =1.5<br>-<br>D.C.<br>1.0 | -<br>-<br>-<br>-                  | +0.8<br>V <sub>cc,</sub> +0.3<br>10.0<br>5.0<br>350<br>- | Volts Volts pF                 | See Fig. 4  V <sub>IN</sub> = V <sub>CC</sub> f= 1MHz  V <sub>IN</sub> - V <sub>CC</sub> = -10V at 25° C  Square Wave  Pulse either high or low |  |

| True/Complement/<br>Control Input<br>Input Current                                 | 10<br>10                                                    | 40<br>25                     | 100<br>50                                               | 10<br>10                                                    | -                                 | 50<br>25                                                 | μΑ<br>μΑ                       | $V_{IN} = V_{CC}$<br>$V_{IN} = V_{GI}$ See Fig. 5                                                                                               |  |

| Digit Select Clock<br>Input Current<br>Internal Freg.                              | 10<br>50<br>1.0                                             | 60<br>250<br>2.0             | 150<br>1600<br>4.0                                      | 5<br>50<br>1.0                                              | 25<br>150<br>2.0                  | 75<br>1000<br>4.0                                        | μΑ<br>μΑ<br>kHz                | $V_{IN} = V_{CC}$ (Sink)<br>$V_{IN} = V_{GI}$ (Source) See Fig.[3]                                                                              |  |

| External Freq.—Data only Display                                                   |                                                             | -                            | 100<br>15                                               | D.C.<br>D.C.                                                | -<br>-                            | 50<br>7                                                  | kHz<br>kHz                     | Display Duty Cycle 25%                                                                                                                          |  |

| Shift Clock<br>Frequency<br>Pulse Width<br>Input Current                           | D.C.<br>0.4<br>20                                           | -<br>-<br>100                | 1<br>1000<br>400                                        | D.C.<br>0.5<br>10                                           | 30                                | 0.8<br>1000<br>200                                       | MHz<br>μsec<br>μA              | See functional description $V_{\rm IN} = V_{\rm GI}$ (See Fig. 6)                                                                               |  |

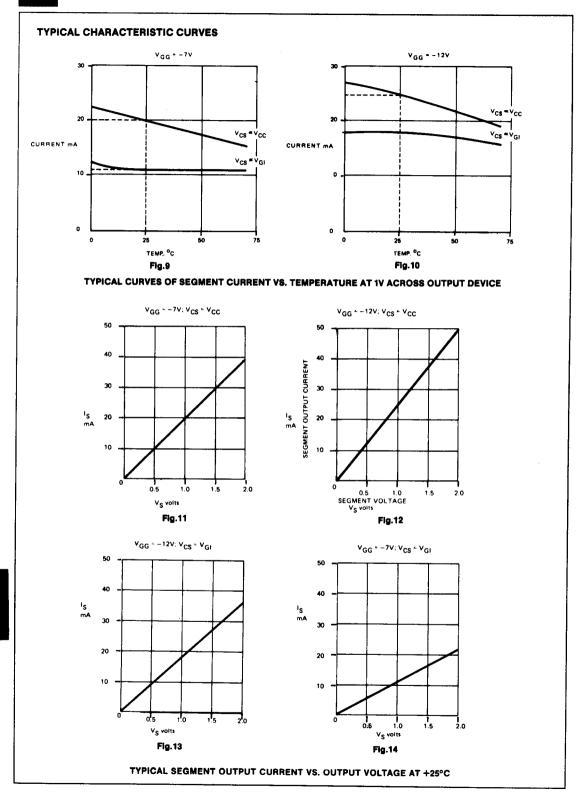

| Outputs—7 Segment<br>(See Note 2)<br>Leakage Current<br>Device on Current          | -<br>15                                                     | _<br>25                      | 10<br>45                                                | -<br>12                                                     | _<br>20                           | 10<br>35                                                 | μA<br>mA                       | $V_{OUT}$ — $V_{CC} = -10V$ at 25°C<br>$V_{CS}$ — $V_{OUT} = +1.0V$ at 25°C,<br>$V_{CS} = V_{CC}$                                               |  |

| Device on Current                                                                  | 12                                                          | 18                           | 27                                                      | 7                                                           | 11                                | 17                                                       | mA                             | $V_{CS} - V_{OUT} = -1.0V$ at 25°C,<br>$V_{CS} = V_{GI}$                                                                                        |  |

| Power Dissipation (per segment at 25°C)                                            | -                                                           | -                            | 200                                                     | -                                                           | -                                 | 200                                                      | mW                             | See Note 1 & Fig.fl                                                                                                                             |  |

| Other Outputs Logic '0' Logic '1' Propagation Delay                                | -<br>V <sub>cc</sub> –1.0<br>-                              | 0.2<br>V <sub>cc</sub> -0.65 | 0.4<br>-<br>1.0<br>1.5                                  | V <sub>cc</sub> -1.0                                        | 0.3<br>V <sub>cc</sub> –0.65<br>- | 0.4<br>-<br>1.5<br>2.0                                   | Volts<br>Volts<br>μsec<br>μsec | $I_{OL} = 1.6$ mA with 10pF load $I_{OL} = 50 \mu$ A Carry Output $\{$ Serial Output $\}$                                                       |  |

| Tr, Tf<br>Rise, Fall Times                                                         | -                                                           | 0.15                         | 0.3                                                     | -                                                           | 0.3                               | 0.6                                                      | μsec                           |                                                                                                                                                 |  |

| Power<br>lgg                                                                       | -                                                           | 25                           | 40                                                      | -                                                           | 13                                | 20                                                       | mA                             | (V <sub>cc</sub> to V <sub>GG</sub> )                                                                                                           |  |

<sup>\*\*</sup>Typical values are at +25°C and nominal voltages.

NOTES:

2 See also Typical 7-Segment Output Curves, Figs. 9, 11, & 13 (-12V ±1V) See also Typical 7-Segment Output Curves, Figs. 10, 12, & 14 (-7V ±0.5V)

<sup>1.</sup> Derate Power Linearly to 100mW at 70°C.

# **OPERATION**

# **Decade Counters**

The four decade counters are synchronously operated on the positive going edges of the Count Input; a single DOWN/UP Command controls the direction of counting. The edge-triggered structure of the master-slave flip-flops allows the count direction to be changed between count pulses at either Count Input level. A Reset Input resets decade counters to 0000.

Carry outputs are provided at the 2nd, 3rd and 4th decade; these outputs are activated when an overflow (in counting up) or an underflow (in counting down) condition exists in the corresponding decade counter. The carry output pulse is the same as the Count input pulse causing the carry.

The look ahead design of the carry stages gives error free outputs when reversing the count direction.

#### Storage Register

Data in the decade counters is transferred to the storage register under control of the Transfer Input signal. The Transfer Input may be connected to a logic '1' for a continuous transfer and display operation.

The Storage register may also be operated as a parallel-in serialout shift register. In this case clock pulses are to be provided to Shift Clock Input, the serial content of storage register is available on the Serial Output line, and recirculated back to the first stage input. A train of 16 clock pulses is needed to extract the full content of the register, least significant bit of least significant digit first. When operating the storage register serially, Transfer input is to be kept at a logic '0'.

# **Digit Select Counter and Multiplexer**

The digit select counter is driven by a built in oscillator which

requires no external components. The internal oscillator can be overridden by applying an external signal to the Digit Select Clock Input.

The digit select counter controls the multiplexer to route information from storage register to the 7 segment decoder drivers and to the BCD Outputs.

The counter scans from MSD (10³ digit) to LSD (10° digit). Each of the four Digit Select Outputs is sequentially activated when the corresponding digit is selected and displayed.

The Digit Select counter is forced to MSD position and Digit Select Outputs are forced to 'not active' logic levels as long as Reset Input is active. This feature blanks the display when the device is being reset. The True/Complement Control inverts the Digit Select Outputs active logic level for flexibility of output interface circuitry.

Internal delay logic ensures that both 7 segment outputs and BCD outputs are valid before activation of the corresponding Digit Select Output to avoid "ghost images".

7 Segment Decoder Driver

The 7 segment decoder drivers consist of very low impedance output transistors (typically 40 ohms) to minimize external inter- accomponents when driving 7 segment displays such as LEDs, fluorescents, incandescents, etc.

The 7 Segment Outputs are the drains of the corresponding output transistors, these outputs are programmed according to the truth table below. A Common Source terminal is also available to increase flexibility of use.

| DIGIT |     | 7 SEG | MENT | UTPUT | BCD OUTPUT |   |                       |            |          |           |    |

|-------|-----|-------|------|-------|------------|---|-----------------------|------------|----------|-----------|----|

| DIGIT | A B | С     | D    | E     | F          | G | MSB<br>2 <sup>3</sup> | <b>2</b> ² | 21       | LSB<br>2º |    |

| 0     | •   | •     | •    | *     |            |   | -                     | 0          | 0        | 0         | 0  |

| 1     | -   | •     | •    | _     | -          | _ | _                     | 1 6        | Ô        | ñ         | 1  |

| 2     | *   | •     | -    |       | *          | _ |                       | ň          | ñ        | 1         | 'n |

| 3     | •   | •     | •    | *     | -          | _ | *                     | ١٠         | ň        |           | •  |

| 4     | _   |       | •    | _     | _          |   |                       | ١          | 1        | ,         | ,  |

| 5     | •   | -     | •    | •     | _          |   |                       | 1 6        | 4        | 0         | •  |

| 6     | *   | _     |      |       | •          |   |                       | ١،         | \ \      | 4         | ,  |

| 7     | •   | •     |      | _     |            |   |                       | 1 %        | <u> </u> | !         | Ü  |

| a     |     | *     |      |       | -          | - | - :                   | 0          | 1        | 1         | 1  |

| اة    |     |       |      |       |            | - | -                     | 1          | 0        | 0         | 0  |

### LEGEND:

- \* output transistor ON

- output transistor OFF

- 0 logic '0'

- 1 logic '1'

7 SEGMENT AND BCD OUTPUTS TRUTH TABLE