# gmB135 Data Sheet

(Bridge 135)

## **DAT0019C**

(Date:10/13/99)

Genesis Microchip Inc. believes the information contained in this document to be accurate. However, this information is subject to change without any notice. Genesis Microchip Inc. does not assume any responsibility for its use, nor for infringement of patents or any other rights of third parties. This document implies no license under patents or copyrights. Trademarks in this document belong to their respective companies.

#### **Copyright Notice**

This manual is copyrighted. All rights are reserved. This document may not, in whole or part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior written consent from Genesis Microchip Inc

#### Genesis Microchip Inc.

165 Commerce Valley Dr. West, Thornhill, ON Canada L3T 7V8 Tel: (905) 889-5400 Fax: (905) 889-0035

1871 Landings Drive, Mountain View, CA, USA 94043 Tel: (650) 428-4277 Fax (650) 428-4288

www.genesis-microchip.com / info@genesis-microchip.on.ca

Revision History:

- January, 1999 (First publication)

- March, 1999 (Update information)

- June, 1999 (New Format, Pin Diagram Orientation, Pin Assignment Corrections)

- July, 1999 (Added Related Documents)

- October, 1999 (Updated pin diagram on page 7 to match the pin descriptions)

#### Related Documents

- DSR-0019 (gmB135 Register Specification)

- SED-0694 (gmB135 Evaluation Board)

- MSD-0061 (gmB135 Stepping Infomation)

**Table of Contents** Chapter Page 5 **General Description** 1. 5 1.1 Summary 1.2 Features 5 1.3 Pin Diagram 7 8 1.4 Pin Description 1.5 System-Level Implementation 18 1.6 Operating Modes gmB135 20 21 1.7 Input Video Mode Support 2. **Functional Block Description.** 22 23 2.1 Input Data Capture Block 23 2.1.1 Input ports 2.1.1.a Analog input ports 24 24 2.1.1.b Digital input port 1 2.1.1.c CCIR601 input port 24 2.1.2 Analog-to-digital converter 26 2.1.3 Clock recovery circuit 27 28 2.1.3.a Sampling phase adjustment 28 2.1.3.b Composite-sync support 2.1.4 Source Timing Generator Block 29 29 2.1.4.a Capture window definition 29 2.1.4.b Interlaced input support 2.2 Input Timing Measurement Block 30 2.2.1 Source timing measurement block 30 2.2.2 IRQ controller 31 2.3 Data Path Block 32 2.3.1 Input Gamma Table 32 2.3.2 Expander Interpolator and Coefficients 33 33 2.3.3 Output Gamma Table 2.3.4 RGB Offset 33 2.3.5 Panel Data Dither 33

## **GENESIS MICROCHIP**

| 2.3.6      | Panel Background Color                   | 33 |

|------------|------------------------------------------|----|

| 2.4 Pane   | Interface                                | 34 |

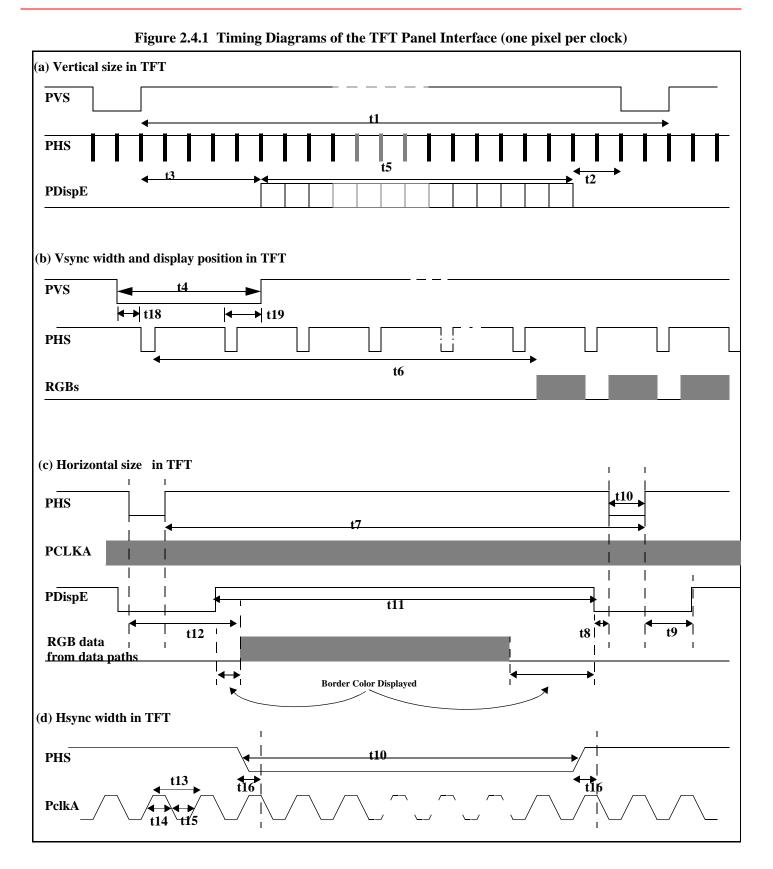

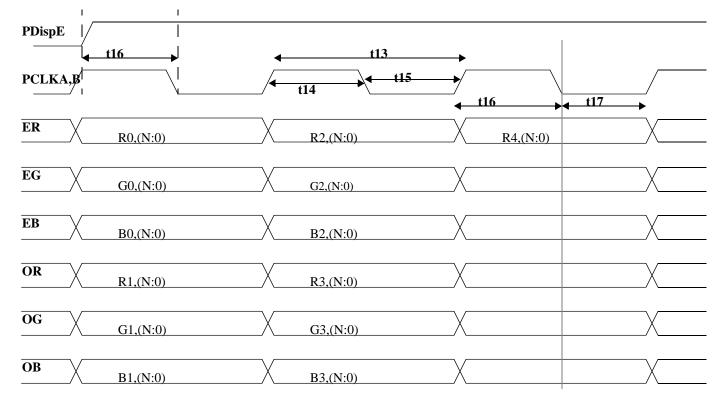

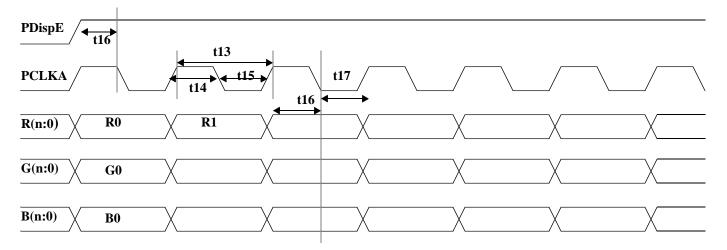

| 2.4.1      | TFT Panel Interface Timing Specification | 35 |

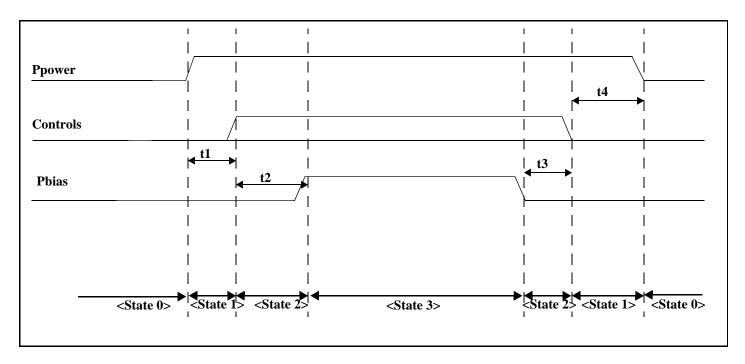

| 2.4.2      | TFT LCD Power Manager/Sequencer          | 39 |

| 2.4.3      | Panel Interface Drive Strength           | 40 |

| 2.5 Host   | Interface                                | 41 |

| 2.5.1      | Host interface pin connection            | 41 |

| 2.5.2      | gmB135 Serial Communication Protocol     | 42 |

| 2.6 OSD    | (On-Screen Display) Control              | 44 |

| 2.6.1      | On-Chip OSD                              | 44 |

| 2.6.2      | External OSD Support                     | 47 |

| 2.7 TCL    | K Input                                  | 50 |

| 2.8 Powe   | r Down Mode                              | 50 |

| Electrical | Characteristics                          | 51 |

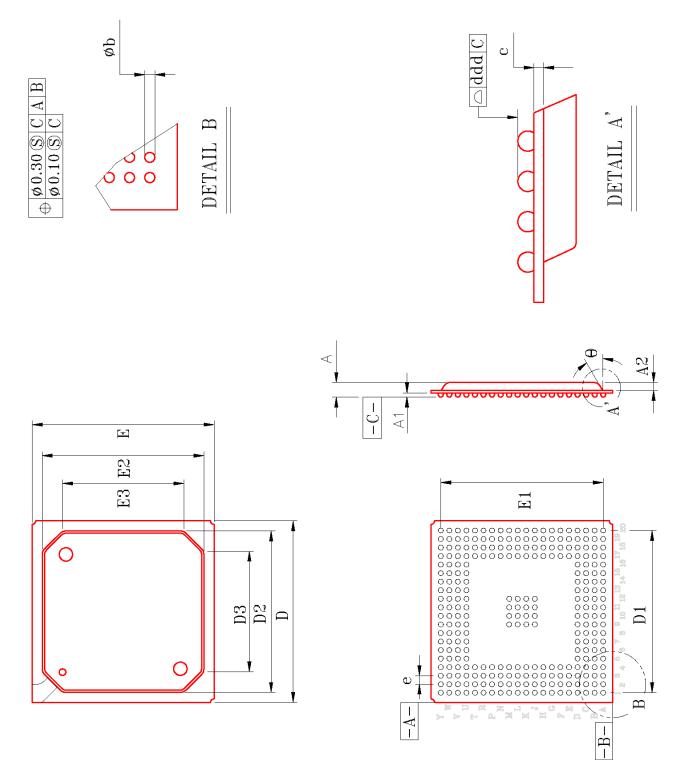

| Package D  | Dimension                                | 52 |

3. 4.

## **1. General Description**

## 1.1 Summary

Based on the B120 architecture, the gmB135 continues to simplify TFT LCD monitor design while providing "CRT-like" ease of use and uncompromising image quality. The gmB135's revolutionary scaling engine, capable of expanding any source resolution to a highly uniform and sharp image, combined with the critically proven integrated 8 bit triple-ADC and patented Rapid-Lock digital clock recovery system, create a uniquely cost effective solution. This rich feature set yields an extremely suitable match between the gmB135 and high end XGA and SXGA applications as illustrated in the figure on the next page.

## **1.2 Features**

#### **Integrated 135 Mhz Triple ADC**

- No additional components are needed for the three differential input ADCs which are capable of converting analog RGB data rates up to 135 Mhz.

- Flexible resolution support without frame buffer, from low resolution VGA and NEC98 modes up to 1280 x 1024 at 75 Hz. All color depths up to 24 bits per pixel are supported.

#### **Best of Class Scaling Engine**

- The gmB135 scaling engine algorithm is optimized to match TFT LCDs optical display response to provide uniform intensity across the entire image.

- Text font clarity and sharpness is enhanced by gmB135's  $(\sin\theta)/\theta$  re-scaling convolver.

#### **Multiple Video Format Input Support**

gmB135 interfaces to various video transmission formats to provide universal connectivity.

#### **Serial Digital Receivers**

- Serial digital receivers such as TMDS, LVDS or GVIF configured in either 1 pixel per clock or 2 pixels per clock connect directly to gmB135 to create a DFP, Plug and Display or DISM compatible monitor

#### **Two Analog Connector Inputs**

- Two separate sets of analog RGB inputs are internally multiplexed in gmB135. This allows the monitor to select RGB analog signals from two PCs.

## **Digital TV**

- CCIR601 input from a digital TV decoder. Using the gmB135 internal YUV-to-RGB conversion circuit and expansion circuit, the de-interlaced image is displayed on a progressive-scan TFT LCD.

#### **Integrated High Speed Digital Clock Recovery**

- Solid and completely stable locking to the source pixel clock is achieved in worst case test patterns.

- All clocks required for the gmB135 are generated from a single 50 Mhz reference oscillator.

#### Integrated RAM based OSD Controller

Customer defined fonts as well as standard fonts are supported in a fully featured integrated OSD controller. Complete "look and feel" and a familiar user interface can be maintained.

#### Automatic ADC Sampling Phase Optimization

Performs measurements so that firmware can automatically optimize the ADC sampling phase.

#### **Optimized Panel Clock**

- Panel clock frequency is optimized to support each mode at the lowest possible frequency. 1280 x 1024 x 75Hz is supported without driving the panel clock at 135 Mhz.

- Panel clock pad drive strength and clock to data skew are programmable to reduce EMI in the panel interface cable.

#### **TFT LCD Panel Support**

- All panel resolutions and sizes are supported up to SXGA

- Panel interface supports one or two pixel per clock, Sync only, DE only and Sync/DE composite.

#### Four Wire Interface to Microcontroller

Simple 4 wire serial interface connects directly to monitor microcontroller. Can be expanded to 7 wires by increasing data width from 1 to 4.

#### Standard 292 Pin BGA Package

256 signal/power/ground pins plus 36 (6 x 6) middle ground pins.

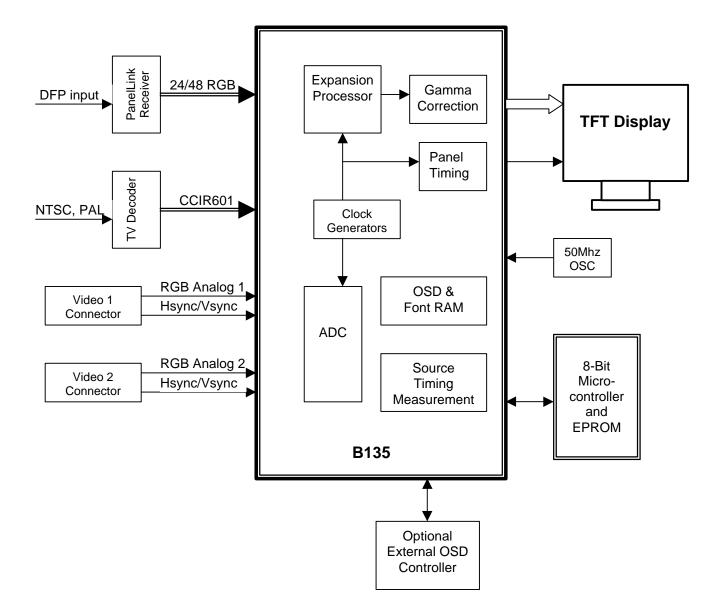

Figure 1.1.1 Single-Chip Solution for a Feature-Rich, Low-Cost Flat Panel Monitor

## 1.3 Pin Diagram

Bottom View of 292-pin BGA (including 6x6 middle pins).

| 8            | 19       | 18                | 17            | 5           | 5                       | 14                      | 13                             | 12                      | =         | 10       | φ        | œ             | 7             | Ø                       | Ch                              | 4               | ω              | N                        | -                                        |    |

|--------------|----------|-------------------|---------------|-------------|-------------------------|-------------------------|--------------------------------|-------------------------|-----------|----------|----------|---------------|---------------|-------------------------|---------------------------------|-----------------|----------------|--------------------------|------------------------------------------|----|

| ADC_<br>GND2 | VD01     | ADC_              | VEST          | ARSRV1      | INPUT2                  | GND A                   | VD0_                           | RES_<br>PAD             | HDATA_1   | HOATAUS  | EVREF    | EDIN_<br>PAD1 | EDIN_<br>PAD3 | MF8_2                   | MF8_5                           | MFB_8           | MFB_10         | MFB_11                   | HSYNCI                                   | Þ  |

| ADC_<br>VDD2 | GNDA     | BLUEZM            | BLUETM        | GREEN<br>2M | UREEN<br>1M             | RED2M                   | REDIM                          | VDDA                    | HDATA_0   | HDATA_2  | EHREF    | PADO PADO     | PAD2          | MPB_1                   | MFB_4                           | MFB_7           | MEB_9          | CONASA                   | HSYNC2                                   | 8  |

| ADC_<br>GND3 | GND-     | BLUE2P            | BLUETP        | GREEN<br>2P | GREEN<br>1P             | RED2P                   | REDIP                          | GNDA_                   | HFS       | HOLK     | ₫        | ECLK          | EFSW          | MFB_0                   | MFB_3                           | MFB_6           | VSS_CRT_       |                          | VSYNCI                                   | 0  |

| VD03         | VDDA     | GND ADC           | ADC_<br>BVDDA | GND_        | ADC_                    | GND ADO                 | RVDDA                          | CVDO                    | CVDO      | HE_VD0   | HE_VSS   | H€_VDD        | HE_VSS        | HE_VD0                  | HE_VSS                          | RVDR.           | VBUFC          | SUB_<br>RGNDA            | TCLK                                     | 0  |

| PVS          | PHS      | PBIAS             | PPWR          |             |                         |                         |                                |                         |           |          |          |               |               |                         |                                 | RGNDA           | DAC.           | DAO_                     | XTAL                                     | m  |

| PD_2         | PD_1     | PD_0              | PLVSS         |             |                         |                         |                                |                         |           |          |          |               |               |                         |                                 |                 | DVODA          | VBUFC_D                  | SUB_                                     | ч  |

| P0_5         | P0_4     | PD_3              | PLVDD         |             |                         |                         |                                |                         |           |          |          |               |               |                         |                                 | DGNDA           | SUB_           | SUB_                     | SUB_                                     | G  |

| 90_8         | P0_7     | PO_6              | PCLK2         |             |                         |                         | CVSS                           | CVSS                    | CVSS      | CVSS     | CVSS     | CVSS          |               |                         |                                 | SGNDA           | SVDOA          | VBUFC_S                  | DAC                                      | т  |

| PD_11        | PD_10    | 6 <sup>7</sup> 04 | PL_VSS        |             |                         |                         | CVSS                           | CVSS                    | CVSS      | CVSS     | CVSS     | CVSS          |               |                         |                                 | CVDD            | DAC_<br>SVDDA  | DAC_                     | DAC_                                     | ۷  |

| PD_14        | PD_13    | PD_12             | PL_VSS PL_VDD |             |                         |                         | CVSS                           | CVSS                    | CVSS      | CVSS     | CVSS     | CVSS          |               |                         |                                 | D_VD0           | PIXIN_0        | PIXIN_1                  | PIXIN_2                                  | ×  |

| PD_17        | PD_16    | PD_15             | CVDD          |             |                         |                         | CVSS                           | CVSS                    | CVSS      | CVSS     | CVSS     | CV55          |               |                         |                                 | D_VSS           | C_NIXIA        | PIXIN_4                  | VSYNC                                    | -  |

| PD_20        | PD_19    | PD_18             | CVDD          |             |                         |                         | CVSS                           | CVSS                    | CVSS      | CVSS     | CVSS     | CVSS          |               |                         |                                 | S_VSS           | PIXIN_S        |                          | CC HREP                                  | M  |

| P0_23        | P0_22    | P0,21             | PL_VD0        |             |                         |                         | CVSS                           | CVSS                    | CV3S      | CVSS     | CVSS     | CVSS          |               |                         |                                 | \$_VD0          | PIXIN_7        | BTNIXIA 9TNIXIA          | CC HREF HSYNC                            | z  |

| PD_26        | PD_25    | PD_24             | PL_VSS        |             |                         |                         |                                |                         |           |          |          |               | •             |                         |                                 |                 |                |                          | OCSOLK                                   | σ  |

| P0_29        | PO_28    | P0_27             | PCLK          |             |                         |                         |                                |                         |           |          |          |               |               |                         |                                 |                 | PIXIN_9 CC_VSS | PIXIN_10 PIXIN_12        | PIXIN_11                                 | סג |

| PD_32        | PD_31    | PD_30             | PD€           |             |                         |                         |                                |                         |           |          |          |               |               |                         |                                 | DĻVSS           | PIXIN_13       |                          | PIXIN_15                                 | ٦  |

| PD_36        | PD_35    | PD_34             | PD_33         | PSCAN       | PLOO_23                 | CVDD                    | DL'VDD                         | PLOO_1                  | CVDD      | DLVSS    | CVDD     | CVIDD         | PLOCEX        | DI_VDD                  | PLOE_1                          | PLOELO          | PLDE           | PIXIN_14 PLVSYNC_ PLOE_5 | COSCLK PIXIN_11 PIXIN_15 PLHSYNC- PLCE_1 | c  |

| PD_39        | PD_38    | PD_37             | PLVDD         | STI_TMI     | 1.00                    |                         | PLO0_                          | FLOO_                   | PLOO_9    | PLOO_6   | PLOO_3   | PLOO_0        | PLOE_21       | PLOE                    | PLOE                            |                 | PLOE_8         | - PLOE                   | - PLOE                                   | <  |

| PO_42        | 8 P0_41  | 7 PD_40           | D PLVSS       | N STLINZ    | 2 PLQO                  | PLOO_                   | 16 PLOO                        | PLOO_13 PLOO_12 PLOO_11 | 8 PLOO_8  | 6 PLOO_5 | 3 PL00_2 | 0 PLOE_23     | 21 PLOE_20    | 8 PLOE                  | 14 PLOE                         | PLOE_11 PLOE_10 | 8 PLOE_7       | 5 PLOE_4                 | 1 PLOE_2                                 | v  |

| 2 PD_47      | 11 PD_46 | 0 PD_45           | 3S PD_44      | PD_43       | PLO0_22 PLO0_21 PLO0_20 | PLOO_19 PLOO_18 PLOO_17 | DL_VDD PLOO_16 PLOO_15 PLOO_14 | 11 PLOO_10              | _8 PLQO_7 | 5 PLOO_4 | 2 PLOO_1 | 23 PLOE_22    | 20 PLOE_19    | PLOE_18 PLOE_17 PLOE_16 | PLOE_15 PLOE_14 PLOE_13 PLOE_12 | 10 PLOE_9       | 7 PLOE_6       | 4 PLOE_3                 | 2 No<br>Connect                          | Y  |

## **1.4 Pin Description**

Unless otherwise mentioned in the pin-description, tie unused input pins to ground and leave unused output pins open. For information about power distribution and ground plane isolation on a print circuit board, refer to gmB135-AN1: gmB135 Evaluation Board Application Note (to be published).

| Pin<br>No.                  | Name      | In /<br>Out | 5-V Tolerant<br>Input? | Description                                                                                                                                                                                          |  |

|-----------------------------|-----------|-------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A19                         | ADC_VDD1  |             |                        | Digital power for ADC clocking circuit. Must be bypassed with 0.1 uF capacitor to ACD_GND1.                                                                                                          |  |

| A18                         | ADC_GND1  |             |                        | Digital GND for ADC clocking circuit. Must be directly connected to the digital system ground plane.                                                                                                 |  |

| B20                         | ADC_VDD2  |             |                        | Digital power for ADC encoding logic. Must be bypassed with 0.1 uF capacitor to ADC_GND2.                                                                                                            |  |

| A20                         | ADC_GND2  |             |                        | Digital GND for ADC encoding logic. Must be directly connected to the digital system ground plane.                                                                                                   |  |

| D20                         | ADC_VDD3  |             |                        | Digital power for ADC encoding logic. Must be bypassed with 0.1 uF capacitor to ADC_GND3.                                                                                                            |  |

| C20                         | ADC_GND3  |             |                        | Digital GND for ADC encoding logic. Must be directly connected to the digital system ground plane.                                                                                                   |  |

| B19                         | SUB_GNDA  |             |                        | Dedicated pin for substrate guard ring that protects the ADC reference system. Must be directly connected to the analog system ground plane.                                                         |  |

| D19                         | ADC_VDDA  |             |                        | Analog power for ADC analog blocks that are shared by all three channels. Includes bandgap reference, master biasing and full scale adjust. Must be bypassed with 0.1 uF capacitor to ADC_GND (C19). |  |

| D17                         | ADC_BVDDA |             |                        | Analog power for the blue channel. Must be bypassed with 0.1 uF capacitor to ADC_GND (D18).                                                                                                          |  |

| D15                         | ADC_GVDDA |             |                        | Analog power for the green channel. Must be bypassed with 0.1 uF capacitor to ADC_GND (D16).                                                                                                         |  |

| D13                         | ADC_RVDDA |             |                        | Analog power for the red channel. Must be bypassed with 0.1 uF capacitor to ADC_GND (D14).                                                                                                           |  |

| D14,<br>D16,<br>D18,<br>C19 | ADC_GND   |             |                        | Analog ground for ADC. Must be directly connected to the analog system ground plane.                                                                                                                 |  |

| A15                         | INPUT2    | In          | Yes (5V-tolerant)      | Reserved. For internal testing purposes.                                                                                                                                                             |  |

| C13                         | RED1P     | In          | No (up to 3.3V)        | Positive analog input for Red channel 1. Enabled when analog port 1 is selected.                                                                                                                     |  |

| B13                         | RED1M     | In          | No (up to 3.3V)        | Negative analog input for Red channel 1. Enabled when analog port 1 is selected.                                                                                                                     |  |

| C15                         | GREEN1P   | In          | No (up to 3.3V)        | Positive analog input for Green channel 1. Enabled when analog port 1 is selected.                                                                                                                   |  |

| B15                         | GREEN1M   | In          | No (up to 3.3V)        | Negative analog input for Green channel 1. Enabled when analog port 1 is selected.                                                                                                                   |  |

| C17                         | BLUE1P    | In          | No (up to 3.3V)        | Positive analog input for Blue channel 1. Enabled when analog port 1 is selected.                                                                                                                    |  |

| B17                         | BLUE1M    | In          | No (up to 3.3V)        | Negative analog input for Blue channel 1. Enabled when analog port 1 is selected.                                                                                                                    |  |

| C14                         | RED2P     | In          | No (up to 3.3V)        | Positive analog input for Red channel 2. Enabled when analog port 1 is selected.                                                                                                                     |  |

| B14                         | RED2M     | In          | No (up to 3.3V)        | Negative analog input for Red channel 2. Enabled when analog port 2 is selected.                                                                                                                     |  |

| C16                         | GREEN2P   | In          | No (up to 3.3V)        | Positive analog input for Green channel 2. Enabled when analog port 2 is selected.                                                                                                                   |  |

| B16                         | GREEN2M   | In          | No (up to 3.3V)        | Negative analog input for Green channel 2. Enabled when analog port 2 is selected.                                                                                                                   |  |

| C18                         | BLUE2P    | In          | No (up to 3.3V)        | Positive analog input for Blue channel 2. Enabled when analog port 2 is selected.                                                                                                                    |  |

| B18                         | BLUE2M    | In          | No (up to 3.3V)        | Negative analog input for Blue channel 2. Enabled when analog port 2 is selected.                                                                                                                    |  |

| B12                         | DPA_VDDA  |             |                        | Internal test pin.                                                                                                                                                                                   |  |

| Pin<br>No. | Name     | In /<br>Out | 5-V Tolerant<br>Input? | Description        |

|------------|----------|-------------|------------------------|--------------------|

| C12        | DPA_GNDA |             |                        | Internal test pin. |

| A13        | DPA_VDD  |             |                        | Internal test pin. |

| A14        | DPA_GND  |             |                        | Internal test pin. |

| A16        | ARSRV1   |             |                        | Internal test pin. |

| A17        | VFST     |             |                        | Internal test pin. |

## Table 1.4.1. Analog-to-Digital Converter

| Pin | Name      | In /<br>Out | 5-V Tolerant Input<br>/Output Drive<br>Current @10pF | It Description                                                                                                                                                                                                                            |  |  |  |  |

|-----|-----------|-------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A12 | RES_PAD   | In          | 5-V tolerant                                         | Resets the gmB135 chip when low for at least 100 ns. Active low.                                                                                                                                                                          |  |  |  |  |

| C9  | IRQ       | Out         | 4 mA                                                 | Interrupt request output                                                                                                                                                                                                                  |  |  |  |  |

| C10 | HCLK      | In          | 5-V tolerant                                         | Host interface clock signal input.                                                                                                                                                                                                        |  |  |  |  |

| C11 | HFS       | In          | 5-V tolerant                                         | Active-high Host Frame Sync. Marks the beginning of the host interface data packet. This pin has an internal pull-down resistor.                                                                                                          |  |  |  |  |

| A10 | HDATA_3   | In/Out      | 5-V tolerant / 8mA                                   | Bit 3 of 4-bit host interface data HDATA[3:0].                                                                                                                                                                                            |  |  |  |  |

| B10 | HDATA_2   | In/Out      | 5-V tolerant / 8mA                                   | Bit 2 of 4-bit host interface data HDATA[3:0].                                                                                                                                                                                            |  |  |  |  |

| A11 | HDATA_1   | In/Out      | 5-V tolerant / 8mA                                   | Bit 1 of 4-bit host interface data HDATA[3:0].                                                                                                                                                                                            |  |  |  |  |

| B11 | HDATA_0   | In/Out      | 5-V tolerant / 8mA                                   | Bit 0 of 4-bit host interface data HDATA[3:0].                                                                                                                                                                                            |  |  |  |  |

| A9  | EVREF     | Out         | 4 mA                                                 | VREF output for external OSD controller.                                                                                                                                                                                                  |  |  |  |  |

| B9  | EHREF     | Out         | 4 mA                                                 | HREF output for external OSD controller.                                                                                                                                                                                                  |  |  |  |  |

| C8  | ECLK      | Out         | 4 mA                                                 | Clock output for external OSD controller.                                                                                                                                                                                                 |  |  |  |  |

| C7  | EFSW      | In          | 5-V tolerant                                         | External OSD window display enable. Displays data from external O controller when high.                                                                                                                                                   |  |  |  |  |

| A7  | EDIN_PAD3 | In          | 5-V tolerant                                         | Data input 3 from an external OSD controller.                                                                                                                                                                                             |  |  |  |  |

| B7  | EDIN_PAD2 | In          | 5-V tolerant                                         | Data input 2 from an external OSD controller.                                                                                                                                                                                             |  |  |  |  |

| A8  | EDIN_PAD1 | In          | 5-V tolerant                                         | Data input 1 from an external OSD controller.                                                                                                                                                                                             |  |  |  |  |

| B8  | EDIN_PAD0 | In          | 5-V tolerant                                         | Data input 0 from an external OSD controller.                                                                                                                                                                                             |  |  |  |  |

| A2  | MFB_11    | In/Out      | 5-V tolerant / 8mA                                   | Bit 11 of 12-bit Multi-Function Bus MFB[11:0], which may be used as general purpose I/O (GPIO).                                                                                                                                           |  |  |  |  |

| A3  | MFB_10    | In/Out      | 5-V tolerant / 8mA                                   | Bit 10 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.                                                                                                                                                                       |  |  |  |  |

| B3  | MFB_9     | In/Out      | 5-V tolerant / 8mA                                   | Bit 9 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.                                                                                                                                                                        |  |  |  |  |

| A4  | MFB_8     | In/Out      | 5-V tolerant / 8mA                                   | Bit 8 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.                                                                                                                                                                        |  |  |  |  |

| B4  | MFB_7     | In/Out      | 5-V tolerant / 8mA                                   | Bit 7 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.<br>Do not connect external pull-up resistors to this pin.                                                                                                              |  |  |  |  |

| C4  | MFB_6     | In/Out      | 5-V tolerant / 8mA                                   | Bit 6 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO. If<br>an external pull-up resistor is connected to this pin, gmB135 is config-<br>ured for 1-bit host interface. The default host interface configuration is<br>4-bit. |  |  |  |  |

| A5  | MFB_5     | In/Out      | 5-V tolerant / 8mA                                   | Bit 5 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.                                                                                                                                                                        |  |  |  |  |

| B5  | MFB_4     | In/Out      | 5-V tolerant / 8mA                                   | Bit 4 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.                                                                                                                                                                        |  |  |  |  |

| C5  | MFB_3     | In/Out      | 5-V tolerant / 8mA                                   | Bit 3 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.                                                                                                                                                                        |  |  |  |  |

| A6  | MFB_2     | In/Out      | 5-V tolerant / 8mA                                   | Bit 2 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.                                                                                                                                                                        |  |  |  |  |

| B6  | MFB_1     | In/Out      | 5-V tolerant / 8mA                                   | Bit 1 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.                                                                                                                                                                        |  |  |  |  |

| C6  | MFB_0     | In/Out      | 5-V tolerant / 8mA                                   | Bit 0 of 12-bit Multi-Function Bus MFB[11:0]. May be used as GPIO.                                                                                                                                                                        |  |  |  |  |

#### Table 1.4.2. Host Interface (HIF), External On-Screen Display (EOSD), and Multi-Function Bus (MFB).

| Pin              | Name      | In /<br>Out | 5-V Tolerant<br>Input? | Description                                                                                                                            |

|------------------|-----------|-------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| C2               | CRT_VDD   |             | -                      | Digital power for the Hsync/Vsync input pads.                                                                                          |

| C3               | CRT_VSS   |             |                        | Digital ground for the Hsync/Vsync input pads.                                                                                         |

| J3               | DAC_SVDDA |             |                        | Analog power for the Source DDS DAC. Must be bypassed with a 0.1 uF capacitor to pin J2 (DAC_SGNDA)                                    |

| H1,<br>J1,<br>J2 | DAC_SGNDA |             |                        | Analog ground for the Source DDS DAC. Must be directly connected to the analog ground plane.                                           |

| F4               | DAC_DVDDA |             |                        | Analog power for Destination DDS DAC. Must be bypassed with a 0.1 uF capacitor to pin E3 (DAC_DGNDA)                                   |

| E2,<br>E3        | DAC_DGNDA |             |                        | Analog ground for Destination DDS DAC. Must be directly connected to the analog ground plane.                                          |

| D4               | PLL_RVDDA |             |                        | Analog power for the Reference DDS PLL. Must be bypassed with a 0.1 uF capacitor to pin E4 (PLL_RGNDA)                                 |

| E4               | PLL_RGNDA |             |                        | Analog ground for the Reference DDS PLL. Must be directly connected to the analog ground plane.                                        |

| H3               | PLL_SVDDA |             |                        | Analog power for the Source DDS PLL. Must be bypassed with a 0.1 uF capacitor to pin H4 (PLL_SGNDA)                                    |

| H4               | PLL_SGNDA |             |                        | Analog ground for the Source DDS PLL. Must be directly connected to the analog ground plane.                                           |

| F3               | PLL_DVDDA |             |                        | Analog power for the Destination DDS PLL. Must be bypassed with a 0.1 uF capacitor to pin G4 (PLL_DGNDA)                               |

| G4               | PLL_DGNDA |             |                        | Analog ground for the Destination DDS PLL. Must be directly connected to the analog ground plane.                                      |

| D2               | SUB_RGNDA |             |                        | Dedicated pin for the substrate guard ring that protects the Reference DDS. Must be directly connected to the analog ground plane.     |

| G3               | SUB_DGND  |             |                        | Dedicated pin for the substrate guard ring that protects the Destination DDS. Must be directly connected to the analog ground plane.   |

| F1,<br>G1,<br>G2 | SUB_SGND  |             |                        | Dedicated pin for the substrate guard ring that protects the Source DDS. Must be directly connected to the analog system ground plane. |

| D1               | TCLK      | In          | 5-V Tolerant           | Reference clock (TCLK) input from the 50 Mhz crystal oscillator.                                                                       |

| E1               | XTAL      | Out         |                        | Crystal oscillator output.                                                                                                             |

| C1               | VSYNC1    | In          | 5-V Tolerant           | CRT Vsync input 1. Enabled when analog port 1 is selected. TTL Schmitt trigger input.                                                  |

| A1               | HSYNC1    | In          | 5-V Tolerant           | CRT Hsync or composite sync input 1. Enabled when analog port 1 is selected. TTL Schmitt trigger input.                                |

| B2               | VSYNC2    | In          | 5-V Tolerant           | CRT Vsync input 2. Enabled when analog port 2 is selected. TTL Schmitt trigger input.                                                  |

| B1               | HSYNC2    | In          | 5-V Tolerant           | CRT Hsync or composite sync input 2. Enabled when analog port 2 is selected. TTL Schmitt trigger input.                                |

| D3               | VBUFC     | Out         |                        | Used for testing only. Do not connect.                                                                                                 |

| F2               | VBUFC_D   | Out         |                        | Used for testing only. Do not connect.                                                                                                 |

| H2               | VBUFC_S   | Out         |                        | Used for testing only. Do not connect.                                                                                                 |

Table 1.4.3. Clock Recovery and Time Base Conversion

|     | 1         | 1           |                               | pins are programma   | 1       |               |       |         |                |

|-----|-----------|-------------|-------------------------------|----------------------|---------|---------------|-------|---------|----------------|

| Pin | Name      | In /<br>Out | Output Drive<br>Current @10pF | Description          | TFT (on | e pixel/clock | )     | TFT (tw | o pixel/clock) |

|     |           |             |                               |                      | 8 bit   | 6 bit         | 4 bit | 8 bit   | 6 bit          |

| Y20 | PD_47     | Out         | 2 mA ~ 20 mA                  | Panel data output 47 |         |               |       | OB1     |                |

| Y19 | PD_46     | Out         | 2 mA ~ 20 mA                  | Panel data output 46 |         |               |       | OB0     |                |

| Y18 | PD_45     | Out         | 2 mA ~ 20 mA                  | Panel data output 45 |         |               |       | OG1     |                |

| Y17 | PD_44     | Out         | 2 mA ~ 20 mA                  | Panel data output 44 |         |               |       | OG0     |                |

| Y16 | PD_43     | Out         | 2 mA ~ 20 mA                  | Panel data output 43 |         |               |       | OR1     |                |

| W20 | PD_42     | Out         | 2 mA ~ 20 mA                  | Panel data output 42 |         |               |       | OR0     |                |

| W19 | PD_41     | Out         | 2 mA ~ 20 mA                  | Panel data output 41 | B1      |               |       | EB1     |                |

| W18 | PD_40     | Out         | 2 mA ~ 20 mA                  | Panel data output 40 | B0      |               |       | EB0     |                |

| V20 | PD_39     | Out         | 2 mA ~ 20 mA                  | Panel data output 39 | G1      |               |       | EG1     |                |

| V19 | PD_38     | Out         | 2 mA ~ 20 mA                  | Panel data output 38 | G0      |               |       | EG0     |                |

| V18 | PD_37     | Out         | 2 mA ~ 20 mA                  | Panel data output 37 | R1      |               |       | ER1     |                |

| U20 | PD_36     | Out         | 2 mA ~ 20 mA                  | Panel data output 36 | R0      |               |       | ER0     |                |

| U19 | PD_35     | Out         | 2 mA ~ 20 mA                  | Panel data output 35 |         |               |       | OB7     | OB5            |

| U18 | PD_34     | Out         | 2 mA ~ 20 mA                  | Panel data output 34 |         |               |       | OB6     | OB4            |

| U17 | PD_33     | Out         | 2 mA ~ 20 mA                  | Panel data output 33 |         |               |       | OB5     | OB3            |

| T20 | PD_32     | Out         | 2 mA ~ 20 mA                  | Panel data output 32 |         |               |       | OB4     | OB2            |

| T19 | PD_31     | Out         | 2 mA ~ 20 mA                  | Panel data output 31 |         |               |       | OB3     | OB1            |

| T18 | PD_30     | Out         | 2 mA ~ 20 mA                  | Panel data output 30 |         |               |       | OB2     | OB0            |

| R20 | PD_29     | Out         | 2 mA ~ 20 mA                  | Panel data output 29 |         |               |       | OG7     | OG5            |

| R19 | PD_28     | Out         | 2 mA ~ 20 mA                  | Panel data output 28 |         |               |       | OG6     | OG4            |

| R18 | PD_27     | Out         | 2 mA ~ 20 mA                  | Panel data output 27 |         |               |       | OG5     | OG3            |

| P20 | PD_26     | Out         | 2 mA ~ 20 mA                  | Panel data output 26 |         |               |       | OG4     | OG2            |

| P19 | PD_25     | Out         | 2 mA ~ 20 mA                  | Panel data output 25 |         |               |       | OG3     | OG1            |

| P18 | PD_24     | Out         | 2 mA ~ 20 mA                  | Panel data output 24 |         |               |       | OG2     | OG0            |

| N20 | PD_23     | Out         | 2 mA ~ 20 mA                  | Panel data output 23 |         |               |       | OR7     | OR5            |

| N19 | PD_22     | Out         | 2 mA ~ 20 mA                  | Panel data output 22 |         |               |       | OR6     | OR4            |

| N18 | PD_21     | Out         | 2 mA ~ 20 mA                  | Panel data output 21 |         |               |       | OR5     | OR3            |

| M20 | PD_20     | Out         | 2 mA ~ 20 mA                  | Panel data output 20 |         |               |       | OR4     | OR2            |

| M19 | PD_19     | Out         | 2 mA ~ 20 mA                  | Panel data output 19 |         |               |       | OR3     | OR1            |

| M18 | PD_18     | Out         | 2 mA ~ 20 mA                  | Panel data output 18 |         |               |       | OR2     | OR0            |

| L20 | PD_17     | Out         | 2 mA ~ 20 mA                  | Panel data output 17 | B7      | B5            | B3    | EB7     | EB5            |

| L19 | PD_16     | Out         | 2 mA ~ 20 mA                  | Panel data output 16 | B6      | B4            | B2    | EB6     | EB4            |

| L18 | PD_15     | Out         | 2 mA ~ 20 mA                  | Panel data output 15 | B5      | B3            | B1    | EB5     | EB3            |

| K20 | PD_14     | Out         | 2 mA ~ 20 mA                  | Panel data output 14 | B4      | B2            | B0    | EB4     | EB2            |

| K19 | PD_13     | Out         | 2 mA ~ 20 mA                  | Panel data output 13 | B3      | B1            |       | EB3     | EB1            |

| K18 | PD_12     | Out         | 2 mA ~ 20 mA                  | Panel data output 12 | B2      | B0            |       | EB2     | EB0            |

| J20 | <br>PD_11 | Out         | 2 mA ~ 20 mA                  | Panel data output 11 | G7      | G5            | G3    | EG7     | EG5            |

| J19 | <br>PD_10 | Out         | 2 mA ~ 20 mA                  | Panel data output 10 | G6      | G4            | G2    | EG6     | EG4            |

| J18 | PD_9      | Out         | 2 mA ~ 20 mA                  | Panel data output 9  | G5      | G3            | G1    | EG5     | EG3            |

| Table 1.4.4. TFT Panel Interface | Table | 1.4.4. | TFT | Panel | Interface |

|----------------------------------|-------|--------|-----|-------|-----------|

|----------------------------------|-------|--------|-----|-------|-----------|

| H20 | PD_8  | Out | 2 mA ~ 20 mA | Panel data output 8                                                                                                   | G4                | G2              | G0              | EG4      | EG2 |  |

|-----|-------|-----|--------------|-----------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|-----------------|----------|-----|--|

| H19 | PD_7  | Out | 2 mA ~ 20 mA | Panel data output 7                                                                                                   | G3                | G1              |                 | EG3      | EG1 |  |

| H18 | PD_6  | Out | 2 mA ~ 20 mA | Panel data output 6                                                                                                   | G2                | G0              |                 | EG2      | EG0 |  |

| G20 | PD_5  | Out | 2 mA ~ 20 mA | Panel data output 5                                                                                                   | R7                | R5              | R3              | ER7      | ER5 |  |

| G19 | PD_4  | Out | 2 mA ~ 20 mA | Panel data output 4                                                                                                   | R6                | R4              | R2              | ER6      | ER4 |  |

| G18 | PD_3  | Out | 2 mA ~ 20 mA | Panel data output 3                                                                                                   | R5                | R3              | R1              | ER5      | ER3 |  |

| F20 | PD_2  | Out | 2 mA ~ 20 mA | Panel data output 2                                                                                                   | R4                | R2              | R0              | ER4      | ER2 |  |

| F19 | PD_1  | Out | 2 mA ~ 20 mA | Panel data output 1                                                                                                   | R3                | R1              |                 | ER3      | ER1 |  |

| F18 | PD_0  | Out | 2 mA ~ 20 mA | Panel data output 0                                                                                                   | R2                | R0              |                 | ER2      | ER0 |  |

| T17 | PDE   | Out | 2 mA ~ 20 mA | Panel Display Enable                                                                                                  | signal, active v  | when flat panel | data is valid.  |          |     |  |

| E19 | PHS   | Out | 2 mA ~ 20 mA | This output provides t                                                                                                | he panel line c   | lock signal.    |                 |          |     |  |

| E20 | PVS   | Out | 2 mA ~ 20 mA | This output provides t                                                                                                | he panel frame    | start signal.   |                 |          |     |  |

| R17 | PCLK  | Out | 2 mA ~ 20 mA | This output drives the                                                                                                | flat panel shift  | clock.          |                 |          |     |  |

| H17 | PCLK2 | Out | 2 mA ~ 20 mA | This output drives the second panel shift clock. The polarity and phase of this signal is independently programmable. |                   |                 |                 |          |     |  |

| E17 | PPwr  | Out | 8 mA         | This output controls the power to a flat panel.                                                                       |                   |                 |                 |          |     |  |

| E18 | PBias | Out | 8 mA         | This output turns on/o                                                                                                | off the panel bia | as power or cor | ntrols panel ba | cklight. |     |  |

#### **Table 1.4.4. TFT Panel Interface**

#### Table 1.4.5. Pin-Scan Test Pins

| Pin# | Name    | In/<br>Out | 5-V Tolerant Input? | Description                                                                                                                                                                                                                                                                                             |

|------|---------|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U16  | PSCAN   | In         | 5-V tolerant        | Automatic PCB assembly test enable. When this input is pulled high, the chip enters automatic PCB assembly test mode. An internal pull-down resistor drives this input low for normal operation. Do not connect for normal operation. For further details please refer to Appendix A: gmB135 Para-Scan. |

| V16  | STI_TM1 | In         | 5-V tolerant        | Internal test pin.                                                                                                                                                                                                                                                                                      |

| W16  | STI_TM2 | In         | 5-V tolerant        | Internal test pin.                                                                                                                                                                                                                                                                                      |

| Pin# | Name     | In/ | 5-V Tolerant | Description                       |                                    |

|------|----------|-----|--------------|-----------------------------------|------------------------------------|

|      |          | Out | Input?       | 8-bit (2x-clock)<br>Configuration | 16-bit (1x-clock)<br>Configuration |

| T1   | PIXIN_15 | In  | 5-V Tolerant |                                   | U[7]/V[7]                          |

| T2   | PIXIN_14 | In  | 5-V Tolerant |                                   | U[6]/V[6]                          |

| T3   | PIXIN_13 | In  | 5-V Tolerant |                                   | U[5]/V[5]                          |

| R2   | PIXIN_12 | In  | 5-V Tolerant |                                   | U[4]/V[4]                          |

| R1   | PIXIN_11 | In  | 5-V Tolerant |                                   | U[3]/V[3]                          |

| P2   | PIXIN_10 | In  | 5-V Tolerant |                                   | U[2]/V[2]                          |

| P3   | PIXIN_9  | In  | 5-V Tolerant |                                   | U[1]/V[1]                          |

| N2   | PIXIN_8  | In  | 5-V Tolerant |                                   | U[0]/V[0]                          |

| N3   | PIXIN_7  | In  | 5-V Tolerant | Y[7]/U[7]/V[7]                    | Y[7]                               |

| M2   | PIXIN_6  | In  | 5-V Tolerant | Y[6]/U[6]/V[6]                    | Y[6]                               |

| M3   | PIXIN_5  | In  | 5-V Tolerant | Y[5]/U[5]/V[5]                    | Y[5]                               |

| L2   | PIXIN_4  | In  | 5-V Tolerant | Y[4]/U[4]/V[4]                    | Y[4]                               |

| L3   | PIXIN_3  | In  | 5-V Tolerant | Y[3]/U[3]/V[3]                    | Y[3]                               |

| K1   | PIXIN_2  | In  | 5-V Tolerant | Y[2]/U[2]/V[2]                    | Y[2]                               |

| K2   | PIXIN_1  | In  | 5-V Tolerant | Y[1]/U[1]/V[1]                    | Y[1]                               |

| K3   | PIXIN_0  | In  | 5-V Tolerant | Y[0]/U[0]/V[0]                    | Y[0]                               |

| L1   | CCVSYNC  | In  | 5-V Tolerant | Video                             | Vsync                              |

| N1   | CCHSYNC  | In  | 5-V Tolerant | Video                             | Hsync                              |

| M1   | CCHREF   | In  | 5-V Tolerant | Horizontal Display Reference      | e. Valid when the data is valid.   |

| P1   | CCSCLK   | In  | 5-V Tolerant | 2x Video Clock                    | 1x Video Clock                     |

| Pin# | Name    | In / | 5V Tolerant<br>Input? | Description          | One pixel/clock |       |       | Two piz | Two pixels/clock |  |

|------|---------|------|-----------------------|----------------------|-----------------|-------|-------|---------|------------------|--|

|      |         | Out  |                       |                      | 8 bit           | 6 bit | 4 bit | 8 bit   | 6 bit            |  |

| U15  | PLQO_23 | In   | No (up to 3.3V)       | Digital odd data 23  |                 |       |       | OR7     | OR5              |  |

| V15  | PLQO_22 | In   | No (up to 3.3V)       | Digital odd data 22  |                 |       |       | OR6     | OR4              |  |

| W15  | PLQO_21 | In   | No (up to 3.3V)       | Digital odd data 21  |                 |       |       | OR5     | OR3              |  |

| Y15  | PLQO_20 | In   | No (up to 3.3V)       | Digital odd data 20  |                 |       |       | OR4     | OR2              |  |

| V14  | PLQO_19 | In   | No (up to 3.3V)       | Digital odd data 19  |                 |       |       | OR3     | OR1              |  |

| W14  | PLQO_18 | In   | No (up to 3.3V)       | Digital odd data 18  |                 |       |       | OR2     | OR0              |  |

| Y14  | PLQO_17 | In   | No (up to 3.3V)       | Digital odd data 17  |                 |       |       | OR1     |                  |  |

| V13  | PLQO_16 | In   | No (up to 3.3V)       | Digital odd data 16  |                 |       |       | OR0     |                  |  |

| W13  | PLQO_15 | In   | No (up to 3.3V)       | Digital odd data 15  |                 |       |       | OG7     | OG5              |  |

| Y13  | PLQO_14 | In   | No (up to 3.3V)       | Digital odd data 14  |                 |       |       | OG6     | OG4              |  |

| U12  | PLQO_13 | In   | No (up to 3.3V)       | Digital odd data 13  |                 |       |       | OG5     | OG3              |  |

| V12  | PLQO_12 | In   | No (up to 3.3V)       | Digital odd data 12  |                 |       |       | OG4     | OG2              |  |

| W12  | PLQO_11 | In   | No (up to 3.3V)       | Digital odd data 11  |                 |       |       | OG3     | OG1              |  |

| Y12  | PLQO_10 | In   | No (up to 3.3V)       | Digital odd data 10  |                 |       |       | OG2     | OG0              |  |

| V11  | PLQO_9  | In   | No (up to 3.3V)       | Digital odd data 9   |                 |       |       | OG1     |                  |  |

| W11  | PLQO_8  | In   | No (up to 3.3V)       | Digital odd data 8   |                 |       |       | OG0     |                  |  |

| Y11  | PLQO_7  | In   | No (up to 3.3V)       | Digital odd data 7   |                 |       |       | OB7     | OB5              |  |

| V10  | PLQO_6  | In   | No (up to 3.3V)       | Digital odd data 6   |                 |       |       | OB6     | OB4              |  |

| W10  | PLQO_5  | In   | No (up to 3.3V)       | Digital odd data 5   |                 |       |       | OB5     | OB3              |  |

| Y10  | PLQO_4  | In   | No (up to 3.3V)       | Digital odd data 4   |                 |       |       | OB4     | OB2              |  |

| V9   | PLQO_3  | In   | No (up to 3.3V)       | Digital odd data 3   |                 |       |       | OB3     | OB1              |  |

| W9   | PLQO_2  | In   | No (up to 3.3V)       | Digital odd data 2   |                 |       |       | OB2     | OB0              |  |

| Y9   | PLQO_1  | In   | No (up to 3.3V)       | Digital odd data 1   |                 |       |       | OB1     |                  |  |

| V8   | PLQO_0  | In   | No (up to 3.3V)       | Digital odd data 0   |                 |       |       | OB0     |                  |  |

| W8   | PLQE_23 | In   | No (up to 3.3V)       | Digital even data 23 | R7              | R5    | R3    | ER7     | ER5              |  |

| Y8   | PLQE_22 | In   | No (up to 3.3V)       | Digital even data 22 | R6              | R4    | R2    | ER6     | ER4              |  |

| V7   | PLQE_21 | In   | No (up to 3.3V)       | Digital even data 21 | R5              | R3    | R1    | ER5     | ER3              |  |

| W7   | PLQE_20 | In   | No (up to 3.3V)       | Digital even data 20 | R4              | R2    | R0    | ER4     | ER2              |  |

| Y7   | PLQE_19 | In   | No (up to 3.3V)       | Digital even data 19 | R3              | R1    |       | ER3     | ER1              |  |

| V6   | PLQE_18 | In   | No (up to 3.3V)       | Digital even data 18 | R2              | R0    |       | ER2     | ER0              |  |

| W6   | PLQE_17 | In   | No (up to 3.3V)       | Digital even data 17 | R1              |       |       | ER1     |                  |  |

| Y6   | PLQE_16 | In   | No (up to 3.3V)       | Digital even data 16 | R0              |       |       | ER0     |                  |  |

| U5   | PLQE_15 | In   | No (up to 3.3V)       | Digital even data 15 | G7              | G5    | G3    | EG7     | EG5              |  |

| V5   | PLQE_14 | In   | No (up to 3.3V)       | Digital even data 14 | G6              | G4    | G2    | EG6     | EG4              |  |

| W5   | PLQE_13 | In   | No (up to 3.3V)       | Digital even data 13 | G5              | G3    | G1    | EG5     | EG3              |  |

| Y5   | PLQE_12 | In   | No (up to 3.3V)       | Digital even data 12 | G4              | G2    | G0    | EG4     | EG2              |  |

| V4   | PLQE_11 | In   | No (up to 3.3V)       | Digital even data 11 | G3              | G1    |       | EG3     | EG1              |  |

| W4   | PLQE_10 | In   | No (up to 3.3V)       | Digital even data 10 | G2              | G0    |       | EG2     | EG0              |  |

| Y4   | PLQE_9  | In   | No (up to 3.3V)       | Digital even data 9  | G1              |       |       | EG1     |                  |  |

| V3   | PLQE_8  | In   | No (up to 3.3V)       | Digital even data 8  | G0              |       |       | EG0     |                  |  |

| W3   | PLQE_7  | In   | No (up to 3.3V)       | Digital even data 7  | B7              | B5    | B3    | EB7     | EB5              |  |

## Table 1.4.7. Digital Input Port

| Y3 | PLQE_6          | In | No (up to 3.3V) | Digital even data 6     | B6 | B4 | B2 | EB6 | EB4 |

|----|-----------------|----|-----------------|-------------------------|----|----|----|-----|-----|

| V2 | PLQE_5          | In | No (up to 3.3V) | Digital even data 5     | B5 | B3 | B1 | EB5 | EB3 |

| W2 | PLQE_4          | In | No (up to 3.3V) | Digital even data 4     | B4 | B2 | B0 | EB4 | EB2 |

| Y2 | PLQE_3          | In | No (up to 3.3V) | Digital even data 3     | B3 | B1 |    | EB3 | EB1 |

| W1 | PLQE_2          | In | No (up to 3.3V) | Digital even data 2     | B2 | B0 |    | EB2 | EB0 |

| V1 | PLQE_1          | In | No (up to 3.3V) | Digital even data 1     | B1 |    |    | EB1 |     |

| U4 | PLQE_0          | In | No (up to 3.3V) | Digital even data 0     | B0 |    |    | EB0 |     |

| U1 | PLHsync_<br>PAD | In | No (up to 3.3V) | PL Hsync input          |    |    |    |     |     |

| U2 | PLVsync_<br>PAD | In | No (up to 3.3V) | PL Vsync input          |    |    |    |     |     |

| U3 | PLDE_           | In | No (up to 3.3V) | PL Display Enable input |    |    |    |     |     |

|    | PAD             |    |                 |                         |    |    |    |     |     |

| U7 | PLOCLK          | In | No (up to 3.3V) | PL Clock input          |    |    |    |     |     |

## Table 1.4.7. Digital Input Port

# Table 1.4.8. Digital VDD/VSS for the Core Circuitry, Host Interface, digital and CCIR-601 input ports, source and destination DDSs, and Panel Output Interface (All the VDDs including analog VDDs must be in the range of +3.3V +/-5%.)

| Pins                                                                               | Name   | Description                                                           |

|------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------|

| D11, D12, J4, U8, U9, U11, U14, L17,<br>M17                                        | CVDD   | Core circuitry VDD. Tie to PVDD on a print circuit board.             |

| H8 ~ H13, J8 ~ J13, K8 ~ K13, L8 ~ L13,<br>M8 ~ M13, N8 ~ N13<br>(middle 6x6 pins) | CVSS   | Digital grounds for core circuitry and panel output interface.        |

| G17, K17, N17, V17                                                                 | PL_VDD | VDD for panel output interface. Tie to CVDD on a print circuit board. |

| F17, J17, P17, W17                                                                 | PL_VSS | Ground for panel output interface.                                    |

| D6, D8, D10                                                                        | HE_VDD | VDD for host interface and external OSD interface.                    |

| D5, D7, D9                                                                         | HE_VSS | Ground for host interface and external OSD interface.                 |

| K4                                                                                 | D_VDD  | VDD for destination DDS.                                              |

| L4                                                                                 | D_VSS  | VSS for destination DDS.                                              |

| N4                                                                                 | S_VDD  | VDD for source DDS.                                                   |

| M4                                                                                 | S_VSS  | VSS for source DDS.                                                   |

| P4                                                                                 | CC_VDD | CCIR-601 input port VDD.                                              |

| R3, R4                                                                             | CC_VSS | CCIR-601 input port ground.                                           |

| U6, U13                                                                            | DI_VDD | Digital input port VDD.                                               |

| T4, U10                                                                            | DI_VSS | Digital input port ground.                                            |

## **1.5** System-Level Implementation

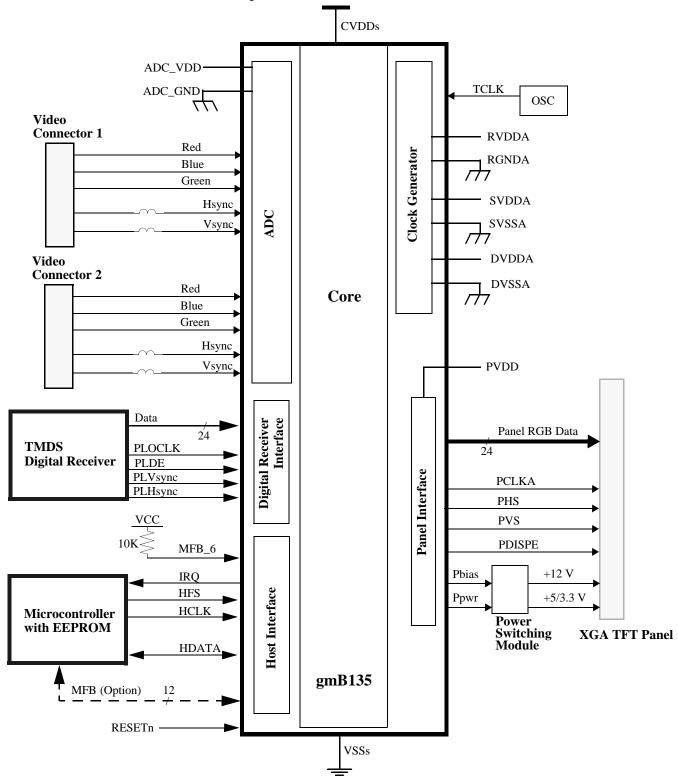

Figure 1.5.1. Typical Configuration with 1-bit Host Interface, 1 pixel/clock XGA Panel, 2-Channel Analog RGB input and 1 pixel/clock TMDS Receiver.

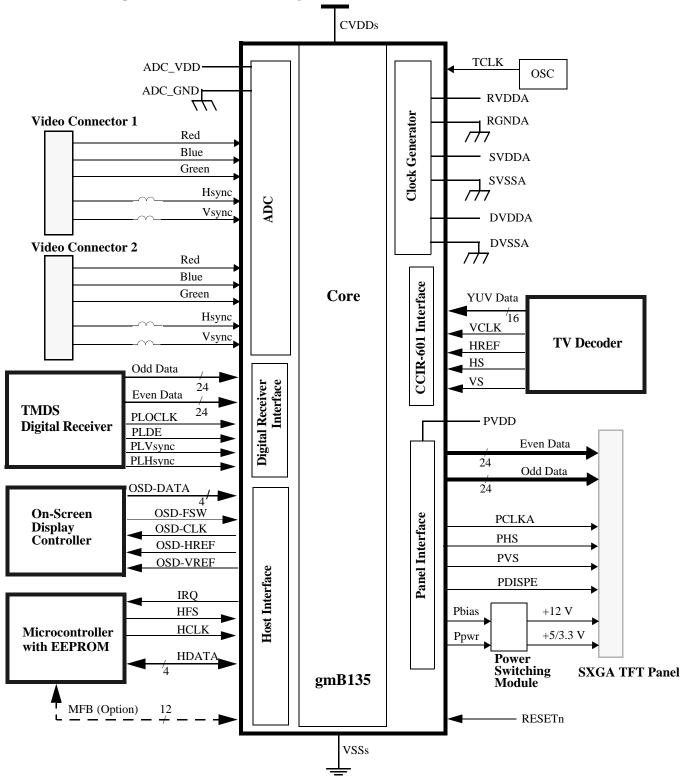

Figure 1.5.2. Typical Configuration with 4-bit Host Interface, 2 pixels/clock SXGA panel, 2-channel analog RGB input, 2 pixel/clock TMDS Receiver, digital TV decoder and external OSD controller

## **1.6 Operating Modes gmB135**

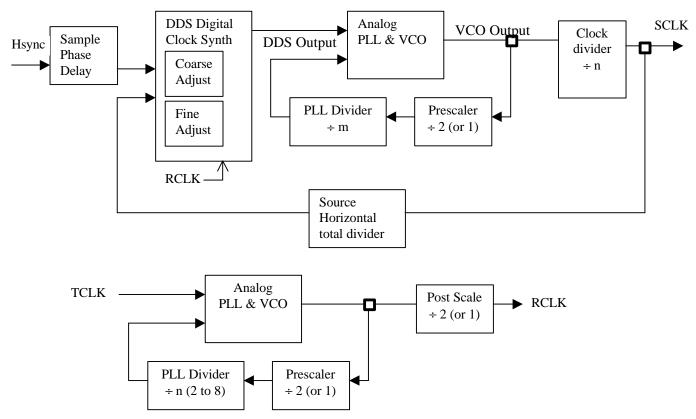

This section describes the operating modes of the gmB135. To explain the types of operating modes, the Source Clock (also called as SCLK in this document), the Panel Clock are defined as follows:

- The Source Clock is the sample clock, either regenerated from the input Hsync timing (called clock recovery) by SCLK DDS (direct digital synthesis)/ PLL for analog inputs, or from the input digital clock for digital inputs.

- The Panel Clock is the timing clock for panel data at the one pixel per clock rate. The actual PCLK to the panel may be one-half that frequency for double-pixel panel data format. When its frequency is different from that of source clock, the panel clock is generated by Destination Clock (or DCLK) DDS/PLL.

There are six display modes: Native, Slow DCLK, Expansion, Downscaling, Destination Stand Alone, Source Stand Alone.

Each mode is unique in terms of:

- input video resolution vs. panel resolution,

- Source Clock frequency / Panel Clock frequency ratio,

- Source Hsync frequency / Panel Hsync frequency ratio,

- data source (video input, panel background color, on-chip pattern generator).

#### 1.6.1 Native

Panel clock frequency = Source clock frequency Panel Hsync frequency = Input Hsync frequency Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is the same as the panel resolution and the input data clock frequency is within the panel clock frequency specification of a panel being used.

#### 1.6.2 Slow DCLK

Panel clock frequency < Source clock frequency Panel Hsync frequency = Input Hsync frequency Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is the same as the panel resolution, but the input data clock frequency exceeds the panel clock frequency specification of a panel being used. The panel clock is scaled to the Source clock, and the internal data buffers are used to spread out the timing of the input data by making use of the large CRT blanking time to extend the panel horizontal display time.

#### 1.6.3 Expansion

Panel clock frequency > Source clock frequency Panel Hsync frequency > Input Hsync frequency Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is less than the panel resolution. The input data clock is then locked to the panel clock, which is at a higher frequency. The input data is expanded.

#### 1.6.4 Downscaling

Panel clock frequency > Source clock frequency Panel Hsync frequency < Input Hsync frequency Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is greater than the panel resolution, and is used to provide enough of a display to enable the user to recover to a supported resolution. The input clock is operated at a frequency less than that of the input pixel rate (under-sampled horizontally) and the expander function is used to drop input lines. Expansion interpolation is not provided and must be off.

1.6.5 Destination Stand Alone

Panel clock = DCLK in open loop (not locked) Panel Hsync frequency = DCLK frequency / (Destination Htotal register value) Panel Vsync frequency = DCLK frequency / (Destination Htotal register value \* Destination Vtotal register value)

This mode is used when the input is changing or not available. The OSD may still be used as in all other display modes, and stable panel timing signals are produced. This mode may be automatically set when the gmB135 detect input timing changes that could cause out-of-spec operation of the panel.

1.6.6 Source Stand Alone

Panel clock = SCLK in open loop (not locked to input Hsync) Panel Hsync frequency = SCLK frequency / (Source Htotal register value) Panel Vsync frequency = SCLK frequency / (Source Htotal register value \* Source Vtotal register value)

This mode is used to display the Pattern Generator Data. This mode may be useful for testing an LCD panel on the manufacturing line (color temperature calibration, etc.).

## 1.7 Input Video Mode Support

The gmB135 can support various standard VGA/VESA/Macintosh display modes depending on the LCD panel specifications. By default, all data input is expanded to full-panel-screen resolution. An Excel 97 spreadsheet (Mode Support.XLS) showing the relationship between panel specifications and supported modes is provided separately. Note that in the spreadsheet, the user needs to supply the panel parameters that are marked in blue. The spreadsheet will automatically determine whether the listed modes can be supported based on the user-supplied panel parameters.

## 2. Functional Block Description.

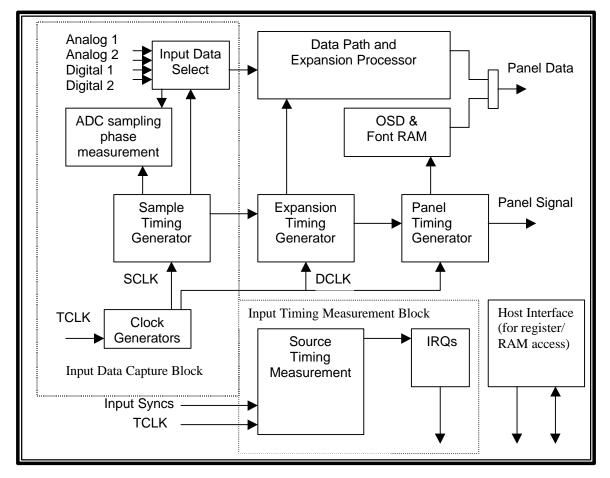

Figure 2.1 shows the high-level block diagram of gmB135 chip. Each block is described in detail in this chapter.

Figure 2.1 Functional Block Diagram of gmB135

## 2.1 Input Data Capture Block

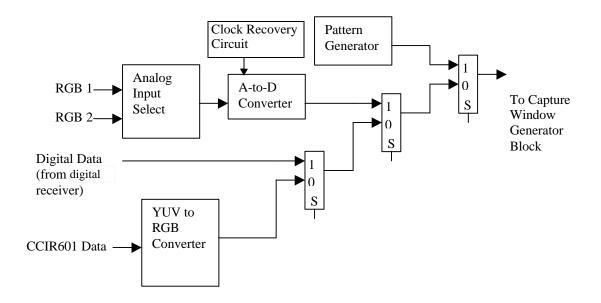

Input data capture block consists of two major function blocks: (1)data source block and (2)source timing generator block.

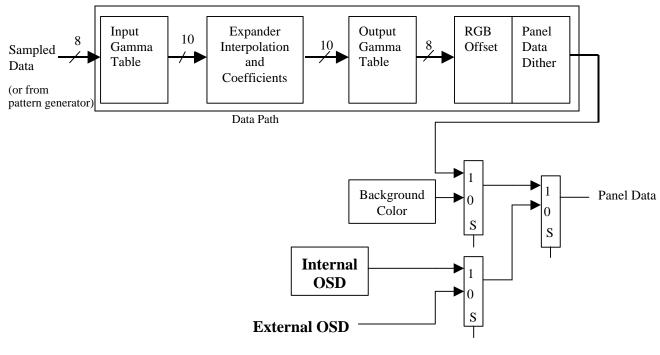

The data source block consists of input ports, analog-to-digital converter (ADC), and clock-recovery circuit. There are four input ports: two analog and two digital. This block receives video data input and digitizes it if the video data is analog or perform YUV-to-RGB conversion if the video data is CCIR601 compatible.

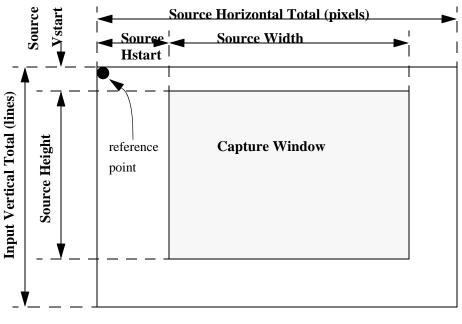

Sitting right after the data source block, the source timing generator (STG) block sets a "capture window." The data within this window gets sent to the data path block.

2.1.1 Input ports

gmB135 has four video inputs:

- Analog input port 1,

- Analog input port 2,

- Digital input port 1,

- Digital input port 2 (for CCIR601-compatible, YUV format data).

Only one input is selected at a time via a register programming.

Figure 2.1.1 Data Source Block Diagram

#### 2.1.1.a Analog input ports

Two analog input ports are connected to the same 3-channel ADCs and clock recovery circuit through an analog multiplexer inside the gmB135 chip.

| Pin No.       | Pin Name          |                                                                                                         |

|---------------|-------------------|---------------------------------------------------------------------------------------------------------|

| Analog Port 1 |                   |                                                                                                         |

| TBD           | RED1+             | Positive analog input for the Red channel 1.                                                            |

| TBD           | RED1-             | Negative analog input for the Red channel 1.                                                            |

| TBD           | GREEN1+           | Positive analog input for the Green channel 1.                                                          |

| TBD           | GREEN1-           | Negative analog input for the Green channel 1.                                                          |

| TBD           | BLUE1+            | Positive analog input for the Blue channel 1.                                                           |

| TBD           | BLUE1-            | Negative analog input for the Blue channel 1.                                                           |

| C1            | VSYNC1            | CRT Vsync input 1. Enabled when analog port 1 is selected. TTL Schmitt trigger input.                   |

| A1            | HSYNC1/<br>CSYNC1 | CRT Hsync or composite sync input 1. Enabled when analog port 1 is selected. TTL Schmitt trigger input. |

| Analog Port 2 |                   |                                                                                                         |

| TBD           | RED2+             | Positive analog input for the Red channel 2.                                                            |

| TBD           | RED2-             | Negative analog input for the Red channel 2.                                                            |

| TBD           | GREEN2+           | Positive analog input for the Green channel 2.                                                          |

| TBD           | GREEN2-           | Negative analog input for the Green channel 2.                                                          |

| TBD           | BLUE2+            | Positive analog input for the Blue channel 2.                                                           |

| TBD           | BLUE2-            | Negative analog input for the Blue channel 2.                                                           |

| B2            | VSYNC2            | CRT Vsync input 2. Enabled when analog port 2 is selected.TTL Schmitt trigger input.                    |

| B1            | HSYNC2/<br>CSYNC2 | CRT Hsync or composite sync input 2. Enabled when analog port 2 is selected.TTL Schmitt trigger input.  |

#### 2.1.1.b Digital input port 1

The digital input port 1 can be configured either for 1 pixel/clock or for 2 pixels/clock. For data mapping information, refer to Table 1.4.7. on page 15. Panel output interface can be set to either 1 pixel/clock or 2 pixels/clock independent of the digital input port configuration.

This input port is to be connected to the output port of a digital receiver chip such as TMDS receiver. The minimum setup/ hold time of this port is 1.5 ns. If the output of a receiver cannot meet this setup/hold time requirement, the clock input should be delayed inside gmB135. The delay value can be programmed in the range of 2 - 45 ns.

#### 2.1.1.c CCIR601 input port

This input port is for the YUV video data. It is to be connected to a digital TV decoder chip that generates CCIR601-compatible video data.

Both 8 and 16 bit wide data are supported. For 8-bit data the input order is: U, Y0, V, Y1 ... For the 16-bit data the D7:0 input order is: Y0, Y1, Y2, Y3 ... The D15:8 input order is: U0, V0, U2, V2, ...

For data mapping information, refer to Table 1.4.6. on page 14. In 8-bit configuration, 2x video clock must be provided.

The U and V color component is the color for the first luminance sample of each pair of Y data. When this input data is reformatted for color conversion the "missing" U and V data for the other luminance data is merely the replicated U and V data.

For CCIR601 data the input Gamma Table will be used to provide both the proper gamma correction for the TV input and to re-scale the YUV-RGB converted data to the full 00h to FFh range.

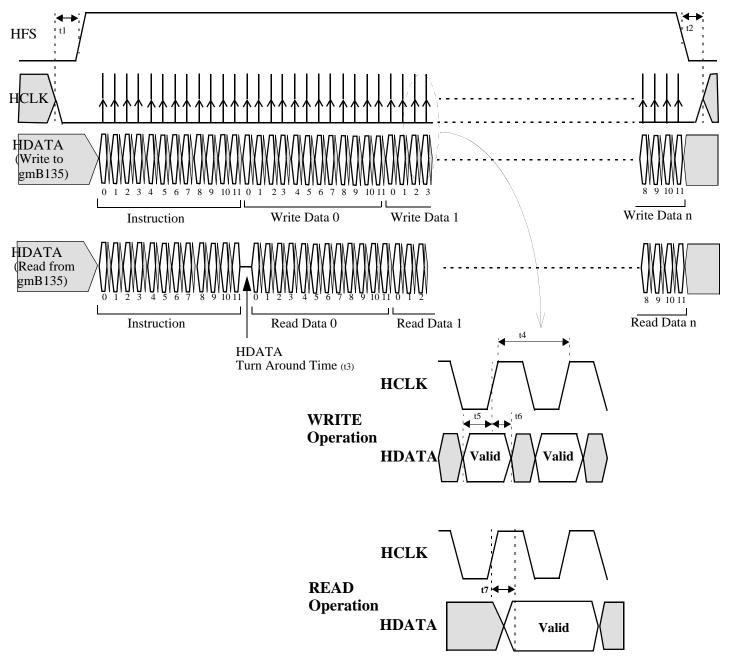

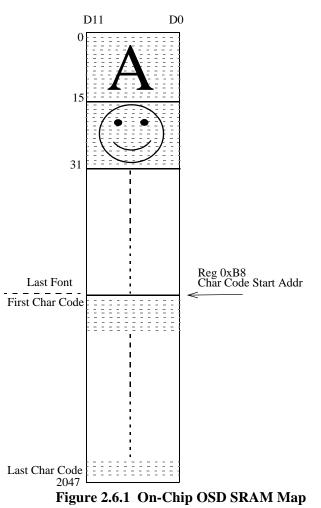

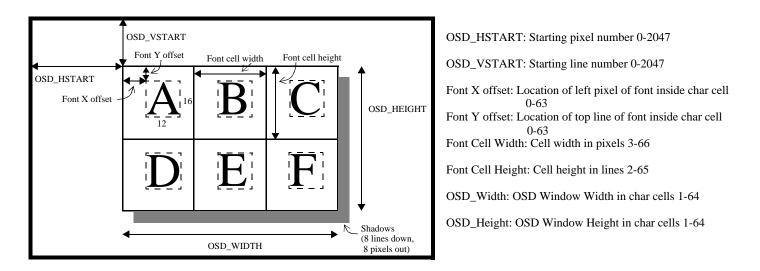

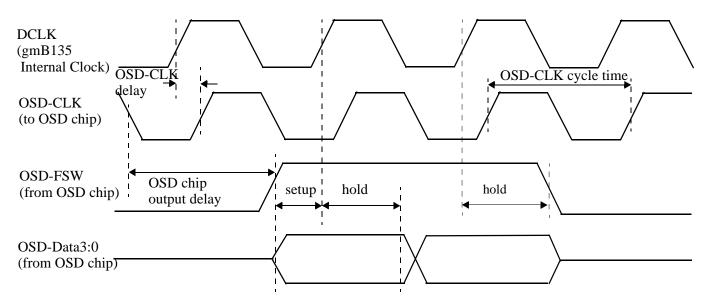

The YUV to RGB conversion equations used are: