# B5110/B5120

# **BIT SPARC Floating Point Chip Set**

# FEATURES

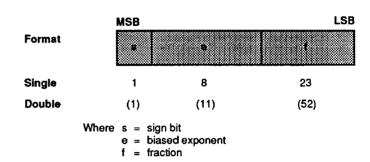

- Complete floating point and integer processor chip set supports the ANSI/IEEE STD. 754 and DEC (F&G) formats. Intended for use with the B5100 SPARC FPC as part of a BIT SPARC B5000 based CPU.

- Functionally equivalent to the B3110A/B3120A except for the addition of a pin-fin heat sink and improved AC parameters.

- Four data formats 64-bit floating point 32-bit floating point 64-bit integer (fixed point) 32-bit integer (fixed point)

- Flowthrough architecture

MFLOPS double precision multiply data rate

MFLOPS double precision ALU data rate

MIPS integer data rate

- Complete instruction set

Floating point instructions include:

Multiply, divide, square root, add, subtract, absolute value, negate, min/max, compare

Multiply, add, subtract, boolean functions, shift and rotate Conversion operations to/from all supported formats

Three port architecture Parity generation and checking Scan paths through all registers

Integer instructions include:

- Fast or wrapped underflow and overflow in IEEE mode

- Synchronous and asynchronous output enables for status flags and output ports

- ECL 10KH compatible interface

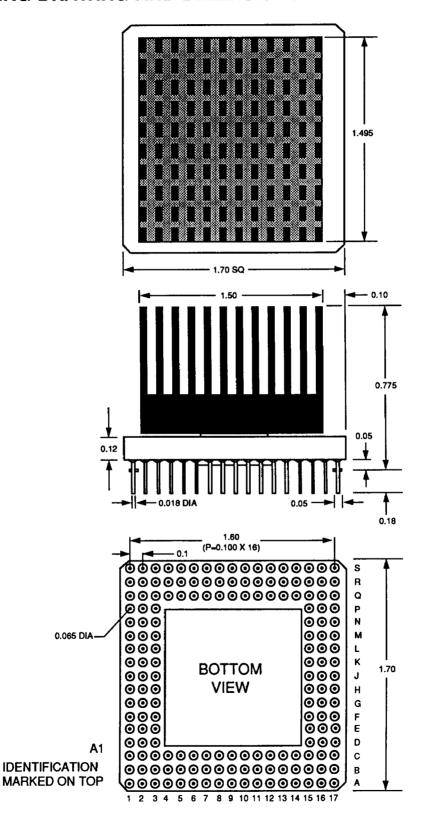

- 169-lead pin-grid-array package

# **■ DESCRIPTION**

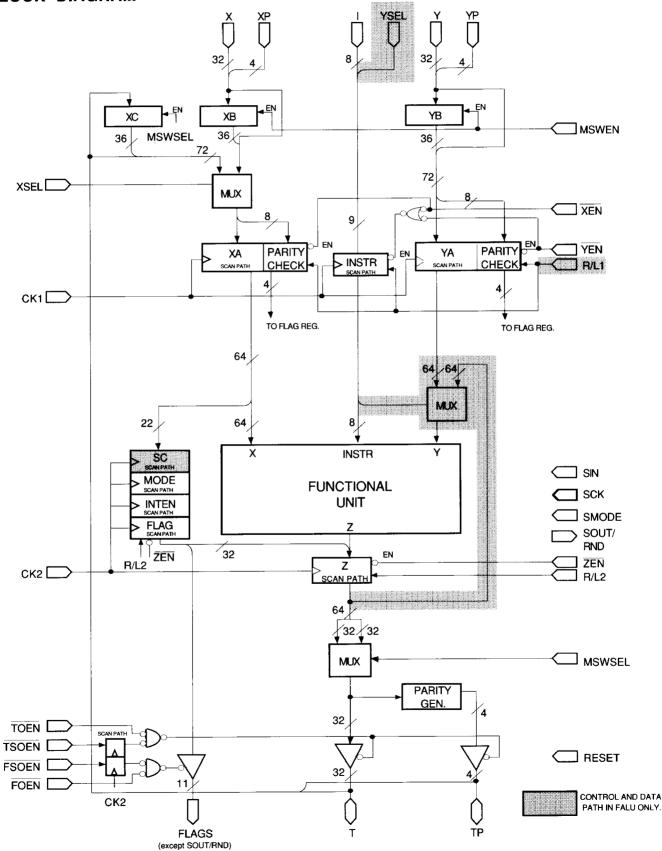

The B5110 floating point multiplier (FMPY) and B5120 floating point arithmetic logic unit (FALU) provide very high performance floating point and integer operations. Because they are fabricated with BIT's high performance VLSI process, the need for multiple pipeline stages normally associated with floating point processors can be eliminated. This architecture allows higher performance than can be attained with heavily pipelined floating point units, simplifying microcode and compiler code generation, system timing and control hardware. All floating point operations can be either single or double precision and are fully compatible with the IEEE standard 754 or DEC F and G formats. The floating point instruction set includes add, subtract, multiply, and conversion operations. In addition, floating point divide, square-root, minimum, maximum, and compare instructions are provided. All four IEEE rounding modes are supported.

The floating point chip set also has a large repertoire of 32- and 64-bit integer functions. A 64-bit integer ALU and barrel shifter provide very high performance for both 32- and 64-bit integer operations. Functions include add and subtract (with and without carry/borrow), negate, absolute value, all 16 boolean functions, rotate, logical shift, arithmetic shift, (32-bit) bit reverse, and rotate two concatenated 32-bit operands. Shifts and rotates use an internal register to define shift distance.

The three port architecture of the FMPY and FALU provides maximum performance. They FMPY provide 72-bit edge-triggered registers at the input ports and a 64-bit transparent latch or edge-triggered register on the output port. Individual clock enables are provided for both input registers and the output register. The output port can also be used as an input port to allow intermediate results to be passed between the FMPY and FALU. Thirteen status flags are provided (interrupt, negative, zero, overflow, underflow, invalid operation, inexact result, rounded up, not-a-number, denormalized input, divide by 0, carry and parity error).

Output enables can be either synchronous, asynchronous or both. The synchronous output enable option helps reduce bus conflicts.

Byte parity on each port is provided for increased system reliability. Built in test features include scan paths through all registers.

# ■ SIGNAL SUMMARY

| Date<br>Incute     | Section of the second section of                 |                                       |

|--------------------|--------------------------------------------------|---------------------------------------|

| and the same of    | Mes of XPIs of Vist of APIs of<br>Tis of TPIs of |                                       |

|                    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1            |                                       |

| (*:);(;e)          |                                                  |                                       |

| Instruction        | F7 ()                                            |                                       |

| Flags              | NT PE N                                          | - 11                                  |

|                    | ZP, CV, UF NX                                    |                                       |

|                    | INV NeN CEN                                      |                                       |

|                    | DIVZ (FMPY only)                                 |                                       |

|                    |                                                  |                                       |

|                    | CRY (FALU only)                                  |                                       |

| Mode Select        | R/L11FALU only), R/L2                            |                                       |

|                    | PESET                                            |                                       |

| Multiplexor Select | XSEL*                                            |                                       |

|                    | YSEL (FALU only)                                 | •                                     |

|                    | ZEN XEN VEN                                      |                                       |

| Clock Enables      |                                                  | 3 2 2                                 |

| Output Enables     | TOEN, FOEN                                       | 4                                     |

|                    | TSOEN FROEN                                      |                                       |

|                    | AND STATEMENT ASSESSED.                          |                                       |

| Clocks             | CKI, CK2 MSWSEL MSWEN                            |                                       |

| Scen Path          |                                                  |                                       |

| input              | SMODE SCK SIN                                    | 9                                     |

| Cutout             | SOUTAND                                          | · · · · · · · · · · · · · · · · · · · |

| ****               |                                                  |                                       |

|                    |                                                  |                                       |

| Pawer              |                                                  |                                       |

| Look Ground        | YCC                                              | 10                                    |

| Oribut Ground      | VCC2                                             |                                       |

| -5.2V              | VEE                                              |                                       |

|                    |                                                  |                                       |

|                    |                                                  |                                       |

| Total              |                                                  |                                       |

|--|

32-bit X input port

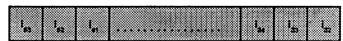

# DATA X[31..0]

| XP[30]  | Byte parity bits corresponding to the X input port         |

|---------|------------------------------------------------------------|

| Y[310]  | 32-bit Y input port                                        |

| YP[30]  | Byte parity bits corresponding to the Y input port         |

| T[310]  | 32-bit T bidirectional port                                |

| TP[30]  | Byte parity bits corresponding to the T bidirectional port |

| CONTROL |                                                            |

| I[70]   | 8-bit instruction port. Determines the instruction         |

| l[70] | 8-bit instruction port. Determines the instruction executed by the floating point chip set.                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| INT   | Interrupt flag; asserted if the appropriate bits are enabled in the interrupt enable register and the corresponding condition is true. |

| PE    | Parity flag; asserted whenever a byte parity error is detected by on-chip circuitry at ports X, Y, or T.                               |

| N | Negative flag; asserted whenever a computation       |

|---|------------------------------------------------------|

|   | produces a result which has its most significant bit |

|   | set.                                                 |

| ZR | Zero flag; asserted whenever a computation |

|----|--------------------------------------------|

|    | produces a result equal to zero.           |

|    |                                            |

OV Overflow flag; this bit is set if the result of an operation is larger than the maximum representable normalized number in the chosen format.

Underflow flag; this bit is set if the result of an operation is less than the minimum representable normalized number in the chosen format.

Inexact flag; asserted whenever the result of a INX computation is not infinitely precise.

UF

R/L1, R/L2

RESET

Invalid operation flag; asserted whenever an op-INV erand is invalid for the operation to be performed.

Not a number flag; asserted whenever operands or NaN the result of a computation has no numerical significance (IEEE), or a reserved operand (DEC).

SOUT/RND The SOUT/RND pin normally outputs the rounded up flag (SMODE not asserted). Asserted when the magnitude of the infinitely precise result is less than the magnitude of the returned result. In scan

I/O mode, scan data is output. The SOUT/RND pin is not affected by output enables.

DEN Denormalized flag; asserted whenever one of the input operands is a denormalized number.

DIVZ (FMPY) Divide by zero flag; asserted when a finite nonzero number is divided by zero.

CRY (FALU) Carry flag; asserted during integer arithmetic operations whenever there is a carry out of the most significant result bit. For shift and rotate opera-

tions, set equal to the last bit shifted out.

Not applicable for the B5110/B5120. Both inputs must be tied to a 10KH high level. For latch mode operation see the B3110A/3120A.

Hardware reset. Asynchronously resets the mode, interrupt mask, flag and SC registers when

asserted high.

**XSEL** Input multiplexer select for register XA. Selects the X port when low. Selects the T port when high.

**YSEL** Input multiplexer for operand port Y. Selects the Y port when low. Selects the Z result when high (FALU only). Clocked same as 10-7.

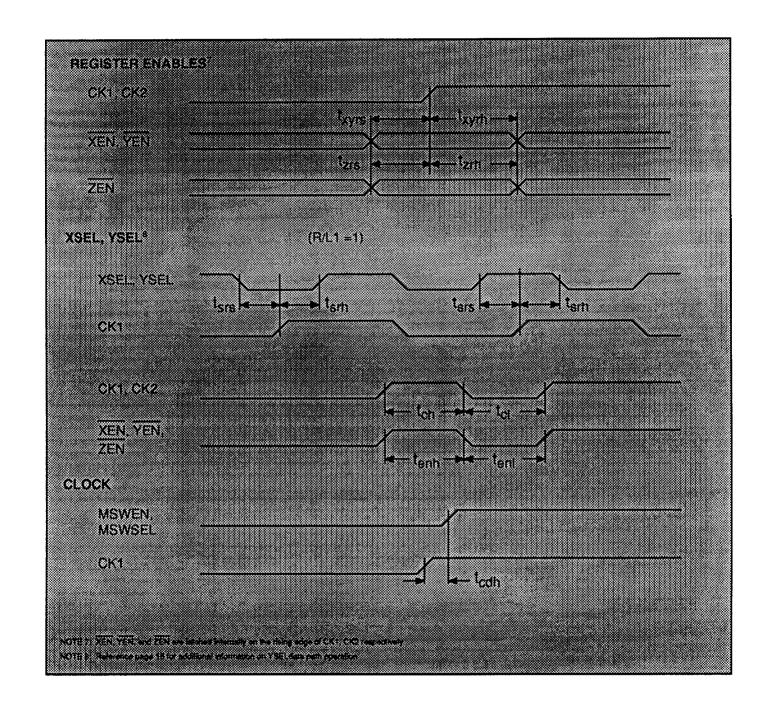

**XEN** Active low enable for CK1 at XA. Opcode register/ latch is enabled if either XEN or YEN is true.

YEN Active low enable for CK1 at YA. Opcode register/

latch is enabled if either XEN or YEN is true.

ZEN Active low enable for CK2 (the clock is always enabled for TSOEN and FSOEN).

# B5110/B5120

# ■ SIGNAL DESCRIPTION (cont'd)

| OI. | ITPI | IT | ₽N | ΔR | LES |

|-----|------|----|----|----|-----|

|     |      |    |    |    |     |

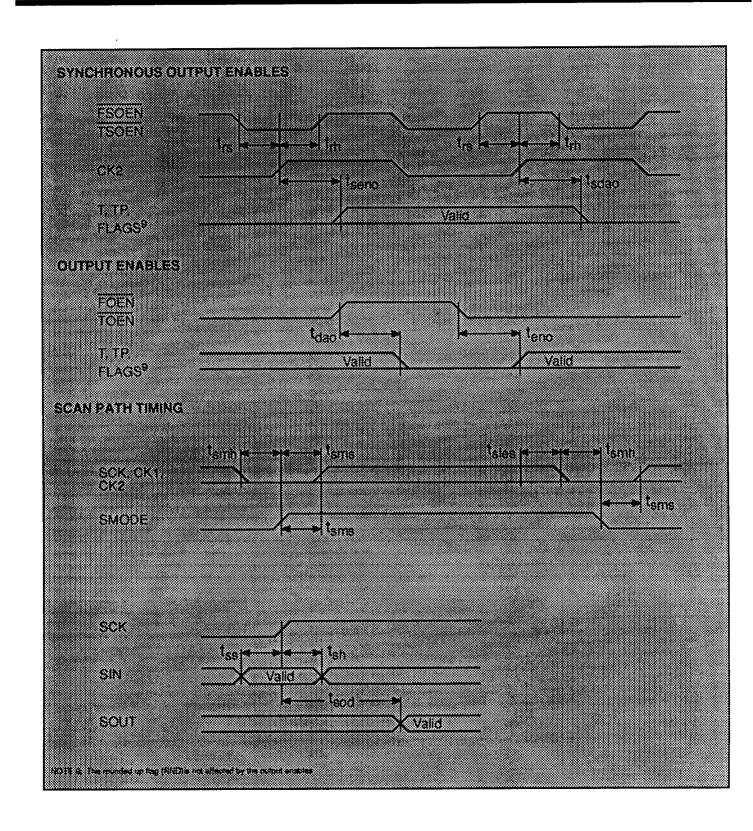

<u>TOEN</u> Active low output enable for the T output port.

FOEN Active low output enable for the flag port.

TSOEN Synchoronous active low output enable for the T

port

FSOEN Synchronous active low output enable for the flag

port.

**CLOCKS**

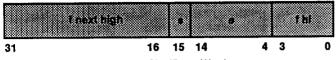

CK1 Input clock for the X and Y ports, the instruction

port, and YSEL. In register mode, data is clocked

on the rising edge of the clock.

CK2 Output clock for computation results, flags, and

internal register writes. In register mode data is

clocked on the rising edge of the clock.

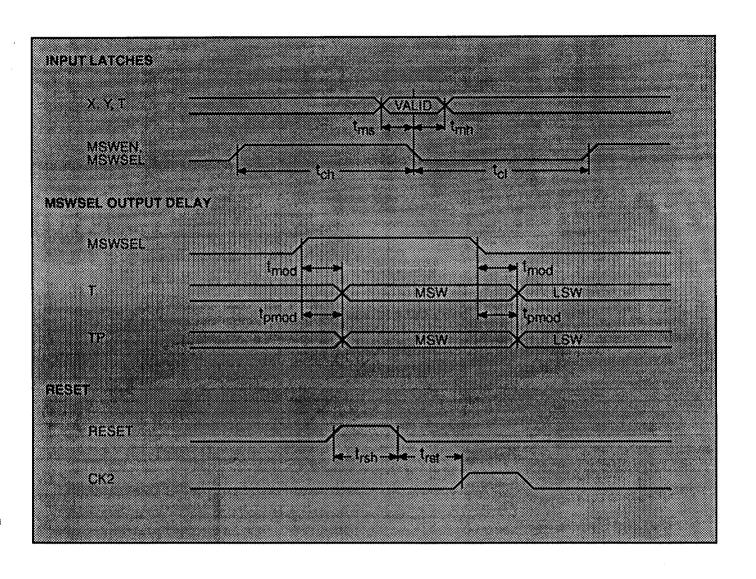

MSWSEL Multiplexer clock for output port T and clock for

latch XC. Selects the most significant word of the T port and opens latch XC when high. For single precision operations, the 32-bit result in register Z will be selected, regardless of the state of

MSWSEL.

MSWEN Clock which opens the input demultiplexing latch

on X and Y ports. Latches are transparent when

high.

**SCAN PATH**

SMODE Configures the on-chip registers in the scan path

into a serial shift register when high. The RND flag is output on SOUT when the SMODE pin is

low.

SCK Clock which shifts data in the scan path. Ignored

when SMODE is low, overrides CK1 and CK2 when SMODE is high. Rising edge triggered.

SIN Input port to the scan path.

SOUT/RND Scan path output when SMODE is asserted;

otherwise RND flag (see flag description).

**POWER**

VCC1 Most positive supply voltage to internal circuitry.

Usually ground.

VCC2 Most positive supply voltage to output circuitry.

Usually ground.

VEE Most negative supply.

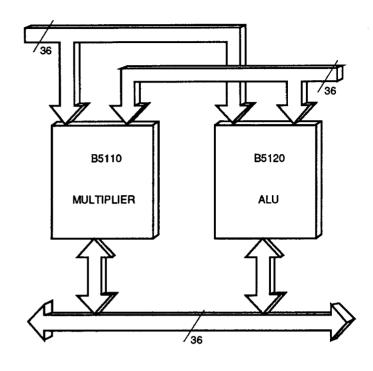

# BLOCK DIAGRAM

# B5110/B5120

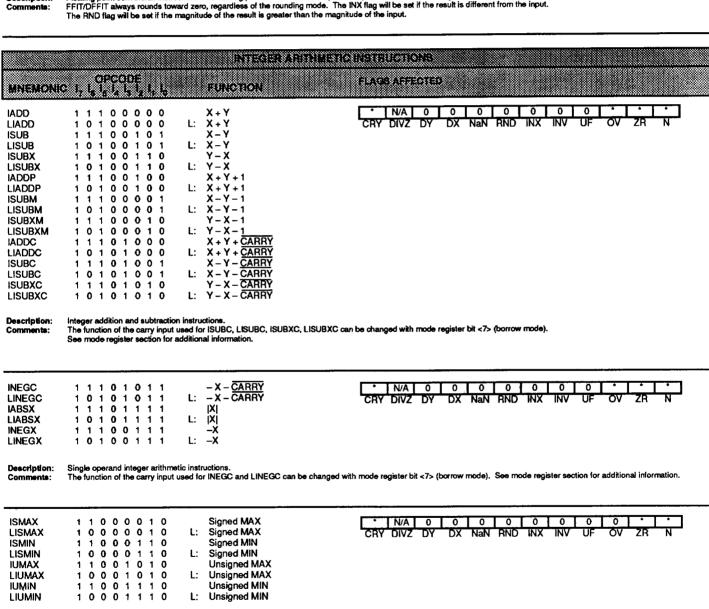

# ■ INSTRUCTION SET

The B5110/B5120 instruction set supports numeric intensive, bit manipulation and general purpose computing applications.

The instruction operation codes of the FMPY and FALU were encoded to allow the same 8-bit instruction stream (I[7..0]) to be sent to each device.

The FMPY performs four types of operations: multiply, divide, square root, and pass operand. The FALU performs all other operations.

Three instructions are provided to perform sum of product operations (MAC/DMAC, MACS/DMACS, SMAC/DSMAC) where the same instruction opcode is interpreted by the FMPY as a multiply and the FALU as an add or subtract.

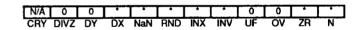

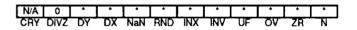

#### FLAGS

The following rules apply towards the flag charts in the instruction description section.

An overflow condition will return infinity (or DEC reserved operand) if the wrapped overflow mode is reset. An overflow condition will return a wrapped number if the wrapped overflow mode is set, independent of the wrapped underflow mode.

If the wrapped underflow mode is reset, both the FMPY and FALU treat denormalized inputs as exact zeros. If the wrapped underflow mode is set, the FALU handles denormalized inputs directly, whereas the FMPY treats them as inexact zeros.

The following sections have been included:

- Instruction symbols

- Instruction set description

# **■ INSTRUCTION SYMBOLS**

| SYMBOL   | DEFINITION                                             |

|----------|--------------------------------------------------------|

| CRY      | Carry                                                  |

| DEN      | Denormalized number                                    |

| DIVZ     | Divide by 0                                            |

| DP       | 64 bit floating point number                           |

| DX       | Denormalized input X                                   |

| DY       | Denormalized input Y                                   |

| Ē.       | Smallest magnitude normalized number                   |

| FALU     | Floating point arithmetic logic unit                   |

| FMPY     | Floating point multiplier                              |

| INF      | Infinity                                               |

| INV      | Invalid                                                |

| INX      | Inexact                                                |

| Ľ        | Long integer - 64 bits                                 |

| M        | Largest magnitude normalized number                    |

| N        | Negative                                               |

| n        | User determined binary number                          |

| N/A      | Not applicable                                         |

| NaN      | Not a number                                           |

| NORM     | Normalized number                                      |

| OV       | Overflow                                               |

| Q        | Quiet NaN                                              |

| R        | DEC reserved operand                                   |

| RND      | Rounded up                                             |

| S        | Signaling NaN                                          |

| sb       | Sticky bit                                             |

| SP       | 32 bit floating point number                           |

| UF       | Underflow                                              |

| WRP      | Wrapped number                                         |

| ZR       | Zero                                                   |

| <b>√</b> | Square root                                            |

| 1        | Divide                                                 |

| •        | Multiply                                               |

|          | Indicates status flags are affected                    |

| ! .      | Concatenation                                          |

| ļļ       | Absolute value                                         |

| [,]      | Items within braces are alternative items, one of them |

|          | must be used                                           |

# ■ INSTRUCTION SET DESCRIPTION

| MNEMONIC    | OPC | opi |  |  |   | FI | OA<br>Gerri | ING PI | ) TARC | KRITI | METIC | INST<br>FLAG | RUC<br>3 AF | TIC | HS<br>HEE |    |     |     |          |          |    |    |    |   |   |

|-------------|-----|-----|--|--|---|----|-------------|--------|--------|-------|-------|--------------|-------------|-----|-----------|----|-----|-----|----------|----------|----|----|----|---|---|

| DIV<br>DDIV | 0 0 |     |  |  | _ | DI | X/Y         |        |        |       |       | N/A<br>CRY   | DIV         | Ţ   | Y         | DX | NaN | RND | INX<br>• | INV<br>• | UF | ٥٧ | ZR | N | ] |

Description: Floating Point Division.

In the tables below, the first entry represents the flag that is set, the second represents the returned result. When the FALU receives this opcode, it returns a zero result.

## IEEE-WRAPPED UNDERFLOW MODE

# X OPERAND

| Υ   |         |            | DEN.       | NOTA                               | S S S      | •          |            |

|-----|---------|------------|------------|------------------------------------|------------|------------|------------|

| 0   |         | INV, NaN/Q | DIVZ/INF   | DIVZ/INF                           | INF        | NANQ       | INV, NaN/Q |

| Р   | 20 to 1 | ZR/0       | INV, NaN/Q | INX, DIVZ/INF                      | INF        | NAN/Q      | INV, NaN/Q |

| E R | NORM    | ZR/0       | INX, ZR/o  | OV/[WRP, INF, M]<br>NORM<br>UF/WRP | INF        | NAN/Q      | INV, NaN/Q |

| N   |         | ZR/0       | ZR/0       | ZR/0                               | INV, NaN/Q | NaN/Q      | INV, NaN/Q |

| U   |         | NaN/Q      | NaN/Q      | NaN/Q                              | NaN/Q      | NaN/Q      | INV, NaN/Q |

|     |         | INV, NaN/Q | INV, NaN/Q | INV, NaN/Q                         | INV, NaN/Q | INV, NaN/Q | INV, NaN/Q |

## DEC MODE

### X OPERAND

Ď

| Υ       | - 0   | NORM    | 9     |

|---------|-------|---------|-------|

| 0       | INV/R | DIVZ/R  | INV/R |

| Р       |       | OV/R    |       |

| E NO    | ZR/0  | NORM    | INV/R |

| R       |       | UF,ZR/0 |       |

| A MARIE | INV/R | INV/R   | INV/R |

| N       |       |         |       |

#### IEEE-WRAPPED UNDERFLOW MODE DISABLED

#### X OPERAND

| Υ           |      |            | (0) E(1)   | Nie)gi).                                    | Ripass     |            | ::::::::::::::::::::::::::::::::::::::: |

|-------------|------|------------|------------|---------------------------------------------|------------|------------|-----------------------------------------|

| 0           | 6    | INV, NaN/Q | INV, NaN/Q | DIVZ/INF                                    | INF        | NAN/Q      | INV, NaN/Q                              |

| Ρ           | DEN  | INV, NaN/Q | INV, NaN/Q | DIVZ/INF                                    | INF        | NAN/Q      | INV, NaN/Q                              |

| E<br>R<br>A | NORM | ZR/0       | ZR/0       | OV/[WRP, INF, M]<br>NORM<br>UF, [ZR]/[0, E] | INF        | NAN/Q      | INV, NaN/Q                              |

| N           | NA.  | ZR/0       | ZR/0       | ZR/0                                        | INV, NaN/Q | NaN/Q      | INV, NaN/Q                              |

| U           | 9    | NaN/Q      | NaN/Q      | NaN/Q                                       | NaN/Q      | NaN/Q      | INV, NaN/Q                              |

|             |      | INV, NaN/Q | INV, NaN/Q | INV, NaN/Q                                  | INV, NaN/Q | INV, NaN/Q | INV, NaN/Q                              |

| SQRTX  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | ~    |

|--------|---|---|---|---|---|---|---|---|------|

| DSQRTX | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | DP:√ |

Description:

Floating Point Square Root. The square root of operand X is returned.

The Y operand should not be changed during square root instructions. In the tables below, the first entry represents the flag that is set, the second represents the result returned to Z. When the FALU receives this opcode, it returns a zero result. Comments:

### IEEE-WRAPPED UNDERFLOW MODE

| XOPERAND |            |

|----------|------------|

| S        | INV, NaN/Q |

| Q        | NaN/Q      |

| -INF     | INV, NaN/Q |

| -NORM    | INV, NaN/Q |

| -DEN     | INV, NaN/Q |

| -0       | ZR/-0      |

| +0       | ZR/+0      |

| +DEN     | INX, ZR/0  |

| +NORM    | +NORM      |

| +INF     | +INF       |

### IEEE-WRAPPED UNDERFLOW MODE DISABLED

|       | ************************************** |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|

| S     | INV, NaN/Q                             |  |  |  |  |

| Q     | NaN/Q                                  |  |  |  |  |

| -INF  | INV, NaN/Q                             |  |  |  |  |

| -NORM | INV, NaN/Q                             |  |  |  |  |

| -DEN  | ZR/-0                                  |  |  |  |  |

| -0    | ZR/-0                                  |  |  |  |  |

| +0    | ZR/+0                                  |  |  |  |  |

| +DEN  | ZR/+0                                  |  |  |  |  |

| +NORM | +NORM                                  |  |  |  |  |

| +INF  | +INF                                   |  |  |  |  |

### DEC MODE

| R     | INV/R |

|-------|-------|

| +0    | ZR/0  |

| +NORM | +NORM |

| -NORM | INV/A |

# B5110/B5120

|          |     |       |            |   |              |      |       |          |  | W.C    |            |          |         |          |          |         |          |          |      |         |    |     |   |

|----------|-----|-------|------------|---|--------------|------|-------|----------|--|--------|------------|----------|---------|----------|----------|---------|----------|----------|------|---------|----|-----|---|

| MNEMONIC |     | (0.0) |            |   | FI           | Net  | ЮN    |          |  | FL.4   |            | e e e    | CTEL    |          |          |         |          |          |      |         |    |     |   |

|          |     |       |            |   |              |      |       |          |  |        |            |          | ******* | ******** |          | ******* |          |          | ~~~~ | ******* |    |     |   |

| MULTWX   | 000 |       |            | 0 |              | RAPP |       |          |  | <br>N/ |            | o I      | *       | *        | *        |         | ·        | 1 :      | •    | 0       | *  | ٠ . | 1 |

|          |     |       | 1 0<br>1 0 | - | WF<br>WF: WF |      | ED X• | •Y<br>•Y |  | CR     | ( ]<br>/ D | 0<br>IVZ | DY      | DX       | *<br>NaN | RND     | INX<br>• | INV<br>I | UF   | 0<br>OV | ŻR | N   | ] |

Description: Comments:

Floating Point Multiplication. The wrapped operand is multiplied by [X, Y].

Floating Point Multiplication. The wapped operand is multiplied by [X, Y]. The chip must have IEEE Underflow mode set to one, or underflows (wrapped outputs) will be set to zero. The wrapped multiply instructions assume that one of their operands is a wrapped underflow. They do not work on wrapped overflows.

The result of WRAPPED X \* WRAPPED Y is always too small to make a denormalized number, thus the result always underflows and no instruction is provided. The denormalized number flag will not be set if the wrapped number looks like a denormalized number.

If the result is too small to return as a wrapped number, then the underflow and zero flags are raised, and inexact zero is returned.

In the tables below, the first entry represents the flag that is set, the second represents the returned result. When the FALU receives this opcode, it returns a zero result.

### **IEEE-WRAPPED UNDERFLOW MODE**

#### IEEE-WRAPPED UNDERFLOW MODE DISABLED

| UNWHAPPED |            |  |  |  |  |  |

|-----------|------------|--|--|--|--|--|

| OPERAND   | Z RESULT   |  |  |  |  |  |

| 0         | ZR/0       |  |  |  |  |  |

| DEN       | INX, ZR/0  |  |  |  |  |  |

|           | NORM       |  |  |  |  |  |

| NORM      | UF/WRP     |  |  |  |  |  |

|           | ZR, UF/01  |  |  |  |  |  |

| JNF       | INF        |  |  |  |  |  |

| Q         | NaN/Q      |  |  |  |  |  |

| S         | INV, NaN/Q |  |  |  |  |  |

| Note <sup>1</sup> : | Double underflowthe result is         |

|---------------------|---------------------------------------|

|                     | too small to return a wrapped result. |

| OPERANO | Z RESULT        |

|---------|-----------------|

| 0       | ZR/0            |

| DEN     | ZR/0            |

|         | NORM            |

| NORM    | UF, [ZR]/[0, E] |

| INF     | INF             |

| Q       | NaN/Q           |

| S       | INV, NaN/Q      |

| MULT    | ^ | ^ | ^ | ^ |   | 0 | ^ | ^ | X•Y       |

|---------|---|---|---|---|---|---|---|---|-----------|

|         | _ | _ | _ | _ |   | _ | _ | _ |           |

| DMULT   | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | DP: X•Y   |

| MULTAY  | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | X• Y      |

| DMULTAY | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | DP: X• Y  |

| MULTAX  | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | X •Y      |

| DMULTAX | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | DP: XI-Y  |

| MULTA   | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | [X•Y]     |

| DMULTA  | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | DP: jX•Yj |

VADEDAND

D

Description:

Floating Point Multiplication. [[X], [Y]] represents the absolute value of [X, Y]; [X\* Y] is the absolute value of the result.

In the tables below, the first entry represents the flag that is set, the second represents the returned result. When the FALU receives this opcode, it returns a zero result.

## IEEE-WRAPPED UNDERFLOW MODE

### DEC MODE

| X | 0 | Ρ | Е | R | Α | ١ | i | ľ |

|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |

| Υ           |               | ij         | DEN        | 10034                              | INF        |            |            |

|-------------|---------------|------------|------------|------------------------------------|------------|------------|------------|

| 0           | •             | ZR/0       | ZR/0       | ZR/0                               | INV, NaN/Q | NAN/Q      | INV, NaN/Q |

| Ρ           | 325           | ZR/0       | INX, ZR/0  | INX, ZR/0                          | INF        | NAN/Q      | INV, NaN/Q |

| E<br>R<br>A | NORM          | ZR/0       | INX, ZR/0  | OV/[WRP, INF, M]<br>NORM<br>UF/WRP | INF        | NAN/Q      | INV, NaN/Q |

| L/A         | in the second | INV, NaN/Q | INF        | INF                                | INF        | NaN/Q      | INV, NaN/Q |

| U           |               | NaN/Q      | NaN/Q      | NaN/Q                              | NaN/Q      | NaN/Q      | INV, NaN/Q |

|             |               | INV, NaN/Q | iNV, NaN/Q | INV, NaN/Q                         | INV, NaN/Q | INV, NaN/Q | INV, NaN/Q |

|        | V OLEHWIND                              |       |          |       |

|--------|-----------------------------------------|-------|----------|-------|

| Υ      |                                         |       | NORM     | 9     |

| 0      |                                         | ZR/0  | ZR/0     | INV/R |

| Ρ      |                                         |       | OV/R     |       |

| Ē      | NORM                                    | ZR/0  | NORM     | INV/R |

| Ŗ      |                                         |       | ZR, UF/0 |       |

| A<br>N | ::::::::::::::::::::::::::::::::::::::: | INV/R | INV/R    | INV/R |

## FLOATING POINT ARTHMETIC INSTRUCTIONS (confd) SLACS AFFECTED FUNCTION MNEMONIC

### X OPERAND

#### IEEE-WRAPPED UNDERFLOW MODE DISABLED

| Y           |      | 6          |            | **************************************      |            |            |            |

|-------------|------|------------|------------|---------------------------------------------|------------|------------|------------|

| 0           | **** | ZR/0       | ZR/0       | ZR/0                                        | INV, NaN/Q | NAN/Q_     | INV, NaN/Q |

| Ρ           | 0.5  | ZR/0       | ZR/0       | ZR/0                                        | INV, NaN/Q | NAN/Q      | INV, NaN/Q |

| E<br>R<br>A | NGRM | ZR/0       | ZR/0       | OV/(WRP, INF, M)<br>NORM<br>UF, (ZR)/(0, E) | INF        | NAN/Q      | INV, NaN/Q |

| L)          |      | INV, NaN/Q | INV, NaN/Q | INF                                         | INF        | NaN/Q      | INV, NaN/Q |

| U           | •    | NaN/Q      | NaN/Q      | NaN/Q                                       | NaN/Q      | NaN/Q      | INV, NaN/Q |

|             |      | INV, NaN/Q | INV, NaN/Q | INV, NaN/Q                                  | INV, NaN/Q | INV, NaN/Q | INV, NaN/Q |

| MAC   | 00010010 | X•Y, X+Y     | FMPY                                        |

|-------|----------|--------------|---------------------------------------------|

| DMAC  | 00010011 | DP: X•Y, X+Y | N/A 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1   |

| MACS  | 00010100 | X•Y, X–Y     | CRY DIVZ DY DX NaN RND INX INV UF OV ZR N   |

| DMACS | 00010101 | DP: X•Y, X–Y |                                             |

| SMAC  | 00010110 | X•Y, Y–X     | FALU                                        |

| DSMAC | 00010111 | DP: X•Y, Y–X | 0 N/A * * * * * * * * * * * * * * * * * * * |

|       |          |              | CRY DIVZ DY DX NaN RND INX INV UF OV ZR N   |

Description: Comments:

Floating Point Multiply/Accumulate instruction. Multiplication is performed by the FMPY, whereas addition or subtraction is performed by the FALU. These commands may be used as true multiply/accumulate instructions when the FALU and FMPY outputs are connected and the FALU XSEL and YSEL inputs are high. In this mode, the FMPY output is fed back as the FALU X operand and the FALU result is fed back as the Y operand.

See the ADD and MULT instructions for details regarding the flags and operation result.

| MIN  | 0 0 1 0 0 1 0 0 | FLOATING POINT MIN     | <u> </u>                                | N/A  | •  |     | 1   | 0   | 0   | •   | *  | 0  | •  | • |

|------|-----------------|------------------------|-----------------------------------------|------|----|-----|-----|-----|-----|-----|----|----|----|---|

| DMIN | 00100101        | DP: FLOATING POINT MIN | CRY                                     | DIVZ | DY | DX  | NaN | RND | INX | INV | UF | ÓV | ZR | N |

| MAX  | 00100110        | FLOATING POINT MAX     | • • • • • • • • • • • • • • • • • • • • |      |    | 271 |     |     |     |     |    |    |    |   |

| DMAX | 00100111        | DP: FLOATING POINT MAX |                                         |      |    |     |     |     |     |     |    |    |    |   |

Description:

These floating point instructions return the smaller of the two operands X and Y (MIN/DMIN) or larger (MAX, DMAX).

The carry flag is reset if X is returned, otherwise it is set. X is returned if X = Y, except that MAX/DMAX (-0, +0) = +0 and MIN/DMIN (+0, -0) = -0.

The invalid Op flag is set if either operand is a signaling NaN. If either operand is not-a-number, then the result is not-a-number.

In IEEE wrapped underflow mode, a denormalized result is wrapped and the underflow flag is set. If either operand is a NaN, the carry flag is unspecified.

| ABSX          | 0 0 1 0 1 0 0 0 | X            |

|---------------|-----------------|--------------|

| DABSX         | 0 0 1 0 1 0 0 1 | DP: įXį      |

| NEGX<br>DNEGX | 00101010        | –x<br>DP: –X |

| PASSX         | 0 0 1 0 1 1 0 0 | X            |

| DPASSX        | 0 0 1 0 1 1 0 1 | DP: X        |

These single operand floating point instructions use the X operand input. PASSX/DPASSX returns X through the FALU. If X is denormalized and the wrapped underflow mode is reset, zero is returned, otherwise a wrapped result is returned.

PASSX/DPASSX with an infinite input sets CRY, otherwise CRY is reset. In IEEE wrapped underflow mode, the denormalized result is wrapped and the underflow flag is set. Description:

| DD    | 00110000        | X+Y        | 0   | N/A  | *  | •  | ٠ . | 1   | •   | T • | •  | Ī | $\Gamma$ |

|-------|-----------------|------------|-----|------|----|----|-----|-----|-----|-----|----|---|----------|

| ADD   | 00110001        | DP: X+Y    | CRY | DIVZ | DY | DX | NaN | RND | INX | INV | UF |   | OV       |

| UB    | 00110010        | X-Y        |     |      |    |    |     |     |     |     |    |   |          |

| UB    | 00110011        | DP: X-Y    |     |      |    |    |     |     |     |     |    |   |          |

| SUBX  | 00110100        | Y-X        |     |      |    |    |     |     |     |     |    |   |          |

| DSUBX | 00110101        | DP: Y-X    |     |      |    |    |     |     |     |     |    |   |          |

| ADDA  | 00111000        | X + Y      |     |      |    |    |     |     |     |     |    |   |          |

| DADDA | 00111001        | DP  X + Y  |     |      |    |    |     |     |     |     |    |   |          |

| SUBA  | 00111010        | įxį–įYį    |     |      |    |    |     |     |     |     |    |   |          |

| DSUBA | 0 0 1 1 1 0 1 1 | DP:  X - Y |     |      |    |    |     |     |     |     |    |   |          |

| SUBXA | 00111100        | IYI–IXI    |     |      |    |    |     |     |     |     |    |   |          |

| SUBXA | 0 0 1 1 1 1 0 1 | DP:  Y - X |     |      |    |    |     |     |     |     |    |   |          |

Description: Comments:

Floating point addition and subtraction. [|X|, |Y|] represents the absolute value of [X,Y].

When the sum of two operands with opposite signs (or the difference of two operands with like signs) is exactly zero, the result is +0 for all rounding modes except round to minus infinity, in which case, the result is -0. Note that (+0) + (+0) = (+0) - (-0) = +0 and (-0) + (-0) = (-0) - (+0) = -0 for all rounding modes.

In the tables on the next page, the first entry represents the flag that is set, the second represents the result returned to Z.

# B5110/B5120

# FLOATING POINT ARITHMETIC INSTRUCTIONS (contd) MNENONIC L OPCODE FLAGS AFFECTED FUNCTION

X OPERAND

IEEE-WRAPPED UNDERFLOW MODE

| Υ           |      |            | DEN                                | 5(8)37                             | li);               | •          | :          |

|-------------|------|------------|------------------------------------|------------------------------------|--------------------|------------|------------|

| 0           |      | ZR/0       | UF/WRP                             | NORM                               | INF                | NAN/Q      | INV, NaN/Q |

| P<br>E<br>R | DEN  | UF/WRP     | UF/WRP<br>NORM                     | OV/[WRP, INF, M]<br>NORM<br>UF/WRP | INF                | NAN/Q      | INV, NaN/Q |

| A<br>N<br>D | NORM | NORM       | OV/[WRP, INF, M]<br>NORM<br>UF/WRP | ÖV/[WRP, INF, M]<br>NORM<br>UF/WRP | INF                | NaN/Q      | INV, NaN/Q |

|             | INF  | INF        | INF                                | INF                                | INF1<br>INV, NaN/O | NaN/Q      | INV, NaN/Q |

|             |      | NaN/Q      | NaN/Q                              | NaN/Q                              | NaN/Q              | NaN/Q      | INV, NaN/Q |

|             |      | INV, NaN/Q | INV, NaN/Q                         | INV, NaN/Q                         | INV, NaN/Q         | INV, NaN/Q | INV, NaN/Q |

| X OPER | AND   | DEC MODE                 |       |

|--------|-------|--------------------------|-------|

| Y      | 0     | Sielel A                 | 8     |

| )      | ZR/0  | NORM                     | INV/R |

| NOR    | NORM  | OV/R<br>NORM<br>ZR, UF/0 | INV/R |

| )      | INV/R | INV/R                    | INV/R |

X OPERAND

### IEEE-WRAPPED UNDERFLOW MODE DISABLED

| Υ                |      | 6          | DEN        | ALC) GIA                                    | NF.                              | •          | 5          |

|------------------|------|------------|------------|---------------------------------------------|----------------------------------|------------|------------|

| 0                |      | ZR/0       | ZR/0       | NORM                                        | INF                              | NAN/Q      | INV, NaN/Q |

| Р                |      | ZR/0       | ZR/0       | NORM                                        | INF                              | NAN/Q      | INV, NaN/Q |

| E<br>R<br>A<br>N | NORM | NORM       | NORM       | OV/[WRP, INF, M]<br>NORM<br>UF, [ZR]/[0, E] | INF                              | NaN/Q      | INV, NaN/Q |

| D                | INF  | INF        | INF        | INF                                         | INF 1<br>INV, NaN/Q <sup>1</sup> | NaN/Q      | INV, NaN/Q |

|                  |      | NaN/Q      | NaN/Q      | NaN/Q                                       | NaN/Q                            | NaN/Q      | INV, NaN/Q |

|                  |      | INV, NaN/Q | INV, NaN/Q | INV, NaN/Q                                  | INV, NaN/Q                       | INV, NaN/Q | INV, NaN/Q |

| MNEMONK                   | FLOATING POINT SUPPORT INSTRUCTS OPCODE C. L. L. L. L. L. FUNCTION FLAG                                                                                                                                                                                                          | ONS<br>S AFFECTED    |            |            |           |          |          |           |            |         |        |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|------------|-----------|----------|----------|-----------|------------|---------|--------|

| PASSXM<br>DPASSXM         | 0 0 0 1 0 0 0 0 0 X                                                                                                                                                                                                                                                              | N/A 0 C              |            | ] 0<br>NaN | 0<br>RND  | 0<br>INX | O<br>INV | 0<br>UF   | OV         | ż<br>ZR | Ň      |

| Description:<br>Comments: | The X input is returned unmodified through the FMPY.  The zero and negative flags are set as if the result is a signed integer. The remaining flags                                                                                                                              | s are reset.         |            |            |           |          |          |           |            |         |        |

| CALE<br>SCALE             | 0 0 1 0 0 0 0 0 EXPONENT X + Y 0 0 1 0 0 0 0 1 DP: EXPONENT X + Y                                                                                                                                                                                                                | 0 N/A C              |            | T 0<br>NaN | 0 RND     | Ó        | ] 0      | I .       | OV         | 0<br>ZR | ·      |

| escription:<br>omments:   | The integer input Y is added to the exponent of X. The sign and mantissa of X are passed Overflows and underflows always return a wrapped result regardless of the overflow or und (double precision) of Y are interpreted as a two's complement integer. Other bits of Y are in | derflow mode. The    | least sign | nilicant B | bits (sin | gle pre  | cision)  | or 11 bi  | ts         |         |        |

| ERGE<br>MERGE             | 0 0 1 0 0 0 1 0 SIGN X EXPONENT Y MANTISSA X 0 0 1 0 0 0 1 1 DP: SIGN X EXPONENT Y MANTISSA X                                                                                                                                                                                    | 0 N/A C              |            | 0<br>NaN   | 0<br>RND  | 0<br>INX | 0<br>INV | UF        | ov         | 0<br>ZR | · N    |

| escription:<br>omments:   | The exponent field of $Y$ is concatenated with the sign and mantissa field of $X$ . If a NaN or INF results, the overflow flag is set. If a denormalized number or zero results, t                                                                                               | the underflow flag   | is set. Us | e PASS)    | K/DPAS    | SX to c  | heck re  | suit type | <b>)</b> . |         |        |

| IORMX                     | 0 0 1 0 1 1 1 0 NORMALIZE X                                                                                                                                                                                                                                                      | 0 N/A C              |            | ] 0<br>NaN | 0 RND     | 0<br>INX | O<br>INV | UF        | o<br>ov    | ·<br>ZR | 0<br>N |

| escription:               | X is assumed to be a 32-bit unsigned positive integer. The leading one of X will be left shift. The shift count will be placed in the SC register and output as the result.                                                                                                      | fted to the most sig | nificant b | t position | ٦.        |          |          |           |            |         |        |

|                           | ELOATINE POINT SUPPORT N | ISTRUCTIONS    |  |

|---------------------------|--------------------------|----------------|--|

| MNEMONIC I L. L. L. L. L. | 4 FUNCTION               | FLAGS AFFECTED |  |

CMPR 0 0 1 1 0 1 1 0 **DCMPR** 00110111 CMPRA 00111110 **DCMPRA** 00111111

0 0 0 N/A DIVZ RND

Description: Comments:

Floating Point compare |X|, |Y| represents the absolute value of X, Y. The following values will be returned to the result based on the relative magnitude of operands X and Y. Exactly one of CRY, N, ZR, or NaN will be set by compare. For example, If X = Y in round to minus infinity mode, -0 is returned, and the ZR flag is set, but the N flag is reset. If a compare is performed on a signaling NaN, the INV flag will be set.

When comparing  $\pm$  INF and  $\pm$ 0, the following states occur:

| Input     | 30 P | Corna                        |

|-----------|------|------------------------------|

| X > Y     | CRY  | 1                            |

| X < Y     | N    | -1                           |

| X = Y     | ZR   | 0 (-0 in round to -INF mode) |

| [X,Y] NaN | NaN  | NaN                          |

| ) Ing | ouil<br>Y | Flag | Dutput |

|-------|-----------|------|--------|

| ±0    | ±0        | ZR   | 0      |

| +INF  | +INF      | ZR   | 0      |

| +INF  | -INF      | CRY  | 1      |

| -INF  | +INF      | N    | -1     |

| -INF  | -INF      | ZR   | 0      |

**PASSn**

0 1 0 0 n n n n

X•16 + n

Description: Comments:

X is logically left shifted four places and the four least significant bits of the opcode field are added to it.

Allows microcode to build constants on the datapath. PASSn does not change the flags. In this repect, it acts like a NOP.

| SCREGR | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | SC register read         |

|--------|---|---|---|---|---|---|---|---|--------------------------|

| SCREGW | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | SC register write        |

| FREGAR | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | FALU flag register read  |

| FREGAW | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | FALU flag register write |

| FREGMR | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | FMPY flag register read  |

| FREGMW | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | FMPY flag register write |

| IREGAR | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | FALU int register read   |

| IREGAW | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | FALU int register write  |

| IREGMR | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | FMPY int register read   |

| IREGMW | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | FMPY int register write  |

| MREGAR | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | FALU mode register read  |

| MREGAW | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | FALU mode register write |

| MREGMR | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | FMPY mode register read  |

| MREGMW | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | FMPY mode register write |

Description:

Register access instructions. SCREGx accesses the SC register (FALU only), FREGx accesses the flag register, IREGx accesses the interrupt enable register and MREGx

accesses the mode register.

NOP

0 1 0 1 1 0 0 0

No operation

Description: Comments:

All registers and flags remain unchanged. The result is unspecified. Parity is checked during NOP's (and all unimplemented instructions).

**CLRFLAG**

0 1 0 1 1 0 0 1

Clear flag register

Description:

The flag register is cleared, the SC (FALU only), interrupt enable and mode registers are unaffected. If an interrupt has frozen the flag register (see freeze on interrupt mode), CLRFLAG will clear and unfreeze the register.

SDF

# B5110/B5120

|                                                                                                                                     |                                                             |                                                                                         |                                                                                                                                                                                                                                 | elektra:sile                                                                                                                                                                                                                                                                                                                                                                                                        | N RESTRUCTED                                                                | <b>303</b>                               |                                |                                 |                                   |                                      |                                             |          |           |           |               |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------|--------------------------------|---------------------------------|-----------------------------------|--------------------------------------|---------------------------------------------|----------|-----------|-----------|---------------|

|                                                                                                                                     | OP/                                                         | CODE                                                                                    |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                     | FLAGS AF                                                                    |                                          |                                |                                 |                                   |                                      |                                             |          |           |           |               |

| MNEMONE                                                                                                                             | 3 1, 1, 1,                                                  | , t, t, t,                                                                              | <sub>o</sub> FUN                                                                                                                                                                                                                | CTION                                                                                                                                                                                                                                                                                                                                                                                                               | . LAGO A                                                                    |                                          |                                |                                 |                                   |                                      |                                             |          |           |           |               |

| FCUI<br>DFCUI<br>FCSI<br>DFCSI<br>UICF<br>UICDF<br>SICF<br>SICDF<br>FCLUI<br>DFCLUI<br>FCLSI<br>DFCLSI<br>LUICF<br>LUICDF<br>LSICDF | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                     | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0                                                 | DP→32-b DP→32-b DP→32-b DP→32-b DP→32-b DP→32-b DP→32-b DP→64-b | it unsigned integar it unsigned integer it signed integer it signed integer it signed integer it unsigned integer it unsigned integer it signed integer it unsigned integer it unsigned integer it unsigned integer it unsigned integer it signed integer it unsigned integer it signed integer it signed integer it signed integer | O<br>CRY                                                                    | N/A J                                    | O I                            | · Xd                            | NaN                               | PND IN                               | NX INV                                      | UF       | OV        | ZR        | N             |

| FCUIT DFCUIT FCSIT DFSCIT FCLUIT FCLUIT FCLSIT DFCLSIT                                                                              | 0 1 1<br>0 1 1<br>0 1 1<br>0 1 1<br>0 1 1<br>0 1 1<br>0 1 1 | 1 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 1 0 0 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | O SP→32-b 1 DP→32-b O SP→32-b 1 DP→32-b O SP→64-b O SP→64-b O SP→64-b                                                                                                                                                           | it unsigned integer (Rnd it unsigned integer (Rnd it unsigned integer (Rnd to it signed integer (Rnd to it unsigned integer (Rnd to it unsigned integer (Rnd it unsigned integer (Rnd to it signed integer (Rnd to it signed integer (Rnd to it signed integer (Rnd to                                                                                                                                              | to 0) 0) 0) to 0) to 0) to 0)                                               |                                          |                                |                                 |                                   |                                      |                                             |          |           |           |               |

| Description:<br>Comments:                                                                                                           | rounding m<br>When a float                                  | ode (see mod<br>ting point to in                                                        | e register), except :                                                                                                                                                                                                           | g point conversion instruction<br>the xxxT format instructions valued in the inva-<br>struction overflows, the inva-<br>or example:                                                                                                                                                                                                                                                                                 | which always round to                                                       | ward zero.                               |                                |                                 |                                   |                                      |                                             |          | •         |           |               |

| 32 bit sign<br>64 bit sign<br>32 bit unsig<br>64 bit unsig                                                                          | ed result:<br>ed result:<br>ned result:                     | 7FFFFF<br>FFF                                                                           |                                                                                                                                                                                                                                 | 80000000<br>800000000000000<br>0000000<br>0000000                                                                                                                                                                                                                                                                                                                                                                   | result i                                                                    | N is conve<br>s an overfi<br>to floating | low with                       | the sign                        | n of the                          | NaN.                                 |                                             |          |           |           |               |

| WDNM<br>DWDNM                                                                                                                       |                                                             | 1 0 1 0 0                                                                               |                                                                                                                                                                                                                                 | PPED→DENORM<br>PPED→DENORM                                                                                                                                                                                                                                                                                                                                                                                          | 0<br>CRY                                                                    | N/A DIVZ                                 | 0 [                            | O I                             | 0  <br>NaN F                      | RND IN                               | IX INV                                      | UF       | oV        | *  <br>ZR | N N           |

| Description:<br>Comments:                                                                                                           | The underflo<br>The inexact<br>wrapped und                  | w flag is set it<br>and rounded-<br>terflow. The r                                      | the result is inexa-<br>up flags are used a<br>ounding mode mus                                                                                                                                                                 | nt the wrapped X input to a d<br>z. This corresponds to the li<br>s inputs to prevent a double<br>tt also be the same as when<br>up flags are latched externa                                                                                                                                                                                                                                                       | EEE specification which<br>rounding error. These<br>the wrapped underflored | th says that<br>flags must<br>was pro-   | at an un<br>st be se<br>duced. | derflow<br>t equal t<br>The rou | shall be<br>to the co<br>inded up | signaled<br>prrespond<br>oflag is us | if a result<br>ling flags on<br>Inspecified | is denor | ration th | at produc | ct.<br>ed the |

| SDF          | 0 1 1 1 0 1 1 0                  | SP→DP                                       | 0 N/A CRY DIVZ    | DY DX | NaN F | 0 0<br>RND INX | INV I | 0   0<br>UF OV | ZR       | N |

|--------------|----------------------------------|---------------------------------------------|-------------------|-------|-------|----------------|-------|----------------|----------|---|

| Description: | Floating point precision convers | sion instruction. Conversion is carried out | on the X operand. |       |       |                |       |                |          |   |

| DSDF         | 0 1 1 1 0 1 1 1                  | DP→SP                                       | N/A CRY DIVZ      | DY D) | NaN I | RND INX        | I · I | UF OV          | ZR<br>ZR | · |

Floating point precision conversion instruction. Conversion is carried out on the X operand.

The carry flag is set if a normalized double precision number is output as a single precision infinity. This will occur it overflows are not wrapped, or if the result is too large to be represented by a wrapped overflow. If a result underflows to the extent that it cannot be wrapped, zero is returned and the zero, underflow and inexact flags are set. Refer to ANSVIEEE STD. 754, section 7.3 (overflows) for additional information. Description: Comments:

| MNEMON                       | o pecape                                        | CONVERSION INSTRU                                                                                                                                        |            | 9 (00)<br>19 APP |         | b                     |                    |                       |                  |            |          |         |      |     |   |

|------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|---------|-----------------------|--------------------|-----------------------|------------------|------------|----------|---------|------|-----|---|

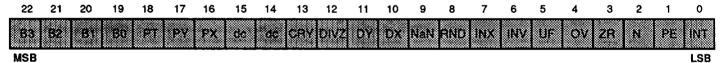

| FFI<br>DFFI<br>FFIT<br>DFFIT | 0 1 1 1 1 1 0 0<br>0 1 1 1 1 1 0 1<br>0 1 1 1 1 | SP→DP format integer<br>DP→SP format integer<br>SP→SP format integer (Round to 0)<br>DP→DP format integer (Round to 0)                                   | O<br>CRY   | N/A<br>DIVZ      | DY      | DX<br>L .             | NaN                | RND                   | INX              | INV<br>I . | UF       | OV      | ZR   | I , | I |

| Description:<br>Comments:    | FFIT/DFFIT always rounds tow                    | ction. The floating point number at the X operan<br>ard zero, regardless of the rounding mode. The<br>magnitude of the result is greater than the magnit | INX flag v | vill be so       | to an i | integral<br>result is | valued<br>differen | floating<br>nt from t | point nuthe inpu | umber in   | n the sa | me form | nat. |     |   |

Description: The larger of the two operands X and Y is returned (ISMAX/LISMAX, IUMAX/LIUMAX) or the smaller of the two operands is returned (ISMIN/LISMIN, IUMIN/LIUMIN).

Comments: Sign and zero flags are set based on returned result. The carry flag is reset if X is returned, otherwise it is set. X is returned if X = Y.

# B5110/B5120

|                                                                |                                                                                                                                                                    | NITE SERVED SERVE                                                                                                                                                                                     | ETIC MISTRUCTIONS (control)                      |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| MNEMONI                                                        | C LILY STATE                                                                                                                                                       | FUNCTION                                                                                                                                                                                              | FLAGS AFFECTED                                   |

| IMULT IMULTSX IMULTSY IMULTS IMULTH IMULTHSX IMULTHSY IMULTHSY | 1 1 1 1 1 0 0 0<br>1 1 1 1 1 1 0 0 1<br>1 1 1 1 1 1 0 0 1<br>1 1 1 1 1 1 0 1 0<br>1 1 1 1 1 1 0 0<br>1 1 1 1 1 1 1 0 0<br>1 1 1 1 1 1 1 1 1 0<br>1 1 1 1 1 1 1 1 1 | Unsigned X • Unsigned Y Signed X • Unsigned Y Unsigned X • Signed Y Signed X • Signed Y Unsigned X • Unsigned Y Signed X • Unsigned Y Signed X • Unsigned Y Unsigned X • Signed Y Signed X • Signed Y | IMULT  N/A 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

Description: Integer multiplication instructions. IMULT returns a 64 bit result, whereas IMULTH returns the least significant 32 bits.

|         |   |    |   |   |   |   |   |   |    | 1844:GE;836(6)8C     | ar (Distrible |                   |         |    |     |     |     |     |    |    |    |   |

|---------|---|----|---|---|---|---|---|---|----|----------------------|---------------|-------------------|---------|----|-----|-----|-----|-----|----|----|----|---|

| MNEMONI |   | ı, |   |   |   |   |   |   |    | FUNCTION             | FLAC          | ) <b>8.</b> 7 (1) | (e) (e) |    |     |     |     |     |    |    |    |   |

| INAND   | 1 | 1  | 0 | 1 | 0 | 0 | 0 | 0 |    | <b>X</b> or <b>Y</b> | 0             | N/A               | 0       | 0  | 0   | 0   | 0   | 0   | 0  | 0  | •  | ٠ |

| LINAND  | 1 | 0  | 0 | 1 | 0 | 0 | 0 | 0 | L: | X or Y               | CRY           | DIVZ              | DY      | DX | NaN | RND | INX | INV | UF | OV | ŽR | N |

| IORNX   | 1 | 1  | 0 | 1 | 0 | 0 | 0 | 1 |    | <b>X</b> or <b>Y</b> |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIORNX  | 1 | 0  | 0 | 1 | 0 | 0 | 0 | 1 | L: | <b>又</b> or Y        |               |                   |         |    |     |     |     |     |    |    |    |   |

| IORNY   | 1 | 1  | 0 | 1 | 0 | 0 | 1 | 0 |    | X or ₹               |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIORNY  | 1 | 0  | 0 | 1 | 0 | 0 | 1 | 0 | L: | X or $\overline{Y}$  |               |                   |         |    |     |     |     |     |    |    |    |   |

| IOR     | 1 | 1  | 0 | 1 | 0 | 0 | 1 | 1 |    | X or Y               |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIOR    | 1 | 0  | 0 | 1 | 0 | 0 | 1 | 1 | L: | X or Y               |               |                   |         |    |     |     |     |     |    |    |    |   |

| IANDNY  | 1 | 1  | 0 | 1 | 0 | 1 | 0 | 0 |    | X and Y              |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIANDNY | 1 | 0  | 0 | 1 | 0 | 1 | 0 | 0 | L: | X and ♥              |               |                   |         |    |     |     |     |     |    |    |    |   |

| IAND    | 1 | 1  | 0 | 1 | 0 | 1 | 0 | 1 |    | X and Y              |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIAND   | 1 | 0  | 0 | 1 | 0 | 1 | 0 | 1 | L: | X and Y              |               |                   |         |    |     |     |     |     |    |    |    |   |

| INOR    | 1 | 1  | 0 | 1 | 0 | 1 | 1 | 0 |    | X and Y              |               |                   |         |    |     |     |     |     |    |    |    |   |

| LINOR   |   | 0  | 0 | 1 | 0 | 1 | 1 | 0 | L: | X and Y              |               |                   |         |    |     |     |     |     |    |    |    |   |

| IANDNX  | 1 | 1  | 0 | 1 | 0 | 1 | 1 | 1 |    | X and Y              |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIANDNX | 1 | 0  | 0 | 1 | 0 | 1 | 1 | 1 | L: | X and Y              |               |                   |         |    |     |     |     |     |    |    |    |   |

| IXNOR   | 1 | 1  | 0 | 1 | 1 | 1 | 1 | 0 |    | X XNOR Y             |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIXNOR  | 1 | 0  | 0 | 1 | 1 |   | 1 | 0 | L: | X XNOR Y             |               |                   |         |    |     |     |     |     |    |    |    |   |

| IXOR    | 1 | 1  | 0 | 1 | 1 | 1 | 1 | 1 |    | X XOR Y              |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIXOR   | 1 | 0  | 0 | 1 | 1 | 1 | 1 | 1 | L: | X XOR Y              |               |                   |         |    |     |     |     |     |    |    |    |   |

| ISET    | 1 | 1  | 0 | 1 | 1 | 0 | 0 | 0 |    | Z = all ones         |               |                   |         |    |     |     |     |     |    |    |    |   |

| LISET   | 1 | 0  | 0 | 1 |   | 0 | 0 | 0 | L: | Z = all ones         |               |                   |         |    |     |     |     |     |    |    |    |   |

| INOTX   | 1 | 1  |   | 1 | 1 | 0 | 0 | 1 |    | Z = X                |               |                   |         |    |     |     |     |     |    |    |    |   |

| LINOTX  |   | 0  | Ō | 1 | 1 | Ō | Ō | 1 | L: | Z = X                |               |                   |         |    |     |     |     |     |    |    |    |   |

| IPASSY  | 1 | 1  | 0 | 1 | 1 | 0 | 1 | 0 |    | Z = Y                |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIPASSY | 1 | Ó  |   |   |   |   | 1 |   | L: | Z = Y                |               |                   |         |    |     |     |     |     |    |    |    |   |

| IPASSX  |   | 1  |   |   |   |   | 1 |   |    | Z = X                |               |                   |         |    |     |     |     |     |    |    |    |   |

| LIPASSX | - | 0  | _ | 1 |   | _ | 1 |   | L: | Z=X                  |               |                   |         |    |     |     |     |     |    |    |    |   |

| ICLR    |   | 1  | ō | 1 |   |   | ò |   |    | Z = all zeros        |               |                   |         |    |     |     |     |     |    |    |    |   |

| LICLR   |   | ò  | _ |   | - |   | ō | _ | L: | Z = all zeros        |               |                   |         |    |     |     |     |     |    |    |    |   |

| INOTY   |   | _  | _ |   |   |   | Ŏ |   |    | Z = Ÿ                |               |                   |         |    |     |     |     |     |    |    |    |   |

| LINOTY  |   | ò  |   |   |   |   |   |   |    | Z≖Ÿ                  |               |                   |         |    |     |     |     |     |    |    |    |   |

Description: Comments:

Boolean logic instructions. Flags are set based on signed operands.

| MHEMONI                   | PLASS APPECTED  FUNCTION  PLASS APPECTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSS<br>LLSS<br>LS<br>LLS  | 1 1 1 1 0 0 0 0 Logical shift X w/sb 1 0 1 1 0 0 0 0 L: Logical shift X w/sb 1 1 1 1 0 0 0 0 1 Logical shift X w/sb 1 0 1 1 0 0 0 1 Logical shift X 1 0 1 1 0 0 0 1 L: Logical shift X                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Description:              | Integer shift instructions. The two's complement number in the SC register determines the shift. If SC > 0, then shift left by SC; if SC < 0, then shift right by -SC. If SC = 0, then no shift is performed. For LSS/LLSS right shifts, all bits of the result shifted out are ored with the least significant bit position of the result (i.e., sticky bit).                                                                                                                                                                                                                                                               |

| Comments:                 | Zeroes are shifted in during right and left shifts.  Carry bit receives the last bit shifted out of the operand if SC ≠ 0. Flags are set based on a signed operand. The overflow flag is reset. Carry is reset if SC = 0.                                                                                                                                                                                                                                                                                                                                                                                                    |

| AS<br>LAS                 | 1 1 1 1 0 0 1 0 Arithmetic shift X 1 0 1 1 0 0 1 0 L: Arithmetic shift X CRY DIVZ DY DX NaN RND INX INV UF OV ZR N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Description: Comments:    | Arithmetic shift instruction. The two's complement number in the SC register determines the shift. If SC > 0, then shift left by SC; if SC < 0, then shift left by SC; if SC < 0, then shift left by SC; if SC < 0, then shift left by SC; if SC < 0, then shift shifts, zeroes are shifted in. For right shifts, AS/LAS shifts in copies of the sign bit. Carry bit receives the last bit shifted out of the operand if SC ≠ 0. Carry is reset if SC = 0. Flags are set based on a signed operand. Left AS/LAS shifts set the OV flag if any bits shifted out differ from the result sign.                                  |

| ROTX<br>LROTX             | 1 1 1 1 0 0 1 1 Rotate X 1 0 1 1 0 0 1 1 L: Rotate X CRY DIVZ DY DX NaN RND INX INV UF OV ZR N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Description:<br>Comments: | Rotate X by the signed two's complement number in the shift count (SC) register. If SC > 0, rotate left by SC. If SC = 0, no shift is performed. As bits are shifted out, they are used as shift inputs. Carry gets the last bit wrapped from one end of the word to the other. Carry is reset if SC = 0.                                                                                                                                                                                                                                                                                                                    |

| ROTC<br>LROTC             | 1 1 1 1 0 1 0 0 Rotate Y X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Description: Comments:    | The 32 bit integers Y and X are concatenated and rotated by the signed two's complement number in the shift count register. Before the rotate operation, Y is in the most significant word position. If SC > 0, rotate left by SC. If SC < 0, rotate right by -SC. If SC = 0, no shift is performed. As bits are shifted out, they are used as shift inputs. LROTC returns all 64 bits of the the result. ROTC returns the least significant 32 bits of the result. Carry gets the last bit wrapped from one end of the word to the other. Carry is reset if SC = 0.                                                         |