# **UM8312**

# Double Row-Buffer(DRB)

#### Features

- Low-cost solution to CRT memory contention problem

- Provides enhanced processor throughput for CRT display systems

- Replaces shift registers or several RAM and counter ICs in CRT display system

- Permits display of one data row while next data row is being loaded

- Data may be written into buffer at less than the video painting rate

- Double data row buffer permits second data row to be loaded anytime during the display of the preceding data row

- Permits active video on all scan lines of data row

- Dynamically variable number of characters per data Row-... 64, 80, 132,.... up to a maximum of 135

- Cascadable for data rows greater than 135 characters

- Stackable for "Invisible Attributes" or character widths of greater than 8 Bits

- Three-state outputs

- Up to 4 MHz read/write data rate

- Compatible with UM9007 and other CRT controllers

- 28 pin dual-in-line package

- +5 volt only power supply

- TTL-compatible

# **General Description**

The UM8312 Double Row Buffer (RDB) provides a lowcost solution to memory contention between the system processor and the CRT controller in video display systems.

The UM8312 DRB is a RAM-based buffer which provides two rows of buffering. It appears to the system as two octal shift registers of dynamically variable length (2-135 bytes) plus steering logic.

The UM8312 permits the loading of one data row while the previous data row is being displayed. The loading of data may take place during any of the scan line times of the data row. This relaxed time-constraint allows the processor to perform additional processing on the data or service other high-priority interrupt conditions (such as a Floopy Disk DMA request) which may occur during a single video scan line. The result is enhanced processor throughput and flicker-free display of data.

## Absolute Maximum Ratings\*

| Operating Temperature Range 0°C to + 70°C           |

|-----------------------------------------------------|

| Storage Temperature Range55°C to + 150°C            |

| Lead Temperature (soldering, 10 sec.) +325°C        |

| Positive Voltage on any Pin, with respect to ground |

|                                                     |

| Negative Voltage on any Pin, with respect to ground |

|                                                     |

#### \*Comments

Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied.

Electrical Characteristics  $(T_A = 0^{\circ}C \text{ to } 70^{\circ}C, V_{CC} = +5V \pm 5\%)$

#### D.C. CHARACTERISTICS

| Parameter                                                                                                                                               | Min.       | Тур.     | Max.                   | Units                | Conditions                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|------------------------|----------------------|-------------------------------------|

| INPUT VOLTAGE LEVELS<br>Low Level V <sub>IL</sub><br>High Level V <sub>IH1</sub><br>High Level V <sub>IH2</sub>                                         | 2.0<br>4.2 |          | 0.8                    | > >                  | excluding RCLK; WCLK<br>RCLK, WCLK  |

| OUTPUT VOLTAGE LEVELS<br>Low Level V <sub>OL</sub><br>High Level V <sub>OH</sub>                                                                        | 2.4        |          | 0.4                    | >>                   |                                     |

| INPUT LEAKAGE CURRENT<br>High Leakage I <sub>LH1</sub><br>Low Leakage I <sub>LL1</sub><br>High Leakage I <sub>LH2</sub><br>Low Leakage I <sub>LL2</sub> |            | 1        | 10<br>10<br>400<br>400 | μΑ<br>μΑ<br>μΑ<br>μΑ | excluding OE excluding WEN1 WEN1 OE |

| INPUT CAPACITANCE  C <sub>IN1</sub> C <sub>IN2</sub>                                                                                                    |            | 10<br>15 |                        | pF<br>pF             | excluding RCLK, WCLK RCLK, WCLK     |

| POWER SUPPLY CURRENT                                                                                                                                    |            | 100      | 140                    | mA                   |                                     |

# A.C. CHARACTERISTICS

| Parameter          | Min. | Тур.              | Max. | Units | Conditions                                       |

|--------------------|------|-------------------|------|-------|--------------------------------------------------|

| t <sub>CYW</sub>   | 300  |                   |      | ns    | Write clock period                               |

| t <sub>CYR</sub>   | 300  |                   |      | ns    | Read clock period                                |

| <sup>t</sup> CKH   | 247  |                   | DC   | ns    |                                                  |

| <sup>†</sup> CKL   | 33   |                   |      | ns    |                                                  |

| t <sub>CKR</sub>   |      |                   | 10   | ns    | measured from 10% to 90% points                  |

| <sup>†</sup> CKF   |      |                   | 10   | ns    | measured from 90% to 10% points                  |

| t <sub>DS</sub>    | 50   |                   |      | ns    | referenced to WCLK                               |

| <sup>t</sup> DH    | 0    |                   |      | ns    | referenced to WCLK                               |

| tEN12              | 0    |                   |      | ns    |                                                  |

| t <sub>EN2</sub> 2 | 100  |                   |      | ns    |                                                  |

| tenh <sup>2</sup>  | . 0  |                   |      | ns    |                                                  |

| t <sub>DV</sub>    |      |                   | 175  | ns    | $C_L = 50pF$ ; referenced from $\overline{RCLK}$ |

| <sup>t</sup> DOFF  |      |                   | 175  | ns    |                                                  |

| t <sub>DON</sub>   |      |                   | 175  | ns    |                                                  |

| tOF <sup>3</sup>   |      |                   | 175  | ns    | C <sub>L</sub> = 30pF                            |

| tcs                | 100  |                   |      | ns    |                                                  |

| t <sub>CH</sub>    | 0    |                   |      | ns    |                                                  |

| t <sub>WT</sub> 4  | 1    | 1t <sub>CYW</sub> |      |       |                                                  |

- 1 Reference points for all AC paramete s are 2.4V high and 0.4V low.

- 2 For REN, referenced from RCLK; for WEN1 or WEN2 referenced to WCLK.

- 3 For ROF, referenced from RCLK; for WOF referenced from WCLK.

- 4 At least 1 WCLK rising edge must occur etween CLRCNT or TOG (whichever occurs last) and WEN (= WEN1-WEN2).

74°C

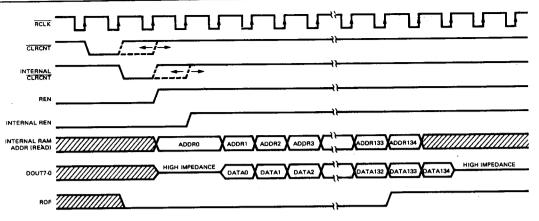

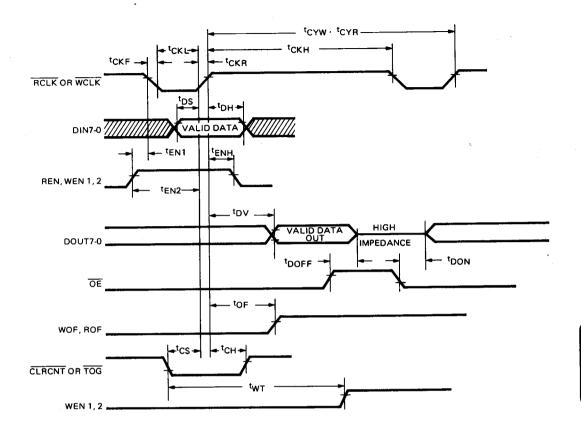

Figure 1. UM8312 Double Row Buffer Read Timing

# Pin Description

| Pin No.          | Name           | Symbol          | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3-0. 28<br>16-13 | Data inputs    | DINO-DIN7       | DIN DIN7 are the data inputs from the system memory.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 12-9, 7-4        | Data outputs   | DOUTO-<br>DOUT7 | DOUTO-DOUT7 are the data outputs from the UM8312 internal data outpulatch. Valid information will appear on DOUTO-DOUT7 two RCLK period after the rising edge of REN. This introduces two pipeline delays whe supplying data                                                                                                                                                                                                                              |  |  |

| 17               | Read Clock     | RCLK            | RCLK increments the current "read" address register, clocks data throug<br>the "read" buffer and moves data through the internal pipeline at the trail<br>ing edge. See Figure 1.                                                                                                                                                                                                                                                                         |  |  |

| 18               | Toggle Signal  | TOG             | TOG alternates the function of each buffer between read and write. TOG normally occurs at every data row boundary. Switching of the buffers occurs when both TOG and CLRCNT are low. See Figure 2.                                                                                                                                                                                                                                                        |  |  |

| 19               | Clear Counter  | CLRCNT          | Clear Counter clears the current "read" address counter at the next RCL positive edge. CLRCNT is normally asserted low at the beginning of each horizontal retrace interval. CLRCNT clears the current "write" addre counter when the TOG is active.                                                                                                                                                                                                      |  |  |

| 20               | Read Enable    | REN             | REN enables the loading of data from the selected "read" buffer into the output latch. Data is loaded when Read Clock is active.                                                                                                                                                                                                                                                                                                                          |  |  |

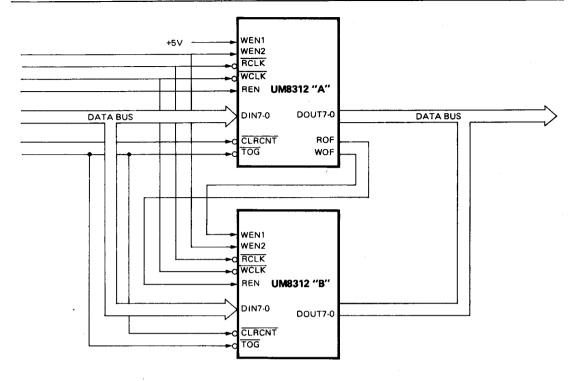

| 21               | Write Overflow | WOF             | WOF high indicates that data is being written into the last memory positic (position 135). When WOF is high, further writing into the selected "write buffer is disabled. WOF may be connected to the WEN1 or WEN2 inputs a second UM8312 for cascaded operation where data row lengths of great than 135 characters are desired. See Figure 3.                                                                                                           |  |  |

| 22               | Read Overflow  | ROF             | The Read Overflow output is high when data is being read from the last memory position (position 135). ROF high disables further reading from the selected "read" buffer. ROF may be connected to the REN input of a second UM8312 for cascaded operation where data row lengths of greater than 135 characters are desired. DOUTO-7 will switch into a high impedance state at the second positive transition of RCLK after ROF goes high. See Figure 3. |  |  |

| 24, 25           | Write Enable   | WEN1<br>WEN2    | WEN allows input data to be written into the selected "write" buffer du WCLK active. Both WEN1 and WEN2 must be high to enable writing. Whas an internal pull-up resistor allowing it to assume a high if pin 24 is open.                                                                                                                                                                                                                                 |  |  |

| 26               | Output Enable  | ŌĒ              | When the $\overline{OE}$ input is low the data outputs DOUTO-7 are enabled. When $\overline{OE}$ is high, DOUTO-7 present a high impedance state. $\overline{OE}$ has an internal pull-down resistor allowing it to assume a low if pin 26 is left open.                                                                                                                                                                                                  |  |  |

| 27               | Write Clock    | WCLK            | WCLK clocks input data into the selected "write" buffer and increments the current "write" address register when WEN1 and WEN2 are high.                                                                                                                                                                                                                                                                                                                  |  |  |

| 8                | Power Supply   | Vcc             | +5 Volt supply                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 23               | Ground         | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

### **Operational Description**

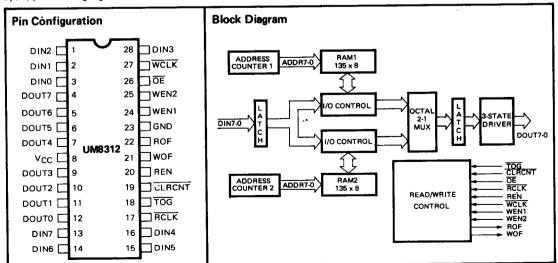

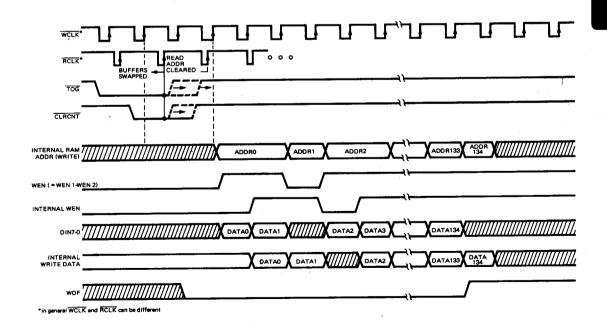

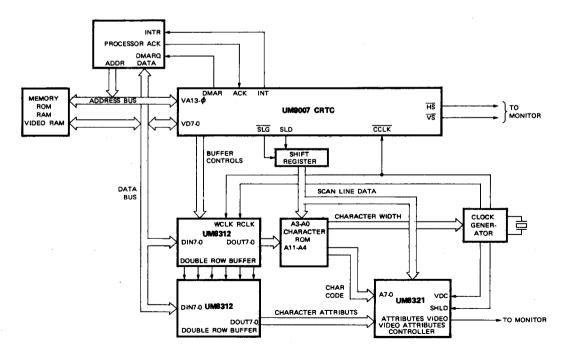

Block diagram illustrates the internal architecture of the UM8312. It contains 135 bytes of RAM in each of its two buffers. In normal operation, data is written into the input latch on the positive-going edge of Write Clock (WCLK). When both Write Enable (WEN1, WEN2) signals go high, the next WCLK causes data from the input latch to be written into the selected buffer (1 or 2) and the associated address counter to be incremented by one. Loading of the selected RAM buffer continues until WEN goes inactive or until the buffer has been fully loaded. At the next data row boundary, the Toggle Signal (TOG) will go low. When Clear Counter (CLRCNT) goes low, the next Read Clock (RCLK) will begin to reset both buffer address counters to zero, switching the buffer just loaded from a "write buffer" to a "read buffer", permitting the next row of data to be written into the other buffer. Data from the current "read" buffer is read out of the buffer and to the output latch whenever Read Enable (REN) is high during a Read Clock (RECLK). Each read-out from the buffer RAM causes the "read" address counter to be

incremented. REN is normally high during the entire visible line time of each scan line of the data row. CLRCNT resets the present "read" address counter. The negative edge of CLRCNT is detected by the UM8312 and the internal "read" address counter is cleared independently of the CLRCNT pulse width. The CLRCNT input may be tied to the REN input for proper operation.

Figures 1 and 2 illustrate the functional timing for reading and writing in the UM8312. It is possible to cascade two or more UM8312s to allow for data storage greater than 135 bytes by employing the read overflow (ROF) and write overflow (WOF) outputs. Figure 3 illustrates two UM8312's cascaded together.

The UM8312 is compatible with the UM9007 video processor and controller (VPAC<sup>TM</sup>) and the UM9021 video attributes controller (VAC). A typical video configuration employing the three parts is illustrated in Figure 4.

Figure 2. UM8312 Double-Row Buffer Write Timing

Figure 3. UM8312 Cascaded Configuration for Data Row Lengths up to 270 Characters

Figure 4. UM8312 Configured with the UM9007 CRTC and the UM8321 CRT VAC

Figure 5. UM8312 I/O Timing