# **Token Ring Physical Interface**

### **GENERAL DESCRIPTION**

The ML6682 Token Ring Physical Interface Circuit is designed for use as a token ring concentrator port interface in 4Mb/s and 16Mb/s IEEE 802.5 networks using category 4 and 5 unshielded twisted pair (UTP) and type 1 shielded twisted pair (STP) cable. It can also be configured as a Ring-In or Ring-Out port for concentrator interface to the main network trunk. It includes a receiver equalizer for suppression of inter-symbol distortion, a narrow-bandwidth master PLL with a constant-gain phase/frequency detector for enhanced clock tracking and low VCO phase distortion, an 8 UI FIFO and slave PLL for additional jitter attenuation, internal frequency/phase tracking select logic, and a waveshaping twisted pair transmit driver which requires only a very simple external filter to meet the 802.5 standard. The circuit also includes phantom wire fault detection and output drivers for use with an external phantom switching mechanism in a concentrator-to-trunk interface application. The part has an on-chip single-pin crystal oscillator designed for a 16MHz crystal. It can also be used with an external clock of either 16MHz or 32MHz frequency. The part uses a frequency squelch circuit at the twisted pair receiver to allow detection of incorrect network speed.

### **FEATURES**

- Supports the complete interface for a concentrator.

- Supports dual PLL jitter attenuator and clock regeneration for each lobe port and Ring In/Ring Out ports for UTP/STP extended distance concentrators.

- Compatible with IEEE 802.5-1989 Standard for Token Ring

- Pin selectable 16 and 4Mb/s data rates

- Supports dual ring fault tolerant Ring In/ Ring Out trunks

- Fault isolation capability at each concentrator port available for network management.

- Provides Dual Phase-Locked Loop with single edge constant gain phase detector and 8 UI FIFO for clock regeneration, jitter attenuation and data recovery.

- Phantom voltage drive/sense for both transmit and receive cable pairs.

- On-chip crystal oscillator can also be driven by external clock.

- On-chip receiver channel equalization switchable for both 4 and 16 Mbps

- Advanced BiCMOS technology

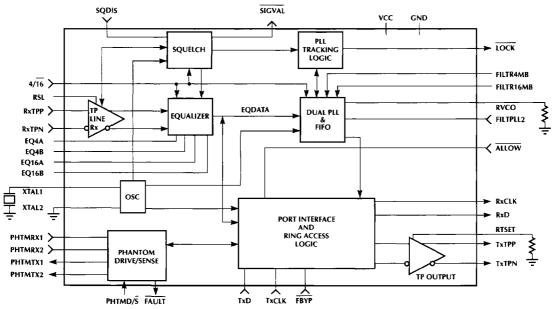

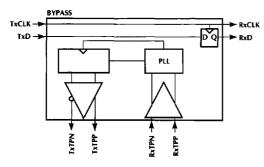

# **BLOCK DIAGRAM** SQDIS

### **GENERAL DESCRIPTION** (Continued)

External components are minimized by the use of internally-controlled station fault, receiver pulse width squelch, on-chip crystal oscillator, and internal 4/16 Mbps switching logic. The ML6682 performs the hybrid switching functions, eliminating the need for relays. Isolation can be achieved optically. The circuit requires a single +5V power supply, and is fabricated in BiCMOS technology.

### PIN CONFIGURATION

# **PIN DESCRIPTION**

| PIN#          | NAME                    | FUNCTION                                                                                                                                                                                                                                                                                                                | PIN# | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>44       | RxTPP<br>RxTPN          | Receive wire pair inputs. These inputs receive data from the twisted pair media through the receive isolation transformer. These pins are DC biased                                                                                                                                                                     | 13   | ALLOW              | ALLOW is a digital input that allows the port to control INSERT/BYPASS through phantom current, or allows the port to be forced into INSERT mode using FBYP.                                                                                                                                                                                                                                                      |

|               | D.G. ID.                | internally for proper receive data biasing.                                                                                                                                                                                                                                                                             | 14   | FBYP               | Force Bypass input. This digital input provides network management control to                                                                                                                                                                                                                                                                                                                                     |

| 2<br>20       | DGND2<br>DGND1          | Digital ground pins.                                                                                                                                                                                                                                                                                                    | 15   | N/C                | force the ML6682 into BYPASS mode.                                                                                                                                                                                                                                                                                                                                                                                |

| 3<br>21       | DVCC2<br>DVCC1          | Positive power supply pins (+5V) for digital part of the chip.                                                                                                                                                                                                                                                          | 16   | SIGVAL             | Valid signal indicator output. This output goes low when the signal at                                                                                                                                                                                                                                                                                                                                            |

| 4<br>35       | AVCC3<br>AVCC1          | Positive power supply pins (+5V) for analog part of the chip.                                                                                                                                                                                                                                                           |      |                    | RxTPP/N meets frequency and amplitude squelch requirements.                                                                                                                                                                                                                                                                                                                                                       |

| 5             | FILTR4MB                | 4Mbps PLL filter input. Connection point for external PLL filter components for 4 Mbps data rate.                                                                                                                                                                                                                       | 17   | XTAL1              | Crystal/external clock input. Connecting a 16MHz crystal between this pin and ground provides the required reference                                                                                                                                                                                                                                                                                              |

| 6             | FILTPLL2                | Second PLL filter input. Connection point for external PLL filter components for second (slave) PLL.                                                                                                                                                                                                                    |      |                    | frequency. This pin may also be driven by<br>an external 16MHz clock. XTAL2 must<br>be connected to ground when XTAL1 is<br>used.                                                                                                                                                                                                                                                                                 |

| 7             | FILTR16MB               | 16 Mbps PLL filter input. Connection point for external PLL filter components for 16 Mbps data rate.                                                                                                                                                                                                                    | 18   | XTAL2              | Clock input pin. Connecting a 32MHz external clock between this pin and                                                                                                                                                                                                                                                                                                                                           |

| 8<br>29<br>32 | AGND3<br>AGND2<br>AGND1 | Analog ground pins.                                                                                                                                                                                                                                                                                                     |      |                    | ground provides the required reference<br>frequency. When XTAL2 is used, XTAL1<br>must be grounded.                                                                                                                                                                                                                                                                                                               |

| 9             | N/C                     |                                                                                                                                                                                                                                                                                                                         | 19   | N/C                |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10            | LOCK                    | PLL phase lock indicator output. This output goes low when both PLLs achieve lock. May be externally gated with FBYP for zero delay lockout. (Prevent a 4 Mbps station from entering a 16 Mbps Ring).                                                                                                                   | 22   | RxD                | Receive data output. When the ML6682 is in INSERT mode, RxD is sourced by the PLL reclocked data from receive twisted pair inputs RxTPP, RxTPN. When the ML6682 is in the BYPASS mode, RxD is sourced by the TxD input.                                                                                                                                                                                           |

| 11            | 4/16                    | Data rate selection input. A logic one selects 4 Mbps operation. A logic zero selects 16 Mbps operation. The pin automatically switches the receive equalizer and the PLL loop filter for the                                                                                                                           | 23   | RxCLK              | Synchronized data clock output. When<br>the ML6682 is in INSERT mode, RxCLK<br>is sourced by the PLL. When the<br>ML6682 is in BYPASS mode, RxCLK is<br>sourced by the TxCLK input.                                                                                                                                                                                                                               |

| 12            | PHTMD/S                 | "Phantom drive/sense" select input.  When set low, the chip is configured for "phantom sense". In the "phantom sense" state PHTMRX1 pin serves as an input coming from an opto-isolator to sense phantom current and PHTMTX1 is an output. When PHTMD/\$\overline{S}\$ is set high, the chip is configured for "phantom | 24   | FAULT              | Phantom wire fault detection output. When this output is low, the phantom current test has failed. In the "phantom drive" mode this will be detected as an open or a short by the PHTMTX1, PHTMTX2, PHTMRX1, PHTMRX2 pins. In the "phantom sense" mode, FAULT is an output that simply buffers the PHTMRX1 input.                                                                                                 |

|               |                         | drive". In the "phantom drive" state PHTMTX1 and PHTMTX2 provide the phantom drive and fault detect for the transmit pair of wires, and PHTMRX1 and PHTMRX2 sense fault detect for the receive pair of wires.                                                                                                           |      | PHTMRX2<br>PHTMRX1 | Receive pair phantom sense inputs. In the "phantom drive" mode (PHTMD/ $\overline{S}$ pin is tied to $V_{CC}$ ) these inputs sense phantom current on the receive pair wires to detect a phantom circuit fault condition. In "phantom sense" configuration (PHTMD/ $\overline{S}$ pin is tied to GND) PHTMRX1 is the sense input for phantom current coming from an opto isolator and PHTMRX2 should be grounded. |

# PIN DESCRIPTION (Continued)

| PIN# | NAME               | FUNCTION                                                                                                                                                                                                                                       | PIN#     | NAME           | FUNCTION                                                                                                                                                                                            |

|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | PHTMTX1<br>PHTMTX2 | Transmit pair phantom drive/sense pair. In the "phantom drive" mode, these pins output a +5 volt phantom signal and sense opens and shorts as a                                                                                                | 36       | RVCO           | External resistor input. A precision resistor of the appropriate value connected to this input sets the phase detector gain.                                                                        |

|      |                    | phantom circuit fault condition. In the "phantom sense" mode, PHTMTX1 is an open collector pin that can be used to drive an LED to reflect the INSERT/                                                                                         | 37       | RTSET          | External resistor input. A precision resistor of the appropriate value connected to this input sets the twisted pair transmitter output level.                                                      |

|      |                    | BYPASS state. In the INSERT state,<br>PHTMTX1 is low to light the LED and<br>in the BYPASS state PHTMTX1 is high.<br>PHTMTX2 should be left floating in<br>the "phantom sense" mode.                                                           | 38       | RSL            | Receive squelch low select input. When this pin is tied to V <sub>CC</sub> the receive squelch level will be lower; more sensitive. When this pin is tied to GND, the receive squelch level will be |

| 30   | TxTPN              | Transmitter wire pair outputs. These pins are the differential current driver                                                                                                                                                                  |          |                | higher; less sensitive.                                                                                                                                                                             |

| 31   | TxTPP              | outputs to the lobe fed through an isolation transformer out on to the ring.                                                                                                                                                                   | 39       | SQDIS          | Squelch disable input. Normally wired to ground. A high level input disables the RX wire pair squelch function.                                                                                     |

| 33   | TxD                | Data input from the previous lobe or Ring In/Ring Out port. In INSERT mode TxD is clocked by TxCLK out onto the transmit twisted pair cable TxTPP, TxTPN. In BYPASS mode the TxD                                                               | 40<br>41 | EQ16B<br>EQ16A | Differential connection for external equalization components for 16 Mbps operation. The equalizer is disabled when these two pins are tied together.                                                |

|      |                    | input is internally connected to the RxD output.                                                                                                                                                                                               | 42<br>43 | EQ4B<br>EQ4A   | Differential connection for external equalization components for 4 Mbps                                                                                                                             |

| 34   | TxCLK              | Synchronized data clock input from the previous lobe or Ring In/Ring Out port. In INSERT mode TxCLK clocks TxD out onto the transmit twisted pair at TxTPP, TxTPN. In BYPASS mode the TxCLK input is internally connected to the RxCLK output. |          |                | operation. The equalizer is disabled when these two pins are tied together.                                                                                                                         |

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> Supply Voltage Range0.3V to 6V Input Voltage Range |

|--------------------------------------------------------------------|

| Digital Inputs0.3 to V <sub>CC</sub>                               |

| TxD, TxCLK, RxTPP,                                                 |

| RxTPN, XTAL1, XTAL2 –0.3V to V <sub>CC</sub>                       |

| Output Current                                                     |

| TxTPP, TxTPN 50mA                                                  |

| PHTMRX1, PHTMRX2, PHTMTX1, PHTMTX2 25mA                            |

| All other outputs 10mA                                             |

| Storage Temperature65°C to +150°C                                  |

| Lead Temperature (Soldering, 10 sec) 260°C                         |

# **OPERATING CONDITIONS**

| V <sub>CC</sub> Supply Voltage                    | 5V ± 5%           |

|---------------------------------------------------|-------------------|

| All V <sub>CC</sub> supply pins must be within 0. | 1V of each other. |

| All GND pins must be within 0.1V of               | each other.       |

| T <sub>A</sub> , Ambient Temperature              | 0°C to +70°C      |

| T <sub>I</sub> , Junction Temperature             | 0°C to +125°C     |

| REXT1                                             | 1.66K ohms ± 1%   |

| REXT2                                             | 2.42K ohms ± 1%   |

|                                                   |                   |

# **ELECTRICAL CHARACTERISTICS**

Over full range of operating conditions unless otherwise specified.

| SYMBOL             | PARAMETER                                            | CONDITIONS                                                    | MIN                                          | TYP | MAX                   | UNITS |

|--------------------|------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------|-----|-----------------------|-------|

| TTL Inputs (       | 4/16, NSERT, PHTMD/S, SQDIS,                         | ALLOW, TxD, TxCLK, FBYP)                                      |                                              |     | ,                     |       |

| V <sub>IL</sub>    | Input Low Voltage                                    | i <sub>IL</sub> = 400μA                                       | -0.3                                         | _   | 8.0                   | v     |

| V <sub>IH</sub>    | Input High Voltage                                   | l <sub>IH</sub> = 100μA                                       | 2.0                                          |     | V <sub>CC</sub> +0.3V | V     |

| I <sub>IL</sub>    | Input Low Current                                    | All except TxD, TxCLK; V <sub>IN</sub> = 0.4V                 | -400                                         |     |                       | μА    |

|                    |                                                      | TxD, TxCLK; $V_{IN} = 0.4V$                                   | -1600                                        |     | 1 1                   | μА    |

| I <sub>IH</sub>    | Input High Current                                   | V <sub>IN</sub> = 2.7V                                        |                                              |     | 100                   | μА    |

| TTL Output         | s (FAULT, LOCK, RxCLK, RxD, R                        | xCLK, RxD):                                                   | <u>'                                    </u> |     |                       |       |

| V <sub>OL</sub>    | Output Low Voltage                                   | I <sub>OL</sub> = 1mA                                         |                                              |     | 0.40                  | V     |

| V <sub>OH</sub>    | Output High Voltage                                  | I <sub>OH</sub> = -0.1mA                                      | 2.4                                          |     |                       | V     |

| Receiver           |                                                      |                                                               |                                              |     |                       |       |

| V <sub>OSR</sub>   | RxTPP-RxTPN Differential<br>Offset Voltage           | V <sub>SQDIS</sub> = V <sub>IH</sub>                          | -35                                          |     | 35                    | mV    |

| V <sub>DSO</sub>   | RxTPP-RxTPN Differential                             | RSL = V <sub>IL</sub>                                         | 335                                          |     | 565                   | mVp-p |

|                    | Squelch Threshold                                    | RSL = V <sub>IH</sub>                                         | 35                                           |     | 70                    | mVp-p |

| V <sub>PSO</sub>   | RxTPP-RxTPN Post-Squelch                             | $RSL = V_{1L}$                                                | 167                                          | •   | 282                   | mVp-p |

|                    | Differential Input Threshold                         | RSL = V <sub>IH</sub>                                         | 23                                           |     | 47                    | mVp-p |

| $V_{IBR}$          | RxTPP-RxTPN Open-Circuit<br>Common-Mode Bias Voltage |                                                               | 2.2                                          |     | 2.8                   | V     |

| R <sub>IDR</sub>   | RxTPP-RxTPN Differential<br>Input Resistance         | Input differential voltage = 2V, centered at V <sub>IBR</sub> | 3.0                                          |     | 6.7                   | ΚΩ    |

| V <sub>STX</sub>   | XTAL1 Input Switching<br>Threshold Voltage           |                                                               | 2.2                                          |     | 3.4                   | V     |

| I <sub>RXT1</sub>  | RExT1 Input Current                                  | RExT1 = 1.66KΩ                                                | 575                                          |     | 625                   | μΑ    |

| I <sub>RXT2</sub>  | RExT2 Input Current                                  | RExT2 = $2.42$ K $\Omega$                                     | 387                                          |     | 438                   | μА    |

| <b>Fransmitter</b> | <u> </u>                                             |                                                               | 1                                            | _   |                       |       |

| I <sub>TOUT</sub>  | TxTPP Differential Output<br>Current                 | $R_L = 100 \text{ or } 150\Omega$                             | 28                                           |     | 33                    | mA    |

| I <sub>TOFF</sub>  | TxTPP-TxTPN Off-state Output Current                 | $V_{\overline{FBYP}} = V_{IL}$ ; $R_L = 200\Omega$            | 1.5                                          |     | mA                    |       |

| I <sub>TXI</sub>   | TxTPP-TxTPN Differential<br>Current Imbalance        | $R_L = 200\Omega$                                             | -900                                         |     | +900                  | μА    |

# **ELECTRICAL CHARACTERISTICS** (Continued)

| SYMBOL           | PARAMETER CONDITIONS                              |                                                                | MIN  | TYP      | MAX  | UNITS |

|------------------|---------------------------------------------------|----------------------------------------------------------------|------|----------|------|-------|

| Phantom O        | utput Driver (PHTMD/ $\overline{S} = V_{1H}$ , ex | cept as noted)                                                 |      | <u> </u> |      |       |

| V <sub>OHP</sub> | PHTMTX1/PHTMTX2                                   | $I_{OHP} = -1 \text{mA}$                                       | 4.1  |          |      | V     |

|                  | Output High Voltage                               | I <sub>OHP</sub> = -2mA                                        | 3.8  |          |      | V     |

| I <sub>OHP</sub> | PHTMTX1/PHTMTX2 Output<br>Short Circuit Current   | V <sub>OHP</sub> = 0V                                          | -20  |          | -4   | mA    |

| l <sub>OZP</sub> | PHTMTX1/Tx2/Rx1/Rx2<br>Output Off Current         | $PHTMD/\overline{S} = V_{IL}$ $0V \le V_{OHP} \le V_{CC}$      | -100 |          | +100 | μА    |

| Phantom O        | utput Fault Sensing (PHTMD/ $\overline{S} =$      | V <sub>IH</sub> )                                              | -    |          |      | •     |

| V <sub>OPN</sub> | FAULT Output Voltage,<br>Normal Condition         | Notes 2, 3                                                     | 2.4  |          |      | V     |

| V <sub>OPF</sub> | FAULT Output Voltage,<br>Fault Condition          | Notes 2, 4                                                     |      |          | 0.45 | V     |

| Power Supp       | ly Current                                        |                                                                |      |          |      |       |

| I <sub>CC1</sub> | Supply Current, Transmitting                      | Note 1                                                         |      |          | 205  | mA    |

| I <sub>CC2</sub> | Supply Current, Idle                              | Current into all V <sub>CC</sub> pins, V <sub>CC</sub> = 5.25V |      |          | 165  | mA    |

| SYMBOL            | PARAMETER                                                  | CONDITIONS                                               | MIN  | TYP | MAX  | UNITS |

|-------------------|------------------------------------------------------------|----------------------------------------------------------|------|-----|------|-------|

| Fransmitter       | (Note 8)                                                   |                                                          |      |     |      |       |

| t <sub>DF01</sub> | TxTPP-TxTPN Output                                         | 16Mb/s, Note 5A                                          | 0.3  |     | 1.0  | ns    |

|                   | Delay Mismatch, Zeros and Ones                             | 4Mb/s                                                    | -0.5 |     | 0.5  | ns    |

| t <sub>DFMX</sub> | TxTPP-TxTPN Output<br>Delay Mismatch, Random Data          | 4Mb/s & 16Mb/s, Note 5B                                  | -2.0 |     | 2.0  | ns    |

| t <sub>DCD</sub>  | TxTPP=TxTPN Output                                         | 16Mb/s, Note 6                                           | -1.5 |     | 1.5  | ns    |

|                   | Duty Cycle Distortion                                      | 4Mb/s, Note 6                                            | -6.0 |     | 6.0  | ns    |

| Receiver, G       | ieneral                                                    |                                                          |      |     |      |       |

| t <sub>RPWL</sub> | Maximum RxTPP-RxTPN Period                                 | 16Mb/s, RxTP V <sub>DIFP-P</sub> = 1V                    | 166  |     | 244  | ns    |

|                   | To Turn On                                                 | 4Mb/s, RxTP V <sub>DIFP-P</sub> = 1V                     | 667  |     | 2000 | ns    |

| t <sub>RPWS</sub> | Minimum RxTPP-RxTPN Period                                 | 16Mb/s, RxTP V <sub>DIFP-P</sub> = 1V                    | 40   |     | 59   | ns    |

|                   | To Turn On                                                 | 4Mb/s, RxTP V <sub>DIFP-P</sub> = 1V                     | 166  |     | 244  | ns    |

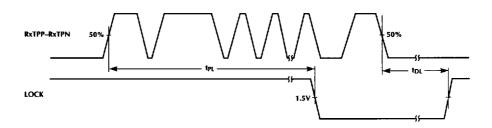

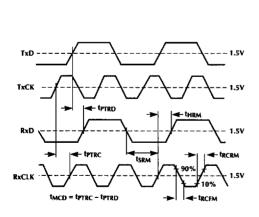

| tpL               | PLL Phase-Lock After Freq. Lock                            | Figure 1                                                 |      |     | 1.5  | ms    |

| t <sub>FL</sub>   | PLL Frequency-Lock After<br>Power-Up                       | Power-up to 2BR ± 1%<br>Hz frequency at RxCLK; Note 7    |      |     | 500  | ms    |

| t <sub>DL</sub>   | PLL Phase Unlock Time                                      | Figure 1                                                 |      |     | 100  | μs    |

| t <sub>PVC1</sub> | RxCLK Period, V <sub>FILTR4MB</sub> = 2.2V                 | $V_{4/\overline{16}} = V_{OH}$ (4Mb/s), Note 9           | 225  |     | 150  | ns    |

| t <sub>PVC2</sub> | RxCLK Period, V <sub>FILTR4MB</sub> = 2.8V                 | $V_{4/\overline{16}} = V_{OH}$ (4Mb/s), Note 9           | 75   |     | 112  | ns    |

| t <sub>PVC3</sub> | RxCLK Period, V <sub>FILTSL</sub> = 2.2V                   | $V_{4/\overline{16}} = V_{OL}$ (16Mb/s), Note 9          | 56.3 |     | 37.5 | ns    |

| t <sub>PVC4</sub> | RxCLK Period, V <sub>FILTSL</sub> = 2.8V                   | $V_{4/\overline{16}} = V_{OL}$ (16Mb/s), Note 9          | 18.8 |     | 28   | ns    |

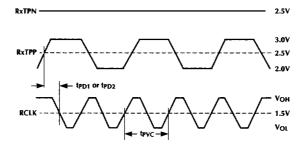

| K <sub>d</sub>    | Phase Detector Gain                                        | 4Mb/s; Note 10 and Figure 2                              | 0.25 |     | 0.35 | μA/ns |

|                   |                                                            | 16Mb/s; Note 10 and Figure 2                             | 1.0  |     | 1.4  | μA/ns |

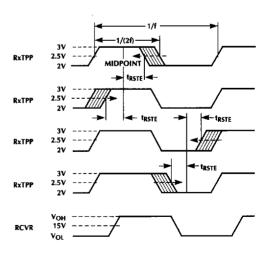

| t <sub>RSTE</sub> | PLL Static Phase Error                                     | Note 11                                                  | -2   |     | +2   | ns    |

| t <sub>RDC</sub>  | RxD to RxCLK Delay                                         |                                                          | -2   |     | 2    | ns    |

| t <sub>RTD</sub>  | RxTP to RxD Delay                                          |                                                          | 1    |     | 4    | ВТ    |

| t <sub>RCFS</sub> | RxCLK 90-10% Fall Time                                     | RxCLK t <sub>PER</sub> = 31.25ns                         |      |     | 5    | ns    |

| t <sub>PTRD</sub> | TxD to RxD Propagation Delay                               | $V_{\overline{FBYP}} = V_{OL}$ , Figure 4                | TBD  |     | TBD  | ns    |

| t <sub>PTRC</sub> | TxCK to RxCK Propagation Delay                             | $V_{\overline{FBYP}} = V_{OL}$ , Figure 4                | TBD  |     | TBD  | ns    |

| tsrm              | Setup Time, RxD Valid to RxCLK<br>Rising Edge (1.5V point) | RxCLK t <sub>PER</sub> = 31.25ns, Figure 4               | 10   |     |      | ns    |

| t <sub>HRM</sub>  | Hold Time, RxD Valid After<br>RxCLK Rising Edge (1.5V)     | RxCLK t <sub>PER</sub> = 31.25ns, Figure 4               | 2    |     |      | ns    |

| t <sub>RCRM</sub> | RxCLK 10-90% Rise Time                                     | RxCLK $t_{PER} = 31.25$ ns, $C_L = 15$ pF;<br>Figure 4   |      |     | 5    | ns    |

| t <sub>RCFM</sub> | RxCLK 90-10% Fall Time                                     | RxCLK $t_{PER} = 31.25 ns$ , $C_L = 15 pF$ ;<br>Figure 4 |      |     | 5    | ns    |

|                   |                                                            |                                                          |      |     |      |       |

- Note 1: Current into all  $V_{CC}$  pins,  $V_{CC}$  = 5.25V, transmitting and receiving 16MHz data. Note 2: Use a 2K ohm load at FAULT for these tests.

- Note 3: 2.9K < RL1 < 5.5K, 2.9K < RL2 < 5.5K. RL1 connected between PHTMTX1 and PHTMRX1; RL2 connected between PHTMTX2 and PHTMRX2.

- Note 4: Tested under the following conditions:

- A. RL1 > 9.9K and 2.9K < RL2 < 5.5K, or RL2 > 9.9K and 2.9K < RL1 < 5.5K.

- B. RL1 <  $100\Omega$  and 2.9K < RL2 < 5.5K, or RL2 <  $100\Omega$  and 2.9K < RL1 < 5.5K.

- Note 5: A. Difference between the delay from the nearest TxCLK rising edge to the TxTPPN differential BR edge and the delay from the nearest TxCLK rising edge to the TxTPPN differential BR/2 edge. Measured for either rising output edges or falling output edges only, with measurements made for each. Measurements are to be made at the output of both test circuits shown in Figure 3. (See waveforms in Figure 7 -4 of draft IEEE 802.5q/D4).

- B. Difference between the delay from the nearest TxCLK rising edge to the TxTPPN differential edge and the delay from the nearest TxCLK rising edge to the TXTPPN differential edge. Measured for either rising output edges or falling output edges only, with measurements made for each using random data (IKs, Os, 1s). Measurements are to be made at the output of both test circuits shown in Figure 3. (See waveforms in Figure 7 - 4 of draft IEEE 802.5q/D4).

- Note 6: One-half the difference between the positive-going differential output pulsewidth and the negative-going differential output pulsewidth. Measured at the output of both test circuits in Figure 3 with a constant stream of all zeros or all ones. Measurements are to be averaged over 128 data pulses. Measured with input drive to

- Not tested in production. Guaranteed by characterization measurements.

- Note 8: The transmitter TxTPP-TxTPN output waveform must also meet the waveform templates shown in section 7.2.2.2 of IEEE 802.5q.

- Note 9: Disconnect the filter components at the FILT4MB or FILT16MB pins and apply the indicated voltage to that pin. Measure the output period at RxCLK. Disconnect RxTPPN from all input.

- Note 10: See Figure 2 for timing. With the circuit in phase-lock, inject II = +5µA and measure the propagation delay tpD1 between an RXTPP rising edge and the corresponding RxCLK falling edge. Make a second delay measurement  $t_{PD2}$  while injecting  $t_2 = -5\mu A$ . Phase detector gain is given by  $K_d = (t_2-t_1)/(t_{PD1}-t_{PD2})$ .

- Note 11: The ML6682 is phase-locked to the RxTPP waveform with RxTPN biased to 2.5V (see Figure 5). Monitor RxD to observe correct data being latched. For one pulse, shorten the positive pulse at RxTPP by moving the rising edge, and check to see if the short pulse was latched. Continue to shorten the pulse in this manner until incorrect data appears at RxCLK. The time between the rising edge and the unshortened positive pulse midpoint is t<sub>RSTE</sub>. Repeat this procedure for the other 3 cases shown in Figure 5.

Figure 1. PLL Phase Lock Timing.

Figure 2. Phase Detector Gain Test.

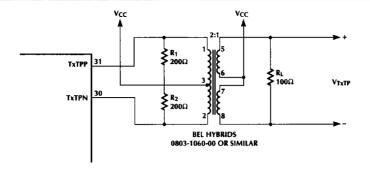

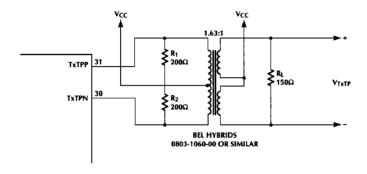

Figure 3A. Transmitter AC Test Circuit, 100 Ohms (UTP).

Figure 3B. Transmitter AC Test Circuit, 150 Ohms (STP).

Figure 4. Receiver Timing.

Figure 5. Receiver Static Timing Error Test.

### **FUNCTIONAL DESCRIPTION**

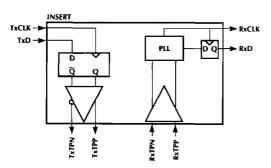

Page 1 shows the functional block diagram of the ML6682. The device contains four major functional blocks; twisted pair line interface, port interface, PLL retiming circuit and crystal oscillator. In normal operation, the data is retransmitted from the previous port on to the transmit TP wire pair (to the station) by the use of TxD and TxCLK. The data from the station via the receive wire pair is retimed through the use of a dual PLL/FIFO. The retimed data at RxD is then clocked out to the next port by RxCLK.

#### **PORT INTERFACE**

The ML6682 can be used for implementing Lobe, Ring In and Ring Out ports in a concentrator. The device can be placed into either the INSERT state or the BYPASS state. Figure 6 is a functional illustration of the INSERT and BYPASS states.

When ML6682 is in the BYPASS state, the station is bypassed. The data input from the previous port is retimed and fed directly through to the next port (see figure 6). Signal from the receive twisted pair is retimed via the PLL and looped back to the transmit twisted pair. However, if the signal does not meet the receive frequency squelch criteria, the signal will not be fed to the PLL. The PLL will transmit the local clock signal onto the transmit twisted pair.

Figure 6. Bypass and Insert States.

When the port is INSERTed into the network, the transmit data TxD from the previous port is clocked by transmit clock TxCLK, and fed out on the twisted pair lines. The data from the receive twisted pair input is passed through the PLL and output on RxD and RxCLK pins.

Through various input pins, the ML6682 may be selected for one of three options:

- 1. Forced into the INSERT state

- 2. Forced into the BYPASS state

- 3. Allow the remote station to place the ML6682 into INSERT or BYPASS state with phantom control.

The logic equation to implement these options is as follows:

$$\overline{FBYP} \times (\overline{ALLOW} + \overline{FAULT}) = INSERT$$

When INSERT is a logic 1, the ML6682 is placed into the INSERT state as shown in Figure 6. When INSERT is a logic 0, the ML6682 is placed into the BYPASS state. Truth table 1 illustrates how the three above options can be achieved.

|                              | FBYP | ALLOW | FAULT | INSERT<br>State |

|------------------------------|------|-------|-------|-----------------|

| Forced<br>Bypass Mode        | 0    | х     | х     | 0               |

| Phantom<br>Controlled Bypass | 1    | 0     | 0     | 0               |

| Phantom<br>Controlled Insert | 1    | 0     | 1     | 1               |

| Forced Insert                | 1    | 1     | Х     | 1               |

X = Don't Care

Table 1. Logic for INSERT/BYPASS.

#### **TP LINE INTERFACE**

TP Line Receiver consists of a line equalizer, receive squelch circuit and a resistive attenuator.

### **RECEIVE EQUALIZER**

This receive equalizer compensates for twisted-pair cable dispersion, which otherwise would give rise to intersymbol interference (ISI). The amount of equalization varies with the average amplitude of the received signal. The received signal amplitude gives a rough value for the length of the attached cable. The filter/equalizer characteristic is the inverse of the cable's dispersion characteristic. Both UTP and STP cables approximate a low-pass filter, so the filter/equalizer approximates an inverse root equalizer. There are two sets of equalizers, one for 4 Mbps operation and one for 16 Mbps operation. This is switched automatically when the 4/16 pin is toggled. Each equalizer has its own external components which consist of two resistors and a capacitor.

### **RECEIVE SQUELCH CIRCUIT**

The TP line receiver consists of a resistive attenuator with common-mode bias set circuit and voltage offset comparators to set the amplitude squelch threshold. When the RxTP input signal meets amplitude and pulsewidth requirements, the SQUELCH circuit reduces the offset voltage of the TP Line Receive comparators, decreasing the amplitude squelch threshold. This hysteresis allows the receiver to stay on in the presence of a fading input signal.

The receive squelch circuit qualifies the incoming signal to determine whether the signal contains valid data. The circuit qualifies the signal on the basis of both the amplitude and frequency of the signal. This prevents the PLL from trying to lock onto the wrong frequency when using 4 or 16 Mbps data rates, as well as preventing the PLL from locking onto noise. Once the signal has been qualified, the circuit will then unsquelch. The RSL pin selects one of two amplitude levels for the amplitude squelch criteria, while the  $4/\overline{16}$  pin selects one of two frequency squelch criteria.

The level of the amplitude squelch circuit can be selected by using the RSL pin. The squelch threshold range is as follows:

|         | MIN Threshold         | MAX Threshold         |  |

|---------|-----------------------|-----------------------|--|

| RSL = 1 | 35 mV <sub>P-P</sub>  | 70 mV <sub>P-P</sub>  |  |

| RSL = 0 | 335 mV <sub>P-P</sub> | 565 mV <sub>P-P</sub> |  |

#### Frequency Squelch Criteria

4 Mbps max limit 4.1MHz to 6MHz

4 Mbps min limit 0.5MHz to 1.5MHz

16 Mbps max limit 17MHz to 25MHz

16 Mbps min limit 4.1MHz to 6MHz

When squelch is on, the PLL is tracking the internal clock frequency coming from an external clock or the internal oscillator. When the part unsquelches the PLL switches into phase acquisition mode, attempting to phase lock onto the incoming data.

#### PHASE LOCK LOOP

The PLLs are third-order, type II charge pump loops (see F.M. Gardner, "Charge-Pump Phase-Lock Loops", IEEE Trans Comm, Vol. COM-28, No. 11, pp. 1849-1858, November 1980). They have high damping factor and low loop bandwidth to minimize accumulated jitter. The loop filter is externally connected. The third pole is at a very high frequency, since the ratio of the second and third order pole capacitors C1/C3 is about 20,000:1. This, too, is done to minimize accumulated jitter.

The 16 Mbps loop filter, slave loop filter, and 4 Mbps loop filter are external to the chip. Each filter consists of two capacitors and a resistor. The switching between the 16Mbps and 4Mbps loop filters is automatic when the  $4\sqrt{16}$  pin is toggled. Each data rate uses a different charge pump.

The VCO uses a MOS voltage-to-current converter at its input to give a very high input impedance and low static phase error. The high VCO input impedance also allows the elimination of a loop filter buffer and the parasitic poles a buffer would add to the loop. The oscillator itself is a bipolar ring type oscillator with temperature and voltage-compensated output frequency for low jitter.

The first PLL will achieve lock after several microseconds of a static phase error of less than  $\pm$  4 nsec. Hysteresis is built into the lock circuit so that it is more difficult to achieve lock than it is to lose lock. This will also prevent any oscillation of the  $\overline{LOCK}$  pin. Lock will be lost if the phase error exceeds  $\pm 4$  nsec for several micro-seconds. Once lock is lost, the PLL will try to achieve phase lock for several milli-seconds. If it is unsuccessful, the ML6682 will switch to internal frequency acquisition mode and recenter the VCO. Once it has achieved frequency lock with its internal oscillator, it will automatically switch to phase acquisition mode and try again to phase lock onto the data.

The frequency squelch circuit will limit the frequency range allowed to pass into the PLL. This limited frequency range in addition to the stringent lock criteria will insure that the PLL will not lock onto harmonics or sidebands of the fundamental data rate.

The first PLL clocks the data into an 8 UI FIFO. Each flip-flop in the FIFO stores one UI which is one half bit. The second (slave) PLL has a much narrower bandwidth set by the external filter connected to pin FILTPLL2. The second PLL is fed the first PLL's clock so that it can remove more of the jitter. The clock out of the second PLL is used to clock the data out of the FIFO and onto the RxD pin. The second PLL's clock output appears at RxCLK. This dual PLL architecture is the most effective way to reduce jitter and insure optimal performance from a token ring network.

#### TP LINE DRIVER

The TP OUTPUT driver uses a current mode switch which develops the output voltage by driving current through the terminating resistor and the output filter. Both TxTPP and TxTPN outputs are open collector, intended to drive a center-tapped transformer, with the center tap connected to  $V_{CC}$ . The driver is capable of driving  $150\Omega$  doubly-terminated transmission lines to a minimum  $4.1V_{P-P}$  level or  $100\Omega$  doubly-terminated transmission lines to a minimum  $2.7V_{P-P}$  level. The driver's output is waveshaped, allowing the use of a simple external transmit filter.

#### PHANTOM CURRENT DETECTION

The ML6682 provides a phantom current detection function. With PHTMD/S driven high, the phantom voltage and wire fault detection circuit provides correct phantom DC output voltage under normal conditions. It also senses short-circuit and open-circuit fault conditions, and removes phantom voltage when appropriate.

In the LOBE port application with PHTMD/S tied low (FBYP is tied high and ALLOW is tied low), driving PHTMRX1 high places the device into the INSERT mode. Driving PHTMRX1 low places the device in the BYPASS mode, in which data from the previous port will be passed on to the next port.

#### **CLOCK OSCILLATOR**

The ML6682 provides an on-chip clock oscillator by connecting a crystal to the XTAL1 pin. The ML6682 can also be driven by an external 16MHz clock at the XTAL1 pin, or by an external 32MHz clock at the XTAL2 pin. In either case, the unused XTAL pin should be grounded.

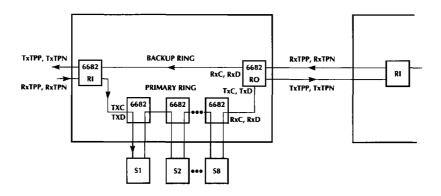

### **APPLICATIONS**

Figure 7 shows a block diagram of an intelligent UTP Hub implementation with active retiming on each port. The architecture shown has a back up ring for fault tolerant operation. The Ring In and Ring Out ports use phantom current to detect wire faults. When a fault is detected, the Ring-In and Ring-Out port go into the bypass state and perform an automatic loopback onto the Back-up Ring. This feature is especially useful in stackable hub designs.

A micro processor can be used to manage each individual port. All the ports including the Ring In and Ring Out ports can be individually programmed into "Force INSERT", "Force BYPASS" or "Allow phantom control".

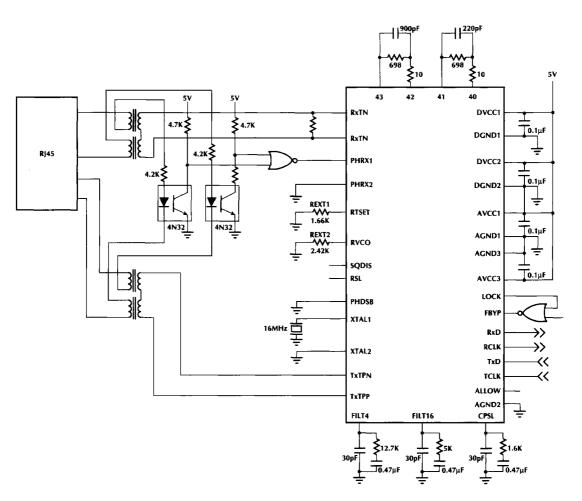

#### LOBE PORT

Figure 8 shows a typical implementation of a lobe port. Lobe ports are configured as phantom sense ports using opto isolators for sensing phantom current. Phantom current is sensed with an opto isolated output signal fed into pin PHTMRX1. PHTMTX1 will go low with an open collector output when the ML6682 goes into the INSERT state. PHTMTX1 may either be used to drive an LED indicator or another opto isolator to signal the remote station whether it is inserted or not.

By connecting the signal from the  $\overline{\text{LOCK}}$  pin to the  $\overline{\text{FBYP}}$  pin, the ML6682 is forced into bypass mode until the PLL achieves lock. When a station with a frequency different than the ring frequency attempts to insert into the ring, the PLL will not achieve lock and thus the station will not be inserted.

Figure 7. Intelligent UTP Hub.

#### **RING-IN PORT**

The Ring In port may also be configured for phantom sense with automatic loopback fault detection. When Phantom current is detected the part is in the INSERT state. If phantom current is lost, the ML6682 will automatically switch to the BYPASS state. Using the FBYP and ALLOW pins the part can also be forced into INSERT state, for compatibility with older standard type hubs, or forced into BYPASS for diagnostic purposes.

The configuration of a fault tolerant Ring In port is implemented exactly like a lobe port. The TxD and TxCLK pins are connected to the RxD and the RxCLK pins of the ring out port to create a "back up" ring. When the fault tolerant feature is not needed for compatibility with the older hubs, the phantom current sense capability of the

ML6682 should be disabled and the device should be placed in the forced insert state by using FBYP and ALLOW. The LOCK pin should still be used to ensure that the proper ring speed is maintained.

#### RING OUT PORT

Tie the PHTMD/S pin high to configure the ML6682 as a Ring Out port. In this mode the Ring Out port looks like a station; however, when a FAULT is detected on the transmit or receive twisted pair wires, the ML6682 will automatically go into BYPASS state. The PHTMRX1 and PHTMRX2 pins drive the receive pair transformer center taps, and the PHTMX1 and PHTMTX2 pins drive the transmit pair transformer center taps on the cable side of the transformers in this mode.

Figure 8. Typical Circuit for a Lobe Port.

# **ORDERING INFORMATION**

| PART NUMBER | TEMPERATURE RANGE | PACKAGE           |  |

|-------------|-------------------|-------------------|--|

| ML6682CS    | 0°C to +70°C      | 44-Pin PLCC (Q44) |  |