Data Sheet

January 2005

## Features

- FAX and Modem interface (V.34/V.34+)

- Designed to work at data rates up to 56 kbits

- External programmable line and network balance impedances

- · Programmable DC termination characteristics

- IEC950 recognised component

- Transformerless 2-4 Wire conversion

- Integral Loop Switch

- Dial Pulse and DTMF operation

- · Accommodates parallel phone detection

- Line state detection outputs:

-loop current/ringing voltage/line voltage

- +5 V operation, low on-hook power (25 mW)

- · Full duplex voice and data transmission

- On-Hook reception from the line

- Meets French current limit requirements

- · Conforms to German dial pulse standards

- Approvable to UL 1950

- Industrial Temperature Range Available

## **Applications**

- · Interface to Central Office or PABX line for:

- FAX/Modem

#### **Ordering Information**

MH88437AD-P 28 Pin DIL Package MH88437AS-P 28 Pin SM Package MH88437AS-PR 28 Pin SM Package (Tape & Reel)

#### 0°C to +70°C

- Electronic Point of Sale

- Security System

- Telemetry

- Set Top Boxes

## Description

The Zarlink MH88437 Data Access Arrangement (D.A.A.) provides a complete interface between audio or data transmission equipment and a telephone line. All functions are integrated into a single thick film hybrid module which provides high voltage isolation, very high reliability and optimum circuit design, needing a minimum of external components.

The impedance and network balance are externally programmable, as are the DC termination characteristics, making the device suitable for most countries worldwide.

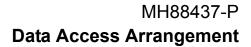

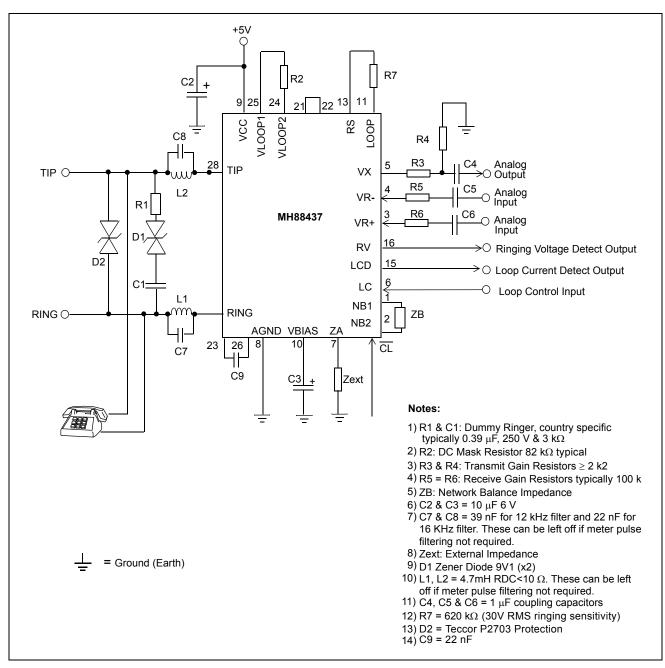

## Figure 1 - Functional Block Diagram

1

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2003-2005, Zarlink Semiconductor Inc. All Rights Reserved.

| 28 | ] TIP                                                                |

|----|----------------------------------------------------------------------|

| 27 | RING                                                                 |

| 26 | ] C1                                                                 |

| 25 | VLOOP1                                                               |

| 24 | VLOOP2                                                               |

| 23 | ] C2                                                                 |

| 22 | ] sc                                                                 |

| 21 | ] sc                                                                 |

| 20 |                                                                      |

| 19 | ] NP                                                                 |

| 18 | ] NP                                                                 |

| 17 |                                                                      |

| 16 | ] RV                                                                 |

| 15 | LCD                                                                  |

|    |                                                                      |

|    | 27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16 |

#### Figure 2 - Pin Connections

# Change Summary

The following table captures the changes from the September 2003 issue.

| Page | ltem     | Change            |  |  |  |

|------|----------|-------------------|--|--|--|

| 4    | Figure 3 | Corrected values. |  |  |  |

# **Pin Description**

| Pin # | Name            | Description                                                                                                                                                                                    |

|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | NB1             | <b>Network Balance 1.</b> External passive components must be connected between this pin and NB2.                                                                                              |

| 2     | NB2             | <b>Network Balance 2.</b> External passive components must be connected between this pin and NB1.                                                                                              |

| 3     | VR+             | Differential Receive (Input). Analog input from modem/fax chip set.                                                                                                                            |

| 4     | VR-             | Differential Receive (Input). Analog input from modem/fax chip set.                                                                                                                            |

| 5     | VX              | <b>Transmit (Output).</b> Ground referenced (AGND) output to modem/fax chip set, biased at +2.0 V.                                                                                             |

| 6     | LC              | <b>Loop Control (Input).</b> A logic 1 applied to this pin activates internal circuitry which provides a DC termination across Tip and Ring. This pin is also used for dial pulse application. |

| 7     | ZA              | <b>Line Impedance.</b> Connect impedance matching components from this pin to Ground (AGND).                                                                                                   |

| 8     | AGND            | Analog Ground. 4-Wire 0 V reference connect to mains earth (ground).                                                                                                                           |

| 9     | V <sub>CC</sub> | Positive Supply Voltage. +5 V.                                                                                                                                                                 |

| 10    | VBIAS           | Internal Reference Voltage. +2.0 V reference voltage. This pin should be decoupled externally to AGND, typically with a 10 $\mu$ F 6.3 V capacitor.                                            |

| 11    | LOOP            | <b>Loop (Output).</b> The output voltage on this pin is proportional to the line voltage across Tip - Ring, scaled down by a factor of 50.                                                     |

|           | escriptio |                                                                                                                                                         |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #     | Name      | Description                                                                                                                                             |

| 12,<br>14 | IC        | Internal Connection. No connection should be made to this pin externally.                                                                               |

| 13        | RS        | <b>Ringing Sensitivity.</b> Connecting a link or resistor between this pin and LOOP (pin 11) will vary the ringing detection sensitivity of the module. |

| 15        | LCD       | Loop Condition Detect (Output). Indicates the status of loop current.                                                                                   |

| 16        | RV        | <b>Ringing Voltage Detect (Output).</b> The RV output indicates the presence of a ringing voltage applied across the Tip and Ring leads.                |

| 17        | CL        | <b>Current Limit.</b> A logic 0 applied to this pin activates internal circuitry which limits the loop current.                                         |

| 18        | NP        | No Pin. Isolation Barrier, fitted, no pin fitted in this position.                                                                                      |

| 19        | NP        | No Pin. Isolation barrier, no pin fitted in this position                                                                                               |

| 20        | IC        | Internal Connection. No connection should be made to this pin externally.                                                                               |

| 21,22     | SC        | Short Circuit. These two pins should be connected to each other via a $0\Omega$ link.                                                                   |

| 24        | VLOOP2    | Loop Voltage Control Node 2. Used to set DC termination characteristics.                                                                                |

| 25        | VLOOP1    | Loop Voltage Control Node 1. Used to set DC termination characteristics.                                                                                |

| 27        | RING      | Ring Lead. Connects to the "Ring" lead of the telephone line.                                                                                           |

| 28        | TIP       | Tip Lead. Connects to the "Tip" lead of the telephone line.                                                                                             |

| 26,23     | C1, C2    | Cap. Fit a 22 nF Cap between these two pins.                                                                                                            |

# Pin Description

# Functional Description

The device is a Data Access Arrangement (D.A.A.). It is used to correctly terminate a 2-Wire telephone line. It provides a signalling link and a 2-4 Wire line interface between an analog loop and subscriber data transmission equipment, such as Modems, Facsimiles (Fax's), Remote Meters, Electronic Point of Sale equipment and Set Top Boxes.

# **Isolation Barrier**

The device provides an isolation barrier capable of meeting the supplementary barrier requirements of the international standard IEC 950 and the national variants of this scheme such as EN 60950 for European applications and UL 1950 for North American applications.

# **External Protection Circuit**

An External Protection Circuit assists in preventing damage to the device and the subscriber equipment, due to over-voltage conditions. See Application Note MSAN-154 for recommendations.

# Suitable Markets

The MH88437 has features such as programmable line and network balance impedance, programmable DC termination and a supplementary isolation barrier. For countries that do not need to meet the French and German requirements there is a pin for pin compatible device the MH88435.

There are, however, a small number of countries with a 100 M $\Omega$  leakage requirement that this device does not meet. These are Belgium, Greece, Italy, Luxembourg, Spain and Poland.

CTR21 is generally accepted within Europe, and this route should be selected for those countries. This should be attempted with the consultation of a local approvals house.

Approval specifications are regularly changing and the relevant specification should always be consulted before commencing design.

## **Line Termination**

When Loop Control (LC) is at a logic 1, a line termination is applied across Tip and Ring. The device can be considered off-hook and DC loop current will flow. The line termination consists of both a DC line termination and an AC input impedance. It is used to terminate an incoming call, seize the line for an outgoing call, or if it is applied and disconnected at the required rate, can be used to generate dial pulses.

The DC termination resembles approximately  $300 \Omega$  resistance, which is loop current dependent. Furthermore, it can be programmed to meet different national requirements. For normal operation VLOOP3 should be open circuit and a resistor (R2) should be fitted between VLOOP1 and VLOOP2, as shown in Figure 5.

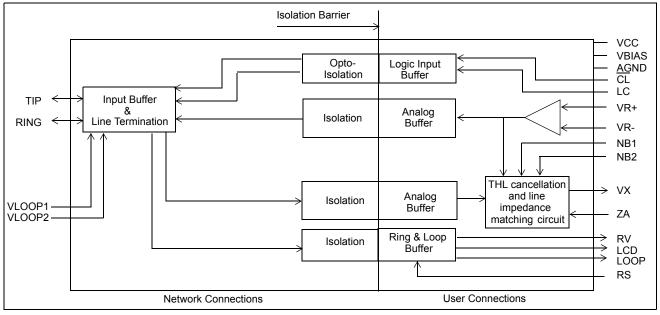

The approval specification will give a DC mask characteristic that the equipment will need to comply to. The DC mask specifies the amount of current the DAA can sink for a given voltage across tip and ring. Graph 1 shows how the voltage across tip and ring varies with different resistors (R2) for a given loop current.

By applying a logic 0 to Pin 17,  $\overline{CL}$ , the loop current will be limited to below 60 mA as required in France and the European TBR21 specification. For all other countries where current limiting is not required,  $\overline{CL}$  should be set to 1.

Figure 3 - DC Programming Capability

## Input Impedance

The AC input impedance should be set by the user to match the line impedance.

The MH88437 has a programmable input impedance set by fitting external components between the ZA pin and AGND.

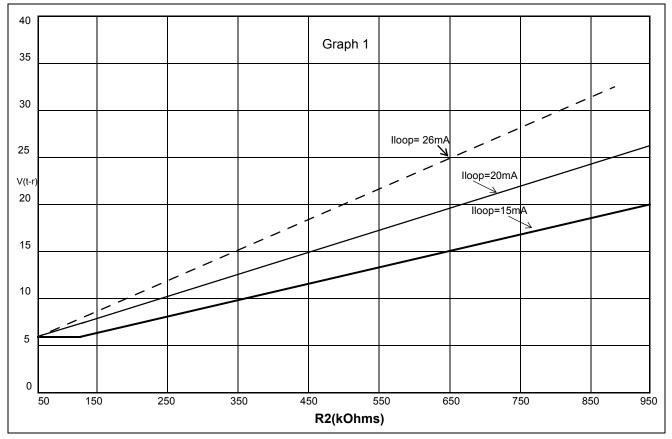

For complex impedances the configuration shown in Figure 4 (below) is most commonly found.

Figure 4 - Complex Impedances

To find the external programming components for configuration 4, the following formula should be used:  $Zext = [(10 \times R1)-1k3]+[(10 \times R2)//(C1/10)]$

e.g. If the required input impedance = 220  $\Omega$  + (820  $\Omega$ //115 nF), the external network to be connected to ZA will be:

#### $ZA = 900 \Omega + (8 k 2 \Omega / / 12 nF)$

Where the input impedance (Z) = 600R the equation can be simplified to:

$ZA = (10 \text{ x } Z) - 1k3\Omega$

ZA = 4k7Ω

Note: A table of commonly used impedances can be found in the DAA Application's document MSAN-154.

Where Zext = external network connected between ZA and AGND and Zint = 1.3 k $\Omega$  (internal resistance).

#### **Network Balance**

The network balance impedance of the device can be programmed by adding external components between NB1 and NB2. For countries where the balance impedance matches the line impedance, a 16 k $\Omega$  resistor should be added between NB1 and NB2.

## **Ringing Voltage Detection**

The sensitivity of the ringing voltage detection circuitry can be adjusted by applying an external resistor (R7, Figure 5) between the RS and LOOP pins. With a short circuit, the threshold sensitivity is ~10Vrms, therefore R7 =  $30 \text{ k}\Omega \times (\text{Desired threshold voltage - }10 \text{ Vrms})$ .

Example: 300 k $\Omega$  gives ~20 Vrms and 600 k $\Omega$  gives ~30 Vrms.

An AC ringing voltage across Tip and Ring will cause RV to output TTL pulses at the ringing frequency, with an envelope determined by the ringing cadence.

## Parallel Phone and Dummy Ringer

An external parallel phone or dummy ringer circuit can be connected across Tip and Ring as shown in Figure 5. A Dummy Ringer is an AC load which represents a telephone's mechanical ringer.

In normal circumstances when a telephone is On-Hook and connected to the PSTN, its AC (Ringer) load is permanently presented to the network. This condition is used by many PTT's to test line continuity, by placing a small AC current onto the line and measuring the voltage across tip (A) and ring (B).

Today's telecom equipment may not have an AC load present across tip and ring (e.g. modems), therefore any testing carried out by the PTT will see an open circuit across tip and ring. In this instance the PTT assumes that the line continuity has been damaged.

To overcome this problem many PTT's specify that a "Dummy Ringer" is presented to the network at all times. Ideally its impedance should be low in the audio band and high at the ringing frequencies (e.g. 25Hz). Note that the requirement for the "Dummy Ringer" is country specific.

Parallel phone detection is used mostly in set-top box applications. This is when a modem call will need to be disconnected from the central office by the equipment when the parallel phone is in the off-hook state. This is to allow the subscriber to make emergency calls.

To detect this state, additional circuitry will be required. Refer to Application Note MSAN-154.

## 2-4 Wire Conversion

The device converts the balanced 2-Wire input, presented by the line at Tip and Ring, to a ground referenced signal at VX, biased at 2.0V. This simplifies the interface to a modem chip set.

Conversely, the device converts the differential signal input at VR+ and VR- to a balanced 2-Wire signal at Tip and Ring. The device can also be used in a single ended mode at the receive input, by leaving VR+ open circuit and connecting the input signal to VR- only. Both inputs are biased at 2.0V.

During full duplex transmission, the signal at Tip and Ring consists of both the signal from the device to the line and the signal from the line to the device. The signal input at VR+ and VR- being sent to the line, must not appear at the output VX. In order to prevent this, the device has an internal cancellation circuit, the measure of this attenuation is Transhybrid Loss (THL).

The MH88437 has the ability to transmit analog signals from Tip and Ring through to VX when on-hook. This can be used when receiving caller line identification information.

## **Transmit Gain**

The Transmit Gain of the MH88437 is the gain from the differential signal across Tip and Ring to the ground referenced signal at VX. The internal Transmit Gain of the device is fixed as shown in the AC Electrical Characteristics table. For the correct gain, the Input Impedance of the MH88437, must match the specified line impedance.

By adding an external potential divider to VX, it is possible to reduce the overall gain in the application. The output impedance of VX is approximately 10  $\Omega$  and the minimum resistance from VX to ground should be 2 k $\Omega$ .

Example: If R3 = R4 = 2 k $\Omega$ , in Figure 5, the overall gain would reduce by 6.0 dB.

## **Receive Gain**

The Receive Gain of the MH88437 is the gain from the differential signal at VR+ and VR- to the differential signal across Tip and Ring. The internal Receive Gain of the device is fixed as shown in the AC Electrical Characteristics table. For the correct gain, the Input Impedance of the MH88437 must match the specified line impedance.

With an internal series input resistance of 47 k $\Omega$  at the VR+ and VR- pins, external series resistors can be used to reduce the overall gain.

Overall Receive Gain = 0 dB+20log (47 k $\Omega$ /(47 k $\Omega$ +R5)).

For differential applications R6 must be equal to R5 in Figure 5.

Example: If R5 = R6 = 47 k in Figure 5, the overall gain would reduce by 6.0 dB.

## **Supervisory Features**

The device is capable of monitoring the line conditions across Tip and Ring, this is shown in Figure 5. The Loop Condition Detect pin (LCD), indicates the status of the line. The LCD output is at logic 1 when loop current flows, indicating that the MH88437 is in an off hook state. LCD will also go high if a parallel phone goes off-hook. Therefore, line conditions can be determined with the LC and the LCD pins.

The LOOP pin output voltage,  $V_{LOOP}$  is proportional to the line voltage across Tip and Ring, V (t-r), scaled down by a factor of 50 and offset by VBias which is approximately 2 V. With the aid of a simple external detector the LC, LCD and LOOP pins can be used to generate the signals necessary for parallel phone operation with a Set Top Box. Refer to Application Note MSAN-154.

If Tip is more positive than ring  $V_{LOOP}$  < VBias

If Tip is more negative than ring  $V_{LOOP}$  >VBias

When the device is generating dial pulses, the LCD pin outputs TTL pulses at the same rate. The LCD output will also pulse if a parallel phone is used to dial and when ringing voltage is present at Tip and Ring.

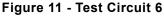

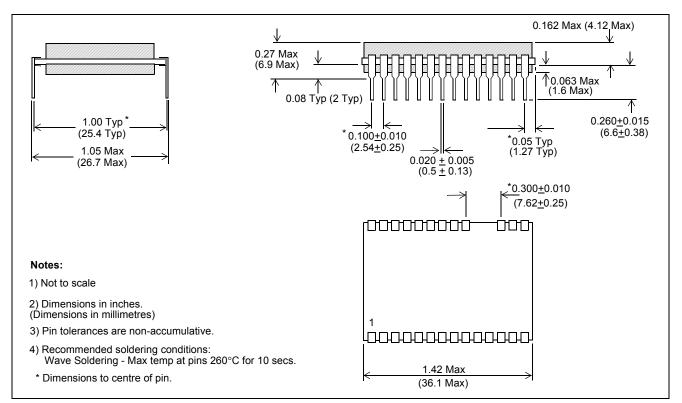

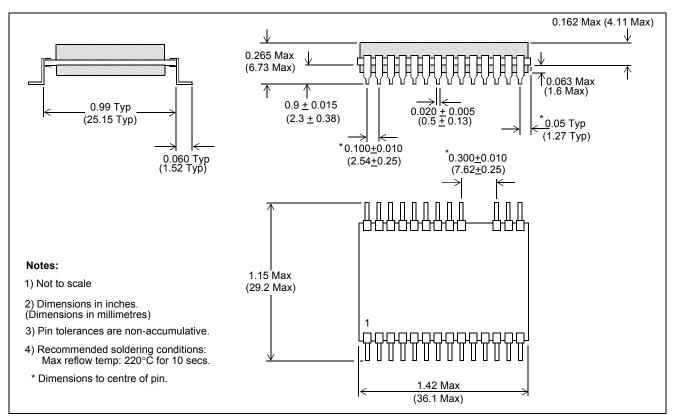

## Mechanical Data

See Figures 12, 13 and 14 for details of the mechanical specification.

Figure 5 - Typical Application Circuit

# Absolute Maximum Ratings\* - All voltages are with respect to AGND unless otherwise specified.

|   | Parameter           | Sym.            | Min. | Max. | Units | Comments |

|---|---------------------|-----------------|------|------|-------|----------|

| 1 | DC Supply Voltage   | V <sub>CC</sub> | -0.3 | 6    | V     |          |

| 2 | Storage Temperature | Τ <sub>S</sub>  | -55  | +125 | °C    |          |

| 3 | DC Loop Voltage     | $V_{TR}$        | -110 | +110 | V     |          |

| 703 | Absolute maximum ratings - Air voltages are with respect to AGND unless otherwise specified. |                   |  |          |          |                                                 |  |  |  |

|-----|----------------------------------------------------------------------------------------------|-------------------|--|----------|----------|-------------------------------------------------|--|--|--|

| 4   | Transient loop voltage                                                                       | V <sub>TR</sub>   |  | 300      | V        | 1ms On hook                                     |  |  |  |

| 5   | Ringing Voltage                                                                              | V <sub>R</sub>    |  | 150      | Vrms     | VBAT = -56V                                     |  |  |  |

| 6   | Loop Current                                                                                 | I <sub>LOOP</sub> |  | 60<br>90 | mA<br>mA | <u>CL</u> =0 V <sub>TIP-RING</sub> ≤40V<br>CL=1 |  |  |  |

| 7   | Ring Trip Current                                                                            | I <sub>TRIP</sub> |  | 180      | mArms    | 250ms 10% duty cycle or 500ms single shot       |  |  |  |

#### Absolute Maximum Ratings\* - All voltages are with respect to AGND unless otherwise specified

\*Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

## **Recommended Operating Conditions**

|   | Parameter                                        | Sym.            | Min.     | Typ.‡ | Max.      | Units | Test Conditions |

|---|--------------------------------------------------|-----------------|----------|-------|-----------|-------|-----------------|

| 1 | DC Supply Voltages                               | $V_{CC}$        | 4.75     | 5.0   | 5.25      | V     |                 |

| 2 | Operating Temperatures<br>Industrial Temperature | T <sub>OP</sub> | 0<br>-40 | 25    | 70<br>+85 | °C    |                 |

| 3 | Ringing Voltage                                  | V <sub>R</sub>  |          | 75    | 90        | Vrms  | VBat = -48 V    |

<sup>‡</sup> Typical figures are at 25°C with nominal +5 V supply and are for design aid only.

## Loop Electrical Characteristics <sup>†</sup>

|   | Characteristics                             | Sym. | Min.   | Typ.‡    | Max.              | Units        | Test Conditions                                                                                                                 |

|---|---------------------------------------------|------|--------|----------|-------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1 | Ringing Voltage<br>No Detect<br>Detect      | VR   | 14     |          | 7                 | Vrms<br>Vrms | Externally Adjustable                                                                                                           |

| 2 | Ringing Frequency                           |      | 15     |          | 68                | Hz           |                                                                                                                                 |

| 3 | Operating Loop Current                      |      | 15     |          | 60<br>80          | mA<br>mA     | $\frac{\overline{CL}}{\overline{CL}}=0 \text{ V}_{\text{TIP-RING}} \leq 40 \text{ V}$<br>$\overline{CL}=1 \text{ (see Note 1)}$ |

| 4 | Off-Hook DC Voltage                         |      |        |          | 6.0<br>6.0<br>7.8 | V<br>V<br>V  | Externally Adjustable<br>$I_{LOOP}$ =15 mA)<br>$I_{LOOP}$ =20 mA) (Note 3)<br>$I_{LOOP}$ =26 mA)<br>where R2 = 110 k $\Omega$   |

| 5 | Leakage Current (Tip<br>or Ring to AGND)    |      |        |          | 10<br>7           | μA<br>mA     | 100V DC (see Note 2)<br>1000V AC                                                                                                |

| 6 | Leakage Current on-hook<br>(Tip to Ring)    |      |        | 9<br>18  | 10<br>20          | μΑ           | V <sub>BAT</sub> (= -50 V)<br>V <sub>BAT</sub> (= -100 V)                                                                       |

| 7 | Dial Pulse Detection ON OFF                 |      | 0<br>0 | +1<br>+1 | +2<br>+2          | ms<br>ms     | Dial pulse delay                                                                                                                |

| 8 | Loop Condition Detect Threshold<br>Off-Hook |      | 5      |          | 16                | V            | Voltage across tip and ring                                                                                                     |

$^+$  Electrical Characteristics are over Recommended Operating Conditions unless otherwise stated.  $^+$  Typical figures are at 25°C with nominal + 5 V supplies and are for design aid only. Note 1: Low Loop current operation depends on value of resistor connected between V<sub>Loop</sub> 1 and V<sub>Loop</sub> 2. Note 2: This is equivalent to 10 MΩ leakage Tip/Ring to Ground. Note 3. Refer to EIA/TIA 464 Section 4.1.1.4.4

## **DC Electrical Characteristics**<sup>†</sup>

|   |            | Characteristics                                                                                            | Sym.                                                                     | Min. | Typ.‡    | Max.             | Units              | Test Conditions                                              |

|---|------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|----------|------------------|--------------------|--------------------------------------------------------------|

| 1 |            | Supply Current                                                                                             | I <sub>CC</sub>                                                          |      | 5        |                  | mA                 | V <sub>DD</sub> (= 5.0V, On-hook)                            |

| 2 | RV,<br>LCD | Low Level Output Voltage<br>High Level Output Voltage                                                      | V <sub>OL</sub><br>V <sub>OH</sub>                                       | 2.4  |          | 0.4              | V<br>V             | I <sub>OL</sub> = 4mA<br>I <sub>OH</sub> = 0.4mA             |

| 3 | LC         | Low Level Input Voltage<br>High Level Input Voltage<br>Low Level Input Current<br>High Level Input Current | V <sub>IL</sub><br>V <sub>IH</sub><br>I <sub>IL</sub><br>I <sub>IH</sub> | 2.0  | 0<br>350 | 0.8<br>60<br>400 | V<br>V<br>μΑ<br>μΑ | V <sub>IL</sub> = 0.0V<br>V <sub>IH</sub> = 5.0V             |

| 4 | VR+<br>VR- | DC common mode                                                                                             | VCM                                                                      | 0    | 2        | VCC              | VDC                | Use coupling caps for<br>higher voltages and single<br>ended |

† Electrical Characteristics are over Recommended Operating Conditions unless otherwise stated.

‡ Typical figures are at 25°C with nominal + 5V supplies and are for design aid only.

# **AC Electrical Characteristics**<sup>†</sup>

|    | Characteristics                                    | Sym.  | Min.           | Typ.‡          | Max. | Units          | Test Conditions                                                         |

|----|----------------------------------------------------|-------|----------------|----------------|------|----------------|-------------------------------------------------------------------------|

| 1  | Input Impedance<br>VR-                             |       |                | 47k<br>94k     |      | Ω<br>Ω         |                                                                         |

|    | VR+                                                |       |                |                |      |                |                                                                         |

| 2  | Output Impedance at VX                             |       |                | 10             |      | Ω              |                                                                         |

| 3  | Receive Gain (VR to 2-Wire)                        |       | -1             | 0              | 1    | dB             | Test circuit (Figure 8)<br>Input 0.5V at 1 kHz                          |

| 4  | Frequency Response Gain (relative to Gain @ 1 kHz) |       | -0.5           | 0              | 0.5  | dB             | ILOOP = 15-60 mA<br>300Hz to 3400 Hz                                    |

| 5  | Signal Output Overload Level<br>at 2-Wire<br>at VX |       |                | 0<br>0         |      | dBm<br>dBm     | THD <u>&lt;</u> 5% @ 1 kHz<br>I <sub>LOOP</sub> = 25-60 mA<br>VCC = 5 V |

| 6  | Signal/Noise & Distortion<br>at 2-Wire<br>at VX    | SINAD |                | 70<br>70       |      | dB<br>dB       | Input 0.5 V at 1 kHz<br>I <sub>LOOP</sub> = 25-60 mA<br>300-3400 Hz     |

| 7  | Power Supply Rejection Ratio<br>at 2-Wire<br>at VX | PSRR  | 25<br>25       | 40<br>40       |      | dB<br>dB       | Ripple 0.1Vrms 1 kHz on $V_{DD}$                                        |

| 8  | Transhybrid Loss                                   | THL   | 16             | 25             |      | dB             | Test circuit (Figure 8)<br>300-3400 Hz at V <sub>R</sub>                |

| 9  | 2-Wire Input Impedance                             | Zin   |                | Note 3         |      | Ω              | @ 1 kHz                                                                 |

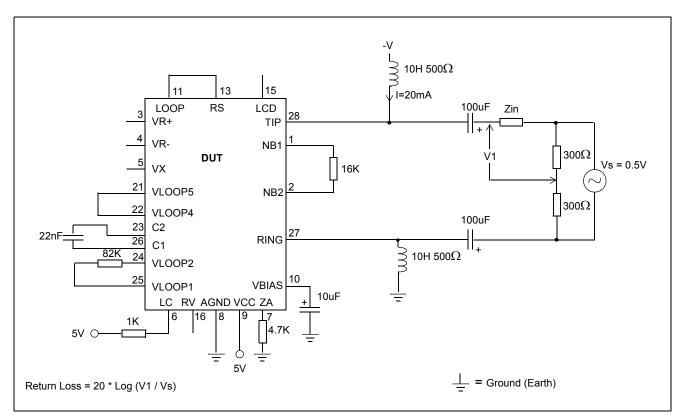

| 10 | Return Loss at 2-Wire (Reference 600 $\Omega$ )    | RL    | 14<br>20<br>18 | 24<br>24<br>24 |      | dB<br>dB<br>dB | Test circuit (Figure 9)<br>200-500 Hz<br>500-2500 Hz<br>2500-3400 Hz    |

# AC Electrical Characteristics <sup>†</sup> (continued)

|    | Characteristics                                                          | Sym. | Min.                 | Typ.‡                  | Max.       | Units                        | Test Conditions                                                                                                    |

|----|--------------------------------------------------------------------------|------|----------------------|------------------------|------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|

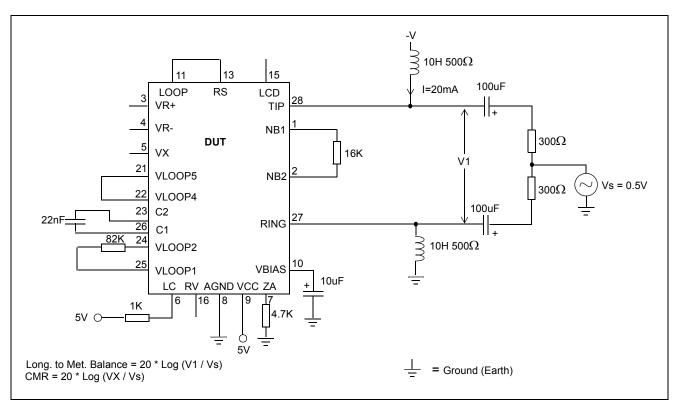

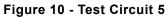

| 11 | Longitudinal to Metallic Balance<br>Metallic to Longitudinal Balance     | Nc   | 46<br>46<br>60<br>40 | 58<br>53               |            | dB<br>dB<br>dB<br>dB         | Test circuit (Figure 10)<br>300-1000 Hz<br>1000-3400 Hz<br>Test circuit (Figure 11)<br>200-1000 Hz<br>1000-4000 Hz |

| 12 | Idle Channel Noise<br>at 2-Wire<br>at VX<br>at 2-Wire<br>at VX           |      |                      | 15<br>15<br>-65<br>-65 | 20<br>20   | dBrnC<br>dBrnC<br>dBm<br>dBm | Cmess filter<br>300-3400 Hz filter                                                                                 |

| 13 | Transmit Gain (2-Wire to VX)<br>Off-Hook<br>On-Hook                      |      | -1                   | 0                      | +1         | dB<br>dB                     | Test circuit (Figure 7)<br>Input 0.5V @ 1 kHz<br>LC = 0 V                                                          |

| 14 | Frequency Response Gain<br>(relative to Gain @ 1 kHz)                    |      | -0.5<br>-0.5         | 0<br>0                 | 0.5<br>0.5 | dB<br>dB<br>dB               | 300 Hz<br>3400 Hz                                                                                                  |

| 15 | Intermodulation Distortion products at VX and 2 W                        | IMD  |                      | 75                     |            | dB                           | I <sub>LOOP</sub> = 25-60 mA<br>F1 = 1kHz at -6 dBm<br>F2 = 800Hz at -6 dBm<br>Total signal power =<br>-3 dBm      |

| 16 | Distortion at VX due to near end<br>echo<br>(300 Hz - 3400 Hz bandwidth) |      |                      | 75                     |            | dB                           | $I_{LOOP}$ = 25-60 mA<br>F1 = 1 kHz at -6 dBm<br>F2 = 800 Hz at -6 dBm<br>Total signal power =<br>-3 dBm           |

| 17 | Common Mode Rejection at VX                                              | CMR  |                      | 50                     |            | dB                           | Test circuit (Figure 10)<br>1-100 Hz Note 4                                                                        |

| 18 | Common Mode overload                                                     | CML  |                      | 100V                   |            | V <sub>pk-pk</sub>           | Test circuit (Figure 10)<br>1-100 Hz Note 4                                                                        |

‡ Electrical Characteristics are over Recommended Operating Conditions unless otherwise stated.

‡ Typical figures are at 25°C with nominal + 5V supplies and are for design aid only.

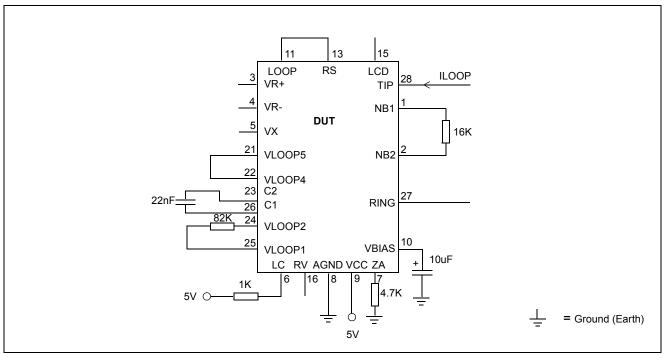

Figure 6 - Test Circuit 1

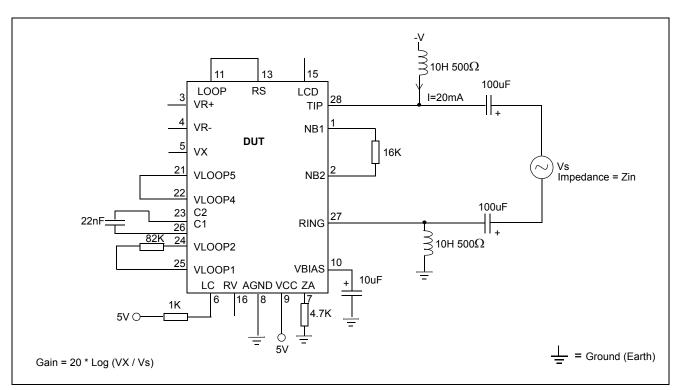

Figure 7 - Test Circuit 2

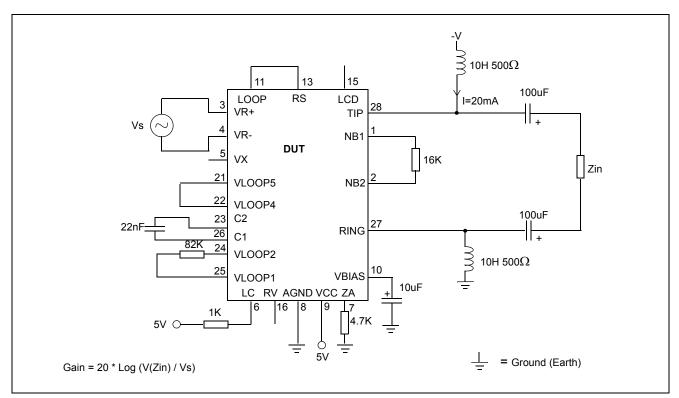

Figure 8 - Test Circuit 3

Figure 9 - Test Circuit 4

Figure 12 - Mechanical Data for 28 Pin DIL Hybrid

Figure 13 - Mechanical Data for 28 Pin Surface Mount Hybrid

Figure 14 - Recommended Footprint for 28 Pin Surface Mount Hybrid

# For more information about all Zarlink products visit our Web Site at

#### www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE