#### DATA SHEET

#### MAY 1999 Revision 2.1

# LXP710

## HDSL Framer/Mapper for 1168 kbps Applications

#### **General Description**

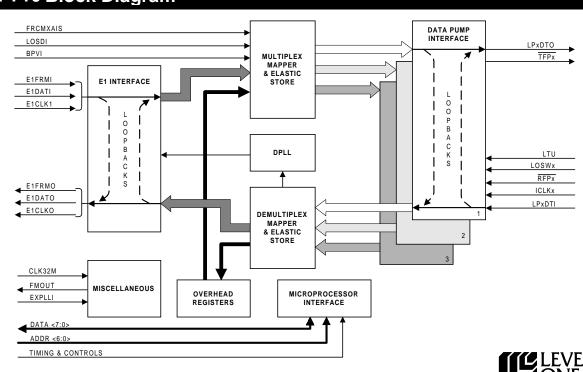

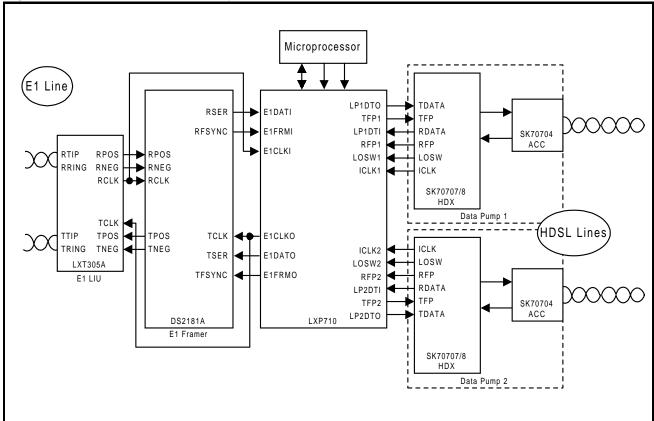

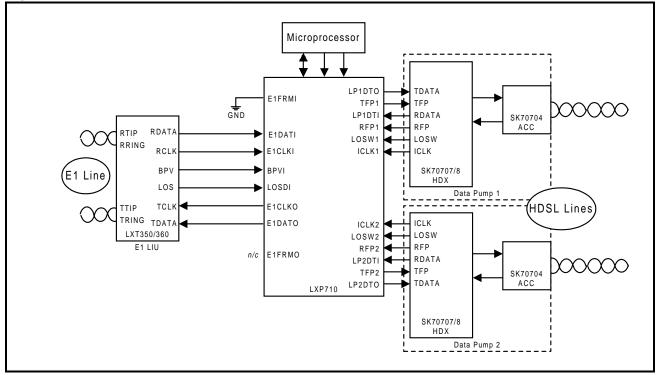

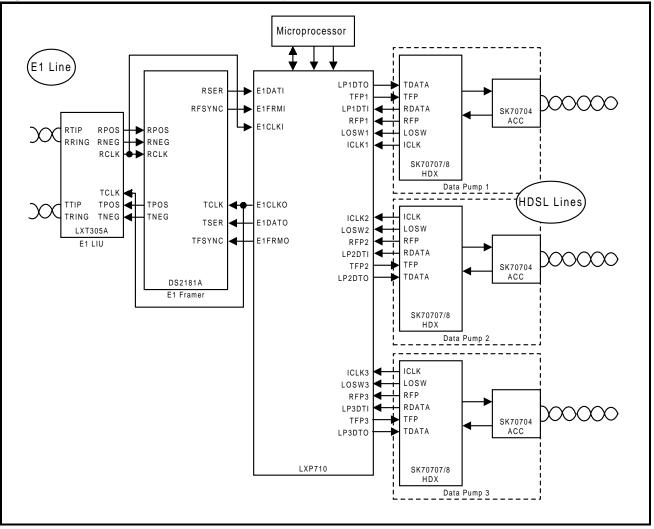

The LXP710 is a complete HDSL framer/mapper that multiplexes and demultiplexes a framed or unframed 2.048 Mbps E1 data stream onto two 1168 kbps HDSL lines. The LXP710 also supports point-to-point and point-to-multipoint fractional E1 applications with 1, 2 or 3 HDSL lines.

The LXP710 interfaces directly with the Level One SK70704/ SK70707 1168 kbps HDSL data pump and industry standard E1 Framers or Line Interface ICs. The framer/mapper is controlled and monitored by an external microprocessor using an 8-bit Intel or Motorola compatible parallel interface. The framer/mapper provides both programmable and 6ms interrupts synchronized to the HDSL frame rate.

The LXP710 provides fully programmable mapping between the E1 and HDSL interfaces on one or more loops. The LXP710 provides support for system performance monitoring with internal CRC, FEBE and BPV error counters and the capability to inject these errors.

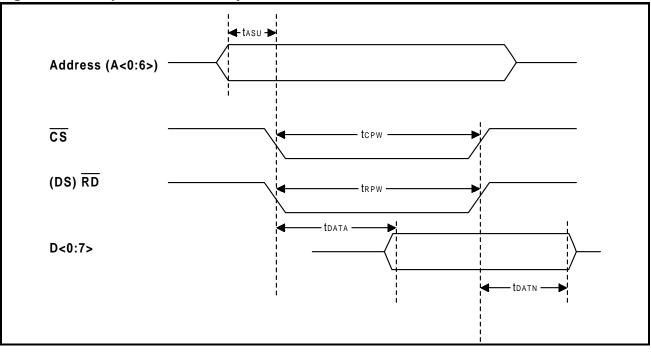

The framer/mapper automatically controls the synchronization between the HDSL loop timing and the E1 payload timing using a digital PLL for E1 timing recovery and a transmitter stuffing control circuit.

#### Features

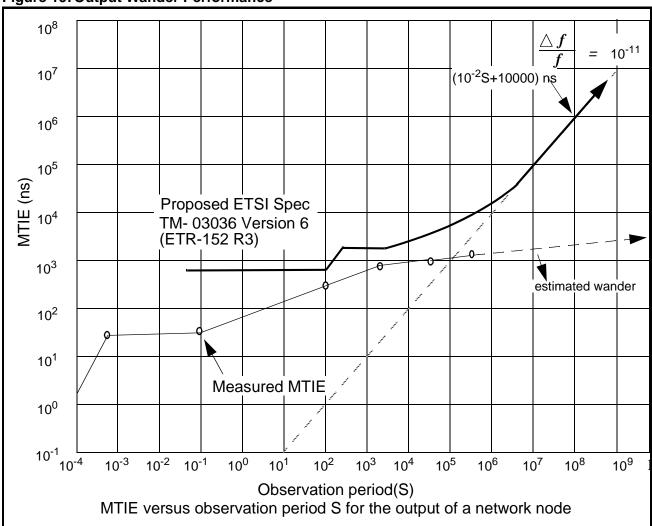

- Compliant with ETSI ETR-152 requirements

- Interfaces with 1, 2 or 3 Level One HDSL Data Pumps and industry standard E1 Framers or Line Interface ICs

- 8-bit, Intel or Motorola compatible parallel processor interface with programmable and 6ms interrupts

- E1 to HDSL Loop Multiplexing/Demultiplexing

- · Programmable time slot mapping

- Accepts framed or unframed E1 data

- IDLE Code Insertion provides channel blocking in mux and demux directions

- DS0 Channel Grouping

- Loopbacks toward E1 and HDSL interfaces

- Diagnostics/Performance Monitoring

- QRSS Pattern Generation and Detection

- CRC, BPV and FEBE counters and error generators

- User definable 10 kbps overhead channel

- HDSL Overhead Management

- DPLL for E1 Timing Recovery

- HDSL Transmit Stuffing Control

Refer to www.level1.com for most current information.

an Intel company

### LXP710 Block Diagram

### PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS

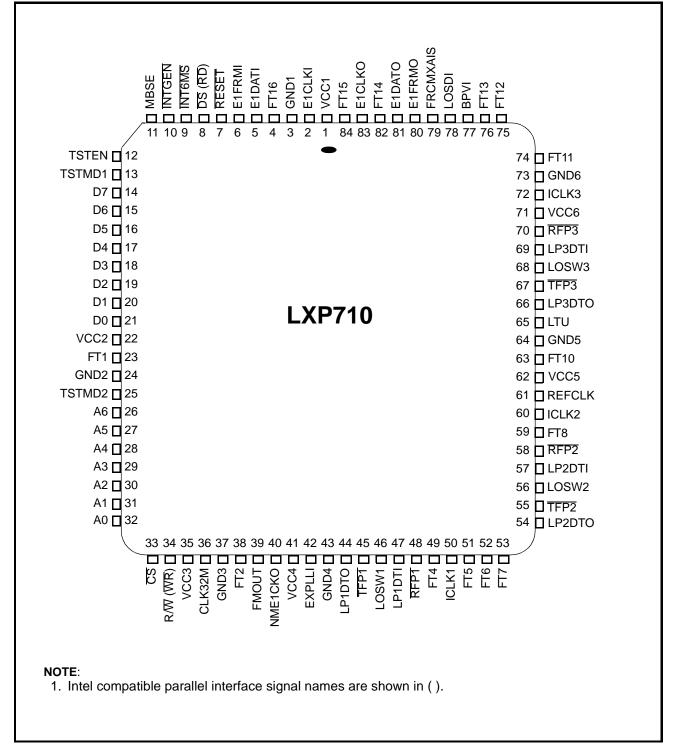

#### Figure 1: LXP710 Pinout Diagram

|                   | Pin Descriptions           |                  |                                                                                                                                                                                                                                                               |  |

|-------------------|----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin               | Symbol                     | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                                   |  |

| 1                 | VCC1                       | -                | +5 Volt Supply.                                                                                                                                                                                                                                               |  |

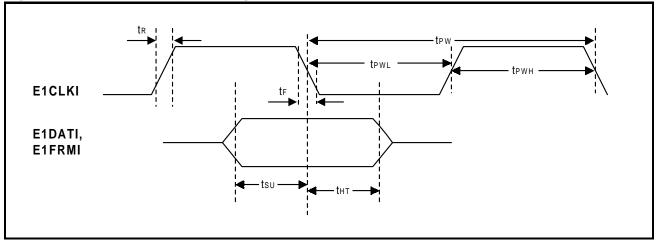

| 2                 | E1CLKI                     | DI               | <b>E1 Clock Input</b> . This input clock samples mux E1 data and frame mark inputs. The sampling edge of this clock can be inverted by the INVMCK control bit. The nominal frequency of this clock is 2.048 MHz.                                              |  |

| 3                 | GND1                       | -                | Ground.                                                                                                                                                                                                                                                       |  |

| 4                 | FT16                       | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                              |  |

| 5                 | E1DATI                     | DI               | E1 Data Input. This input accepts mux E1 data in serial NRZ format.                                                                                                                                                                                           |  |

| 6                 | E1FRMI                     | DI               | <b>E1 Frame Sync Input</b> . This input identifies the first frame bit position of the mux E1 data. The signal must be High for one E1CLKI period.                                                                                                            |  |

| 7                 | RESET                      | DI               | <b>Reset</b> (Active Low). Resets the internal circuits and control registers to their default state when driven Low.                                                                                                                                         |  |

| 8                 | DS (RD)                    | DI               | <b>Data Strobe or Read Enable</b> . In Intel mode, enables a read cycle when Low. In Motorola mode, this signal functions as the data strobe. The LXP710 drives the D<7:0> bus with the contents of the addressed register when RD and CS are Low.            |  |

| 9                 | INT6MS                     | DO               | <b>6ms Interrupt</b> . Can be enabled to go Low for a Mux EOC/Overhead bits Ready, a Demux EOC/Overhead bits Ready, or a Triple-Echo Message Compare.                                                                                                         |  |

| 10                | INTGEN                     | DO               | <b>General Purpose Interrupt</b> (Active Low). This output can be enabled to go Low when one or more of the internal general purpose interrupt conditions have been met.                                                                                      |  |

| 11                | MBSE                       | DI               | <b>Motorola Bus Enable</b> . When MBSE is High, the LXP710 is configured for Motorola bus mode. When MBSE is Low, the LXP710 is configured for Intel mode. This enable signal configures the WR input to function as R/W and the RD signal to function as DS. |  |

| 12                | TSTEN                      | DI               | <b>Test Mode Enable</b> . This input should be tied Low to disable factory test modes.                                                                                                                                                                        |  |

| 13                | TSTMD1                     | DI               | <b>Test Mode 1</b> . This input should be tied Low and is reserved for factory test modes.                                                                                                                                                                    |  |

| 14                | D7                         | DI/O             |                                                                                                                                                                                                                                                               |  |

| 15                | D6                         | DI/O             |                                                                                                                                                                                                                                                               |  |

| 16                | D5                         | DI/O             |                                                                                                                                                                                                                                                               |  |

| 17                | D4                         | DI/O             | <b>Microprocessor Data Bus</b> . This 8-bit, bidirectional, tri-state bus is the general                                                                                                                                                                      |  |

| 18                | D3                         | DI/O             | purpose data path that can transfer data between the LXP710 and the microprocessor.                                                                                                                                                                           |  |

| 19                | D2                         | DI/O             |                                                                                                                                                                                                                                                               |  |

| 20                | D1                         | DI/O             |                                                                                                                                                                                                                                                               |  |

| 21                | D0                         | DI/O             |                                                                                                                                                                                                                                                               |  |

| 1. $DI = digital$ | ital input; DO = digital o | output, DI/O     | = digital input and output; AI = analog input, AO = analog output.                                                                                                                                                                                            |  |

Table 1:

Pin Descriptions

| Table 1:          | Pin Descriptions – continued |                  |                                                                                                                                                                                                                                                  |  |  |

|-------------------|------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin               | Symbol                       | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                      |  |  |

| 22                | VCC2                         | -                | +5 Volt Supply.                                                                                                                                                                                                                                  |  |  |

| 23                | FT1                          | -                | Factory Test. This pin should not be connected and is reserved for factory test                                                                                                                                                                  |  |  |

| 24                | GND2                         | -                | Ground.                                                                                                                                                                                                                                          |  |  |

| 25                | TSTMD2                       | DI               | <b>Test Mode 2</b> . This Input should be tied Low and is reserved for factory test modes.                                                                                                                                                       |  |  |

| 26                | A6                           | DI               |                                                                                                                                                                                                                                                  |  |  |

| 27                | A5                           | DI               |                                                                                                                                                                                                                                                  |  |  |

| 28                | A4                           | DI               |                                                                                                                                                                                                                                                  |  |  |

| 29                | A3                           | DI               | <b>Microprocessor Address Bus</b> . This 7-bit input bus is used by the microprocessor to select LXP710 registers for read/write data transfer.                                                                                                  |  |  |

| 30                | A2                           | DI               | inicroprocessor to select LXP / to registers for read/write data transfer.                                                                                                                                                                       |  |  |

| 31                | A1                           | DI               |                                                                                                                                                                                                                                                  |  |  |

| 32                | A0                           | DI               |                                                                                                                                                                                                                                                  |  |  |

| 33                | CS                           | DI               | <b>Chip Select</b> (Active Low). This input must be Low to enable read or write access to the LXP710.                                                                                                                                            |  |  |

| 34                | R/W (WR)                     | DI               | <b>Read/Write or Write Enable</b> . In Intel mode, enables a write cycle when Low. In Motorola mode, this signal functions as the Read/Write control. The D $<7:0>$ bus contents are latched into the addressed register when WR and CS are Low. |  |  |

| 35                | VCC3                         | -                | +5 Volt Supply.                                                                                                                                                                                                                                  |  |  |

| 36                | CLK32M                       | DI               | <b>External Reference Clock</b> . Requires a 32.768 MHz ±50 ppm input for internal PLL.                                                                                                                                                          |  |  |

| 37                | GND3                         | -                | Ground.                                                                                                                                                                                                                                          |  |  |

| 38                | FT2                          | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                 |  |  |

| 39                | FMOUT                        | DO               | <b>Frame Pulse Output</b> . This output pin provides an 6 ms, active High, frame pulse selected from one of RFPI, RFP2, or RFP3 for an external PLL circuit.                                                                                     |  |  |

| 40                | NME1CKO                      | DO               | <b>External Reference Clock.</b> 2.048 Mhz reference for E1 framer and LIU when E1 input has no clock.                                                                                                                                           |  |  |

| 41                | VCC4                         | -                | +5 Volt Supply.                                                                                                                                                                                                                                  |  |  |

| 42                | EXPLLI                       | DI               | <b>External PLL Input</b> . This input clock pin accepts a 2.048 MHz phase locked clock from an external PLL circuit.                                                                                                                            |  |  |

| 43                | GND4                         | -                | Ground.                                                                                                                                                                                                                                          |  |  |

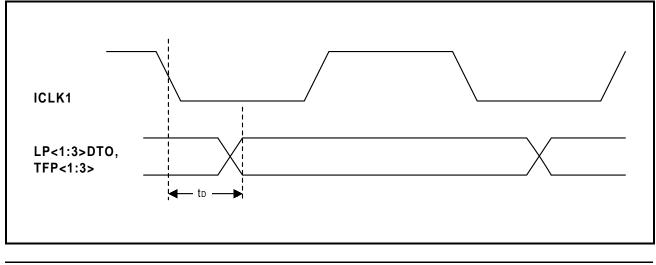

| 44                | LP1DTO                       | DO               | <b>Loop 1 Data Output</b> . This pin outputs mux data, which is updated on falling edge of ICLK1, to the Loop 1 transceiver. The nominal bit rate of this signal is 1168 kbps.                                                                   |  |  |

| 1. $DI = digital$ | ital input; DO = digital     | output, DI/O     | = digital input and output; AI = analog input, AO = analog output.                                                                                                                                                                               |  |  |

#### Table 1: Pin Descriptions – continued

| Pin               | Symbol                     | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                           |

|-------------------|----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45                | TFPI                       | DO               | <b>Loop 1 Transmit Frame Pulse</b> (Active Low). A Low level on this signal indicates the last bit position of each mux HDSL frame for Loop 1. The position of this pulse is at bit 7006 when no stuffing is added, or bit 7010 when stuffing is added. This pulse nominally occurs every 6 milliseconds $\pm 1/584$ milliseconds.    |

| 46                | LOSW1                      | DI               | <b>Loop 1 Loss of Sync Word Status</b> . This pin inputs the LOSW status from the Loop 1 transceiver. This pin provides hardware override for the demux TMGSRC control bits, disables Loop 1 error counters, and can force demux E1 Partial-AIS. (If EXTDXAIS bit enabled). It has an internal pull up resistor, and is active High.  |

| 47                | LP1DTI                     | DI               | <b>Loop 1 Data In</b> . This signal inputs demux data, which is sampled on rising edge of ICLK1, from the Loop 1 transceiver. The nominal bit rate of this signal is 1168 kbps.                                                                                                                                                       |

| 48                | RFPI                       | DI               | <b>Loop 1 Receive Frame Pulse</b> (Active Low). A Low level on this signal indicates the last bit position of each demux HDSL frame for Loop 1. The position of this pulse is at bit 7006 when no stuffing is added, or bit 7010 when stuffing is added. This pulse nominally occurs every 6 milliseconds $\pm 1/584$ milliseconds.   |

| 49                | FT4                        | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |

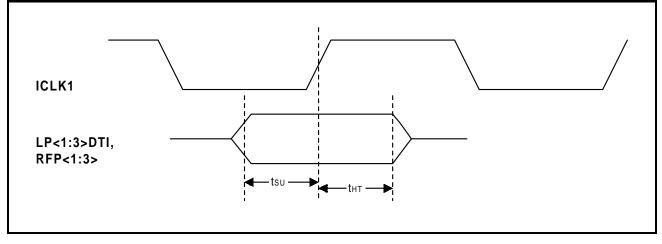

| 50                | ICLK1                      | DI               | <b>Loop 1 Transceiver Interface Clock</b> . This clock input synchronizes the transfer of HDSL data and frame mark to/from the Loop 1 transceiver. This clock samples the LP1DTI and RFPT inputs on rising edge, and outputs the LP1DTO and TFPT outputs on the falling edge. The nominal frequency of this clock signal is 1168 kHz. |

| 51                | FT5                        | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |

| 52                | FT6                        | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |

| 53                | FT7                        | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |

| 54                | LP2DTO                     | DO               | <b>Loop 2 Data Output</b> . This pin outputs mux data, which is updated on falling edge of ICLK2, to the Loop 2 transceiver. The nominal bit rate of this signal is 1168 kbps.                                                                                                                                                        |

| 55                | TFP2                       | DO               | <b>Loop 2 Transmit Frame Pulse</b> (Active Low). A Low level on this signal indicates the last bit position of each mux HDSL frame for Loop 2. This position of this pulse is at bit 7006 when no stuffing is added, or bit 7010 when stuffing is added. This pulse nominally occurs every 6 milliseconds $\pm$ 1/584 milliseconds.   |

| 56                | LOSW2                      | DI               | <b>Loop 2 Loss of Sync Word Status</b> . This pin inputs the LOSW status from the Loop 2 transceiver. This pin provides hardware override for the demux TMGSRC control bits, disables Loop 2 error counters, and can demux E1 Partial-AIS. It has an internal pull up resistor.                                                       |

| 1. $DI = digital$ | ital input; DO = digital o | output, DI/O     | = digital input and output; AI = analog input, AO = analog output.                                                                                                                                                                                                                                                                    |

Table 1:

Pin Descriptions – continued

| Table 1:     | Pin Descriptions – continued |                  |                                                                                                                                                                                                                                                                                                                                       |  |  |

|--------------|------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin          | Symbol                       | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                           |  |  |

| 57           | LP2DTI                       | DI               | <b>Loop 2 Data In</b> . This signal inputs demux data, which is sampled on rising edge of ICLK1, from the Loop 2 transceiver. The nominal bit rate of this signal is 1168 kbps.                                                                                                                                                       |  |  |

| 58           | RFP2                         | DI               | <b>Loop 2 Receive Frame Pulse</b> (Active Low). A Low level on this signal indicates the last bit position of each demux HDSL frame for Loop 2. The position of this pulse is at bit 7006 when no stuffing is added, or bit 7010 when stuffing is added. This pulse nominally occurs every 6 milliseconds $\pm 1/584$ milliseconds.   |  |  |

| 59           | FT8                          | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |  |  |

| 60           | ICLK2                        | DI               | <b>Loop 2 Transceiver Interface Clock</b> . This clock input synchronizes the transfer of HDSL data and frame mark to/from the Loop 2 transceiver. This clock samples the LP2DTI and RFP2 inputs on rising edge, and outputs the LP2DTO and TFP2 outputs on the falling edge. The nominal frequency of this clock signal is 1168 kHz. |  |  |

| 61           | REFCLK                       | DI               | <b>Reference Clock.</b> Provides 18.688 MHz reference clock for HDSL Loopback test.                                                                                                                                                                                                                                                   |  |  |

| 62           | VCC5                         | -                | +5 Volt Supply.                                                                                                                                                                                                                                                                                                                       |  |  |

| 63           | FT10                         | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |  |  |

| 64           | GND5                         | -                | Ground.                                                                                                                                                                                                                                                                                                                               |  |  |

| 65           | LTU                          | DI               | <b>LTU Mode Enable</b> . When this input is High, the LTU mode is selected otherwise, the NTU mode is selected.                                                                                                                                                                                                                       |  |  |

| 66           | LP3DTO                       | DO               | <b>Loop 3 Data Output</b> . This pin outputs mux data, which is updated on falling edge of ICLK3, to the Loop 3 transceiver. The nominal bit rate of this signal is 1168 kbps.                                                                                                                                                        |  |  |

| 67           | TFP3                         | DO               | <b>Loop 3 Transmit Frame Pulse</b> (Active Low). A Low level on this signal indicates the last bit position of each mux HDSL frame for Loop 3. This position of this pulse is at bit 7006 when no stuffing is added, or bit 7010 when stuffing is added. This pulse nominally occurs every 6 milliseconds $\pm 1/584$ milliseconds.   |  |  |

| 68           | LOSW3                        | DI               | <b>Loop 3 Loss of Sync Word Status</b> . This pin inputs the LOSW status from the Loop 3 transceiver. This pin provides hardware override for the demux TMGSRC control bits, disables Loop 3 error counters, and can force demux E1 Partial-AIS. It has an internal pull up resistor.                                                 |  |  |

| 69           | LP3DTI                       | DI               | <b>Loop 3 Data In</b> . This signal inputs demux data, which is sampled on rising edge of ICLK1, from the Loop 3 transceiver. The nominal bit rate of this signal is 1168 kbps.                                                                                                                                                       |  |  |

| 1. DI = digi | tal input; DO = digital o    | output, DI/O     | = digital input and output; AI = analog input, AO = analog output.                                                                                                                                                                                                                                                                    |  |  |

#### Table 1: Pin Descriptions – continued

| Pin           | Symbol                   | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                           |

|---------------|--------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70            | RFP3                     | DI               | <b>Loop 3 Receive Frame Pulse</b> (Active Low). A Low level on this signal indicates the last bit position of each demux HDSL frame for Loop 3. The position of this pulse is at bit 7006 when no stuffing is added, or bit 7010 when stuffing is added. This pulse nominally occurs every 6 milliseconds $\pm 1/584$ milliseconds.   |

| 71            | VCC6                     | -                | +5 Volt Supply.                                                                                                                                                                                                                                                                                                                       |

| 72            | ICLK3                    | DI               | <b>Loop 3 Transceiver Interface Clock</b> . This clock input synchronizes the transfer of HDSL data and frame mark to/from the Loop 3 transceiver. This clock samples the LP3DTI and RFP3 inputs on rising edge, and outputs the LP3DTO and TFP3 outputs on the falling edge. The nominal frequency of this clock signal is 1168 kHz. |

| 73            | GND6                     | -                | Ground.                                                                                                                                                                                                                                                                                                                               |

| 74            | FT11                     | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |

| 75            | FT12                     | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |

| 76            | FT13                     | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |

| 77            | BPVI                     | DI               | <b>BPV Indicator Input</b> . This pin provides hardware access to the mux HDSL BPV overhead bit on each loop. An active High pulse on this pin activates the BPV indicator bit on each loop in the next frame. This signal is ORed with separate software control bits for each loop that can also activate the BPV bits.             |

| 78            | LOSDI                    | DI               | <b>Loss of E1 Signal</b> . This pin provides hardware access to the mux HDSL LOSD overhead bit on each loop. An active High pulse on this pin activates the LOSD indicator bit on all loops in the next frame. This signal is ORed with separate software control bits for each loop that can also activate the LOSD bits.            |

| 79            | FRCMXAIS                 | DI               | <b>Force Mux AIS</b> . When enabled by the EXTMXAIS control bit, a High on this bit forces the mux E1 to insert AIS.                                                                                                                                                                                                                  |

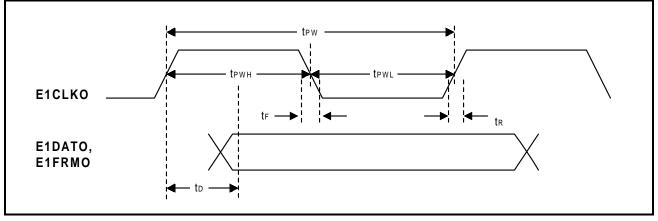

| 80            | E1FRMO                   | DO               | <b>E1 Frame Sync Output</b> . This output identifies the first frame bit position of the demux E1 data. The signal must be High for one E1CLKO period. The nominal frequency of this signal is 8 kHz.                                                                                                                                 |

| 81            | E1DATO                   | DO               | <b>E1 Data Output</b> . This output signal provides the data to the external E1 framer.                                                                                                                                                                                                                                               |

| 82            | FT14                     | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |

| 83            | E1CLKO                   | DO               | <b>E1 Clock Output</b> . This output is used to synchronize the transfer of E1 frame mark and data. The output edge of this clock can be inverted by the INVDXCK control bit. The nominal frequency of this clock is 2.048 MHz.                                                                                                       |

| 84            | FT15                     | -                | Factory Test. This pin should not be connected and is reserved for factory test.                                                                                                                                                                                                                                                      |

| 1. $DI = dig$ | ital input; DO = digital | output, DI/O     | = digital input and output; AI = analog input, AO = analog output.                                                                                                                                                                                                                                                                    |

Table 1:

Pin Descriptions – continued

### **FUNCTIONAL DESCRIPTION**

The framer is separated into the following blocks of logic: the multiplexer, demultiplexer, microprocessor interface, E1 interface, and HDSL interface. The following subsections describe each logic function.

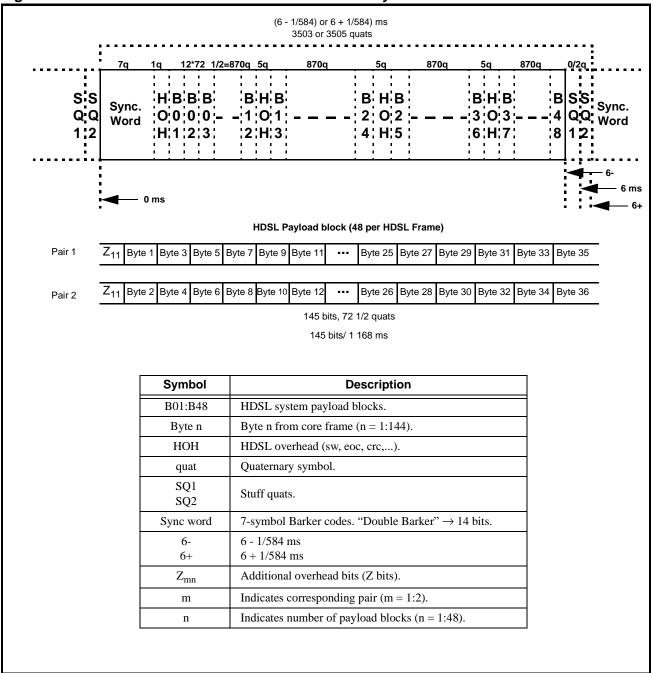

The ETSI Technical Report ETR 152 will yield a better understanding of the ETSI HDSL system. Framer related sections include, but are not limited to, the HDSL core specifications, frame structure and Application specific requirements. It is beyond the scope of this document to completely explain all of the details in ETR 152, but some of the directly related HFMA functionality will be covered.

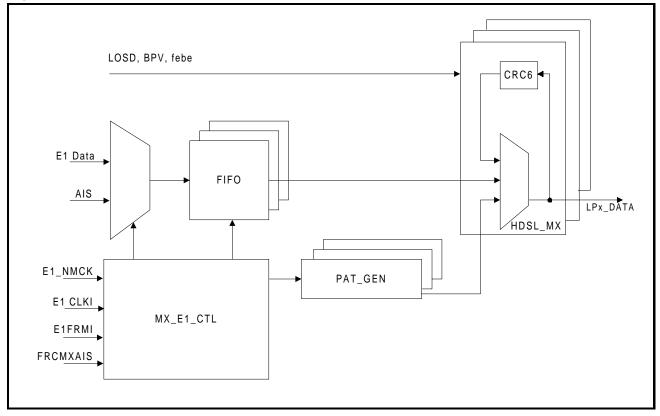

## Multiplexer (MX)

The function of the MX block is to split the E1 payload into 2 or 3 parts and then multiplex each part with HDSL overhead (HOH) bits, including CRC6, eoc and Z-bits to be passed on to the individual HDSL data pumps. The MX block controls stuffing into the HDSL data stream. The MX block configuration registers are programmed by the microprocessor. The microprocessor also sets the eoc and Z-bits. Individual loop testing is supported by generating test and error patterns in the MX block.

Sync word generation and data scrambling, as defined by ETR 152, are done by the SK70707 digital transceiver, and therefore are not performed by the HFMA.

Figure 2 shows a simplified logic block of the MX process. The MX E1 CTL block uses the selected E1 clock to load the E1 data from the E1 Interface into the FIFOs. The E1 clock may be either the derived clock from the E1 data stream, E1CLKI, or an internal nominal clock (E1 NMCK). The MXE1CTL register (see Table 3 on page 17) controls which E1 clock is selected as well as selecting whether E1 data or AIS (all 1s) is clocked into the FIFOs. The NMFMEN bit of the MXE1CTL register, when 0, selects the E1FRMI pin, otherwise an internally generated frame pulse is used. The Loop *n* Time Slot Control Byte registers, LnTSCTLx, listed in Tables 10 through 21, control which time slots of the E1 data stream are assigned to which HDSL loop. The values loaded in these registers become valid only after setting the LDTABLE bit in the TSCTL register (see Table 9 on page 23). The MX Process HDSL loop data is routed to the HDSL Interface.

HDSL loops 2 and 3 are aligned to loop 1. The HDSL\_MX block multiplexes the HOH bits with the payload data as shown in Table 115 on page 56. The HOH bits consist of 19 indicator bits, 13 eoc bits, 14-bit sync word, and 4 stuffing bits (when necessary). Each loop has its own multiplexer. A CRC6 is calculated per frame for each loop excluding the CRC bits, 14-bit sync word and the 4 stuffing bits. The result is stored and transmitted in the following frame.

The other indicator bits are febe, losd, bpv, ps1, ps2, hrp, rrbe, rcbe, rega, rta, indc/indr and uib. The febe bit is generated from the DX process and is sent out to the far end HDSL device to indicate that a CRC error occurred in the local received data. The losd bit is from the LOSDI pin for loss of signal at the E1 interface. The bpv bit is from the BPVI pin for a bipolar violation in the E1 data. The bits ps1 and ps2 are Power Status bits from NTU (HTU-R) -> LTU (HTU-C) only. The hrp is the HDSL Repeater Present bit (repeater only). The rrbe, rcbe and rega bits are used for the regenerator/repeater status. The rta is for the remote (NTU) alarm. The 2 uib bits are the Unspecified Indicator Bits.

Several bits can be set for error injection testing on a per loop basis. The outgoing febe and bpv bits can be injected as single bit errors. The CRC can be set for continuous error generation. Registers LnOHCTL, listed in Tables 6 through 8, control this activity.

The transmitted Z-bits and eoc bits are set by the microprocessor interface. The Z-bit transmit registers are MXL1Zx in Tables 40 through 63, MXL2Zx in Tables 64 through 87, MXL3Zx in Tables 88 through 111. The eoc transmit registers are MXL1EOC in Tables 46 and 47, MXL2EOC in Tables 70 and 71, MXL3EOC in Tables 94 and 95. In general applications, the eoc is used by the HTU-C to transmit a command continuously to the HTU-R unit until the HTU-R echoes the same command back to the HTU-C three times. ETR 152 recommends some common commands that might be used, but it is up to each vendor to specify detailed implementation. The only defined Z-bits are the first three used for loop identification. Other Z-bits are reserved for vendor use.

The PAT\_GEN block generates a QRSS pattern and can be set to generate an error in that pattern. The QRSS is put in place of the E1 data for testing purposes. The QRSS signal is on a per loop basis and is controlled by the PATCTL register as described in Table 23 on page 27.

#### Figure 2: MX Process

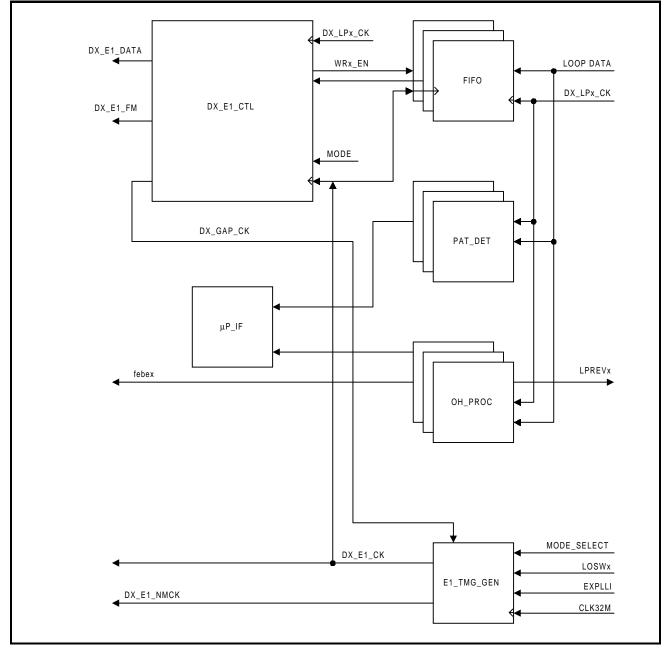

## Demultiplexer (DX)

The DX performs the reverse function of the MX by demultiplexing the HDSL bits into HOH bits and payload data and then combining the 2/3 HDSL payloads into an E1 payload. The HOH bits, eoc and Z-bits, are separated out from the payload, stored into registers for the microprocessor to read. The DX checks the received CRC6 against the data and sets a flag in case of an error condition. The DX also provides the E1 clock based upon an internal PLL.

Figure 3 shows a simplified logic diagram of the DX Process. Each individual loop data is clocked into a separate FIFO. The DX\_E1\_CTL block controls the Write Enable to the FIFOs by blocking the HOH bits from being loaded into the FIFOs. The DX\_E1\_CTL selects from which FIFO to load data. The ordering of the time slots is based on the values programmed into the LnTSCTLx registers as described in Tables 10 through 21. The values loaded in these registers become valid only after setting the LDTABLE bit in the TSCTL register, Table 9. The data is passed through a mux to DX\_E1\_DATA. The other selection of the mux is AIS. The use of AIS for the

outgoing E1 data is controlled by the 4 LSBs of DXE1CTL register (see Table 4).

The DX\_E1\_CTL block generates a 1168KHz gapped clock as a reference for the E1\_TMG\_GEN block. The DX\_E1\_CTL uses the DX\_E1\_CK from the E1\_TMG\_GEN to track the current position in the outgoing E1 data stream and to generate the DX\_E1\_FM, E1 framing pulse.

The E1\_TMG\_GEN uses the DX\_GAP\_CK as the reference for the DX\_E1\_CK. The DX\_E1\_NMCK is a nominal E1 clock used for E1 AIS, E1 loopback and as the source for the NME1CKO pin to sync an E1 framer when it has no clock.

The OH\_PROC, overhead processor, looks for all of the HOH bits in the incoming HDSL frames. There is a OH\_PROC block for each HDSL loop. The received Z-bits, eoc bits and overhead bits are latched into their respective registers in the UP\_IF. A CRC is calculated on the received data and the result is stored for comparison against the CRC bits in the following frame. A CRC error generates the febe bit to the MX Process. The OH\_PROC

increments the associated error counters for CRC, febe and bpv. These counters are in the  $\mu$ P\_IF section. The sync word bits and stuffing bits are discarded.

The OH\_PROC compares the loop ID received from each loop and generates a report to the  $\mu$ P\_IF, LPRSTAT register in Table 29, and sends the loop correction bits to the HDSL Interface.

The PAT\_DET block, one per loop, generates a Pattern Sync Lost indication bit, PATLOS bit in PATSTAT register (see Table 25 on page 28), when the sync is not present. The PAT\_DET increments the appropriate LnPATECL (see Tables 61, 85, and 110) counter for each instance of a QRSS pattern bit failure. Overflows of these counters are indicated in PATSTAT register OVERFLOW bits (see Table 25). Overflows may also be set to trigger an interrupt via the  $\mu$ P\_IF registers GENINTEN and GENINTSTAT (see Tables 30 and 31).

#### Figure 3: DX Process

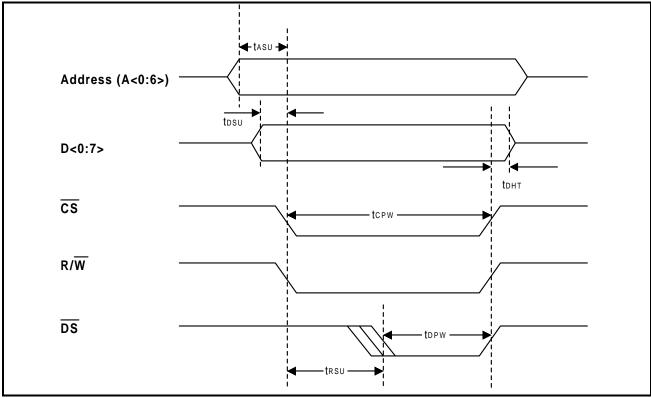

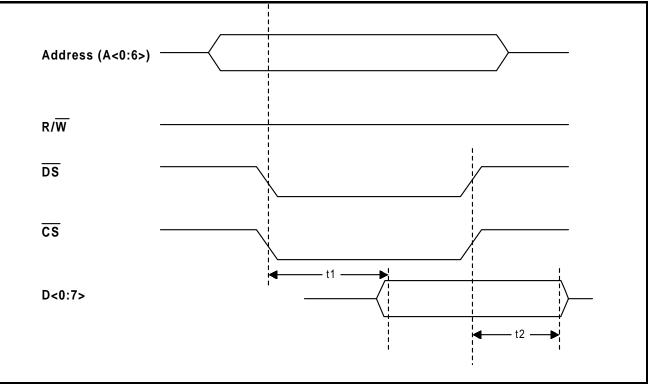

## Microprocessor Interface

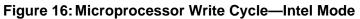

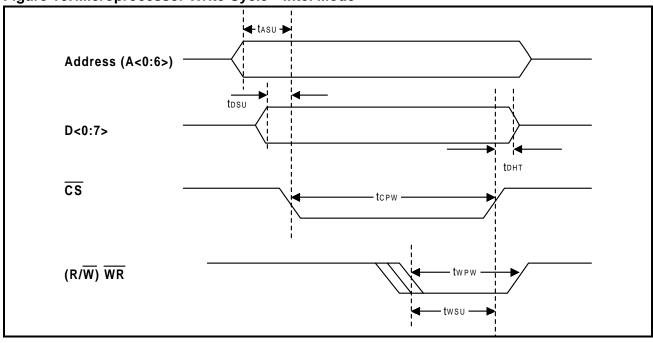

The microprocessor interface provides access to all of LXP710's registers and routes the interrupt signals to external pins. The MBSE pin configures the LXP710 microprocessor interface for either the Intel or Motorola bus timing. The LXP710 registers are described in Tables 2 through 114.

In the Motorola Mode (MBSE pin set High), the data bus D<0:7>, address bus A<0:6>, CS, DS and R/W are used to read or write to the LXP710's internal registers.

In the Intel Mode (MBSE pin set Low), the data bus D<0:7>, address bus A<0:6>, CS, RD and WR are used to read or write to the LXP710's internal registers. The board design must include a latch, using ALE, for the address from the Intel multiplexed AD bus. This latch could be shared with the data pumps and other devices on board that have non-multiplexed address pins.

To optimize code execution, Two external interrupt pins, INTGEN and INT6MS, are provided. The INTGEN pin is for general purpose interrupts as listed in the GENINTEN and GENINTSTAT registers in Tables 30 and 31. The INDCR bits in the IND\_3EOCINTEN and IND\_3EOCINTSTAT registers in Tables 34 and 35 are also tied to the INTGEN pin.

The INT6MS pin is for the 6 ms timing related functions such as when the MX eoc and Z-bits are ready to be loaded to transmit and when the DX eoc and Z-bits have been received. Additionally the EOC Triple-Echo Message Compare Detected bits in the IND\_3EOCINTEN and IND\_3EOCINTSTAT registers (see Tables 34 and 35) are also tied to the INT6MS pin. This feature reduces software processing needed to detect that a message has been received three times.

## E1 Interface

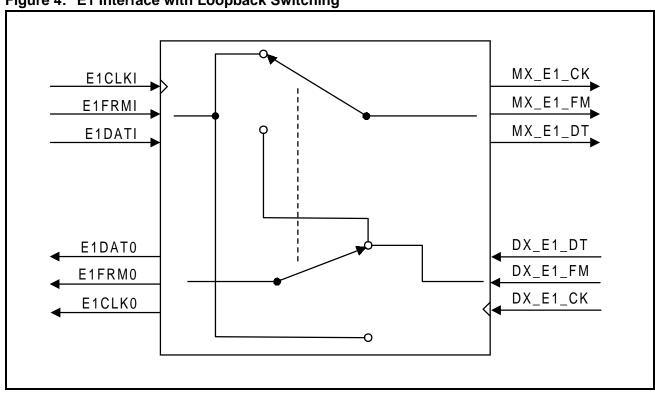

The E1 interface connects to an E1 framer device. As shown in Figure 4, the incoming E1 data is routed to the MX and is controlled by signals from the E1 framer. The E1 interface takes E1 data from the DX and provides control signals for the E1 framer. Two loopbacks are available. The first loopback is for E1 input data to E1 output data. The other is the loopback for the internal DX E1 payload back to the MX block. As shown in the diagram, the two loopbacks are tied together. The loopback is achieved by setting the E1LB bit in the DXE1CTL register as described in Table 4.

Figure 4: E1 Interface with Loopback Switching

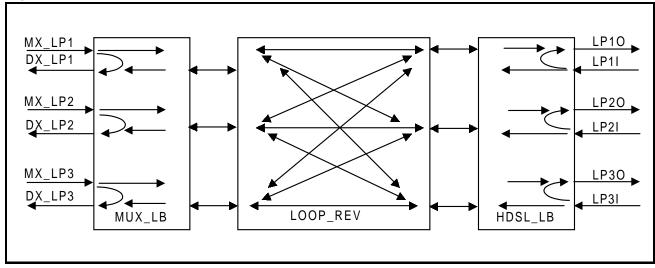

## HDSL Interface

The HDSL interface block connects the HDSL loops to the MX and DX blocks. The block can provide loop switching, as well as loopback for each external incoming loop and a loopback for the internal MX signals to the DX block. Figure 5 shows the possible signal routings. When the

HDSLLB bit in the LPCTL register (see Table 5) is set, all HDSL Interface loopbacks are set. The LOOP\_REV block shows how any loop swap combination can be set by the DX Process in Figure 3. The status of the loop connections can be monitored by reading the LPREV bits in the LPRSTAT register. See Table 29.

#### Figure 5: HDSL Interface

### **REGISTER DEFINITIONS**

Table 2 provides a summary of the LXP710 registers. Tables 3 through 114 provide detailed descriptions of each of the LXP710 register bits. The specified default values are set when the LXP710 is reset by pin 7.

| Here           |                    |               |      |                                             |  |

|----------------|--------------------|---------------|------|---------------------------------------------|--|

| Hex<br>Address | Decimal<br>Address | Symbol        | Туре | Description                                 |  |

| 00             | 0                  | MXE1CTL       | R/W  | Mux E1 control register                     |  |

| 01             | 1                  | DXE1CTL       | R/W  | Demux E1 control register                   |  |

| 02             | 2                  | LPCTL         | R/W  | HDSL loop control register                  |  |

| 03             | 3                  | L10HCTL       | R/W  | HDSL Loop 1 overhead control register       |  |

| 04             | 4                  | L2OHCTL       | R/W  | HDSL Loop 2 overhead control register       |  |

| 05             | 5                  | L3OHCTL       | R/W  | HDSL Loop 3 overhead control register       |  |

| 06             | 6                  | TSCTL         | R/W  | Time slot grouping table control register   |  |

| 07             | 7                  | L1TSCTL1      | R/W  | Loop 1 time slot control byte 1             |  |

| 08             | 8                  | L1TSCTL2      | R/W  | Loop 1 time slot control byte 2             |  |

| 09             | 9                  | L1TSCTL3      | R/W  | Loop 1 time slot control byte 3             |  |

| 0A             | 10                 | L1TSCTL4      | R/W  | Loop 1 time slot control byte 4             |  |

| 0B             | 11                 | L2TSCTL1      | R/W  | Loop 2 time slot control byte 1             |  |

| 0C             | 12                 | L2TSCTL2      | R/W  | Loop 2 time slot control byte 2             |  |

| 0D             | 13                 | L2TSCTL3      | R/W  | Loop 2 time slot control byte 3             |  |

| 0E             | 14                 | L2TSCTL4      | R/W  | Loop 2 time slot control byte 4             |  |

| 0F             | 15                 | L3TSCTL1      | R/W  | Loop 3 time slot control byte 1             |  |

| 10             | 16                 | L3TSCTL2      | R/W  | Loop 3 time slot control byte 2             |  |

| 11             | 17                 | L3TSCTL3      | R/W  | Loop 3 time slot control byte 3             |  |

| 12             | 18                 | L3TSCTL4      | R/W  | Loop 3 time slot control byte 4             |  |

| 13             | 19                 | IDLECODE      | R/W  | Programmable idle code bytes                |  |

| 14             | 20                 | PATCTL        | R/W  | QRSS test pattern control register          |  |

| 15             | 21                 | FMSYNC_PLLCTL | R/W  | Frame pulse sync & PLL control register     |  |

| 16             | 22                 | PATSTAT       | R/W  | Test pattern error counter status register  |  |

| 17             | 23                 | DXPSSTAT      | R/W  | Demux power status register                 |  |

| 18             | 24                 | DXHRPSTAT     | R/W  | Demux HDSL repeater present status register |  |

| 19             | 25                 | DXLOSDSTAT    | R/W  | Demux loss of signal status register        |  |

| 1A             | 26                 | LPRSTAT       | R/W  | Loop reversal status register               |  |

| 1B             | 27                 | GENINTEN      | R/W  | General interrupt enable register           |  |

| 1C             | 28                 | GENINTSTAT    | R/W  | General interrupt status register           |  |

| 1D             | 29                 | 6MSINTEN      | R/W  | 6 ms interrupt enable register              |  |

| 1E             | 30                 | 6MSINTSTAT    | R/W  | 6 ms interrupt status register              |  |

Table 2:

Register Summary

| Table 2:       | Register Summary – continued |                 |      |                                                  |  |  |

|----------------|------------------------------|-----------------|------|--------------------------------------------------|--|--|

| Hex<br>Address | Decimal<br>Address           | Symbol          | Туре | Description                                      |  |  |

| 1F             | 31                           | IND_3EOCINTEN   | R/W  | Indicator bits & triple echo EOC enable register |  |  |

| 20             | 32                           | IND_3EOCINTSTAT | R/W  | Indicator bits & triple echo EOC status register |  |  |

| 21             | 33                           | GLBCTL          | R/W  | Global control register                          |  |  |

| 22             | 34                           | PLL_BWH         | R/W  | PLL band width control (high byte)               |  |  |

| 23             | 35                           | PLL_BWL         | R/W  | PLL band width control (low byte)                |  |  |

| 24             | 36                           | DXRSCNTR        | R    | Demux loops restart counter                      |  |  |

| 25             | 37                           | MXL1Z1          | R/W  | Mux loop 1 Z bits (LSB)                          |  |  |

| 26             | 38                           | MXL1Z2          | R/W  | Mux loop 1 Z bits                                |  |  |

| 27             | 39                           | MXL1Z3          | R/W  | Mux loop 1 Z bits                                |  |  |

| 28             | 40                           | MXL1Z4          | R/W  | Mux loop 1 Z bits                                |  |  |

| 29             | 41                           | MXL1Z5          | R/W  | Mux loop 1 Z bits                                |  |  |

| 2A             | 42                           | MXL1Z6          | R/W  | Mux loop 1 Z bits (MSB)                          |  |  |

| 2B             | 43                           | MXL1EOCH        | R/W  | Mux loop 1 EOC message (high byte)               |  |  |

| 2C             | 44                           | MXL1EOCL        | R/W  | Mux loop 1 EOC message (low byte)                |  |  |

| 2D             | 45                           | MXL1UIB         | R/W  | Mux loop 1 UIB bits                              |  |  |

| 2E             | 46                           | DXL1Z1          | R    | Demux loop 1 Z bits (LSB)                        |  |  |

| 2F             | 47                           | DXL1Z2          | R    | Demux loop 1 Z bits                              |  |  |

| 30             | 48                           | DXL1Z3          | R    | Demux loop 1 Z bits                              |  |  |

| 31             | 49                           | DXL1Z4          | R    | Demux loop 1 Z bits                              |  |  |

| 32             | 50                           | DXL1Z5          | R    | Demux loop 1 Z bits                              |  |  |

| 33             | 51                           | DXL1Z6          | R    | Demux loop 1 Z bits (MSB)                        |  |  |

| 34             | 52                           | DXL1EOCH        | R    | Demux loop 1 EOC message (high byte)             |  |  |

| 35             | 53                           | DXL1EOCL        | R    | Demux loop 1 EOC message (low byte)              |  |  |

| 36             | 54                           | DXL1UIB         | R    | Demux loop 1 UIB bits                            |  |  |

| 37             | 55                           | DXL1CRCEC       | R    | Demux loop 1 CRC error count                     |  |  |

| 38             | 56                           | DXL1FEBEEC      | R    | Demux loop 1 FEBE error count                    |  |  |

| 39             | 57                           | DXL1BPVEC       | R    | Demux loop 1 BPV error count                     |  |  |

| 3A             | 58                           | L1PATECH        | R    | Loop 1 QRSS test pattern error counter (High)    |  |  |

| 3B             | 59                           | L1PATECL        | R    | Loop 1 QRSS test pattern error counter (Low)     |  |  |

| 3C             | 60                           | MX1RSCNTR       | R    | Loop 1 mux restart counter                       |  |  |

| 3D-3F          | 61-63                        | -               | —    | Unused                                           |  |  |

| 40-44          | 64-68                        | -               | -    | Unused                                           |  |  |

| 45             | 69                           | MXL2Z1          | R/W  | Mux loop 2 Z bits (LSB)                          |  |  |

| 46             | 70                           | MXL2Z2          | R/W  | Mux loop 2 Z bits                                |  |  |

| 47             | 71                           | MXL2Z3          | R/W  | Mux loop 2 Z bits                                |  |  |

| 48             | 72                           | MXL2Z4          | R/W  | Mux loop 2 Z bits                                |  |  |

#### Table 2: Register Summary – continued

| Table 2: R     | Register Summary – continued |            |      |                                                    |  |  |  |

|----------------|------------------------------|------------|------|----------------------------------------------------|--|--|--|

| Hex<br>Address | Decimal<br>Address           | Symbol     | Туре | Description                                        |  |  |  |

| 49             | 73                           | MXL2Z5     | R/W  | Mux loop 2 Z bits                                  |  |  |  |

| 4A             | 74                           | MXL2Z6     | R/W  | Mux loop 2 Z bits (MSB)                            |  |  |  |

| 4B             | 75                           | MXL2EOCH   | R/W  | Mux loop 2 EOC message (High byte)                 |  |  |  |

| 4C             | 76                           | MXL2EOCL   | R/W  | Mux loop 2 EOC message (Low byte)                  |  |  |  |

| 4D             | 77                           | MXL2UIB    | R/W  | Mux loop 2 UIB bits                                |  |  |  |

| 4E             | 78                           | DXL2Z1     | R    | Demux loop 2 Z bits (LSB)                          |  |  |  |

| 4F             | 79                           | DXL2Z2     | R    | Demux loop 2 Z bits                                |  |  |  |

| 50             | 80                           | DXL2Z3     | R    | Demux loop 2 Z bits                                |  |  |  |

| 51             | 81                           | DXL2Z4     | R    | Demux loop 2 Z bits                                |  |  |  |

| 52             | 82                           | DXL2Z5     | R    | Demux loop 2 Z bits                                |  |  |  |

| 53             | 83                           | DXL2Z6     | R    | Demux loop 2 Z bits (MSB)                          |  |  |  |

| 54             | 84                           | DXL2EOCH   | R    | Demux loop 2 EOC message (High byte)               |  |  |  |

| 55             | 85                           | DXL2EOCL   | R    | Demux loop 2 EOC message (Low byte)                |  |  |  |

| 56             | 86                           | DXL2UIB    | R    | Demux loop 2 UIB bits                              |  |  |  |

| 57             | 87                           | DXL2CRCEC  | R    | Demux loop 2 CRC error count                       |  |  |  |

| 58             | 88                           | DXL2FEBEEC | R    | Demux loop 2 FEBE error count                      |  |  |  |

| 59             | 89                           | DXL2BPVEC  | R    | Demux loop 2 BPV error counter                     |  |  |  |

| 5A             | 90                           | L2PATECH   | R    | Loop 2 QRSS test pattern error counter (High byte) |  |  |  |

| 5B             | 91                           | L2PATECL   | R    | Loop 2 QRSS test pattern error counter (Low byte)  |  |  |  |

| 5C             | 92                           | MX2RSCNTR  | R    | Loop 2 mux restart counter                         |  |  |  |

| 5D-5F          | 93-95                        | _          | -    | Unused                                             |  |  |  |

| 60-64          | 96-100                       | _          | -    | Unused                                             |  |  |  |

| 65             | 101                          | MXL3Z1     | R/W  | Mux loop 3 Z bits (LSB)                            |  |  |  |

| 66             | 102                          | MXL3Z2     | R/W  | Mux loop 3 Z bits                                  |  |  |  |

| 67             | 103                          | MXL3Z3     | R/W  | Mux loop 3 Z bits                                  |  |  |  |

| 68             | 104                          | MXL3Z4     | R/W  | Mux loop 3 Z bits                                  |  |  |  |

| 69             | 105                          | MXL3Z5     | R/W  | Mux loop 3 Z bits                                  |  |  |  |

| 6A             | 106                          | MXL3Z6     | R/W  | Mux loop 3 Z bits (MSB)                            |  |  |  |

| 6B             | 107                          | MXL3EOCH   | R/W  | Mux loop 3 EOC message (High byte)                 |  |  |  |

| 6C             | 108                          | MXL3EOCL   | R/W  | Mux loop 3 EOC message (Low byte)                  |  |  |  |

| 6D             | 109                          | MXL3UIB    | R/W  | Mux loop 3 UIB bits                                |  |  |  |

| 6E             | 110                          | DXL3Z1     | R    | Demux loop 3 Z bits (LSB)                          |  |  |  |

| 6F             | 111                          | DXL3Z2     | R    | Demux loop 3 Z bits                                |  |  |  |

| 70             | 112                          | DXL3Z3     | R    | Demux loop 3 Z bits                                |  |  |  |

| 71             | 113                          | DXL3Z4     | R    | Demux loop 3 Z bits                                |  |  |  |

| 72             | 114                          | DXL3Z5     | R    | Demux loop 3 Z bits                                |  |  |  |

Table 2:

Register Summary – continued

| Table 2: F     | Register Summary – continued |            |      |                                                    |  |  |  |

|----------------|------------------------------|------------|------|----------------------------------------------------|--|--|--|

| Hex<br>Address | Decimal<br>Address           | Symbol     | Туре | Description                                        |  |  |  |

| 73             | 115                          | DXL3Z6     | R    | Demux loop 3 Z bits (MSB)                          |  |  |  |

| 74             | 116                          | DXL3EOCH   | R    | Demux loop 3 EOC message (High byte)               |  |  |  |

| 75             | 117                          | DXL3EOCL   | R    | Demux loop 3 EOC message (Low byte)                |  |  |  |

| 76             | 118                          | DXL3UIB    | R    | Demux loop 3 UIB bits                              |  |  |  |

| 77             | 119                          | DXL3CRCEC  | R    | Demux loop 3 CRC error count                       |  |  |  |

| 78             | 120                          | DXL3FEBEEC | R    | Demux loop 3 FEBE error count                      |  |  |  |

| 79             | 121                          | DXL3BPVEC  | R    | Demux loop 3 BPV error count                       |  |  |  |

| 7A             | 122                          | L3PATECH   | R    | Loop 3 QRSS test pattern error counter (High byte) |  |  |  |

| 7B             | 123                          | L3PATECL   | R    | Loop 3 QRSS test pattern error counter (Low byte)  |  |  |  |

| 7C             | 124                          | MX3RSCNTR  | R    | Loop 3 mux restart counter                         |  |  |  |

| 7D             | 125                          | VER        | R    | HFMA version number                                |  |  |  |

| 7E             | 126                          | MXTEST     | R/W  | μP mode testing register for mux                   |  |  |  |

| 7F             | 127                          | DXTEST     | R/W  | $\mu P$ mode testing register for demux            |  |  |  |

#### Table 2: Register Summary – continued

### Mux E1 Control Register

Address: 00 Abbreviation: MXE1CTL Read/Write

| Table 3: Mu | ux E1 Contro | l Register |

|-------------|--------------|------------|

|-------------|--------------|------------|

| Bit | Name     | Default | Description                                                                                                                                                                                                                |

|-----|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | n/a      | 0       | Not used; Always read Low.                                                                                                                                                                                                 |

| 6   | n/a      | 0       | Not used; Always read Low.                                                                                                                                                                                                 |

| 5   | INVMXCK  | 0       | Invert Mux E1 Input Clock. When High, the rising edge of E1CLKI samples the mux E1 data and frame mark. When this bit is Low, the falling edge samples the data and frame mark.                                            |

| 4   | NMCKEN   | 0       | Nominal Clock Enable. When High, nominal clock is selected to input the MX_PROCESS block. When Low, E1 recovered clock is selected to input the MX_PROCESS block.                                                          |

| 3   | NMFMEN   | 0       | Nominal Frame Pulse Enable. When High, nominal frame pulse is selected to input the MX_PROCESS block. When Low, Demux E1 frame pulse is selected to input the MX_PROCESS block.                                            |

| 2   | MXSLIDEN | 1       | MUx Sliding Enable. When High, sliding mode is selected. When Low, jerking mode is selected.                                                                                                                               |

| 1   | SNDMXAIS | 0       | Send Mux E1 AIS. When High, E1 AIS is inserted into the mux HDSL payload of two/three loops. When Low, the incoming E1 is inserted. This control bit is ORed with the FRCMAIS input pin (when enabled) to control mux AIS. |

| 0   | EXTMAIS  | 0       | External Mux AIS Enable. When High, the FRCMAIS input pin is<br>enabled to insert mux E1 AIS. When Low, mux AIS insert is controlled<br>solely by the SNDMAIS control bit.                                                 |

NOTE: Usage of NMCKEN and NMFMEN are:

| 0                                              |        |               |  |  |  |  |  |

|------------------------------------------------|--------|---------------|--|--|--|--|--|

| <b>Operation</b>                               | NMCKEN | <u>NMFMEN</u> |  |  |  |  |  |

| Framed service                                 | 0      | 0             |  |  |  |  |  |

| Unframed service                               | 0      | 1             |  |  |  |  |  |

| E1 loopback                                    | 1      | 1             |  |  |  |  |  |

| E1 loss of signal (LOS)                        | 1      | 1             |  |  |  |  |  |

| (where E1 framer doesn't provide clock in LOS) |        |               |  |  |  |  |  |

### **Demux E1 Control Register**

Address: 01 Abbreviation: DXE1CTL Read/Write

| Bit | Name    | Default | Description                                                                                                                                                                                                                                                                                                                                |

|-----|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | INVDXCK | 0       | Invert Demux E1 Output Clock. When High, the demux E1 data and frame mark signals are updated on the falling edge of E1CLKO. When this bit is Low, the data and frame mark are updated on the rising edge.                                                                                                                                 |

| 6   | E1LB    | 0       | E1 Loopback. When High, both directions of the E1 NRZ clock, data, and frame mark are looped back. When Low, normal operation is enabled.                                                                                                                                                                                                  |

| 5   | TMGSRC1 | 0       | Demux E1 Timing Source Select. These two bits can select the ADPLL                                                                                                                                                                                                                                                                         |

| 4   | TMGSRC0 | 0       | output or nominal clock as E1CLK0.<br>00: dependent on the status of input pins LOSWx and software setting in<br>LPCTL register. The loop with first inactive LOSW status will be selected.<br>If all LOSWx are active, force to nominal clock.<br>01: force to loop 1<br>10: force to loop 2<br>11: force to loop 3                       |

| 3   | DXAIS3  | 0       | Demux Loop 3 AIS Enable. When High, the demux Loop 3 payload is forced to all ones. When Low, normal operation is enabled.                                                                                                                                                                                                                 |

| 2   | DXAIS2  | 0       | Demux Loop 2 AIS Enable. When High, the demux Loop 2 payload is forced to all ones. When Low, normal operation is enabled.                                                                                                                                                                                                                 |

| 1   | DXAIS1  | 0       | Demux Loop 1 AIS Enable. When High, the demux Loop 1 payload is forced to all ones. When Low, normal operation is enabled.                                                                                                                                                                                                                 |

| 0   | EXTDAIS | 1       | External Demux AIS Enable. When High, the LOSW1 input pin is enabled to force the demux Loop 1 payload to all ones, LOSW2 input pin is enabled to force the demux Loop 2 payload to all ones, and LOSW3 input pin is enabled to force the demux Loop 3 payload to all ones. When EXTDAIS is Low, external demux AIS insertion is disabled. |

#### Table 4: Demux E1 Control Register

### HDSL Loop Control Register

Address: 02 Abbreviation: LPCTL Read/Write

| Bit | Name    | Default | Description                                                                                                                                                               |

|-----|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | n/a     | 0       | Not used; Always read Low.                                                                                                                                                |

| 6   | HDSLLB  | 0       | HDSL Loopback Enable. When High, both directions of the Loop 1, Loop 2 and Loop 3 frame mark and data signals are looped back. When Low, all HDSL loopbacks are disabled. |

| 5   | LOSW3C1 | 0       | LOSW3 S/W Control                                                                                                                                                         |

|     |         |         | Normal Operation: 0x                                                                                                                                                      |

| 4   | LOSW3C0 | 0       | Force to Active: 10                                                                                                                                                       |

|     |         |         | Force to Inactive: 11                                                                                                                                                     |

| 3   | LOSW2C1 | 0       | LOSW2 S/W Control                                                                                                                                                         |

|     |         |         | Normal Operation: 0x                                                                                                                                                      |

| 2   | LOSW2C0 | 0       | Force to Active: 10                                                                                                                                                       |

|     |         |         | Force to Inactive: 11                                                                                                                                                     |

| 1   | LOSW1C1 | 0       | LOSW1 S/W Control                                                                                                                                                         |

|     |         |         | Normal Operation: 0x                                                                                                                                                      |

| 0   | LOSW1C0 | 0       | Force to Active: 10                                                                                                                                                       |

|     |         |         | Force to Inactive: 11                                                                                                                                                     |

#### Table 5: HDSL Loop Control Register

### HDSL Loop 1 Overhead Control Register

Address: 03 Abbreviation: L1OHCTL Read/Write

| Bit | Name   | Default | Description                                                                                                                                                                                                                                                                                                                            |

|-----|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|