### 2.488 Gbits/sec SONET/SDH FEC Encoder and Decoder (CODEC) Chipset

## Features

- Out of Band Reed-Solomon Encoding and Decoding using a (255,241) Code

- Realizes a Decoder Output BER of 10<sup>-20</sup> for Input BER of 10<sup>-5</sup>

- Processes Data Rates up to 2.654Gb/s and Information Rates to 2.488Gb/s

- Device Pin Configurable as Stand-alone Encoder, Decoder, or Transparent Bypass

- Provides a Dedicated Uuser Defined Data Channel for Transparent out of Band Communications.

- Bit Rate and Protocol Independent

- Interfaces Directly with Vitesse OC-48 Rate Components

- PECL and TTL I/O

- Telecom Temperature Range: 0 85C

- +3.3V Power Supply

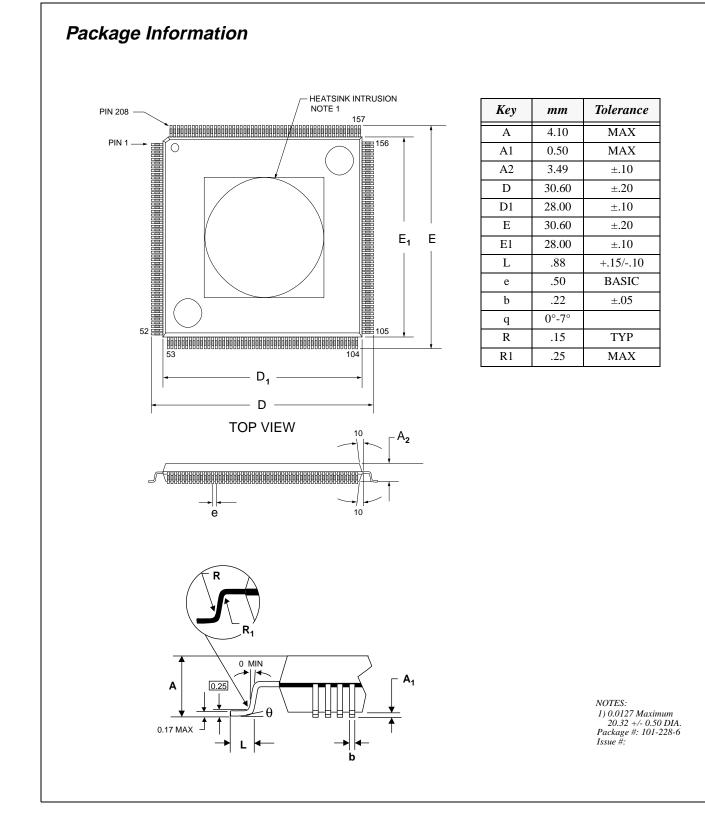

- Thermally Enhanced 208 PQFP Package

- Evaluation Platform with Dual Rate 2.488G/ 2.66G Components Available

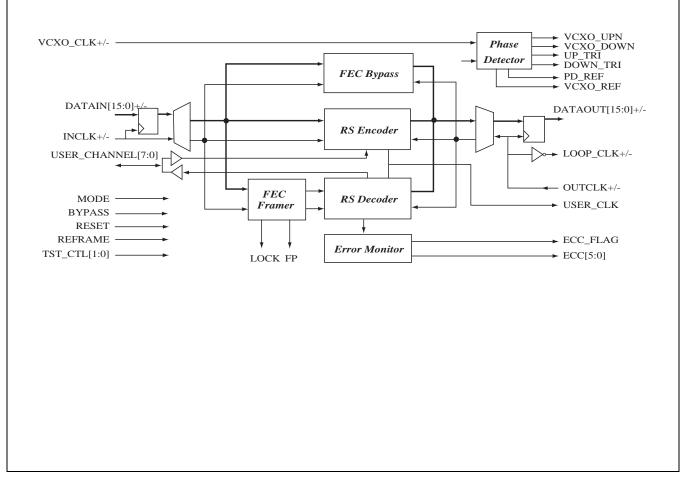

## VSC9210 Block Diagram

## Advance Product Information VSC9210

## **Functional Overview**

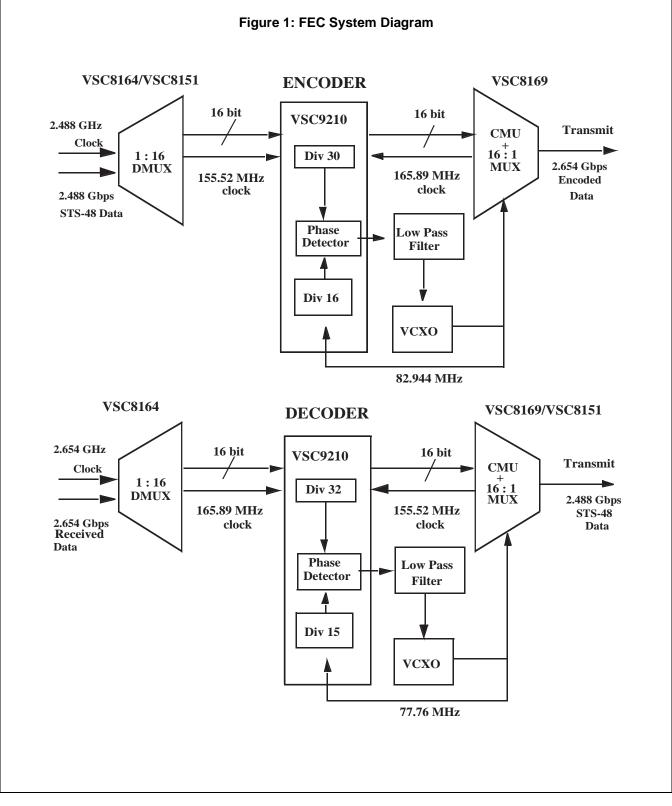

The device utilizes two 16 bit differential PECL I/O ports to interface with a high speed multiplexer and a demultiplexer. For the encoder, the 1:16 demultiplexer (VSC8164) is used to convert the incoming 2.5 Gbps STS-48 information to a 16 bit parallel data at 155 MHz to interface with the VSC9210. After the encoding process, the 16 bit parallel output data from the VSC9210 is obtained at 165 MHz and is converted to a 2.65 Gbps data stream using the 16:1 multiplexer (VSC8169). In the case of the decoder configuration, the demultiplexer operates on a 2.65 Gbps data stream while the multiplexer provides the 2.5 Gbps STS-48 information stream. Clock dividers are incorporated within the VSC9210 to provide control of an external PLL circuit for synthesizing the necessary reference clock for the multiplexer. In the case of the bypass mode, the input and output rates are identical and both the multiplexer and demultiplexer operate at 2.5 Gbps.

The VSC9210 can be operated at or below unencoded and encoded data rates of 155Mbs and 165Mbs respectively. The ratio of the two input clocks (INCLK and OUTCLK) must be 15/16 for encoder operation, and 16/15 for decoder operation. Management of the clocking interface allows the FEC device to operate at multiple clock rates.

An architecture that includes SONET/SDH performance monitoring is also available. The VSC8151 SONET/SDH Section Terminator device has a built in 16 bit PECL interface that allows the encoder VSC8164 demultiplexer and decoder VSC8169 multiplexer to be replaced. This enables the construction of a system that is protocol and bit rate transparent but has optional performance monitoring features for SONET/SDH data.

2.488 Gbits/sec SONET/SDH FEC Encoder and Decoder (CODEC) Chipset

## Advance Product Information VSC9210

## **Overview of Reed-Solomon Codes**

The VSC9210 CODEC device performs error correction and detection using Reed-Solomon (RS) codes. The codeword comprises *n* symbols each being *m* bits long with  $n = 2^m - 1$ . An (n,k) code is guaranteed to correct 't' symbol errors occurring anywhere in the codeword, with 2t = n - k. RS codes can also correct burst errors. An (n,k) RS code can correct a minimum of m(t-1) + 1 bits of burst error within every codeword up to a maximum of *mt* bits depending on the occurrence of the burst error across the symbol boundaries. During encoding for non-systematic RS codes, a *k* symbol information vector is converted to an *n* symbol codeword by multiplying with a generator polynomial. The decoding process involves computing the error locations and the magnitude of the errors, and performing the error correction. Decreasing the ratio k/n improves the error correction performance of the code, but requires an increased encoded data output rate.

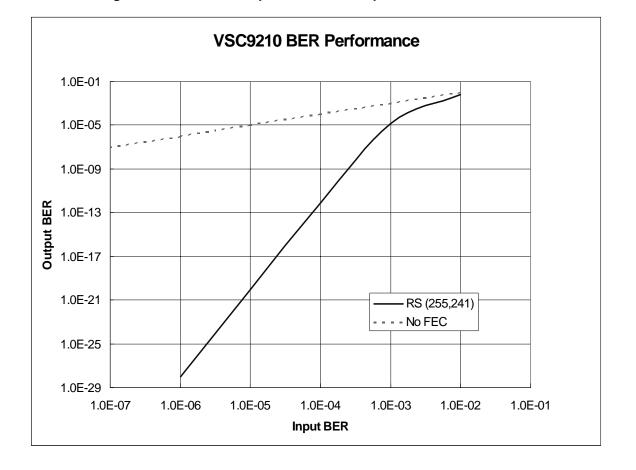

A symbol length of 8 (m = 8) results in a 255 symbol codeword that offers efficient error correction performance. The (255,241) code can correct 7 symbol errors and can handle a maximum burst error of 49 - 56 bits within each codeword as detailed above. For an input BER of 10<sup>-5</sup> the output BER is 10<sup>-20</sup>.

#### Figure 2: Theoretical Output BER versus Input BER for the VSC9210

## 2.488 Gbits/sec SONET/SDH FEC Encoder and Decoder (CODEC) Chipset

## Signal Definitions

| Signal            | Name                                      | <i>I/O</i> | Freq/<br>Type       | Description                                                                                                                                                                                                                                                                                                                           |

|-------------------|-------------------------------------------|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATAIN[15:0] +/-  | Parallel Receive Data.                    | Ι          | 155/166Mbs<br>PECL  | This parallel data bus receives the<br>incoming STS-48 at 155MHz (or<br>Encoded data at 166 MHz).<br>DATAIN[15] is the most significant bit<br>and DATAIN[0] is the least significat<br>bit. DATAIN[15] corresponds to the firs<br>arriving bit on the serial data stream.<br>DATAIN[15:0] is sampled on the rising<br>edge of INCLK. |

| INCLK +/-         | Parallel Receive<br>Data Clock.           | Ι          | 155/166MHz<br>PECL  | This clock reference is used to capture<br>the Parallel Receive Data on the rising<br>edge. The clock frequency is<br>155.52MHz relating to STS-48 for<br>Encoder operation; 165.888MHz for<br>Decoder operation (16/15 ratio).                                                                                                       |

| DATAOUT[15:0] +/- | Parallel Transmit Data                    | 0          | 166/155 Mbs<br>PECL | This parallel data bus outputs the<br>Encoded Data at 166MHz (or Decoded<br>STS-48 data at 155MHz).<br>DATAOUT[15] is the most significant<br>bit and DATAOUT[0] is the least<br>significat bit. DATAOUT[15]<br>corresponds to the first transmitted bit<br>on the serial data stream.                                                |

| OUTCLK +/-        | Parallel Transmit<br>Data Clock.          | Ι          | 166/155MHz<br>PECL  | This clock reference is used to output<br>the Parallel Transmit Data on the falling<br>edge after Encode or Decode operation<br>is complete. The clock frequency is<br>166.888MHz for Encoder operation;<br>155.52MHz relating to STS-48 for<br>Decoder operation (15/16 ratio).                                                      |

| LOOP_CLK +/-      | Parallel Transmit Data<br>Loopback Clock. | О          | 166/155MHz<br>PECL  | This clock is used by the receiving<br>device to capture DATAOUT[15:0] on<br>the rising edge. It is an inverted version<br>of the received OUTCLK input signal.                                                                                                                                                                       |

| MODE              | Mode Control                              | I          | STATIC<br>TTL       | Static control pin to set device to<br>Encoder or Decoder operation (when<br>not in Bypass mode; BYPASS = 0).<br>MODE = 0 for Encoder, MODE = 1 for<br>Decoder. Signal has internal pulldown.                                                                                                                                         |

| BYPASS            | FEC Bypass Control                        | Ι          | STATIC<br>TTL       | Active high signal to disable FEC<br>Encode/Decode operation. INCLK and<br>OUTCLK <i>must</i> be same rate (155.52<br>MHz). Signal has internal pulldown.                                                                                                                                                                             |

## Advance Product Information VSC9210

| Signal            | Name                             | <i>I/O</i> | Freq/<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|----------------------------------|------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET             | Reset                            | Ι          | TTL           | Active high asynchronous reset signal<br>used during manufacturing. Not<br>required for system use. Schmidt trigger<br>input with internal pulldown.                                                                                                                                                                                                                                                   |

| REFRAME           | FEC Re-Frame Control             | Ι          | TTL           | Active high asynchronous control to<br>force a new FEC Frame search.<br>Intended for testing only, not required<br>for system operation. Schmidt trigger<br>input with internal pulldown.                                                                                                                                                                                                              |

| SYNC_INHIBIT      | FIFO Self-Synchronize<br>Inhibit | Ι          | STATIC<br>TTL | Not required for STS-48 system use.<br>Signal has internal pulldown.                                                                                                                                                                                                                                                                                                                                   |

| TEST_CTL[1:0]     | Manufacturing Test Control       | Ι          | STATIC<br>TTL | Allows USER_CHANNEL[7:0] to be<br>used as a test port for manufacturing<br>tests. For user operation these <i>must</i> be<br>set to" 00". Signals have internal<br>pulldown.                                                                                                                                                                                                                           |

| USER_CHANNEL[7:0] | User Data Channel                | I/O        | 2mA<br>TTL    | Bidirectional User Data Channel: input<br>for Encoder, output for Decoder. Input is<br>captured relative to rising edge of<br>USER_CLK in Encoder mode. Output<br>should be captured on rising edge of<br>USER_CLK when in Decoder mode;<br>data is valid when ECC_FLAG is low.<br>Signals are open drain output and<br>require external pullup resistors of<br>approximately 10K to V <sub>DD</sub> . |

| ECC[5:0]          | Error Correction Count           | 0          | 2mA<br>TTL    | Provides count of corrected errors in<br>previous FEC Codeword (2048 bits).<br>Data is to be captured with USER_CLK.<br>Data is valid only when ECC_FLAG is<br>low, otherwise data output is 3F <sub>H</sub> .                                                                                                                                                                                         |

| ECC_FLAG          | Error Correction Count Flag      | 0          | 2mA<br>TTL    | Active high signal indicating that the<br>previous Codeword had an<br>uncorrectable quantity of errors; greater<br>than 7 symbol errors. When high,<br>ECC[5:0] and USER_CHANNEL[7:0]<br>will be invalid.                                                                                                                                                                                              |

| FP                | FEC Frame Pulse                  | 0          | 4mA<br>TTL    | Active high frame signal that occurs<br>every Codeword (1.296 MHz) when<br>FEC Framer is in lock. When Framer is<br>in lock but verifying LOCK status is<br>correct, FP signals are not presented.<br>Pulse width is approximately eight<br>INCLK cycles.                                                                                                                                              |

| LOCK              | FEC Framer Lock Status           | 0          | 2mA<br>TTL    | Active high signal indicating FEC<br>Framing is in lock.                                                                                                                                                                                                                                                                                                                                               |

### 2.488 Gbits/sec SONET/SDH FEC Encoder and Decoder (CODEC) Chipset

| Signal          | Name                                     | <i>I/O</i> | Freq/<br>Type          | Description                                                                                                                                                                                                                                              |

|-----------------|------------------------------------------|------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USER_CLK        | User Data Channel Clock                  | 0          | 4mA<br>TTL             | Clock used for USER_CHANNEL,<br>ECC[5:0], ECC_FLAG, FP, and LOCK<br>access.                                                                                                                                                                              |

| VCXO_UPN/_DOWNN | Phase Detector Error                     | 0          | 8mA                    | Active low error signals from the<br>internal Phase Detector to be used by an<br>external summing and integrating loop<br>filter to drive a VCXO in the PLL<br>circuit. Signals are open-drain and<br>require external pullup resistors.                 |

| UP_TRI/DOWN_TRI | Tri-state Phase Detector Error           | 0          | 4mA<br>TTL             | Error signals from internal Phase<br>Detector that are to be tied together to<br>create a single error signal for an<br>external integrating loop filter to drive a<br>VCXO in the PLL circuit. Signals are<br>Tri-state when no phase error is present. |

| PD_REF/PD_VCXO  | External Phase Detector<br>Scaled Clocks | 0          | 5.184MHz<br>2mA<br>TTL | PD_REF is the scaled input clock<br>(INCLK) and PD_VCXO is the scaled<br>vcxo clock (VCXO_CLK) that can be<br>used by an external phase detector<br>circuit if desired.                                                                                  |

| VCXO_CLK +/-    | VCXO Input Clock                         | Ι          | 78/83MHz<br>PECL       | Input clock from external VCXO in PLL circuit. Signal is scaled to 5.184 MHz to drive internal phase detectors and PD_VCXO.                                                                                                                              |

# Advance Product Information VSC9210