# AT69170E

# **Atmel**

# Space FPGA Configuration Memory

# DATASHEET

# **See Applicable Errata in Section 13.**

### **Features**

- 4 Mbits On-Chip Flash Array

- Memory Designed to Store Configuration Programs for Field Programmable Gate Arrays (FPGAs)

- In-System Programming (ISP) via Two-Wire Bus

- Simple Interface to SRAM FPGAs

- Compatible with AT40K devices

- Cascadable Read-Back to Support Additional Configurations or Higher-Density Arrays

- Memory Write Protection

- Programmable Reset Polarity

- Low-power Rad-Hard non volatile 0.18µm CMOS process

- Operating range:

- Voltage : 3V to 3.6V

- Temperature : -55 to +125°C

- Operating power consumption : 72 mW max

- High-Reliability

- Endurance: 50,000 write cycles (in page mode)

- Data retention: 10 Years @ 125°C

- Radiation Tolerance

- Tested up to a Total Dose of 60 krad (Si)

- RHA capability of 30 krad (Si) according to MIL STD 883 Method 1019

- Quality Grades :

- QML-V or Q

- Package : 305 Mils FP18

- Mass : 1 g

# **Table of Contents**

| 1.  | Description4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.  | Block Diagram4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.  | Pin Configuration53.1Package Description53.2Pin Description53.3Power supply decoupling7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.  | Device Modes Summary7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.  | Factory Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.  | Power-On initialisation8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.  | Standby Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.  | TWI mode     8       8.1     Definitions     8       8.2     TWI Bus Description     8       8.3     TWI Bus Characteristics     9       8.3.1     Bus Ready     9       8.3.2     Start and Stop Conditions     9       8.3.3     Clock and Data Transitions     9       8.3.4     Acknowledge     10       8.3.5     Device Addressing     10       8.3.6     Internal Memory Addressing     10       8.3.7     Data Packets     12       8.4     TWI Operations     13       8.4.1     Write Operations     13       8.4.1     Vrite Operations     13       8.4.1.2     Acknowledge Polling 16       8.4.2     Read Operations     16       8.4.2.1     Random Read 16     8.4.2.2       8.5.1     Configuration Write Function     19       8.5.2     Configuration Read Function     19       8.5.3     Special Functions List     21       8.5.3.1     Data Protection 21     8.5.3.3       8.5.3.3     Full Chip Erase 22     8.5.3.3 |

| 9.  | FPGA Dump Mode239.1Operating Mode overview239.2Single Device Configuration239.3Daisy Chain Configuration25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10. | Electrical Specifications     28       10.1     Absolute Maximum Ratings*     28       10.2     Recommended DC Operating Conditions     28       10.3     Capacitance (F=1MHz, 25°C)     28       10.4     DC Characteristics     28       10.5     AC Characteristics     29       10.5.1     Test Loads and Waveforms     29       10.5.2     TWI Mode Characteristics     30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |       | 10.5.3 Dump Mode Characteristics        |

|-----|-------|-----------------------------------------|

| 11. | Orde  | ring Information                        |

| 12. | Pack  | aging Information                       |

| 13. | Activ | e Errata                                |

|     | 13.1  | A2 pin input not properly processed     |

|     | 13.2  | TWI address acknowledgement             |

|     | 13.3  | TWI page write corruption               |

|     | 13.4  | TWI write frequency limitation          |

|     | 13.5  | READY signal may not rise               |

|     | 13.6  | READY signal drops briefly at power off |

| 14. | Revis | sion History                            |

# 1. Description

The AT69170E FPGA configuration memory (configurator) is an electrically erasable and re-programmable RadHard memory organized as 4Mx1bit. It is an easy-to-use and cost-effective configuration memory for space Field Programmable Grid Array (FPGA). It is manufactured with ATMEL low power non volatile CMOS RadHard process.

It is packaged in the 18-pin 305 Mils wide Flat Pack package. AT69170E uses a simple serial-access procedure to configure one or more FPGA devices. A two wire interface (TWI) is available for memory programmation.

The user can select the polarity of the reset function by programming a dedicated sequence. These devices also support a write-protection mechanism within its programming mode.

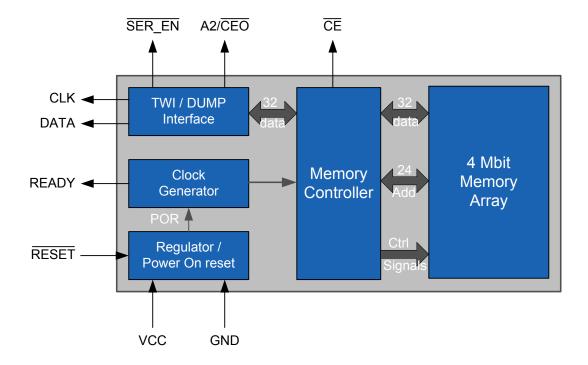

# 2. Block Diagram

### 3. Pin Configuration

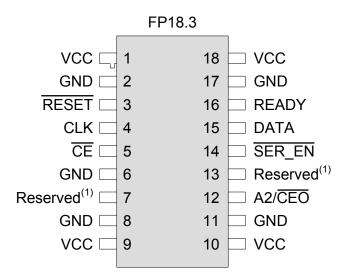

### 3.1 Package Description

The AT69170E is packaged in a 18-pins flat pack package.

#### Figure 3-1. Pin assignement

Note: 1. "Reserved" pins are bonded internally. DO NOT CONNECT.

2. The package lid is connected to GND

### 3.2 Pin Description

| Symbol | Name and Function                                                                                                                                                                                                                                                                                                                                                                                   | Туре  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

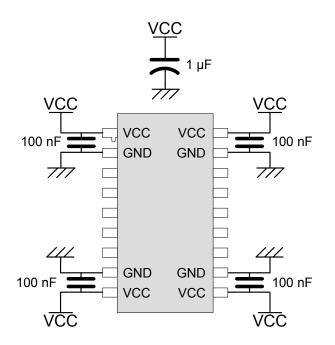

| VCC    | Power Supply input<br>The VCC pin is used to supply the source voltage to the device. Operations at invalid VCC<br>voltages may produce spurious results and should not be attempted.<br>It is recommended to implement two decoupling capacitors between VCC and GND. Each<br>capacitor must have a minimum of 100 nF capacitance.                                                                 | Power |

| GND    | Ground pin<br>The ground reference for the power supply. GND should be connected to the system ground.                                                                                                                                                                                                                                                                                              | Power |

| RESET  | <b>Reset input (operates only in Dump Mode)</b><br>The polarity of this input is programmable. For Atmel FPGA's, the RESET pin should be programmed active low and connected to the FPGA's INIT pin (see Figure 9-3 on page 24).<br>When the RESET pin is active, both address and bit counters are reset. This pin does not reset the device in the Two-Wire serial programming mode (SER_EN low). | Input |

| Symbol | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Туре           |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CLK    | Clock input<br>The clock input is used to increment the internal address and bit counters for reading and<br>programming.<br>In Two-Wire serial programming mode (SER_EN Low), the CLK pin must be compliant with the<br>TWI frame description provided in Section 8. "TWI mode" on page 8.<br>In Dump Mode, the serial data will be provided on the CLK's falling edge (see Figure 10-5 on<br>page 31).                                                                                                                                                                                                                                                                                                                                                                       | Input          |

| CE     | Chip Enable input (active low, operates only in Dump Mode)<br>Low : address counter is incremented by CLK.<br>High : address and bit counters are disabled.<br>This pin has no effect on the device in the Two-Wire serial programming mode (SER_EN Low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Input          |

| A2/CEO | A2 : device selection input (operates only in TWI mode)<br>Device selection input is used to configure the device address for multiple device configuration.<br>A2 enables to attach two AT69170E devices on the same bus (SER_EN low). A2 pin configured<br>to a logic "0" or "1" level. It is recommended to connect it to GND or VCC through a 10 k $\Omega$ pull-<br>up resistor.<br><b>CEO : Chip Enable Output (operates only in DUMP mode)</b><br>CEO is an active low output which goes low when the address counter of the memory has<br>reached the end of the memory plan. In a daisy chain mode including multiple AT69170E<br>devices, the CEO pin of a device is connected to the CE input of the following device in the<br>chain. (see Figure 10. on page 28). | Input / Output |

| SER_EN | Serial Mode Enable input (active low)<br>Low : Two-Wire serial programming mode<br>High : Dump Mode.<br>For applications not using the TWI serial mode, SER_EN should be tied to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input          |

| DATA   | <b>DATA I/O</b><br>It is an open-drain bi-directional pin in TWI mode (SER_EN Low).<br>It is an output in Dump Mode (SER_EN high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| READY  | <b>Open-drain reset state output</b><br>It is an open-drain output. The READY is driven low during Power-On Reset. It is<br>recommended to use a 4.7 k $\Omega$ pull-up resistor.<br>The device does not operate while this signal remains low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

### 3.3 Power supply decoupling

It is recommended to add decoupling capacitors as close as possible to the power supply pins of the device.

### 4. Device Modes Summary

| INPUT  |       |    |         | I/   | 0       | OUTPUT | DEVICE MODES                                    |

|--------|-------|----|---------|------|---------|--------|-------------------------------------------------|

| SER_EN | RESET | CE | CLK     | DATA | A2/CEO  | READY  |                                                 |

| х      | Х     | Х  | Х       | Х    | Х       | L      | Power-on initialisation                         |

| н      | А     | Х  | Х       | HZ   | Х       | Н      | Device Reset                                    |

| н      | I     | Н  | Х       | HZ   | Х       | Н      | Standby Mode                                    |

| н      | I     | L  | Running | OUT  | OUT (H) | Н      | FPGA Dump Mode<br>(Single Device Configuration) |

| н      | I     | L  | Running | OUT  | OUT (L) | Н      | FPGA Dump Mode<br>(Daisy Chain Configuration)   |

| L      | х     | х  | Running | I/O  | IN      | Н      | TWI Mode<br>(Device Programming)                |

X: means don't care between H or L

A : means Active State

I : means Inactive State

HZ : means High Impedance

The active level of the  $\overline{\text{RESET}}$  pin depends on the reset polarity configuration.

# 5. Factory Settings

The following table lists the parameters that can be changed by the user and their respective factory settings. Those parameters can be changed by means of special functions described in Section 8.5.3 on page 21.

| Parameter       | Factory Setting | Comments                                                             |

|-----------------|-----------------|----------------------------------------------------------------------|

| Data Protection | Disabled        | The changing procedure is described<br>in Section 8.5.3.1 on page 21 |

| RESET pin       | Active low      | The changing procedure is described<br>in Section 8.5.3.2 on page 22 |

### 6. Power-On initialisation

The AT69170E provides a READY output pin to indicate that the memory power-on sequence is completed and ready for use.

### 7. Standby Mode

The AT69170E enters in a standby mode whenever  $\overline{CE}$  input pin is asserted high in FPGA loading mode. In standby mode, the data output pin remains in high impedance.

### 8. TWI mode

#### 8.1 Definitions

MASTER : any TWI device controlling the transfer of data, such as a microprocessor.

SLAVE : device being controlled. EEPROMs are always considered as slaves

TRANSMITTER : device currently sending data on the bus. May be either a master or a slave.

RECEIVER : device currently receiving data on the bus. May be either a master or a slave.

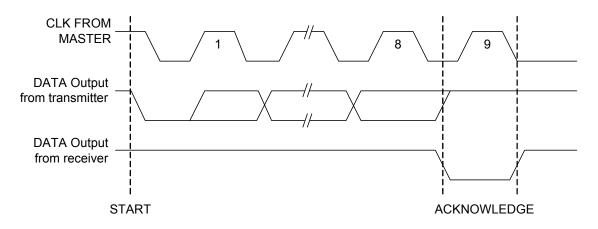

WORD : 32 bit of data, formatted as a 4-byte packet.

PAGE : 128 sequential word locations starting at 3-byte address boundary, that may be programmed during a "page write" programming cycle.

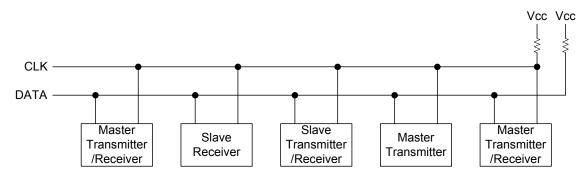

### 8.2 TWI Bus Description

The internal memory of the AT69170E is accessed through a TWI bus which is enabled when SER\_EN pin is driven Low.

The TWI is a bi-directional 2-wire bus which supports a serial synchonous data transmission protocol. A device that sends data onto the bus (DATA wire) is defined as transmitter and a device receiving data as receiver. The bus works in Master/Slave mode. Several slave and master devices can be attached to the bus but only one master and one slave can communicate at a time. The bus is always controlled by the master device which generates the serial clock (CLK wire), controls the bus access and generates the START and STOP conditions. Both master and slaves can operate as transmitter and receiver but the master determines which mode is activated. The slave devices are identified by a unique address on the bus and only one slave can be selected at a time by the master. The data sent onto the bus by the transmitter are acknowledged by the receiver.

The AT69170E is a Slave Transmitter / Receiver.

#### 8.3 TWI Bus Characteristics

The following bus conditions have been defined.

#### 8.3.1 Bus Ready

The bus is ready when both data and clock lines remain high. A data transfer may be initiated only when the bus is ready.

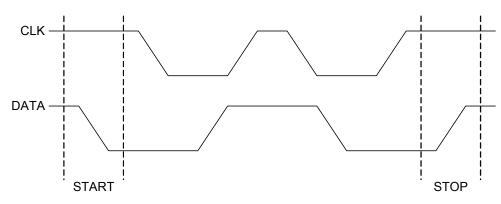

#### 8.3.2 Start and Stop Conditions

A high to low transition of the DATA line while the clock (CLK) is high determines a START condition. A low to high transition of the DATA line while the clock (CLK) is high determines a STOP condition. All data transfers must be preceded by a START condition and terminated by a STOP condition

Figure 8-2. Definition of START and STOP Conditions

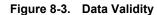

#### 8.3.3 Clock and Data Transitions

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the high period of the clock signal. The data on the line must be changed during the low period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and the STOP conditions is determined by the maximum page size (see Section 8.4).

Changes in the data line while the clock line is high will be interpreted as a START or STOP condition.

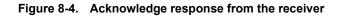

#### 8.3.4 Acknowledge

Each receiver, when adressed, must generate an acknowledge after the reception of each byte. The master must generate an extra clock pulse which is associated with this acknowledge bit.

Note: the AT69170E does not generate any acknowledge bit if an internal programming cycle is in progress.

The device that acknowledges, has to pull down the DATA line during the acknowledge clock pulse in such a way that the DATA line is stable low during the high period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out by the slave . In this case, the slave must leave the data line high to enable the master to generate the STOP condition.

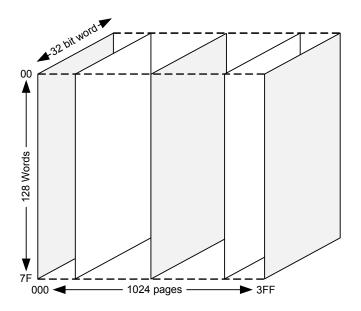

#### 8.3.5 Device Addressing

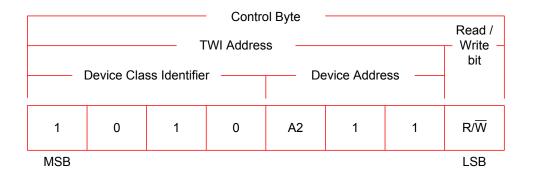

The first byte sent by the master after the START condition is the contol byte. It enables the master to select a unique slave on the bus and indicate if the access is a read or a write operation.

The control byte is composed of three fields :

Device Class Identifier : the TWI bus is designed to support a variety of devices such as RAMs, EPROMs etc .... along with EEPROMs. Hence to properly identify various devices on the TWI bus, a 4-bit "Device Class" identifier string is used. For EEPROMs, the string is 1010.

Device Address : When multiple devices of the same type (e.g. multiple EEPROMs) are present on the TWI bus, the Device Adress is used to properly identify the device in the Class.

The device Adress of the AT69170E is "A2 1 1". A2 is the value of A2 pin. This address allows as many as two AT69170E on the same bus.

Read/Write bit : the last bit of the control byte indicates if the access is Read or Write. If the bit is "1", then the access is Read, whereas if the bit is "0", then the access is Write.

#### Figure 8-5. Control Byte Format

|     |             |   | Contro | ol Byte |   |   | Read / |  |

|-----|-------------|---|--------|---------|---|---|--------|--|

|     | TWI Address |   |        |         |   |   |        |  |

|     |             |   | •      |         |   |   |        |  |

| 1   | 0           | 1 | 0      | A2      | 1 | 1 | R/W    |  |

| MSB | •           |   |        |         |   |   | LSB    |  |

The most significant bit (MSB) of the control byte is transmitted first on the TWI bus. The TWI addresses of the memory device are supplied in the table below.

Table 8-1. TWI Device Adress

| A2 pin | TWI Device Address |

|--------|--------------------|

| GND    | 53h                |

| VCC    | 57h                |

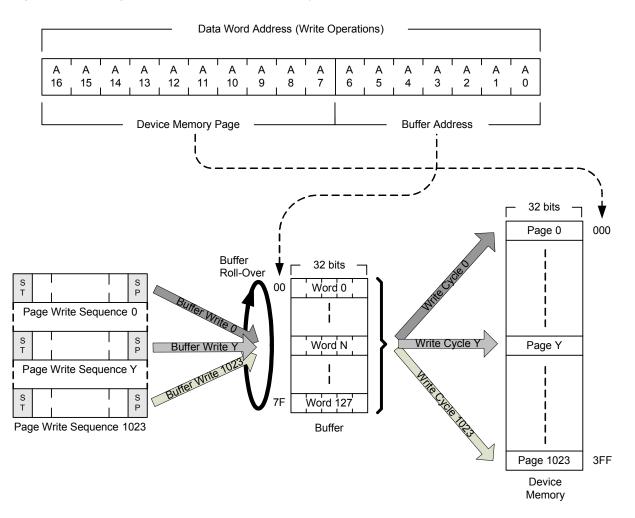

#### 8.3.6 Internal Memory Addressing

The internal memory of the AT69170E is based on a 32-bit architecture interface and is accessed by pages of 128 words. A word is 32 bit wide. The AT69170E has a size of 1024 pages.

Figure 8-6. Internal Memory Access

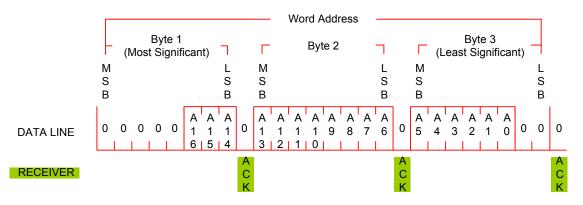

Therefore a word address is composed of 17 bits which means that 3 bytes are necessary to define a word address. The word address is encoded in a TWI frame as described herafter :

The word address must be shift left by two bits when encoded in a TWI frame. The unused bits must be cleared. The most significant byte of the word address is transmitted first and the most significant bit of a byte is transmitted first. Each byte of a word address must be acknowledged by the receiver device.

#### 8.3.7 Data Packets

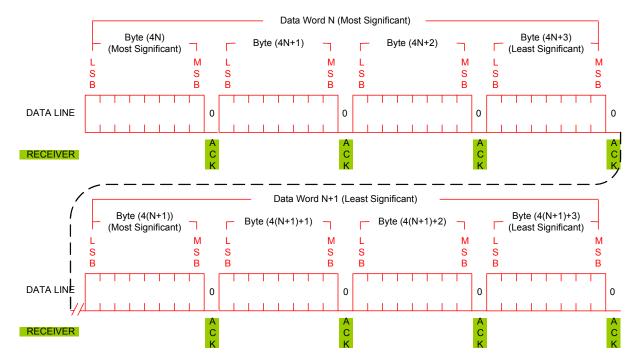

The data packets are composed of an integer number of words and are encoded in a TWI frame in the following manner :

#### Figure 8-8. TWI Data Packets format

The data packets encoded in TWI frames must be multiples of a data word.

The most significant word of a data packet and the most significant byte of a data word are transmitted first while <u>the least</u> <u>significant bit of a byte is transmitted first</u>.

#### 8.4 TWI Operations

#### 8.4.1 Write Operations

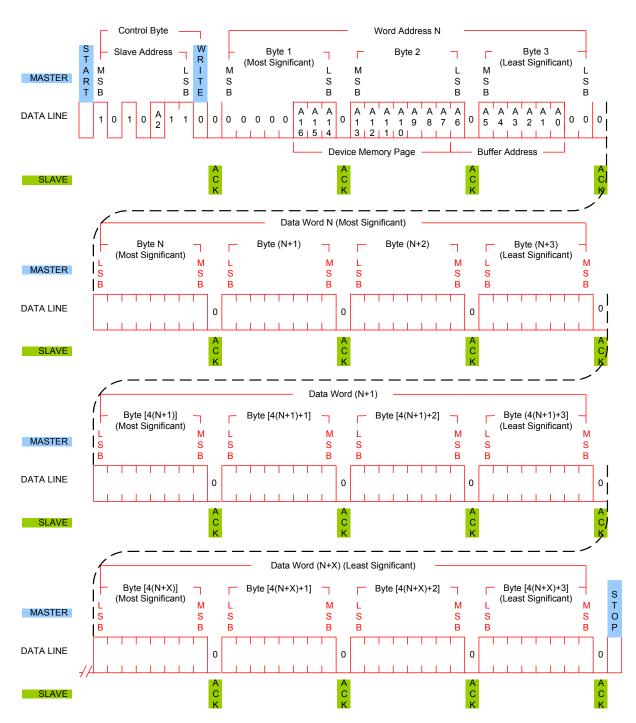

#### 8.4.1.1 Page Write Sequence

In programming mode, the internal memory of AT69170E is organized as 1024 pages of 128 words. This organization involves that it's not possible to program an amount of data lower than a page during a write operation. A page is written through an internal FIFO buffer of 128 words. The buffer is filled by a unique TWI sequence called Page Write sequence.

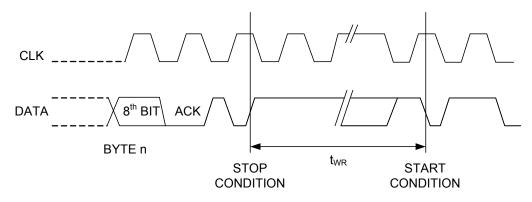

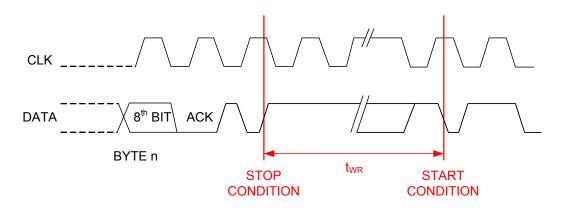

The Stop Condition of a Page Write sequence generates an internal write cycle whose maximum duration is  $T_{WR}$  (see Table 10-2 on page 31). During this time, the AT69170E ignores the DATA and CLK signals and does not acknowledge any bytes that a transmitter could send.

A power loss during the reception of a page write sequence does not damage the memory contents while a STOP condition is not received. However, the data packet is lost and must be resent by the master.

#### Figure 8-9. Write Cycle Timing

A Page Write frame is composed of the following fields :

- Control Byte

- Word Address

- Data Packet

The figure below describes a full page write sequence.

The Data Packet field contains all the words that will be written to the buffer during a Page Write Sequence. Only an integer number of words is allowed.

The Word Address field contains only the address of the first word of the Data Packet field. This address is shifted left by two bits and the two least significant bits of the Word Address field are cleared. The Data Word Address is copied by the device into an internal Address Counter. The rest of data word addresses are internally generated by an automatic incrementation of the Address Counter. This involves that the buffer must be written by a packet of contiguous data words locations. The number of data words can range from 1 to 128. In case, the buffer is not entirely filled, the unwritten words are set to "FF FF FF FF" by default.

The Word Address field is composed of two sections :

- the Device Memory Page

- the Buffer Address

The Device Memory Page ranges from 0 to 1023 while the Buffer Address ranges from 0 to 127.

A Page Write operation can be initiated to begin at any location within the buffer, but then the entire buffer only is written to the memory page during a Write Cycle.

To modify a byte within a memory page, it is therefore necessary to read the entire page, modify the byte within the page and perform a Page Write operation.

When the Buffer Address reaches the buffer boundary and additional locations are continued to be accessed, the address "rolls over" from the last word to the first word of the buffer and previous data words are overwritten.

See figure below for a description of the complete writing processus of the device memory.

Figure 8-11. Writing processus of the device memory

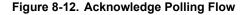

#### 8.4.1.2 Acknowledge Polling

Since the AT69170E does not acknowledge during a write cycle, this can be used to determine when the cycle is complete. This feature can be used to maximize bus thoughput. Once the stop condition for a Page Write sequence has been issued from the master, the device initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master sending a start condition followed by the control byte for a write command (R/W=0). If the AT69170E is still busy with the write cycle, then no ACK is returned. If the write cycle is complete, then the AT69170E returns the ACK and the master can then proceed with the next write or read operation. See figure below for the flow chart.

An alternative way to the acknowledge polling would be to wait for a t<sub>wR</sub> time before initiating the next write or read operation.

#### 8.4.2 Read Operations

For read operations, the internal memory of AT69170E is directly accessed by the TWI bus in 32-bit mode.

Internally the AT69170E contains an address counter that maintains the address of the last word accessed, incremented by one. Therefore, if the last access (either a read or a write) is done to address N, the next read operation will access data word from address N+1.

When address N reaches the device memory boundary, the address counter is incremented by one and the word address "rollsover" from the last to the first location of the memory.

Read operations are initiated in the same manner as write operations. There are two basic read operations :

- random read

- sequential read

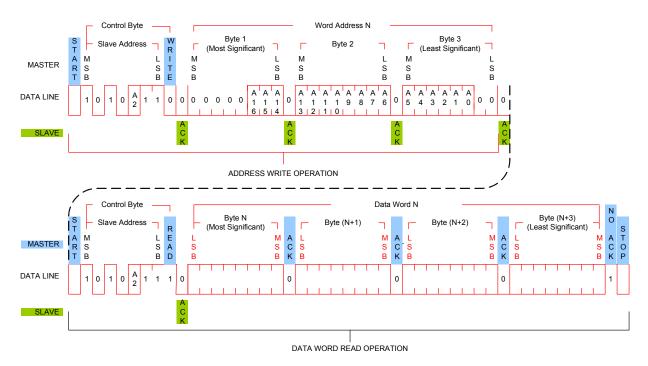

#### 8.4.2.1 Random Read

A random read requires a word address write sequence to load in the address counter. Once the control byte and the word address are clocked in and acknowledged by the AT69170E, the master must generate another start condition. Then, the master initiates a read sequence by sending a control byte with the  $R/\overline{W}$  bit set to "1". The AT69170E acknowledges the control byte and serially clocks out the data word. The master acknowledges all the bytes except the last one and then generates a stop condition to discontinue the transmission.

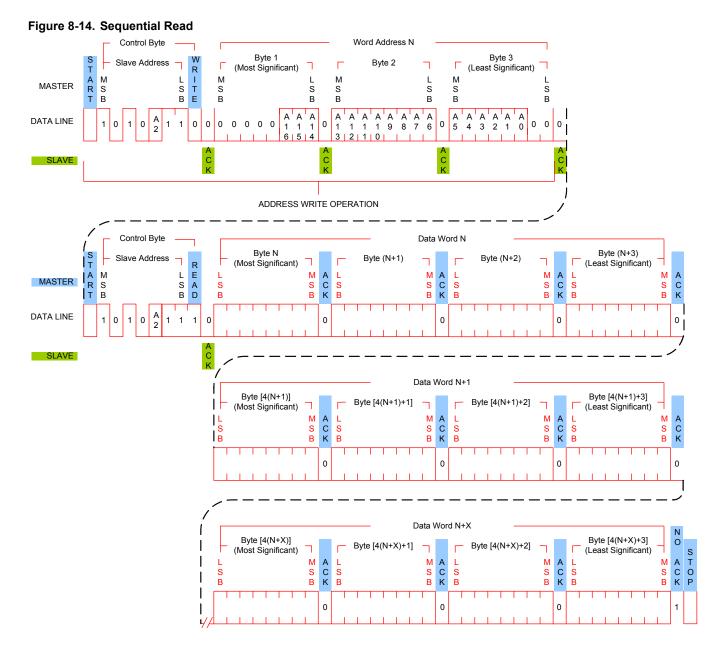

#### 8.4.2.2 Sequential Read

Sequential reads must be initiated as random read access. The first word is clocked out by AT69170E in the same manner as the random read mode. However, the master now responds with an acknowledge indicating it requires additional data. As long as the AT69170E receives an acknowledge, it continues to increment the word address and serially clock out sequential data words. The read operation is terminated by the master which does not acknowledge the reception of the last byte but does generate the stop condition.

The data output is sequential, with the word from address N followed by the word from address N+1. The address counter for read operations increments all the byte addresses of a data word, allowing the entire memory contents to be serially read during one operation. When the memory address limit is reached, the word address will "roll-over" from the last to the first location of the memory and the AT69170E continues to output data for each acknowledge received.

### 8.5 Special Functions

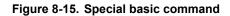

The AT69170E supports special functions that are accessible by commands sent through the TWI bus.

A Special Function command is obtained by the concatenation of special basic commands.

A special basic command frame is composed of the following fields :

- Control Byte

- Special Word Address

- Special Word Data

See figure below for a complete description of a special basic command frame.

A special basic command is differentiated from a normal read/write operation by means of the address field. The address word of read/write operations is shift left by two bits while the address word for special basic commands is not. The two least significant bits of the word address field are always cleared for read/write operations while they cannot be simultaneously equal to zero (A1A0 <> 0) for special basic commands.

The least significant byte of a data word and the least significant bit of a byte are transmitted first.

Special Functions commands allow to read or write configurations which are saved by means of internal fuse bits.

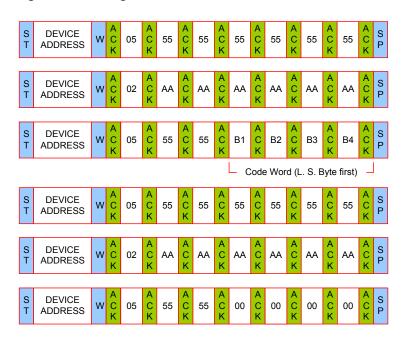

#### 8.5.1 Configuration Write Function

The Configuration Write Function is built by the concatenation of the following special basic commands :

- write "AA AA AA AA" at address "05 55 55"

- write "55 55 55 55" at address "02 AA AA"

- write "Word Code" at address "05 55 55"

- write "AA AA AA AA" at address "05 55 55"

- write "55 55 55 55" at address "02 AA AA"

- write "00 00 00 00" at address "05 55 55"

See figure below for a complete description of the Configuration Write Function

Figure 8-16. Configuration Write Function

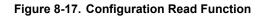

#### 8.5.2 Configuration Read Function

The Configuration Read Function is built by the concatenation of the following special basic commands :

- write "AA AA AA AA" at address "05 55 55"

- write "55 55 55 55" at address "02 AA AA"

- write "Code Word" at address "05 55 55"

- read "Data Word" from address "00 00 01"

- write "AA AA AA AA" at address "05 55 55"

- write "55 55 55 55" at address "02 AA AA"

- write "00 00 00 00" at address "05 55 55"

See figure below for a complete description of the Configuration Read Function.

The Special Functions are listed hereafter :

- Data Protection

- Chip Reset Polarity

- Full Chip Erase

#### 8.5.3 Special Functions List

#### 8.5.3.1 Data Protection

Atmel

The AT69170E has a "Write Protection" feature that disables data write capability to the memory. When the lock is activated, the data uploaded into the buffer is not written to the memory which preserves its content.

The write protection is managed by an internal fuse bit only as the AT69170E does not provide any write protect pin.

| Special Function Name   | Description                                          | Operation | Code Word   | Data Word                                                                                    |

|-------------------------|------------------------------------------------------|-----------|-------------|----------------------------------------------------------------------------------------------|

| Enable Data Protection  | Memory data protection is activated                  | Write     | 00 00 00 A0 |                                                                                              |

| Disable Data Protection | Memory data protection is deactivated                | Write     | 00 00 00 20 |                                                                                              |

| Data Protection Status  | Returns the state of the<br>Data Protection fuse bit | Read      | 00 00 00 F2 | 00 XX XX XX : Memory is not write<br>protected<br>FF XX XX XX : Memory is write<br>protected |

#### Table 8-2. Data protection commands

The "Enable Data Protection" command must be received by the memory device <u>before the last Page Write</u> sequence when a bitstream is programmed into the memory. If this condition is not fulfilled, the memory will not be correctly protected against write operations.

When the memory is write protected the only way to deactivate the memory protection is to apply the "Disable Data Protection" command.

The Full Chip Erase function does not operate when the memory is write protected.

The device is supplied with memory data protection deactivated.

#### 8.5.3.2 Chip Reset Polarity

The AT69170E allows the user to configure the polarity of the RESET pin as either active low or active high. This feature allows the memory device to work with various FPGA families. The device is supplied with the RESET pin active low.

The RESET polarity change is effective immediately. The written value can be verified by reading the Reset Polarity fuse bit.

| Special Function Name | Description                                      | Operation | Code Word   | Data Word                                                                                |

|-----------------------|--------------------------------------------------|-----------|-------------|------------------------------------------------------------------------------------------|

| Reset Active Low      | Chip Reset is active low                         | Write     | 00 00 00 FF |                                                                                          |

| Reset Active High     | Chip Reset is active high                        | Write     | 00 00 FF FF |                                                                                          |

| Chip Reset Status     | Returns the state of the Reset Polarity fuse bit | Read      | 00 00 00 F2 | XX [B2] XX XX<br>B2 = 0XXX XXXX : RESET Active Low<br>B2 = 1XXX XXXX : RESET Active High |

Table 8-3. Chip reset polarity commands

#### 8.5.3.3 Full Chip Erase

This command enables to erase the entire memory with a simple command. This command does not operate when the memory is write protected. The AT69170E does not acknowledge the TWI protocol during the memory erase cycle.

#### Table 8-4.Full chip erase

| Special Function Name | Description             | Operation | Code Word   | Data Word |

|-----------------------|-------------------------|-----------|-------------|-----------|

| Full Chip Erase       | Erase the entire memory | Write     | 00 00 00 B0 |           |

### 9. FPGA Dump Mode

#### 9.1 Operating Mode overview

The I/O and logic functions of any SRAM-based FPGA device are configured with a bitstream supplied by an external memory device. The FPGA's mode pins enable to select the way the bitstream is loaded into the FPGA. The bitstream can be supplied by a remote device or downloaded by the FPGA itself at power-on. In Master Serial Mode (Mode 0), the ATMEL's AT40K FPGA serie automatically downloads the bitstream from an external memory device without the need of an external smart controller. The AT69170E has been designed to support the Master Serial Mode of AT40K FPGA serie.

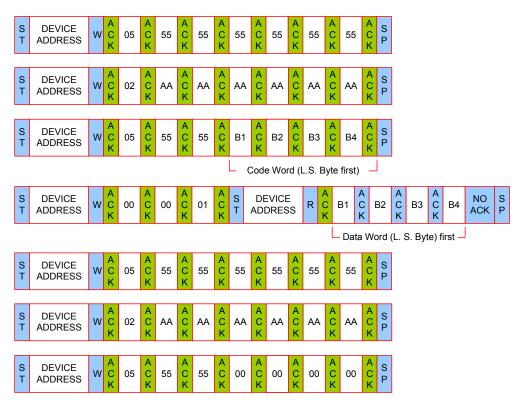

#### 9.2 Single Device Configuration

The interface between FPGA and AT69170E device is composed of signals READY, RESET, CE, CLK and DATA.

| Figure 9-1. Interface between FPGA and AT6 | 69170E for single device configuration |

|--------------------------------------------|----------------------------------------|

|--------------------------------------------|----------------------------------------|

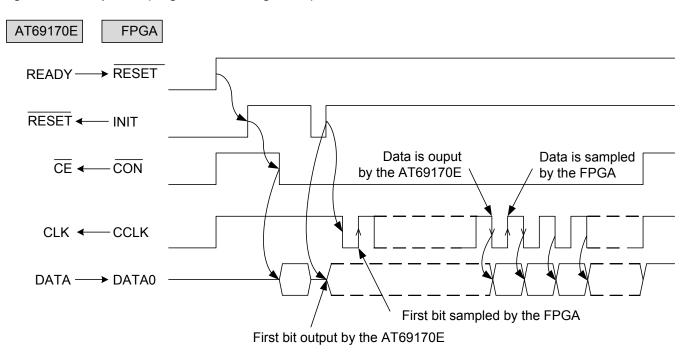

When the power is up, the AT69170E's internal address counter is reset and the READY pin is driven high, enabling the FPGA to leave its reset state and start the download process.

The  $\overrightarrow{\text{RESET}}$  and  $\overrightarrow{\text{CE}}$  pins of the AT69170E device control the tri-state buffer of the DATA output pin and the internal address counter. When the  $\overrightarrow{\text{RESET}}$  pin is driven low, regardless to the level of the  $\overrightarrow{\text{CE}}$  pin, the AT69170E resets its address counter and the DATA pin is set in tri-state mode.

If the CE pin is hold high when RESET pin is released (driven high), the address counter is disabled and the DATA output pin is set in tri-state mode.

if the CE pin is hold low when the RESET pin is released, the address counter and the DATA pin outputs the first data bit which is sampled by the FPGA on the first rising edge of the clock.

The AT69170E is clocked by the FPGA. The internal address counter is incremented on each clock's period. The data bits are output by the AT69170E on the falling edges of the clock so that they can be sampled by the FPGA on the rising edges of the clock.

Once the bitstream's download is complete, the  $\overline{\text{CON}}$  pin is released by the FPGA.

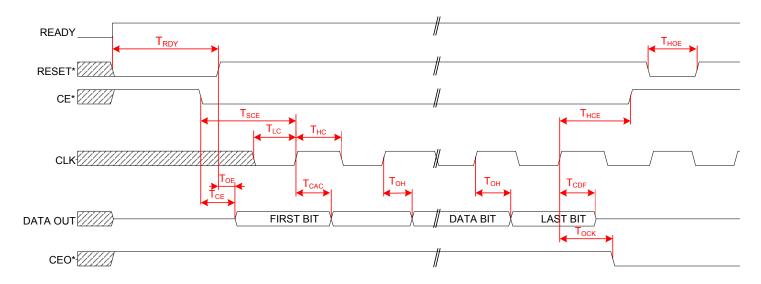

Figure 9-2. Dump Mode (Single Device Configuration)

An exemple of application schematic is provided on Figure 9.3 on page 25.

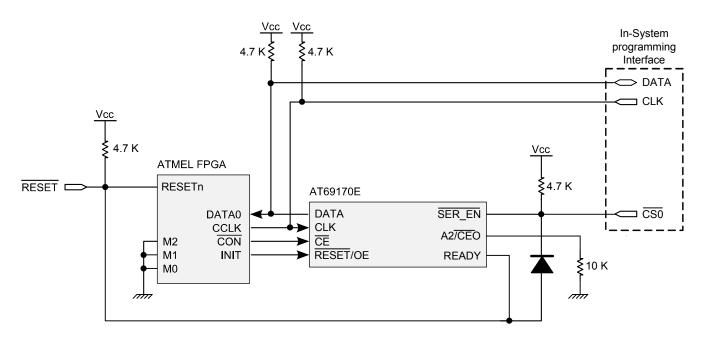

The SER\_EN pin enables to configure the AT69170E in TWI or DUMP mode. This pin is pulled up to Vcc to select the dump mode by default. A diode betwen READY and SER\_EN enables to set automatically the FPGA in the reset state when the TWI mode is selected in order to avoid signal contentions

Pull-up resistors are mandatory on DATA and CLK pins in TWI mode and on READY signal in DUMP mode.

Figure 9-3. Single Device Configuration Schematic

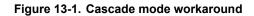

#### 9.3 Daisy Chain Configuration

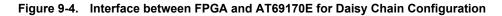

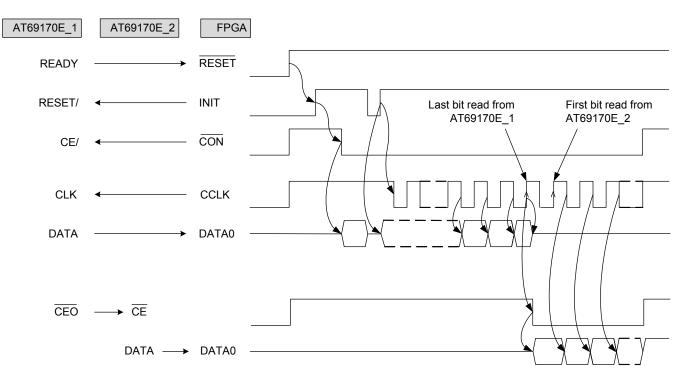

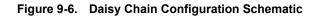

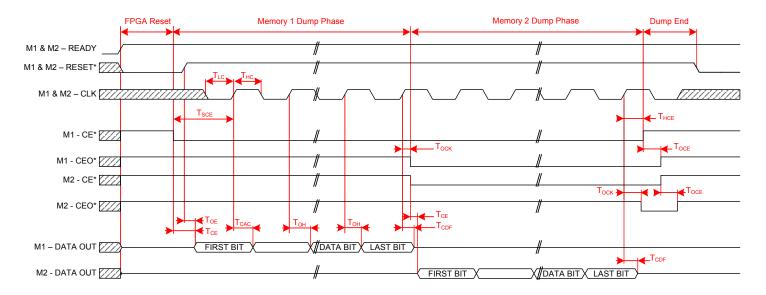

The interface between FPGA and AT69170E devices is composed of signals READY, RESET, CE, CLK, DATA and CEO.

For multiple FPGAs configured as a daisy-chain, or for FPGAs requiring larger configuration memory, it is possible to cascade several AT69170E devices.

Once the last bit from the first AT69170E is read, the device drives its  $\overline{CEO}$  pin low and disables its DATA pin to avoid signal contention with another AT69170E. The second AT69170E recognizes the Low level on its  $\overline{CE}$  pin and enables its DATA pin. The same scenario repeats for the following AT69170E devices.

It is possible to daisy chain up to 4 AT69170E devices.

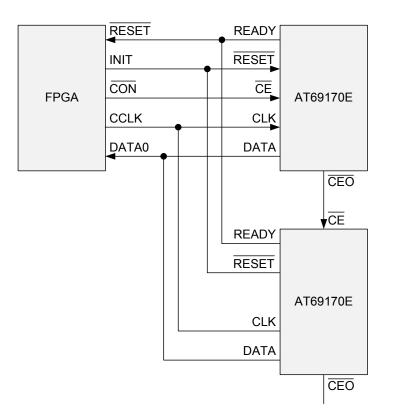

Figure 9-5. ump Mode (Daisy Chain Configuration)

An exemple of application schematic is provided on Figure 10. on page 28.

In TWI mode, it is not possible to select more than two AT69170E devices at a time. Therefore, two chip selects CS1 and CS2 must be defined, each one selecting two devices, in order to program the all the devices two by two.

Pull-up resistors are mandatory on DATA and CLK pins in TWI mode and on READY signal in DUMP mode.

### 10. Electrical Specifications

#### 10.1 Absolute Maximum Ratings\*

| Supply voltage to ground                                                       |

|--------------------------------------------------------------------------------|

| All input voltages (including NC pins) with respect to ground<br>0.5V to +4.6V |

| All output voltages with respect to ground                                     |

| -0.5V to VCC+ 0.5V                                                             |

| Storage temperature                                                            |

| ESD Voltage (MIL STD 883D Method 3015.3) > 4000V                               |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure between recommended DC operating and absolute maximum rating conditions for extended periods may affect device reliability.

### 10.2 Recommended DC Operating Conditions

| Symbol | Parameter                    | Min | Тур | Max | Unit |

|--------|------------------------------|-----|-----|-----|------|

| Vcc    | Supply Voltage               | 3.0 | 3.3 | 3.6 | V    |

| Temp   | Operating Temperature (Case) | -55 | 25  | 125 | °C   |

### 10.3 Capacitance (F=1MHz, 25°C)

| Symbol                          | Description              | Min | Тур | Max | Unit | Condition             |

|---------------------------------|--------------------------|-----|-----|-----|------|-----------------------|

| C <sub>IN</sub> <sup>(1)</sup>  | Input Capacitance        |     | 7   | 10  | pF   | V <sub>IN</sub> = 0V  |

| C <sub>OUT</sub> <sup>(1)</sup> | Output Capacitance       |     | 7   | 10  | pF   | V <sub>OUT</sub> = 0V |

| Note: 1. C                      | Guaranted but not tested |     |     |     |      |                       |

### **10.4 DC Characteristics**

| Symbol                            | Parameter                      | Condition                                                                                                | Min       | Max | Unit |

|-----------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------|-----------|-----|------|

| I <sub>IL</sub> , I <sub>IH</sub> | Low Level Input Current        | IV <sub>IN</sub> = 0 to 3.6V<br>Vcc=3.6V                                                                 | -1        | 1   | μA   |

| $I_{CSL}$ , $I_{CSH}$             | Cold Sparing Leakage Current   | V <sub>IN</sub> = 0 to 3.6V<br>Vcc = 0V                                                                  | -1        | 1   | μA   |

| I <sub>CCSB</sub>                 | Static consumption in TWI mode | SER_EN       = 0V         CE       >= Vcc-0.3V         f <sub>CLK</sub> = 0 MHz         Vcc       = 3.6V |           | 15  | mA   |

| I <sub>CCOP</sub>                 | Operating Current              | I <sub>OUT</sub> = 0 mA                                                                                  |           | 20  | mA   |

| V <sub>IL</sub>                   | Input Low Voltage              | Vcc = 3.0V                                                                                               | GND - 0.3 | 0.8 | V    |

| Symbol          | Parameter           | Condition                                    | Min       | Max     | Unit |

|-----------------|---------------------|----------------------------------------------|-----------|---------|------|

| V <sub>IH</sub> | Input High Voltage  | Vcc = 3.6V                                   | 2.2       | Vcc+0.3 | V    |

| V <sub>OL</sub> | Output Low Voltage  | I <sub>OL</sub> = 8 mA<br>Vcc = 3.0 to 3.6V  |           | 0.4     | V    |

| V <sub>OH</sub> | Output High Voltage | I <sub>OH</sub> = -8 mA<br>Vcc = 3.0 to 3.6V | Vcc - 0.4 |         | V    |

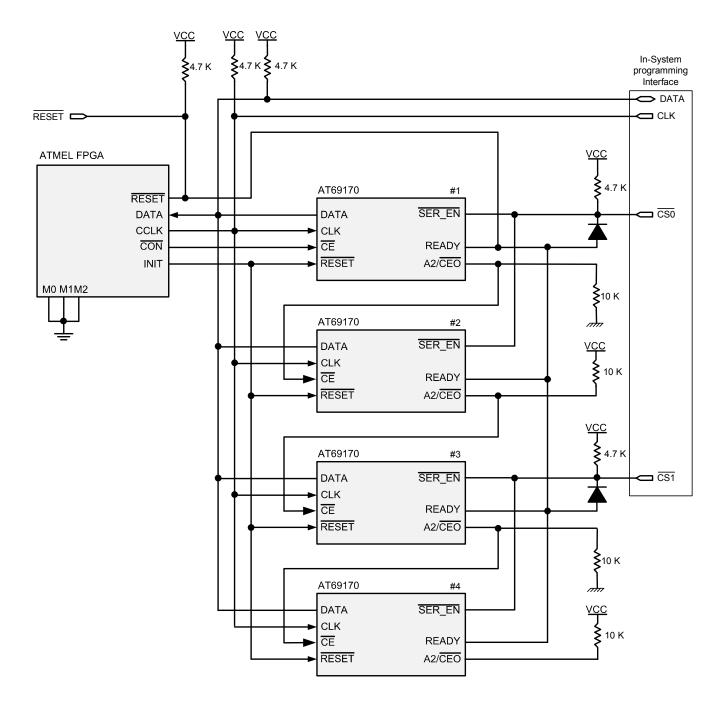

### 10.5 AC Characteristics

| Temperature Range:55 +125°C                    |

|------------------------------------------------|

| Supply Voltage:                                |

| Input and Output Timing Reference Levels: 1.5V |

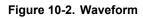

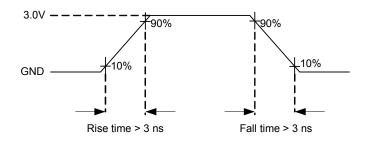

#### 10.5.1 Test Loads and Waveforms

#### 10.5.2 TWI Mode Characteristics

#### Table 10-1. TWI Data Transfer Timings

| Symbol              | Description                                                   | Min | Мах | Unit |

|---------------------|---------------------------------------------------------------|-----|-----|------|

| F <sub>CLOCK</sub>  | Clock Frequency                                               |     | 400 | KHz  |

| T <sub>LOW</sub>    | Clock Low Pulse Width                                         | 1.2 |     | μs   |

| T <sub>HIGH</sub>   | Clock High Pulse Width                                        | 1.2 |     | μs   |

| T <sub>AA</sub>     | Clock Low to Data Out Valid                                   |     | 0.9 | μs   |

| T <sub>BUF</sub>    | Time the bus must be free before a new transmission can start | 1.2 |     | μs   |

| T <sub>HD-STA</sub> | Start Hold Time from CLOCK                                    | 0.6 |     | μs   |

| T <sub>SU-STA</sub> | Start Setup Time from CLOCK                                   | 0.6 |     | μs   |

| T <sub>HD-DAT</sub> | Data In Hold Time                                             | 0.1 |     | μs   |

| T <sub>SU-DAT</sub> | Data In Setup Time                                            | 0.1 |     | μs   |

| T <sub>R</sub>      | Inputs Rise Time                                              |     | 0.3 | μs   |

| T <sub>F</sub>      | Inputs Fall Time                                              |     | 0.3 | μs   |

| T <sub>SU-STO</sub> | Stop Setup Time                                               | 0.6 |     | μs   |

| T <sub>DH</sub>     | Data Out Hold Time                                            | 0   |     | μs   |

Figure 10-4. Write Cycle Waveform

| Tab             | le 10-2. | Write Cycle Time |     |     |      |

|-----------------|----------|------------------|-----|-----|------|

| Sy              | mbol     | Description      | Min | Мах | Unit |

| t <sub>WF</sub> | २        | Write Cycle Time | 34  | 68  | ms   |

#### 10.5.3 Dump Mode Characteristics

#### Figure 10-5. Dump Mode Waveforms

#### Figure 10-6. Cascade Mode Waveforms

#### Table 10-3. Dump Mode Timings

| Symbol           | Description                                                        | Min | Max | Unit |

|------------------|--------------------------------------------------------------------|-----|-----|------|

| T <sub>OE</sub>  | Data Output Delay from RESET                                       |     | 35  | ns   |

| T <sub>CE</sub>  | Data Output Delay from CE                                          |     | 40  | ns   |

| T <sub>CAC</sub> | Data Output Delay from CLK                                         |     | 40  | ns   |

| Т <sub>ОН</sub>  | Data Hold from $\overline{CE}$ , $\overline{RESET}$ , or CLK       | 0   |     | ns   |

| T <sub>DF</sub>  | Data Float Output Delay from $\overline{CE}$ or $\overline{RESET}$ |     | 30  | ns   |

| T <sub>CDF</sub> | Data Float Output Delay from CLK                                   |     | 30  | ns   |

| Т <sub>ОСК</sub> | CEO Output Delay from CLK                                          |     | 35  | ns   |

| T <sub>OCE</sub> | $\overline{CEO}$ Output Delay from $\overline{CE}$                 |     | 25  | ns   |

| T <sub>OOE</sub> | CEO Output Delay from RESET                                        |     | 25  | ns   |

| T <sub>LC</sub>  | CLK Low Time                                                       | 20  |     | ns   |

| T <sub>HC</sub>  | CLK High Time                                                      | 20  |     | ns   |

| T <sub>SCE</sub> | CE Setup Time to CLK<br>(to guarantee proper counting)             | 20  |     | ns   |

| T <sub>HCE</sub> | CE Hold Time from CLK<br>(to guarantee proper counting)            | 5   |     | ns   |

| T <sub>HOE</sub> | RESET pulse width that guarantees the counter is reset             | 60  |     | ns   |

| F <sub>MAX</sub> | Maximum Clock Frequency                                            |     | 15  | MHz  |

| T <sub>RDY</sub> | RESET hold Delay after READY                                       | 0   |     | ns   |

# 11. Ordering Information

| Ordering Code  | Package | Flow                |

|----------------|---------|---------------------|

| AT69170E-DT-E  | FP18    | Engineering Samples |

| AT69170E-DT-MQ |         | QMLQ                |

| AT69170E-DT-SV |         | QMLV                |

|     | м                    |       | TN        | <u></u>   |

|-----|----------------------|-------|-----------|-----------|

|     | M<br>Min             | Max   | IN<br>Min | сн<br>Мах |

| A   | 1.14                 | 2, 92 | , 045     | . 115     |

| b   | 0, 38                | 0, 48 | ,015      | , 019     |

| С   | 0, 08                | 0, 15 | , 003     | , 006     |

| D   |                      | 12.45 |           | . 490     |

| E   | 6, 22                | 8, 00 | . 245     | . 315     |

| E2  | 3, 30                |       | , 130     |           |

| E3  | 0, 76                |       | , 030     |           |

| K   | 0, 20                | 0, 39 | , 008     | , 015     |

| k1  | k1 0.63 BSC .025 BSC |       | BSC       |           |

| e   | 1, 27                | BSC   | , 050     | BSC       |

| L   | 6, 35                | 9, 40 | , 250     | . 370     |

| Q   | 0, 66                | 1.14  | , 026     | , 045     |

| S   |                      | 1.14  |           | . 045     |

| S 1 | 0.13                 |       | , 005     |           |

| Ν   | 1                    | 8     |           |           |

Note: The package lid is connected to GND

# 13. Active Errata

### 13.1 A2 pin input not properly processed

#### Issue: It's not possible to map the device with two TWI addresses by means of the A2 pin.

Workaround: There are two ways to work around this issue :

- implement only one AT69170E device on the same TWI bus,

- select only one AT69170E at a time by means of the SER\_EN pin if two AT69170E are implemented on the same bus.

If several memory devices need to be cascaded, the following schematic may be used.

#### 13.2 TWI address acknowledgement

Issue: The device acknowledges all TWI addresses whatever the value of R/W bit in the control byte, from 00h to 7Fh except for addresses 04h, 05h, 06h, 07h, 78h, 79h, 7Ah, 7Bh while it should only acknowledge its own TWI addresses given in the table below.

| A2 pin | TWI Device Address |

|--------|--------------------|

| GND    | 53 h               |

| VCC    | 57 h               |

However, no TWI write operations are processed by the memory device when the TWI device address supplied by the master does not match its own addresses but this issue may generate address conflicts with devices sharing the same TWI bus.

**Workaround:** Do not share the TWI bus with devices whose address is in the range of addresses acknowledged by the AT69170E.

#### 13.3 TWI page write corruption

# Issue: The very first page written just after the power on is always corrupted whatever the written page. All pages to follow are then correctly written.

Workaround: There are at least three ways to work around this issue.

a) Send a dummy page write sequence before the first valid page write. The dummy page write is corrupted but the first valid page write is correctly processed. The dummy page and the first valid page writes must be done of course at the same page number. A dummy page write may consist for instance to write only the first word of the page.

b) Send the very first page write twice so that the first is corrupted but not the second one.

c) Send a Full Chip Erase command before writing the first valid page write.

#### 13.4 TWI write frequency limitation

#### Issue: The TWI write does not work at a frequency greater than 200 Khz

Workaround: The TWI write frequency must be limited to 200 Khz inclusive.

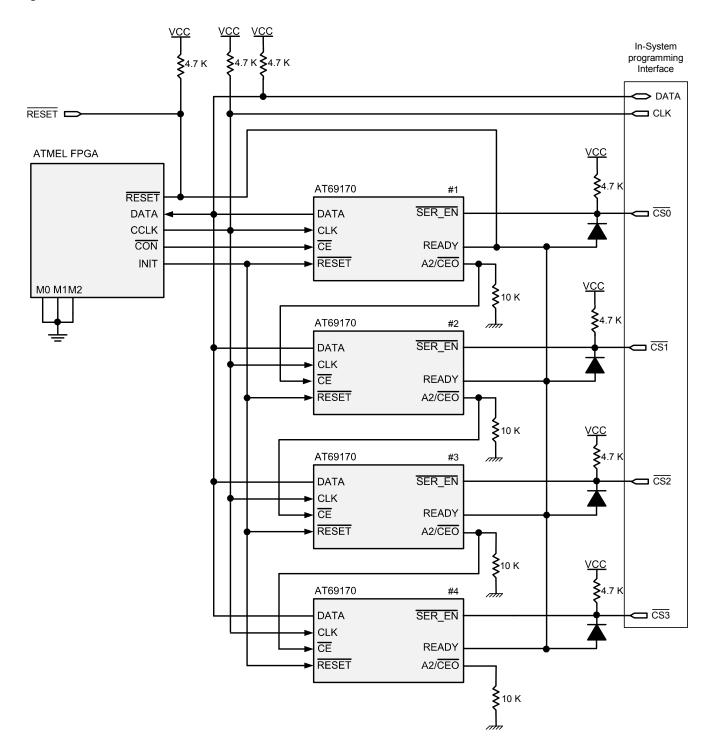

#### 13.5 READY signal may not rise

Issue: Depending on the mode the device is powered on, the READY signal may not rise. In this case the device is inoperative in both TWI and DUMP modes. Workaround: To guarantee the rise of the READY signal, the following hardware condition must be applied when the device is powered on : RESET = 0 and SER\_EN = 1. Whatever the RESET polarity configuration, this hardware condition is true. Once the READY signal has risen, the TWI mode can be selected by setting the SER\_EN pin to ground.

### 13.6 READY signal drops briefly at power off

- Issue: Some applications need to switch the memory device off while keeping the FPGA device running. There is then an incompatibility between the memory device and those applications as the FPGA is reset at the time the device memory is switched off and unable to re-load its configuration.

- **Workaround:** The implementation of an input OR gate with open collector between the READY and RESETn signals as described in the schematic below enables to solve the problem. At power up, the FPGA sets the CON and INIT signals to ground. As soon as the memory device releases the READY signal, the FPGA device exits from reset state and downlaods its configuration. At the end of the download, the FPGA device sets the CON signal to VCC enabling the memory device to be switched off whitout resetting the FPGA.

Figure 13-2. Single Device Configuration (Workaround Schematic)

# 14. Revision History

| Doc. Rev. | Date    | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F         | 11/2013 | Update : Status changed from PRELIMINARY to DATASHEET (Complete) on first page<br>Update : Total Dose parameter in "Features" section<br>Update : Figure 8-6 on page 11<br>Update : Figure 8-11 on page 15<br>Update : Figure 9-3 on page 24<br>Update : Figure 9-5 on page 26<br>Update : Figure 9-6 on page 27<br>Update : Figure 13-1 on page 36<br>Update : Figure 13-2 on page 38<br>Add-on: "Test Loads and Waveforms" on page 29<br>Add-on : "READY signal drops briefly at power off" on page 38 |

| E         | 02/2013 | Initial Document Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# Atmel

# Enabling Unlimited Possibilities®

#### Atmel Corporation

1600 Technology Drive San Jose, CA 95110 USA Tel: (+1) (408) 441-0311 Fax: (+1) (408) 487-2600 www.atmel.com Atmel Asia Limited Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Roa Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369

#### Atmel Munich GmbH

Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621 Atmel Japan G.K.

16F Shin-Osaki Kangyo Bldg 1-6-4 Osaki, Shinagawa-ku Tokyo 141-0032 JAPAN **Tel:** (+81) (3) 6417-0300 **Fax:** (+81) (3) 6417-0370

© 2012 Atmel Corporation. All rights reserved. / Rev.: 7752F-AERO-11/13

Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.