This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

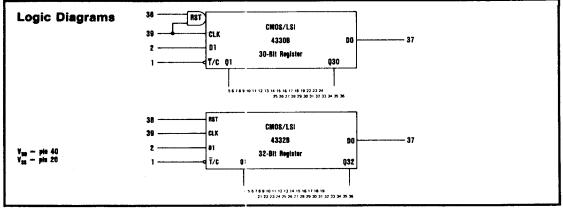

# CMOS MD4330B/MD4332B 30/32 Segment LCD Driver

FEB. 1985

#### Features

- · CMOS Low power

- 3 to 18 volt operation

- On-chip wave-shaping

- High-speed (typ. 3 MHz) shift register

- Std. 40-pin Dual-In-Line packages

#### Pin Names

- DI Serial Data Input

- DO Serial Data Output

- CLK Clock (positive transition) Input

- RST Master Reset (active HIGH) Input

- T/C True/Complement (active LOW) Input

- Q1 thru Q32 True/Complement Outputs

|                                                          | Pin Conr        | ections                          |                 |  |  |  |  |

|----------------------------------------------------------|-----------------|----------------------------------|-----------------|--|--|--|--|

| MD433                                                    | 0B              | MD4                              | 1332B           |  |  |  |  |

|                                                          | 40 D VDD        | T/C d                            |                 |  |  |  |  |

| D1 <b>C</b> 2                                            | 39 🗖 CLK        | D1 <b>C</b> 2                    | 39 CLK          |  |  |  |  |

| NC C 3                                                   | 38 📮 RST        | NC 🕻 3                           | 38 🗗 RST        |  |  |  |  |

|                                                          | 37 🏳 DO         | Q1 <b>C</b> 4                    | 37 📮 do         |  |  |  |  |

| Q1 <b>Q</b> 5                                            | 36 📮 0.30       | O2 🕻 5                           | 36 🗖 032        |  |  |  |  |

| 02 4 6                                                   | 35 📮 029        | O3 🕻 6                           | 35 📮 031        |  |  |  |  |

| O3 <b>Q</b> 7                                            | 34 🗖 028        | Q4 <b>C</b> 7                    | 34 🏳 (130       |  |  |  |  |

| Q4 <b>Q</b> 8                                            | 33 🖸 0.27       | Q5 🗖 8                           | 33 📮 029        |  |  |  |  |

| Q5 <b>Q</b> 9                                            | 32 🖸 0.26       | Q6 🖸 9                           | 32 🖸 0.28       |  |  |  |  |

| Q6 <b>Q</b> 10                                           | 31 🖸 025        | Q7 🚺 10                          | 31 🖸 027        |  |  |  |  |

| 07 <b>Q</b> 11                                           | 30 📮 0.24       | Q8 🖸 11                          | 30 🗖 0.26       |  |  |  |  |

| Q8 <b>Q</b> 12                                           | 29 🗗 Q23        | Q9 🖸 12                          | 29 🖸 025        |  |  |  |  |

| Q9 <b>Q</b> 13                                           | 28 🖸 0.22       | Q10 🖸 13                         | 28 🖸 024        |  |  |  |  |

| Q10 <b>Q</b> 14                                          | 27 🖸 021        | 011 🗖 14                         | 27 🖸 023        |  |  |  |  |

| Q11 Q15                                                  | 26 🖸 020        | Q12 🖸 15                         | 26 🖸 022        |  |  |  |  |

| Q12 <b>Q</b> 16                                          | 25 <b>Q</b> Q19 | Q13 <b>Q</b> 16                  | 25 <b>D</b> Q21 |  |  |  |  |

| Q13 <b>Q</b> 17                                          | 24 <b>D</b> Q18 | Q14 <b>G</b> 17                  | 24 🖸 Q20        |  |  |  |  |

| Q14 🖸 18                                                 | 23 017          | Q15 <b>G</b> 18                  | 23 🖸 Q19        |  |  |  |  |

| Q15 <b>[</b> 19                                          | 22 <b>D</b> Q16 | Q16 <b>Q</b> 19                  | 22 018          |  |  |  |  |

| VSS <b>C</b> 20                                          | 21 D NC         | VSS <b>C</b> 20                  | 21 017          |  |  |  |  |

| Ordering Information                                     |                 |                                  |                 |  |  |  |  |

| MD4330BC 40-Pin Ceramic DIP<br>MD4330BE 40-Pin Epoxy DIP |                 |                                  |                 |  |  |  |  |

| MD4332BC<br>MD4332BE                                     |                 | 40-Pin Ceramie<br>40-Pin Epoxy [ |                 |  |  |  |  |

### Description

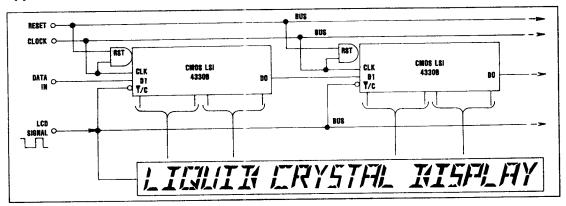

The MD4330B and 4332B are CMOS 30- and 32-bit static shift registers incorporating selectable true/ complement outputs for each bit. These devices are well suited to drive LCD readouts directly since the AC signals required for the display may be generated simply by applying a low frequency signal directly to the True-Complement input pin and to the backplane of the display. One of these devices can drive four 7-segment displays or two 14-segment alphanumeric displays plus decimal points or two 16-segment alphanumeric displays directly.

| Item                         | Symbol           | Limits                       | Unit |

|------------------------------|------------------|------------------------------|------|

| DC Supply Voltage            | V <sub>DD</sub>  | -0.5 to 18                   | Vdc  |

| Input Voltage                | V <sub>IN</sub>  | -0.5 to V <sub>DD</sub> +0.5 | Vdc  |

| DC Current Drain per Pin     | 1                | 10                           | mAdc |

| Operating Temperature Ranges | ТА               | -40 to 85                    | °C   |

| Storage Temperature Range    | T <sub>STG</sub> | -65 to 125                   | °C   |

### Absolute Maximum Rating (Referenced to VSS)

#### **Functional Description**

The 4330B and 4332B are CMOS/LSI static shift registers designed to drive all types of LCD readouts directly or as serial-to-parallel converters where both the true and complementary parallel outputs are available.

The circuits accept a serial input DI which is shifted into the register on the positive transition of the clock (CLK) input. A feature of these circuits is that the clock input and the true/complement control (T/C) input have wave-shaping circuits to ensure fast edges on-chip regardless of the shape of the incoming signals.

The 4330B type also has the reset (RST) input gated with the clock input for synchronous reset on the positive transition of the clock. The 4332B has asynchronous rese( (RST) inputs which are active logic-level HIGH.

The parallel outputs of the shift registers are available in either true or complementary form dependent on the state of the true/complement control input. When input is logic-level LOW, the true form is available at all parallel outputs and when the input goes HIGH, the parallel outputs immediately revert to the complementary form of the data stored in each register. This action is independent of the clock input condition. A serial data (D<sub>o</sub>) output is provided for applications using longer shift registers, etc. This output is the true form of the last stage of the register.

### Application

#### 3-32

| Characteristic                |                 | Symbol           | Test        |                          |      | Limits |       |      | Units |

|-------------------------------|-----------------|------------------|-------------|--------------------------|------|--------|-------|------|-------|

|                               | зушьог          | Conditions       | Vo<br>Volts | V <sub>DD</sub><br>Volts | Min. | Тур.   | Max.  |      |       |

| Quiescent Device<br>Current   |                 | ١L               |             |                          | 5    | -      | 0.5   | 50   |       |

|                               |                 |                  |             |                          | 10   | -      | 1     | 100  | μΑ    |

| Output<br>Voltage             |                 | V <sub>OL</sub>  |             |                          | 5    | -      | 0     | 0.01 |       |

|                               | Low-Level       |                  |             |                          | 10   | -      | 0     | 0.01 |       |

|                               | Allah Asuat     | V <sub>OH</sub>  |             |                          | 5    | 4.99   | 5     | _    |       |

|                               | High-Level      |                  |             |                          | 10   | 9.99   | 10    | -    |       |

|                               |                 |                  |             | 0.8                      | 5    | 1.5    | 2.25  | -    |       |

| Noise Immunity<br>(Any Input) | V <sub>NL</sub> |                  | 1.0         | 10                       | 3    | 4.5    | -     | 1    |       |

|                               | V <sub>NH</sub> |                  | 4.2         | 5                        | 1.5  | 2.25   | -     | -    |       |

|                               |                 |                  | 9.0         | 10                       | 3    | 4.5    | -     |      |       |

| Output Drive<br>Current       |                 | 1 61             | N-Channel   | 0.5                      | 5    | 0.8    | 1.7   | -    |       |

|                               |                 | I <sub>D</sub> N | N-Channel   | 0.5                      | 10   | 1.0    | 3.0   | -    | ]     |

|                               |                 |                  | P-Channel   | 4.5                      | 5    | 0.35   | -0.9  | -    | mA    |

|                               |                 | Ι <sub>D</sub> Ρ |             | 9.5                      | 10   | -0.8   | - 1.9 |      |       |

|                               |                 | I <sub>D</sub> N | N-Channel   | 0.5                      | 10   | 50     | 250   | -    |       |

|                               |                 | I <sub>D</sub> N | P-Channel   | 9.5                      | 10   | -50    | 250   | -    | μΑ    |

| Input Currer                  | it              | lj               |             |                          |      | -      | 10    | _    | pА    |

# D.C. Electrical Characteristics at $T_{A}{=}\ 25^{\circ}C$

## A.C. Electrical Characteristics at $T_{A}=$ 25°C, $C_{L}=$ 50 pF

Typical Temperature Coefficient for all values of  $V_{DD} = 0.3\%/°C$ . All input rise and fall times = 20 ns.

| Characteristic               | Symbol                            | Test                           | Limits                   |      |      |      |       |

|------------------------------|-----------------------------------|--------------------------------|--------------------------|------|------|------|-------|

|                              |                                   | Conditions                     | V <sub>op</sub><br>Volts | Min. | Тур. | Max. | Units |

| Propagation Delay<br>Time    | t <sub>PHL</sub> t <sub>PLH</sub> |                                | 10                       | -    | 300  | -    | ns    |

| Transition Time              | t <sub>THL</sub>                  | D OUT ( $CL = 50 \text{ pF}$ ) | 10                       | - 1  | 70   | 130  | ns    |

|                              | t <sub>TLH</sub>                  | Q OUT (CL = 15 pF)             | 10                       | -    | 300  | -    | ns    |

| Maximum Clock<br>Frequency   | f <sub>CL</sub>                   |                                | 10                       | 1.0  | 3.0  | _    | MHz   |

| Minimum Clock<br>Pulse Width | t <sub>WL</sub> t <sub>WH</sub>   |                                | 10                       | -    | 200  | _    | ns    |

| Minimum Reset<br>Pulse Width | t <sub>WH(R)</sub>                |                                | 10                       | -    | 200  | -    | ns    |

| Input Capacitance            | Cı                                | Any Input                      |                          | - 1  | 5    | -    | pF    |