# **COLOR VIDEO CONTROLLER**

#### PRELIMINARY INFORMATION

#### MAIN FEATURES

Video rates up to 135MHz

Programmable pixel depth and multiplexing ratios

1, 2, 4 and 8-bit pseudo color pixels

15, 16 or 24-bit true color support

Software configurable Video Timing Generator

Comprehensive video RAM framestore manager

On-chip phase-locked loop pixel clock generator

64×64 pixel ×3 color hardware cursor

Triple 8-bit DACs

Triple 256×8 anti-sparkle palette RAM

Support for split SAM VRAMs

Software and hardware compatible with IMS G332

### BENEFITS

Reduced component count

Reduced system power consumption

Enhanced system flexibility

Easy upgradeabilty

All digital signals below RFI regulated frequency

Reduced system design time

#### **APPLICATIONS**

High resolution graphics and imaging Broadcast/CC television systems X-terminals Low cost workstations High-resolution color add-in boards 'Processor Direct' PC graphics systems

#### DESCRIPTION

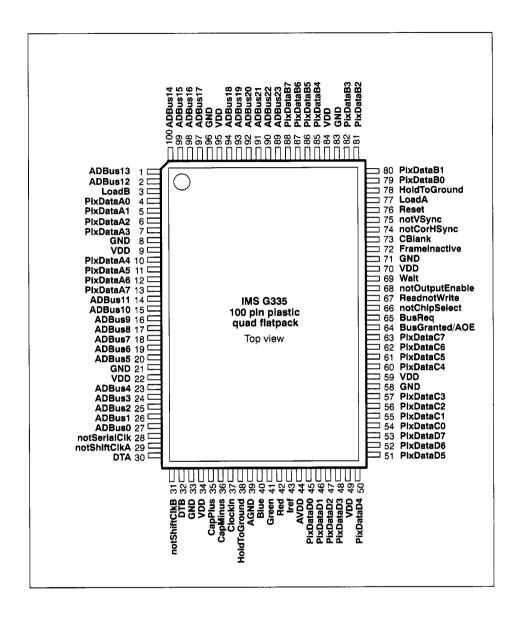

The IMS G335 is a very high performance CMOS device, integrating a triple 8-bit palette-DAC with all the control functions required to produce high resolution color graphic displays. It offers a number of significant enhancements over the older IMS G332.

The IMS G335 supports multiple pseudo color and true color display formats, and offers enormous flexibility in system design and use.

August 1992

42 1559 00

# **TABLE OF CONTENTS**

| 13.1  | Introduction                      | 165 |

|-------|-----------------------------------|-----|

| 13.2  | Pin function reference guide      | 169 |

| 13.3  | Register function reference guide | 171 |

| 13.4  | Clocks                            | 172 |

| 13.5  | The micro port                    | 173 |

| 13.6  | Video Timing Generator            | 174 |

| 13.7  | Framestore manager                | 187 |

| 13.8  | The Pixel Port                    | 197 |

| 13.9  | Hardware cursor                   | 206 |

| 13.10 | Anti-sparkle color palette        | 209 |

| 13.11 | Checksum registers                | 210 |

| 13.12 | The video DACs                    | 211 |

| 13.13 | Register reference guide          | 212 |

| 13.14 | Timing reference guide            | 216 |

| 13.15 |                                   |     |

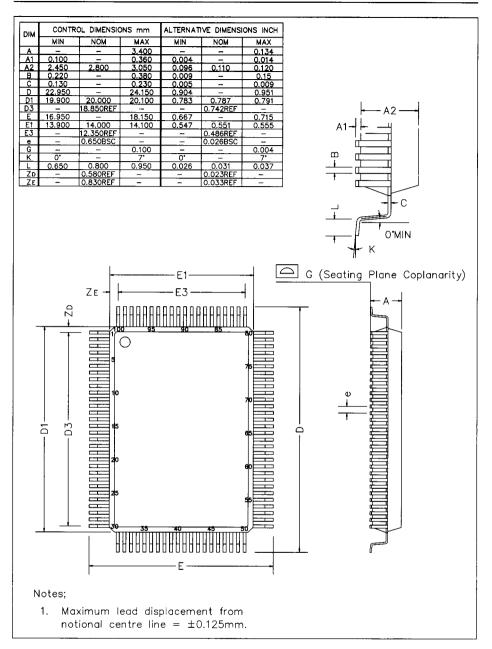

| 13.16 | Package specifications            | 232 |

| 13.17 | Ordering information              | 234 |

## 13.1 Introduction

The IMS G335 provides all the necessary functions to control real-time operation of a raster scan video display, using dual-ported video RAMs.

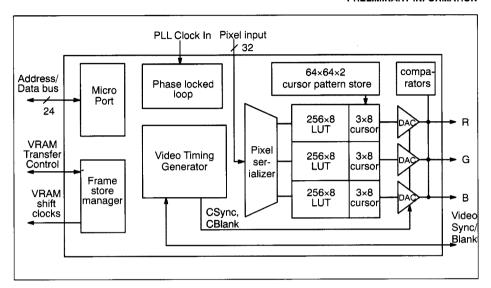

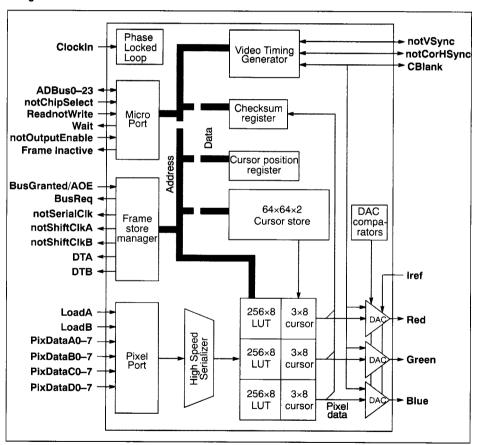

The device consists of a 32-bit variable format multiplexed pixel interface, a programmable video timing generator (VTG), a 256 location color lookup table (LUT) with variable addressing modes, triple 8-bit video Digital-to-Analogue Convertors (video DACs), a  $64 \times 64 \times 2$  bit cursor store and 3 location cursor LUT, a programmable cursor positioning/insertion controller, a video memory control system and phase-locked loop clock generator.

A brief description of each functional block is given in Sections 13.1.1 to 13.1.8; for more detailed information please refer to the relevant section in the datasheet.

### Software and hardware compatibility with IMS G332

The IMS G335 has been designed to be software and hardware compatible with the IMS G332. Pins used for new signals on the IMS G335 were defined as **HoldToGround** on the IMS G332, so new devices can be drop-in replacements. A number of features have been added to the IMS G335 to further improve flexibility and simplify design compared to the IMS G332. **The IMS G335 is recommended for all new designs.**

Figure 13.1 IMS G335 Block Diagram

### 13.1.1 Clocks

An on-chip phase-locked loop clock generator allows the IMS G335 to be driven from a low speed clock in the 5MHz to 10MHz range, which is internally multiplied by a user-specified factor to achieve video data rates. The controller can be clocked by a full rate system clock if desired, although at a reduced frequency compared to that achievable with the PLL.

### 13.1.2 Micro Port

The entire IMS G335 register space is read/write accessible via the micro port. This is a 24-bit wide synchronous interface, with multiplexed address and data, for memory-mapped access to all registers. The micro port interface is also used to provide the VRAM shift register transfer address.

To simplify the micro interface design all IMS G335 micro port control signal pulse widths are independent of the system clock frequency. Total read/write cycle times are system frequency dependent and a wait pin is provided to allow synchronization between the IMS G335 clock regime and that of the processor or interface bus.

### 13.1.3 Video timing generator

The video timing generator is a programmable finite state machine which uses a set of screen description parameters to produce the monitor sync and DAC blanking signals as well as the video RAM shift clock signals. It can be configured to be the system master or, as a slave, to lock onto an external signal which is already synchronous or has been previously genlocked. This may be from another SGS-THOMSON CVC, giving the potential for multiple, synchronous video systems. The timing generator runs at one quarter of the video dot rate and the screen description parameters therefore have a resolution of four pixel periods.

A new interlace mode has been added to the IMS G335, permitting displayed fields to have an even number of lines. Another new option allows line sync signals to be maintained during frame flyback, as required by newer multisync monitors.

### 13.1.4 Framestore manager

All the requirements of supporting a video RAM framestore are met by the IMS G335. The framestore manager uses framestore description parameters to control VRAM row transfers to maintain a constant supply of pixels to the pixel interface. Support is provided for both synchronous and asynchronous (split SAM) row transfers.

For synchronous reloads, the IMS G335 supplies the refresh address and the transfer strobes, synchronized to the VRAM SC signals, so that a packed pixel framestore can be implemented regardless of the variations in screen format and framestore architecture.

#### 13.1.5 Pixel Port

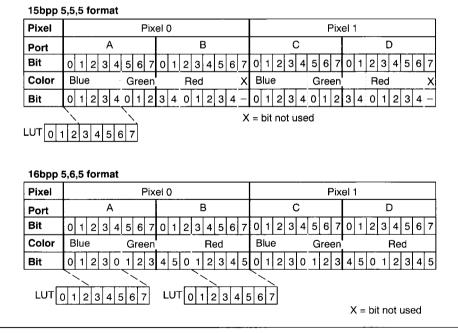

High pixel rates are achieved by multiplexing the VRAM outputs into a 32 bit wide pixel port, the multiplex ratio being dependent on the bpp format selected. An interleaved memory system is supported with all necessary signals in order to give the maximum possible multiplexing ratio in each case. The IMS G335 supports 24, 16, 15, 8, 4, 2 and 1 bpp.

### **Pixel Sampling**

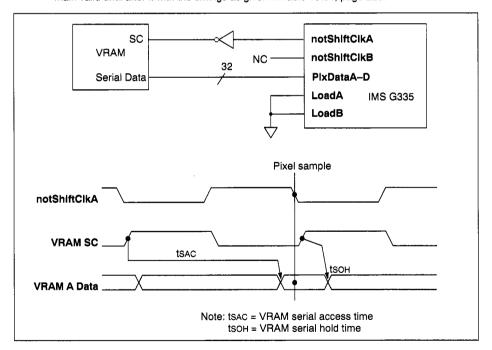

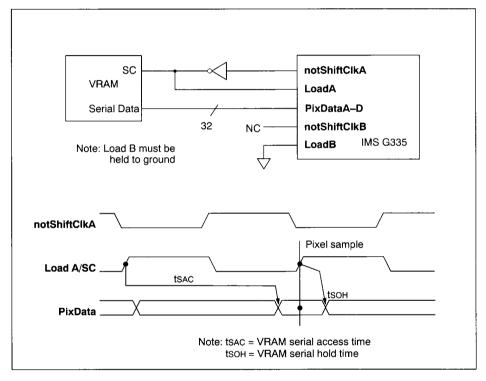

The IMS G335 provides two pixel sampling modes; internal sampling, where the VRAM data is sampled by internally generated strobes and external sampling where the VRAM data is latched by externally supplied signals.

External sampling simplifies high speed system design and allows higher sampling speeds to be achieved through shorter VRAM data set-up and hold times. Internal sampling provides backwards compatibility with the IMS G332 pixel sampling method. In both modes the IMS G335 automatically adjusts the shift clock frequency, along with the multiplex ratio of the port, according to the bits per pixel mode selected. Further details are given in Section 13.8.

#### **Pixel formats**

The XGA graphics standard from IBM includes a 16-bit true color format, split 5,6,5 between the red, green and blue fields. This mode is supported by the IMS G335 and is targetted towards cost-sensitive multimedia applications. It is selectable through Control Register A, and replaces the 6,6,4 format supported by the IMS G332.

#### 13.1.6 Hardware Cursor

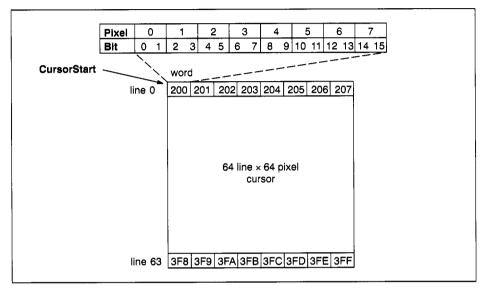

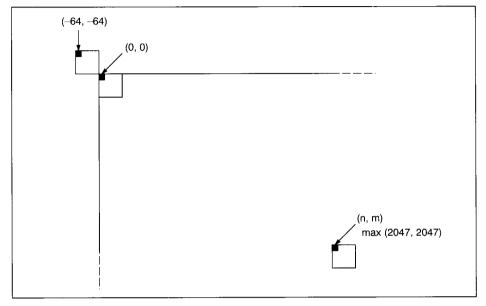

The hardware cursor is a complete system. The cursor store and lookup table are memory mapped, its position being modified by a single register access which can occur at any time, becoming valid at the next frame scan. The cursor position is stored in 2's complement relative to the top left pixel on the screen and is independent of monitor specifications.

The IMS G335 includes pixel complement and XGA cursor pixel options. Pixel complement ensures that cursor pixels are always visible, whatever the background color, by displaying the complement of the background pixel color. The XGA option provides support for XGA standard cursor pixel mapping.

# 13.1.7 Anti-sparkle Color Palette

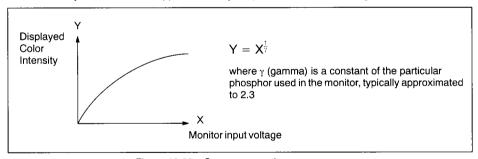

The serialized pixels are used as addresses into a triple 256×8 pipelined RAM. In pseudo color modes one address is applied to all three RAMs giving a maximum of 256 simultaneous colors out of a possible 16·4 million. In true color each RAM is independently addressed for gamma correction of up to 16.4 million simultaneous colors. The palette has an anti-sparkle mechanism which reduces the visible effect of palette updates during display.

### 13.1.8 Video DACs

The three 8-bit DACs drive RS-170 level signals directly into a  $37.5\Omega$  load. They are blanked with programmable setup, internally by the VTG, externally by the **CBlank** pin or by a combination of the two. Composite Sync may be added to all three DACs.

Each DAC output is attached to a comparator which can be used to detect if a termination load (e.g. monitor cable) is connected to the analogue output. Another option enables the red and blue DAC outputs to be compared against the green DAC to provide board level debugging without a monitor connected. The output state of the comparators may be read from Control Register B.

### 13.1.9 System Operation

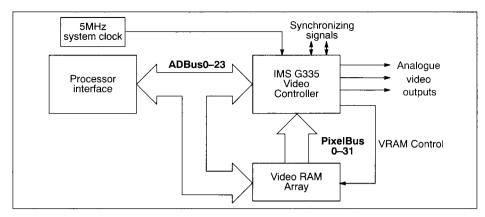

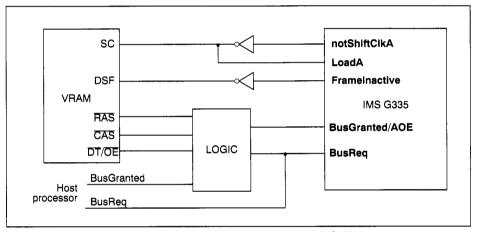

Figure 13.2 IMS G335 operating in a simple graphics system

Figure 13.2 shows how the IMS G335 would fit into a typical single-bitmap display system. The clock is typically sourced from a 5MHz crystal, with the video data being streamed to the screen at the full video rate of up to 135MHz. The video RAM array is directly accessed by the processor, with screen management automatically being performed by the IMS G335. All external digital signals and clocks are running at one quarter of the video rate, alleviating problems of high speed system design.

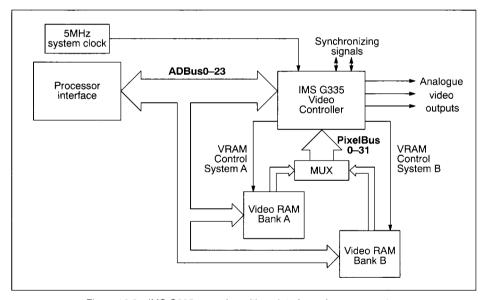

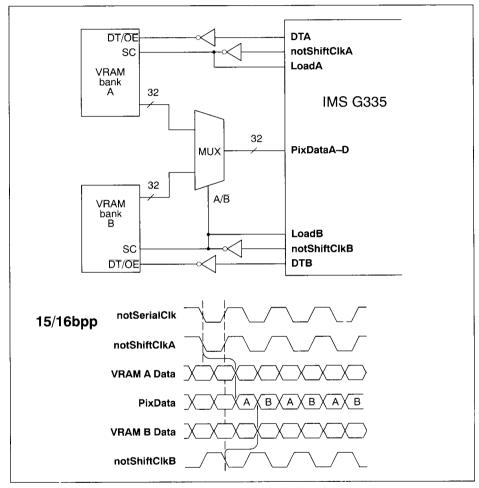

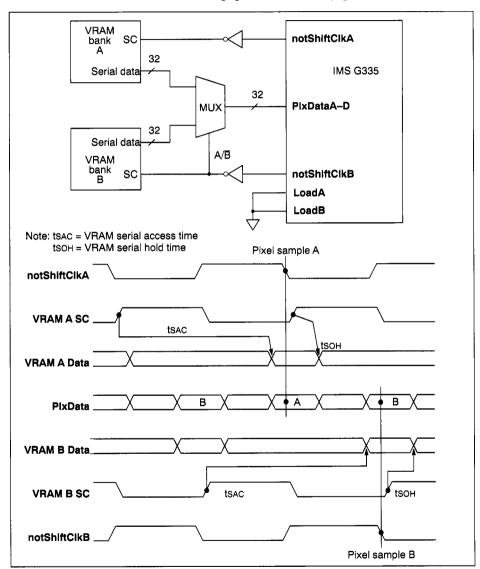

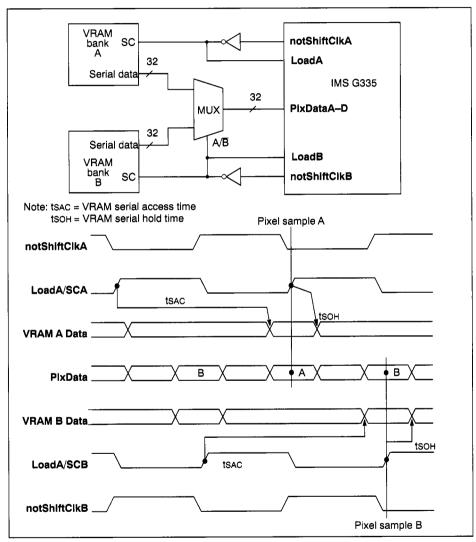

Figure 13.3 IMS G335 operating with an interleaved memory system

Figure 13.3 shows the organization of an interleaved framestore. The IMS G335 accepts alternate loads from each bank in turn through an external multiplexor (or if the video rate is low enough - about 85MHz - the VRAM serial output enables can be used instead of external hardware). The IMS G335 supplies all the controls required to implement this architecture.

# 13.2 Pin function reference guide

# 13.2.1 Micro port

| Pin name I/O Page No.                                   |             | Page No. | Comments                                                                                                                                                                                                                                    |  |  |

|---------------------------------------------------------|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ReadnotWrite I notOutputEnable I notChipSelect I Wait O |             | 173      | Microport control signals.  Wait is used to extend cycle times if necessary.                                                                                                                                                                |  |  |

| ADBus0-23                                               | data<br>Bus |          | Multiplexed address and data bus. All 24 bits are used for data; addresses are supplied either on <b>ADBus2-11</b> or on <b>ADBus3-12</b> depending on the word width. The port is also used to drive out the 22-bit VRAM transfer address. |  |  |

| Framelnactive                                           | 0           | 195      | Timing signal which is active high during vertical blanking.                                                                                                                                                                                |  |  |

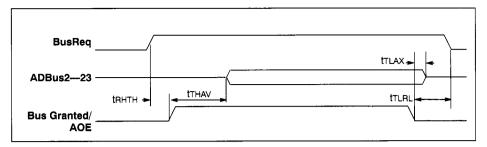

| BusReq O 187<br>BusGranted/AOE I                        |             | 187      | DMA control signals used in conjunction with <b>DTA</b> and <b>DT</b> when refreshing the VRAM shift registers.                                                                                                                             |  |  |

# 13.2.2 Pixel port

| Pin name                                                 | I/O           | Page No. | Comments                                                                                                                                                                                                                                                                                         |  |  |

|----------------------------------------------------------|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

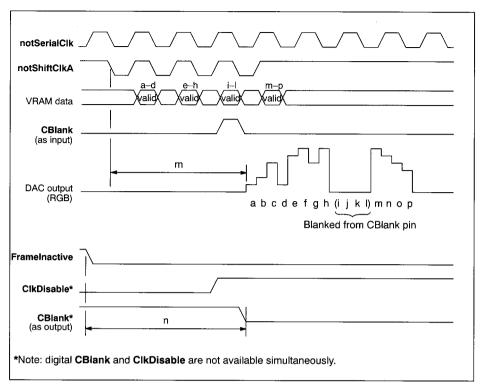

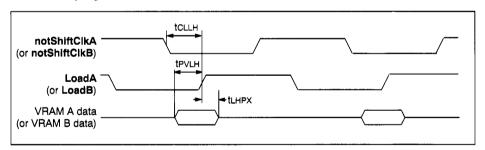

| notSerialClk                                             | 0             | 192      | <b>notSerialClk</b> runs continuously at one quarter the video frequency. This signal must be buffered                                                                                                                                                                                           |  |  |

| notShiftClkA<br>notShiftClkB                             | 0             | 192      | VRAM clocks running under the control of the timing genera tor. The clocks run in anti-phase in interleaved mode; only notShiftClkA runs in non-interleaved mode. These clocks must be buffered with an inverting buffer.                                                                        |  |  |

| DTA<br>DTB                                               | 0             | 187      | VRAM shift register transfer strobes. DTA and DTB are s chronized to notShiftClkA and notShiftClkB respectively split SAM mode DTA and DTB are not used (although still tive).                                                                                                                   |  |  |

| LoadA                                                    | 1             | 200      | Pixel data sampling strobe; non-interleaved and interleaved modes.                                                                                                                                                                                                                               |  |  |

| LoadB                                                    | ı             | 200      | Pixel data sampling strobe; interleaved mode only.                                                                                                                                                                                                                                               |  |  |

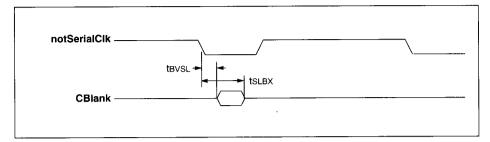

| CBlank                                                   | I/O           | 174      | <b>CBlank</b> is a composite blanking pin. Direction is soft selectable.                                                                                                                                                                                                                         |  |  |

| PixDataA0-7<br>PixDataB0-7<br>PixDataC0-7<br>PixDataD0-7 | 1   1   1   1 | 197      | Pixel input ports A-D. Port A is least significant; port D is most significant. In internal latching mode pixel data is latched synchronous to <b>notShiftClkA</b> or <b>notShiftClkB</b> . In external latching mode pixel data is latched on the rising edge of <b>LoadA</b> or <b>LoadB</b> . |  |  |

# 13.2.3 Miscellaneous

| Pin name         | I/O | Page No. | Comments                                                                                                  |

|------------------|-----|----------|-----------------------------------------------------------------------------------------------------------|

| Reset            | 1   | 184      | Must be held active high with clocks running for 6 periods of <b>ClkIn</b> in order to reset the IMS G335 |

| HoldtoGround – – |     | _        | These pins must be connected directly to ground, but do not supply ground to the chip.                    |

# 13.2.4 Phase locked loop

| Pin name            | I/O | Page No. | Comments                                                                                                                                     |

|---------------------|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| CapPlus<br>CapMinus | N/A | 172      | Phase locked loop decoupling pins, also used to hard select external dot rate clock source by connecting <b>CapPlus</b> to <b>CapMinus</b> . |

| Clockin             | Ι   | 172      | Clock input for both PLL and times-one operation.                                                                                            |

# 13.2.5 Video signals

| Pin name        | I/O | Page No. | Comments                                                                                                                     |  |  |

|-----------------|-----|----------|------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 |     | 204, 211 | Blanked video current outputs. Drive into doubly terminated $75\Omega$ load.                                                 |  |  |

| Iref I 211      |     | 211      | Video DAC reference current.                                                                                                 |  |  |

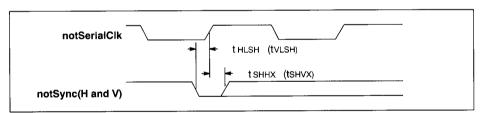

| notCorHSync I/O |     | 176      | Digital soft configurable sync signals for system synchroniza tion. They are inputs in slave mode and outputs in maste mode. |  |  |

# 13.2.6 Supplies

| Pin name I/O Page No.    |  | Page No. | Comments                                      |

|--------------------------|--|----------|-----------------------------------------------|

| AVDD N/A 229<br>AGND N/A |  | 229      | AVDD/AGND supplies analogue portions of chip. |

| VDD N/A 229<br>GND N/A   |  | 229      | VDD/GND supplies digital portions of chip.    |

# 13.3 Register function reference guide

| Register                                 | Word<br>address<br>(hex) | Page<br>No. | Description                                                                                                                                                              |

|------------------------------------------|--------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Boot Location                            | #X000                    | 215         | Startup location to which must be written the clock multiplication factor, whether PLL or ×1 mode, and the 32/64-bit address alignment selection.                        |

| Screen Description<br>Registers          | #X021 to<br>#X02B        | 212         | Read/write registers containing the screen description parameters. These are accessible only when the timing generator is not running.                                   |

| Top of Screen #1                         | #X02C                    | 210         | Read/write register giving ability to reprogram the top of screen pointer while the VTG is disabled.                                                                     |

| Framestore descrip-<br>tion Registers    | #X02D,<br>#X02E          |             | Read/write registers containing effective VRAM register length and DMA latency figures.                                                                                  |

| Mask Register                            | #X040                    | 210         | 8-bit pixel address mask register. Read/write accessible at all times. (Operates only on pseudo color pixels)                                                            |

| Control Register A<br>Control Register B | #X060<br>#X070           | 213         | Read/write control registers contain configuration information. Unassigned bits must be written with zero and are not valid on read. Read/write accessible at all times. |

| Top of Screen #21                        | #X080                    |             | Read/write register giving ability to reprogram the top of screen pointer while the VTG is enabled.                                                                      |

| Cursor palette                           | #X0A1 to<br>#X0A3        | 206         | 3x24 bit cursor color registers. Read/write accessible at all times.                                                                                                     |

| Checksum registers                       | #X0C0 to<br>#X0C2        | 210         | RGB frame checksums.                                                                                                                                                     |

| Cursor position                          | #X0C7                    | 208         | 24-bit register storing the x-y position of the cursor.                                                                                                                  |

| Color Palette                            | #X100 to<br>#X1FF        | 209         | 256 locations of 24-bit colors read/write accessible at all times.                                                                                                       |

| Cursor store                             | #X200 to<br>#X3FF        | 206         | 512 locations of 16-bit words, each containing 8 packed 2-bit pixel color values.                                                                                        |

| N.B. All other address                   | es in the rang           | e are res   | erved and must not be written to.                                                                                                                                        |

#### THE PARTY OF THE P

### Micro port address alignment

The 10-bit addresses given in the table above are word addresses. They are user selectable to align with the address conventions used in 64-bit or 32-bit words. In 32-bit mode, addresses must be supplied on **ADBus2-11**; in 64-bit mode they must be supplied on **ADBus3-12**. The unused address bits **ADBus0-1** (in 32-bit mode) or **ADBus0-2** (in 64 bit mode) are ignored by the IMS G335.

32/64-bit address alignment is selected by programming the appropriate bit of the Boot Location; details are given on page 215.

<sup>1</sup> Both Top of Screen locations address the same physical hardware

# 13.4 Clocks

The IMS G335 has two alternate clocking schemes. The primary clocking system uses a phase locked loop (PLL) on the chip to multiply up the low frequency (<10MHz) input clock to the required video data rate. Alternatively a full dot-rate clock may be supplied (Times 1 mode).

### 13.4.1 PLL mode

In PLL mode, a  $1\mu F$  capacitor must be connected between **CapPlus** and **CapMinus**. A ceramic capacitor is preferred, with an impedance of less than  $3\Omega$  between 100kHz and 10MHz. If a polarized capacitor is used, the negative terminal must be connected to **CapMinus**. Total PCB track length should be less than 50mm.

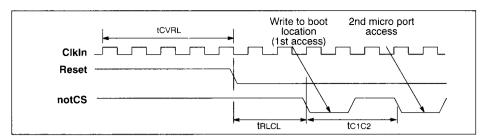

## 13.4.2 Programming the clock frequency

The multiplication factor is stored in bits 4 - 0 of the boot location #X000 and is programmable only after a reset. Whenever the multiplication factor is changed, the PLL will pull into the new frequency within  $20\mu$ s. The second access to the IMS G335 must be held off for this time as described in Section 13.6.5.

Input clock frequencies between 5MHz and 10MHz are recommended for stable operation; multiplication factors from 5 to 31 are permitted, giving a minimum recommended operating frequency of 25MHz and a maximum frequency set by the speed rating of the device.

The input frequencies may vary continuously between the recommended limits. Frequencies outside this range, and multiplication factors of less than 5 (down to 1) will work but special precautions will be needed to ensure power supply noise rejection. The maximum multiplication factor of 31 is a hard limit.

ClockIn must be derived from a crystal oscillator; RC oscillators are not sufficiently stable. ClockIn must not be distributed through a long chain of buffers. Clock edges must be monotonic and remain within the specified voltage and time limits.

### 13.4.3 'Times 1' mode

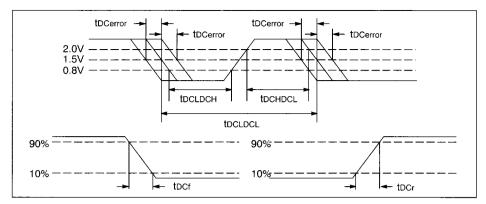

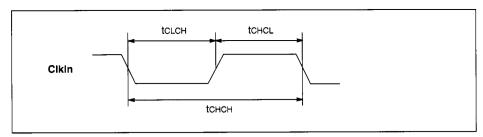

The external dot rate clock can be selected in one of two ways. Either the terminals **CapPlus** and **CapMinus** should be shorted together, or a '0' should be written to the clock source select bit in the boot location. The Times 1 mode timing is shown in Figure 13.47 and parameters in Table 13.39.

It is permissible to short CapPlus and CapMinus via a FET or relay.

Note that Times 1 clocking does not allow operation up to the maximum speed rating of the device but it does extend the operating frequency down below 25MHz. The minimum operating frequency in Times 1 mode is 5MHz

# 13.5 The micro port

### 13.5.1 Introduction

The micro port is a bidirectional 24-bit interface, consisting of a multiplexed address and data bus and several control signals. It is used for programming the VTG screen description registers, color and cursor lookup tables, cursor store, and other registers.

## 13.5.2 Word alignment

The IMS G335 is designed for use with 32 and 64-bit processors, and therefore supports both 32 and 64-bit word alignment conventions. With 32-bit alignment selected, the least significant address bit is on **ADBus2**; with 64-bit alignment selected it is on **ADBus3**. This applies only on host processor accesses to the micro port, in which a 10-bit address is input to the device and not on DMA transfer cycles in which a 22-bit word address, **ADBus2–23** is generated by the IMS G335 framestore manager.

Word alignment is selected through the setting of bit 6 of the boot location, see Table 13.24, page 215.

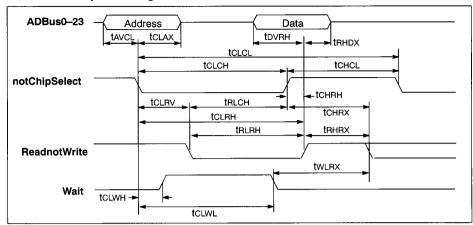

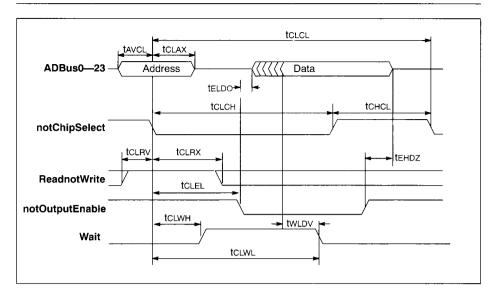

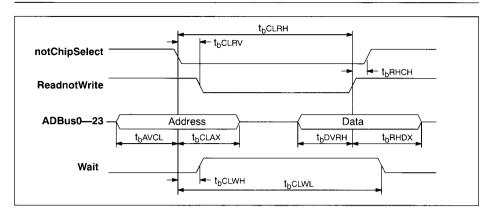

# 13.5.3 Micro port read/write cycles

To simplify system design and reduce the period that bus access is denied to other devices, micro port control signal timings are not dependent on the pixel frequency. Cycle times remain pixel-rate dependent but all other parameters are specified in absolute times as defined in Tables 13.26 and 13.27.

Four signals control the flow of address and data in and out of the device on ADBus0-23:

| Signal          | I/O | Function                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| notChipSelect   | 1   | The falling edge latches the address and begins the access.                                                                                                                                                                                                                                                                  |

| ReadnotWrite    |     | This signal is sampled within 1 SClk of the falling edge of <b>notChip select</b> . A low indicates a write cycle; if a valid low pulse has occurred within the sampling window, this indicates a write. The rising edge latches data in on a write. A write cycle can be extended indefiniteley by holding this signal low. |

| notOutputEnable | I   | This signal turns on the output buffers during a read cycle; it must be pulsed in order to terminate the access. Read cycles can be extended indefinitely by either holding off the pulse or holding the signal low.                                                                                                         |

| Wait            | 0   | This signal is driven high shortly after <b>notChipselect</b> goes low. It returns to low on a read when valid data is ready or, on a write when the cycle has finished and another access can begin.                                                                                                                        |

Table 13.1 Micro port control signals

### 13.5.4 Boot write cycles

These accesses are asynchronous and do not depend on the clock speed in any way. Boot writes are available only as the first cycle after a reset and a boot write must be made after every reset. See Table 13.30, page 220 for the timings applicable to boot write cycles.

The boot location may be read through a normal micro port read cycle.

# 13.6 Video Timing Generator

### 13.6.1 Introduction

The Video Timing Generator is a programmable finite state machine which provides monitor timing strobes and Composite blanking information to both the analogue and digital outputs. It also provides display format information to the cursor controller and framestore manager.

All of the timing parameters are independently variable with a horizontal resolution of 4 pixels and a vertical resolution of  $^{1}/_{2}$  linetime. This allows for control of a wide range of monitors, including NTSC and PAL/SECAM standard systems.

The VTG can be configured to operate as a slave in both non-interlaced and interlaced modes, synchronizing to a master signal which is either already synchronous or has been previously genlocked.

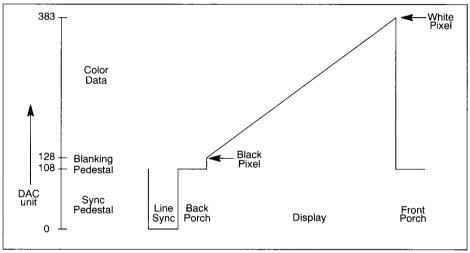

# 13.6.2 The display screen

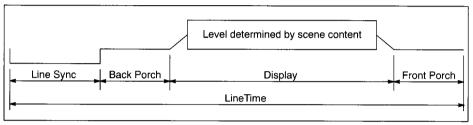

In a raster scan display system the displayed picture is built up of a number of display lines, each consisting of a visible display period and a line flyback period during which the synchronization pulse occurs. The line flyback period is split into three segments, shown in Figure 13.4, known as Front Porch, Back Porch and Line Sync. Standard monitors synchronize to the leading edge of the line sync pulse.

Figure 13.4 Scan line segments

The timing of each of the constituent periods of a line are specified in multiples of four pixels called 'Screen Units' (SU) which are used to specify the line parameters programmed into the screen description registers. In 24 bpp modes, the effective multiplex ratio falls below 4:1 so that on-chip acceleration is not possible. This means that the screen unit definition in these modes varies from the general case.

In 24bpp non-interleaved mode: 1 SU = 1 pixel In 24bpp interleaved mode: 1 SU = 2 pixels

When programming the screen description registers for these pixel modes, the new SU value must be substituted.

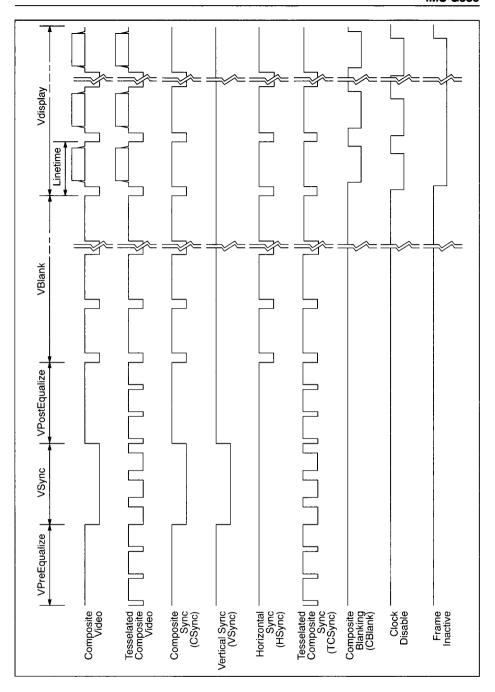

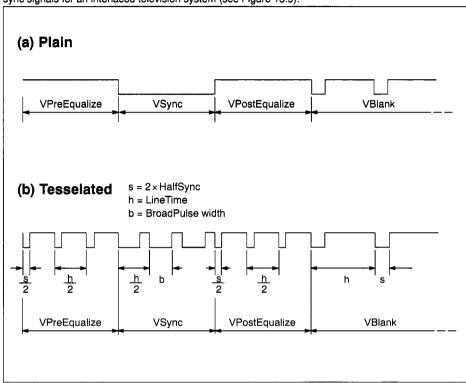

A display picture consists of bursts of display lines (which can number from a few hundred to over a thousand) separated by a number of frame flyback lines. These flyback lines do not carry display information but contain certain sync timings which depend on the waveform standard being obeyed. These timings are also programmed into the screen description registers but, because of their longer duration, are specified in units of half a LineTime. An example of a video output showing frame flyback lines and a few display lines is given at the top of Figure 13.5.

A complete frame comprises a number of discrete time periods, the vertical elements of which, as shown in Figure 13.5, are VPreEqualize, VSync, VPostEqualize, VBlank and VDisplay. The period VSync is the vertical synchronization pulse width. The periods before and after VSync are known as equalization periods (VPreEqualize and VPostEqualize). After VPostEqualize is a period of blanked scan lines, VBlank. The total vertical blanking period is the sum of these four and the position of VSync within it can be adjusted by varying the equalization periods. The display period, Vdisplay, comprises all the displayed lines of the frame.

All of these periods are programmed in multiples of half a linetime and in a non-interlaced system are in fact even multiples, i.e. a whole number of lines (the interlaced case is dealt with on page 181). After the final displayed line the frame scan cycle returns to VPreEqualize and VSync.

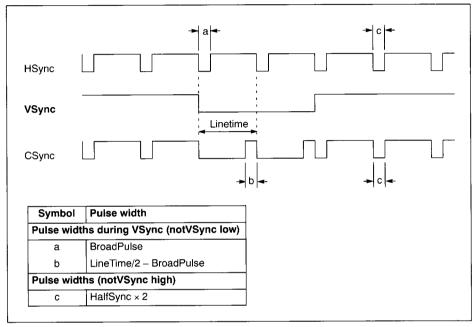

Figure 13.5 Waveforms produced by the Video Timing Generator

### 13.6.3 Sync waveforms produced by the IMS G335

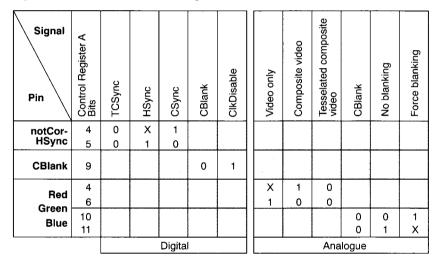

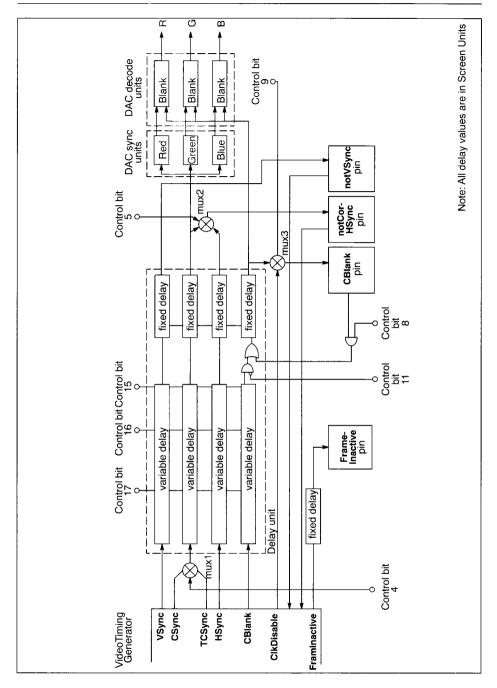

The IMS G335 produces a number of different sync patterns which are required for different output waveform standards. Nine different waveforms are produced simultaneously which can be directed to different destinations under the control of the Control Register A (Word Address = #X060).

These waveforms are shown in Figure 13.5. Composite Sync comprises the horizontal and vertical sync pulses. Composite Video comprises both horizontal and vertical sync pulses and video information. Tesselated Composite Sync (TCSync) includes tesselated cycles during Pre and Post Equalize and VSync. Composite Blanking is a blanking signal for both horizontal and vertical blanking.

The actions of Control Register A control four basic decisions:

- · Whether the video DAC output is video only or video + sync

- · Whether the composite sync mixed onto the DAC outputs is tesselated or plain (mux1)

- Whether the notCorHSync pin carries tesselated composite, composite or horizontal sync (mux2)

- · Whether CBlank pin carries composite blank or ClockDisable (mux3)

This is shown diagrammatically in Figure 13.6, which also includes some more detailed information about the timing of the data. The effect of Control Register A is shown in Table 13.2.

Table 13.2 Control signal routing options

### CBlank as input

The function of this pin is controlled by Control Register A, bit 11. When this bit is high, CBlank from the Video Timing Generator is disabled so that the only blanking signal to the DACs is from the **CBlank** pin (as input). When bit 11 is low, CBlank from the Video Timing Generator is ORed with any blanking signal from the **CBlank** pin before being supplied to the DACs.

### Internal sync and blank delays

Extra delays can be added to the internal sync and blank delays, in increments of 1 SClk to a maximum of 7SClk periods, by setting bits 15–17 of Control Register A. In external sampling mode, these delays can be compensated for by delaying the **LoadA** and **LoadB** signals by a matching amount. The feature is not available in internal sampling mode (see Section 13.8.5).

Figure 13.6 Digital and analogue sync-ing and blanking system

### Horizontal sync during frame flyback

To provide support for certain multisync monitors the IMS G335 supports an additional mode where HSync continues to run during frame flyback (in plain sync mode). Also, if Composite sync is selected, the **notCorHSync** pin will carry the CSync waveform illustrated in Figure 13.7 with the alignment as shown between CSync and HSync. This mode is selected by setting bit 2 of Control Register B (see Table 13.23).

A number of conditions of use are given in the sections headed 'Frame timing parameter calculation', page 184.

Figure 13.7 Flyback sync pattern

# 13.6.4 Programming the screen description registers

The screen description registers are memory mapped as shown in Table 13.3, page 182. They contain the line timing parameters, which are programmed in Screen Units (also referred to as one 'SCIk') and also the frame timing parameters, which are programmed in units of half a linetime.

These registers can only be written to while the Video Timing Generator is turned off (this is controlled by writing to Control Register A (Address #X060)).

### Line timing parameters during blanked and displayed lines

The constituent periods of a display line, introduced in Section 13.6.2, map directly to timing generator registers with two exceptions. Firstly, the line synchronizing pulse is split into two periods of equal duration which are used in immediate succession - the parameter used for this is 'HalfSync'. Secondly, there is no register for FrontPorch, rather the total line time is programmed into a separate register and the end of the scan line occurs when LineTime expires.

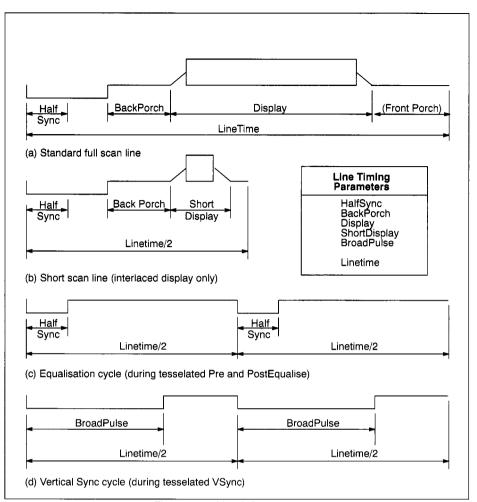

All line timing parameters are specified in Screen Units, so that for example, except for 24 bpp mode, a 1024 pixel screen width is described as 256 SU. The line description parameters are illustrated in Figure 13.8.

Figure 13.8 (a) shows the parameters relating to a full scan line. The duration of FrontPorch is not directly defined but is determined by LineTime minus the duration of the other scan line components. HalfSync is used twice in succession to construct the line sync pulse.

Figure 13.8 (b) shows the parameters relating to a short scan line (occurring only in interlaced displays). The overall duration is determined by LineTime. As for a full scan line the duration of the FrontPorch is not directly defined, hence it can differ from the implied FrontPorch value of a full scan line.

### Line timing parameters during frame flyback

During frame flyback, the VTG uses two variants of the basic linescan sequence. In VPreEqualize and VPostEqualize the waveform produced is either constant high or tesselated as shown in Figure 13.8 (c). The internal cycle, however, uses the parameter sequence as shown in Figure 13.8 (b) so the parameter ShortDisplay must contain a valid value even though interlace is not being used.

In VSync, the waveform produced is either constant low or tesselated as shown in Figure 13.8 (d). The internal cycle uses both BroadPulse and LineTime, so the parameter BroadPulse must contain a valid value, even if flyback tesselations or composite syncs during flyback are not being used.

Figure 13.8 Line timing parameters

### Frame timing parameters

The IMS G335 generates synchronizing signal timings and levels conforming to both broadcast and closed circuit television standards. This means that, as well as being capable of generating frame sync patterns associated with non-interlaced computer graphics systems, it is also able to produce tesselated sync signals for an interlaced television system (see Figure 13.9).

Figure 13.9 Composite Sync frame flyback waveforms

In non-interlaced mode the VBlank and VDisplay parameters must be an even number of  $^{1}/_{2}$  lines. The remaining parameters may be odd or even, depending on the monitor specification.

There are two interlace modes:

- · TV standard interlace (each field must contain an odd number of lines)

- · Even field interlace (each field must contain an even number of lines)

In both these modes bit 1 of Control Register A must be set; bit 14 of Control Register B is used to select either TV standard interlace (set to '0') or Even field interlace (set to '1'). Bit 2 of Control Register A selects the interlace standard required; this bit must be set to 1 for Even field interlace operation.

In TV standard interlace mode, VDisplay must be odd and VBlank may be even or odd, depending on the standard being followed. Note that in both interlace modes the VDisplay parameter describes the number of visible lines in each field, not the number in each frame, so that for example, an n-line interlaced frame, the VDisplay parameter is n  $^{1}/_{2}$ -LineTime periods.

In Even field interlace mode VBlank and VDisplay must remain even. In this mode the even field (lines 0,2,4...) is displayed first, followed by the odd field (lines 1,3,5...).

In non-interlace there is only one field, so that a 1024-line frame would have 2048 <sup>1</sup>/<sub>2</sub>-LineTime periods.

| Parameter        | Notes                                                                                                                                                                                                                                                                                                                                  | Units         | Address |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|--|

| Line timing para | ameters                                                                                                                                                                                                                                                                                                                                |               |         |  |

| LineTime         | eTime  Determines the total line time (the sum of the displayed and blanked periods of a single line).  For interlaced displays LineTime/2 also determines the duration of short (half) scan lines (see Figure 13.8).  LineTime > (2×HalfSync + BackPorch + Display)  LineTime must be an even multiple of the period of notSerialCik* |               |         |  |

| HalfSync         | Determines the line sync pulse duration (2×HalfSync). HalfSync also determines the low period in pre and post equalize cycles of a tesselated frame flyback waveform.                                                                                                                                                                  | SU            | #X021   |  |

| BackPorch        | Determines the duration of BackPorch (shown in Figure 13.8). Note that BackPorch must exceed TransferDelay by at least two notSerialClk* periods. If BackPorch is less than 16 SClk periods then the cursor will be offset as described in Section 13.9.5.                                                                             | SU            | #X022   |  |

| Display          | Determines the duration of the visible portion of the scan line. Display must be a multiple of the period of <b>notShiftClk</b> in SUs.                                                                                                                                                                                                | SU            | #X023   |  |

| FrontPorch       | The duration of FrontPorch (shown in Figure 13.8) is implied by the following parameters:  FrontPorch = LineTime - (Display + BackPorch + (2×HalfSync))                                                                                                                                                                                |               |         |  |

| ShortDisplay     | SU                                                                                                                                                                                                                                                                                                                                     | #X024         |         |  |

| Frame timing pa  | arameters                                                                                                                                                                                                                                                                                                                              |               | •       |  |

| VDisplay         | Describes the vertical display field (visible lines). For a non-interlaced display VDisplay = 2×(Lines per frame). For an interlaced display VDisplay = Half lines per field The total number of displayed lines in each frame must be a whole number.                                                                                 | Half<br>lines | #X02A   |  |

| VBlank           | Determines the number of blanked lines during frame flyback. The total frame blanking period is the sum of VBlank, VSync, VPreEqualize and VPostEqualize.                                                                                                                                                                              | Half<br>lines | #X029   |  |

| VSync            | Determines the duration of the frame sync pulse and, for a tesselated frame flyback waveform, the number of VSync cycles.                                                                                                                                                                                                              | Half<br>lines | #X026   |  |

| VPreEqualize     | Determines the duration of PreEqualize and, for a tesselated frame flyback waveform, the number of PreEqualize cycles.                                                                                                                                                                                                                 | Half<br>lines | #X027   |  |

| VPostEqualize    | Determines the duration of PostEqualize and, for a tesselated frame flyback waveform, the number of PostEqualize cycles.                                                                                                                                                                                                               | Half<br>lines | #X028   |  |

| BroadPulse       | Determines: a. The low period in a VSync cycle of a tesselated frame flyback waveform. b. The pulse widths as shown in Section 13.6.3, Figure 13.7 when sync during flyback has been selected.                                                                                                                                         | SU            | #X025   |  |

leaved mode where 1 SU = 1 pixel period and 24 bpp interleaved mode where 1 SU = 2 pixel period)

Table 13.3 Summary of screen description parameters

### Line timing parameter calculation

The line timing parameters can be calculated using the equations given in Table 13.4. Note that if the monitor waveforms are specified in microseconds, they must first be converted to Screen Units by dividing by the period of **notSerIalClk**.

| During a full line cycle (VBlank, VDlsplay) |                              |                                            |  |  |

|---------------------------------------------|------------------------------|--------------------------------------------|--|--|

| HalfSync                                    | HalfSync = Horizontal Sync/2 |                                            |  |  |

| BackPorch                                   | =                            | BackPorch                                  |  |  |

| Display                                     | =                            | Display                                    |  |  |

| LineTime                                    | >                            | (2×HalfSync + BackPorch + Display)         |  |  |

|                                             | Dı                           | uring an equalization cycle                |  |  |

| ShortDisplay                                | <                            | LineTime/2 - (2×HalfSync + BackPorch)      |  |  |

| Low period                                  | =                            | HalfSync                                   |  |  |

| High period                                 | =                            | LineTime/2 – HalfSync                      |  |  |

|                                             |                              | During a VSync cycle                       |  |  |

| BroadPulse                                  | =                            | LineTime/2 - Pulse width*                  |  |  |

| Low Period                                  | =                            | BroadPulse                                 |  |  |

| High period                                 | =                            | Pulse width                                |  |  |

| * Note: Pulse                               | wid                          | th = duration of serration pulse high time |  |  |

Table 13.4 Screen description line parameter equations

The following restrictions on parameter values must be observed:

#### General restrictions

All parameters must be greater than 1.

LineTime must be an even multiple of the period of notSerialClk.

2×HalfSync + BackPorch + Display > LineTime/2 > 2×HalfSync + BackPorch.

The total number of displayed lines in each frame must be a whole number.

TransferDelay < BackPorch - 2

ShortDisplay < LineTime/2 - (2 × HalfSync + BackPorch) -1

Display must be a multiple of the period of notShiftClk in SUs.

TransferDelay must not exceed ShortDisplay (the parameter TransferDelay is described in Section 13.7).

### Additional restrictions in Interlace mode

BackPorch+Display>bit15+(2×bit 16)+(4×bit 17)+31/2SClk+1notSerialClk\*

(LineTime/2 - FrontPorch) > TransferDelay + 2

TransferDelay < Display - 2

LineTime/2 - FrontPorch > 1

When the cursor is being used, FrontPorch must be > 4

### Additional restrictions in split SAM mode

(2 x HalfSync) + TransferDelay < LineTime/2

\*Note: Refers to Control Register A bits 15 to 17 (pixel pipeline delay)

Table 13.5 Restrictions applying to parameter values

Note that a fully worked example for the Hitachi HM4219/4119 monitor is described in Section 17.3, page 341.

### Frame timing parameter calculation (non-interlaced)

If the monitor waveforms are specified in milliseconds, then they must be converted to  $^{1}/_{2}$  LineTime units as follows:

Total number of lines per frame

$$=$$

$\frac{\text{frame period (ms)}}{\text{line period (us)}}$

Number of flyback lines = Total number of lines - number of displayed lines

The VTG programming rules are:

Number of flyback lines×2 = VPreEqualize + VSync + VPostEqualize +VBlank and

VBlank must be even.

Once VSync has been expressed in terms of  $^{1}/_{2}$  LineTimes then specification of the remaining parameters is determined by the monitor requirement for the location of VSync in the blanking period. A fully worked example for a non-interlaced monitor is given in Section 17.3, page 341.

If horizontal sync during flyback is selected, the following condition must be satisfied:

VBlank, VSync, VPreEqualize and VPostEqualize must be even.

# Frame timing parameter calculation (interlaced)

The interlaced timings generated by the IMS G335 are highly programmable but are specified to conform to the two major broadcast standards. For this reason there are different restrictions on parameter values. These restrictions are:

- 1 In NTSC (EIA) mode, VBlank must be even

- 2 In PAL/SECAM (CCIR) mode, VBlank must be odd

- 3 In both modes, VDisplay must be odd

- 4 In even field interlace mode, VDisplay and VBlank must be even

In all other respects, parameter calculation is identical to the non-interlace mode. A full table of parameters conforming to NTSC and PAL waveforms is given in Section 17.2, page 337. See Section 13.6.3 for further parameter restrictions if sync during frame flyback is selected.

If horizontal sync during flyback is selected, the following conditions must be satisfied:

- If EIA format has been selected the sum of (VSync + VPreEqualize + VPostEqualize) must be even

- If CCIR format has been selected the sum of (VSync + VPreEqualize + VPostEqualize) must be

odd.

- If Even field interlace format has been selected, VBlank and the sum of (VSync + VPreEqualize + VPostEqualize) must be even.

### 13.6.5 The VTG startup sequence

Reading from and writing to the VTG registers, which are memory mapped, is only possible while the timing generator is disabled. Enabling and disabling the VTG is achieved by a write to Control Register A (Address = #X060).

On startup, after reset, the host processor must write a configuration pattern to the IMS G335 bootstrap location. The effect of this is to set the PLL multiplication factor, clock source (PLL or external crystal) and microport address alignment.

Startup sequence:

- 1 Assert, then deassert Reset.

- -Wait 50ns

- 2 Write configuration pattern to bootstrap location.

- -Wait 80us to allow PLL to stabilize

Control Register A will contain a default value of #X0000 and Control Register B will contain a default value of #X0200 (Sync pins tristate).

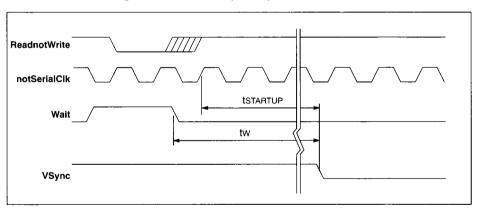

After this the screen parameters, color table, cursor pattern, etc. can be written to the appropriate locations in any order. The processor must then write to Control Register B, followed by Control Register A to enable and start up the VTG. If the rising edge of **ReadnotWrite** occurs after the falling edge of **Walt**, then there will be a fixed delay from the rising edge of **ReadnotWrite** to the falling edge of **notVSync**. If the rising edge of **ReadnotWrite** occurs before the falling edge of **Walt** then the delay will be fixed relative to the falling edge of **Walt**. These delays are detailed in Figure 13.40, page 223. The IMS G335 can be reprogrammed without asserting Reset.

The reprogramming sequence has three steps:

- 1 Write zero to bit 0 of Control Register A, disabling VTG.

- 2 Write to the screen parameter registers chosen for redefinition.

- 3 Write one to bit 0 of Control Register A, (redefining modes if necessary by modifying the relevant register bits) and enabling the VTG.

If only the operating mode is to be changed, step 2 only may be omitted, the remainder of the address space is programmed without disabling the VTG. If the clock multiplication factor is to be changed the full startup procedure must be followed, including reset.

#### 13.6.6 Master and slave modes

### Master mode configuration

The IMS G335 is set to operate as a master by setting the *Device Operating Mode* bit (Control Register A bit 3) low. This sets the composite and horizontal sync (**notCorHSync**) and vertical sync (**notVSync**) pins to be outputs. Sync is generated internally, and these two sync pins are driven appropriately, at TTL levels, active low or active high, depending on the setting of Control Register B.

## Slave mode configuration

The IMS G335 is set to operate as a slave by setting the *Device Operating Mode* bit (Control Register A bit 3) high. This sets the composite and horizontal sync (**notCorHSync**) and vertical sync (**notVSync**) pins to be inputs. To enable and disable the IMS G335 VTG when configured for slave mode, it is necessary to write the *Device Operating Mode* bit at the same time as writing the VTG enable bit. These two control bits should be written in the same data write regardless of whether they are being written high or low.

### Slave mode operation

With non-interlaced slave mode operation, an external horizontal sync is not required, but an external vertical sync must be supplied, as the IMS G335 synchronizes to each frame. The external vertical sync must be supplied to the **notVSync** input, and cannot be supplied to the **notCorHSync** pin.

The IMS G335 has internal synchronizers which eliminate any instability problems. However, unless the system ensures that the sync signals are locked in some way, either by running from a single master clock or by genlocking, then the picture will lock only to the nearest Screen Unit.

For a lock to pixel resolution, the systems must be synchronized and the external **notVSync** signal must be presented with the set up and hold times shown in Figure 13.45.

When using interlaced slave mode operation, external horizontal and vertical sync signals must be supplied to the **notCorHSync** and **notVSync** pins respectively. The *Digital Sync Format* mode must be selected to be separate sync, by setting Control Register A bit 5 high (logic 1). The IMS G335 will initially use the horizontal sync to determine which field is to be displayed, and subsequently synchronize on each field (not frame) using vertical sync.

### Slave mode synchronization

In interlaced slave mode, if the IMS G335 has not been set to 'HSync during Flyback' operation, incoming HSync pulses should not be present during frame flyback. If any pulses are present during this time, then

correct field synchronization will not be possible. Master HSync pulses may be gated with the IMS G335 **FrameInactive** signal to eliminate any HSync pulses from occurring while **FrameInactive** is asserted. If the G335 has been set to operate with Hsync during flyback then, as long as the incoming pulses are identical to those produced by the G335, correct field sync will occur with or without this gating.

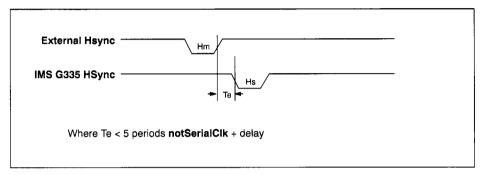

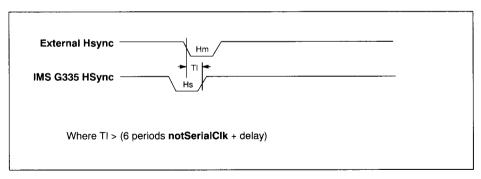

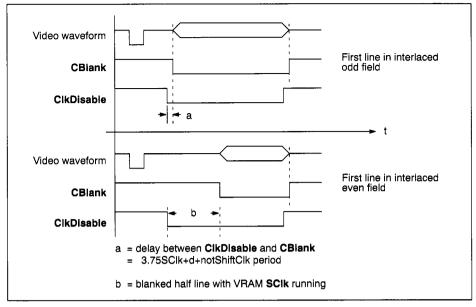

### Position of external HSync pulses in Interlaced mode

When in interlaced slave mode, the position of the external (master) HSync pulse with respect to the internally generated IMS G335 HSync pulse, as output at the DACs, must be as shown in Figures 13.10 and 13.11. The external HSync pulse may occur anywhere between the earliest time and the latest time and must be a minimum of 1SClk in duration.

This timing specification must be observed for all HSync pulses present during each field.

### Early external HSync

Figure 13.10 Early external HSync

The rising edge of the external HSync pulse must occur less than Te periods of **notSerialClk** before the falling edge of the internally generated IMS G335 HSync pulse. The delay value is the programmed IMS G335 sync delay (using **Control Register A** bits 15 - 17).

### Late external HSync

Figure 13.11 Late external HSync

The falling edge of the external HSync pulse must occur more than TI periods of **notSerialClk** before the rising edge of the internally generated IMS G335 HSync pulse. The delay value is the programmed IMS G335 sync delay (using **Control Register A** bits 15 - 17).

# 13.7 Framestore manager

### 13.7.1 Introduction

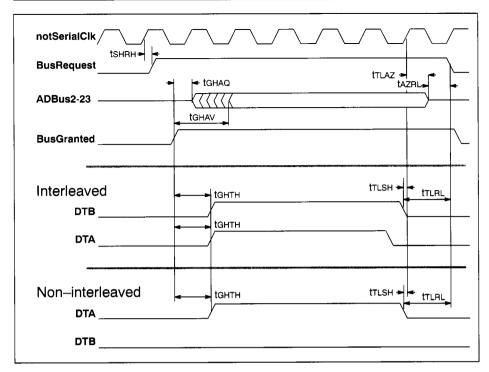

The framestore manager provides VRAM serial port clocking, SAM refresh address and SAM transfer signal for synchronous shift register reload. Since certain pixel port modes require interleaved banks of VRAM, the framestore manager provides two complete clocking and transfer systems, one for each bank. The reload operation is conducted by a DMA into the framestore, and a fully handshaken DMA is provided for this purpose. Transfer cycles may be optionally disabled by writing to bit 14 of Control Register A.

Using this system, it is possible to implement a fully packed framestore for any pixel depth, independent of screen format and memory architecture (providing the Display parameter is a multiple of **notShiftClk** period in Screen Units).

A new mode has been introduced on the IMS G335 to provide support for VRAMs with split SAM capability, further details are given in Section 13.7.5. Operation of the IMS G335 not using split SAM support is referred to as 'synchronous mode'.

### 13.7.2 Non-interleaved framestore (synchronous mode)

### The screen transfer operation

The IMS G335 provides software programmable strobes, **BusRequest** and **DTA**, which enable it to perform the necessary screen data-transfer cycles on video RAMs to reload their internal shift registers with new data. These may be synchronous updates which happen part way across a line or updates which occur during flyback.

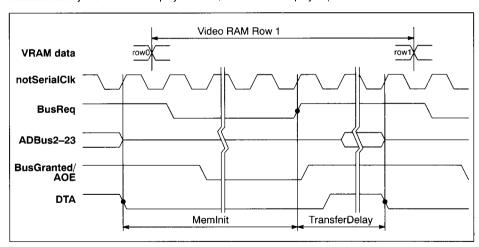

The strobes are controlled by values loaded into the framestore description registers, MemInit and TransferDelay. These are loaded and incremented continuously in turn whenever the display is active (i.e. they count displayed pixels). From the start of any frame, MemInit is loaded first, then TransferDelay. An update cycle is requested at the expiry of MemInit and is completed at the expiry of TransferDelay as shown in Figure 13.12. The IMS G335 also outputs a transfer address specifying the new row of pixels to be displayed. It is left to the user to generate RAS, CAS and any other strobes needed from **BusRequest**, **DTA**, **notSerialClk** and **notShiftClk**.

The transfer sequence is as follows:

- 1 The IMS G335 asserts BusReq. When BusGranted/AOE is given, it drives DTA high and also drives the reload address onto ADbus2-23.

- 2 The IMS G335 waits until the TransferDelay period expires, during which time the system must perform a VRAM access.

- 3 After a fixed time (TransferDelay Screen Units) relative to the rising edge of BusReq, the IMS G335 drives DTA low and tri-states the ADbus. One SCIk cycle later, BusReq will go low.

#### Screen maintenance

The IMS G335 uses the framestore description parameters to implement a packed framestore in the following way:

At the start of each display frame, the IMS G335 initiates a transfer cycle during the backporch of the first vertical blanked line, using the Top of Screen pointer as the transfer address. The data transfer is performed with the delay specified in the TransferDelay register.

This ensures that there is data loaded ready for the first line scan to begin.

At the start of active display the IMS G335 will begin to count **notSerialClk** cycles and will initiate a further transfer cycle after MemInit cycles of **notSerialClk**. It will then follow the transfer sequence as described

above. The falling edge of **DTA** is synchronized to **notShiftClockA** to allow synchronous mid-line updates. The whole Meminit - TransferDelay sequence is repeated as many times as necessary until the bottom of screen is reached. When the system reaches the end of a scan line any unused pixels in the VRAM shift register are held over to be displayed on the following line.

Thus the period of row transfer operations is:

### MemInit + TransferDelay (displayed pixels)

and apart from the restrictions shown in Table 13.6, it need bear no relation to the screen line length at all. This permits any display line length with any type of video RAM.

| Display                 | =   | Multiple of notShiftClk period in SUs      |

|-------------------------|-----|--------------------------------------------|

| TransferDelay           | <   | BackPorch – 2                              |

| TransferDelay           | 2   | System DMA Latency+VRAM Access+1 SClk      |

|                         |     |                                            |

| Additi                  | ona | lly, in an interlaced system <u>only</u> : |

| MemInit + TransferDelay | =   | Display                                    |

| TransferDelay           | <   | ShortDisplay                               |

Table 13.6 Restrictions on Framestore description parameters

The critical parameter as far as DMA accesses are concerned is TransferDelay which needs to be long enough to allow for the DMA latency of the drawing processor as well as the access time of the video RAMs.

Note that, with the exception of the first load operation of each frame, the framestore manager only counts **notSerialClk** cycles while the display is active. i.e. it counts displayed pixels.

Figure 13.12 Data transfer sequence

Figure 13.12 shows the sequence of events, for a non-interleaved system, during a synchronized VRAM row transfer operation performed by the IMS G335 which takes place part-way along a display line. That is to say an uninterrupted stream of pixels is maintained during a reload of the shift registers. MemInit is the time from the falling edge of **DTA** to the assertion of **BusReq**; TransferDelay is the time between the assertion of **BusReq** to the falling edge of **DTA**.

### Transfer cycles occurring during flyback

Since the IMS G335 allows the user to define an arbitrary linewidth and an arbitrary shift register length, transfer operations can in principle occur at any time during the line.

The IMS G335 uses the programmed value TransferDelay to schedule transfer operations early enough to ensure that the VRAM shift registers never run out of data.

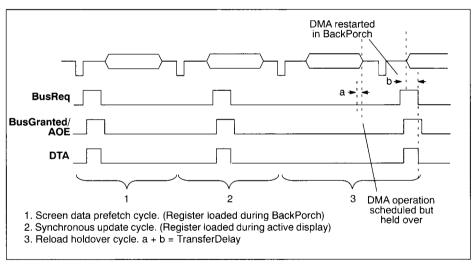

Figure 13.13 shows three separate cases of transfer cycle timing:

Case1 is where the transfer cycle occurs during backporch; this would be the case for the first backporch during vertical blank, where pixels are prefetched for the first displayed line of the frame.

Case 2 is the synchronous transfer case, where the update takes place mid-line. This will generally be the case where the screen width is not programmed to be an exact multiple of the shift register length. In order to avoid visible glitches on the screen at these times, the position of the falling edge of the transfer strobe must be synchronous with **notShiftClkA**.

Case 3 is the case where a synchronous midline update is scheduled to straddle two visible picture lines. If the IMS G335 were to start a transfer cycle at this point it would be holding the memory bus for the whole of the flyback period, preventing any processor access of memory during this time. The IMS G335 therefore holds this transfer cycle over until the start of backporch, allowing memory accesses up until this point. In order to reduce the period when processor memory access is prevented the DMA cycle does not take up the whole of backporch; the DMA operation in case 3 being of the same duration as those in 1 and 2.

Figure 13.13 Data transfer operational behavior

If MemInit + TransferDelay = Display, the transfer cycle is identical to case 2, with the transfer taking place immediately after the end of the scan line.

### The transfer address and top of screen pointers

The IMS G335 outputs a new 22-bit address on **ADBus2-23** during every transfer cycle it initiates irrespective of whether the micro port address alignment is set to 32 or 64-bit mode. The first address in each frame is specified in the Top of Screen register, which is programmed on startup but which can be modified at any time. Note that this register appears at two separate locations, #X02C and #X080. #X02C is accessible only when the VTG is disabled, #X080 only when it is running.

The current row address is incremented by the amount specified in bits 13-12 of Control Register A, used in conjunction with the 'Interlace' bit (bit 2). These bits specify the VRAM step length and the screen format. Refer to Table 13.7 for bit assignments.

Changes to the Top of Screen pointer become effective from the top of the subsequent screen (or field in an interlace system).

In setting MemInit + TransferDelay = Display for an interlaced system, one row transfer is made per line. Therefore since transfers are done on a line by line basis, the framestore format for interlace can be identical to that for a non-interlaced system. The address offset for the second field is added automatically by the IMS G335. Address ordering depends on the standard selected. CCIR scans even lines first, EIA scans odd lines first.

In interlace, the first half of Line Zero is always blanked at the video DACs but the IMS G335 will clock the VRAM shift registers as though visible. This preserves compatibility between interlace and non-interlace.

| Register Bit |    | Non-interlace | Interlace |                     |  |  |

|--------------|----|---------------|-----------|---------------------|--|--|

| 13           | 12 | Increment     | Increment | Second field offset |  |  |

| 0            | 0  | 1             | not used  |                     |  |  |

| 0            | 1  | 256           | 2         | 1                   |  |  |

| 1            | 0  | 512           | 512       | 256                 |  |  |

| 1            | 1  | 1024          | 1024 512  |                     |  |  |

Table 13.7 VRAM address increment as set by Control Register A, bits 12 and 13

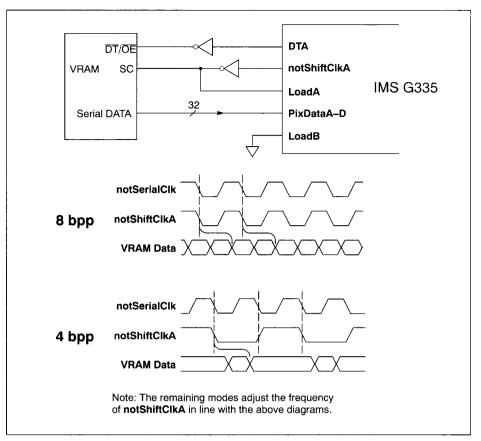

### VRAM ShiftClock generation

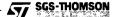

The framestore manager automatically adjusts the frequency of **notShiftClkA** to account for different pixel depths and hence pixel port multiplex ratios.

There are five pixel formats supported in non-interleaved mode; these are shown in Table 13.10, page 197 along with the multiplex ratio of the pixel port and the period of ShiftClock generated by the framestore manager.

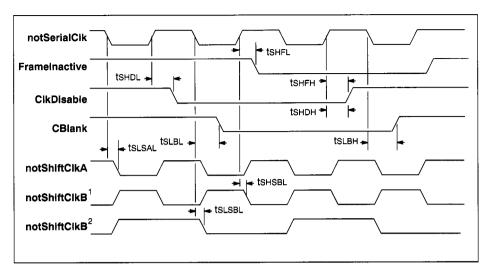

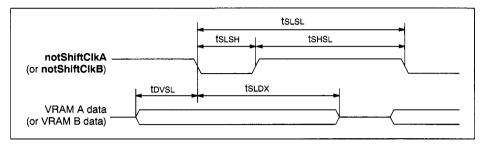

ShiftClock generation and usage are illustrated in Figure 13.14. Note that both **notShiftClkA** and **DTA** are buffered and inverted before use.

Figure 13.14 Non-interleaved VRAM

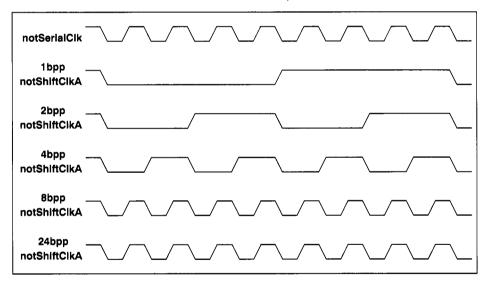

# 13.7.3 Interleaved framestore (synchronous mode)

Because of the very high video rates supported by the IMS G335 it is not possible in some situations to supply pixel data fast enough from a single bank of Video RAMs. An interleaved mode has been provided to allow two banks of VRAM to be used, each running at half the frequency required when using a single bank. 32 bits of pixel data are loaded alternately from one VRAM bank then the other.

In interleaved mode, two **notShiftClk** and the **DTA/B** signals are used to control the two banks, the shift clocks running in anti-phase. It can be seen that the falling edge of **notShiftClkA** will cause data to be driven out from VRAM Bank A into the **PixData** input of the IMS G335.

Figure 13.15 Interleaved VRAM banks

#### Interleaved VRAM control

In order to implement an interleaved framestore, the IMS G335 provides a second set of VRAM clock and transfer signals; notShiftClkB and DTB. notShiftClkB runs in antiphase to notShiftClkA so that the data in each bank is skewed by one half the notShiftClk period. The two streams of data can then be multiplexed into the IMS G335.

The effect of this is that each bank of video RAM must be clocked at half the rate which would be necessary for a non-interleaved framestore. This is taken into account by the IMS G335 and the ShiftClock periods for all possible pixel depths in interleaved mode are shown in Table 13.11, page 198.

An interleaved framestore system is shown in Figure 13.15, along with the **notShiftClk** and VRAM data waveforms for 15/16 bits per pixel format. In this mode, the IMS G335 alternately samples pixel data from VRAM bank A and B.

The timing of **notShiftClkA** and **notShiftClkB** differs at the beginning and the end of each line, such that the bank select signal must be derived, as shown in Figure 13.15, from the **notShiftClkB** signal and not **notShiftClkA**.

#### VRAM reload in an interleaved framestore

The basic reload cycle in interleaved format is the same as the standard format. The difference is that, because of the skew between **notShiftClkA** and **notShiftClkB**, the **DTB** strobe must be delayed by a similar amount with respect to **DTA**. This amount varies depending on the pixel depth, and is automatically adjusted by the IMS G335.

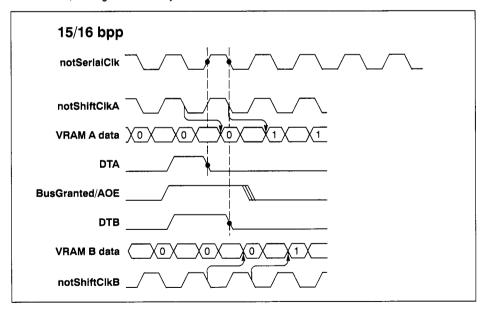

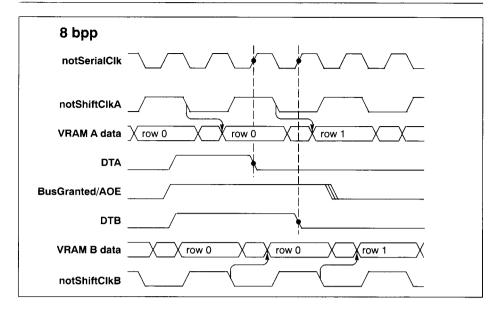

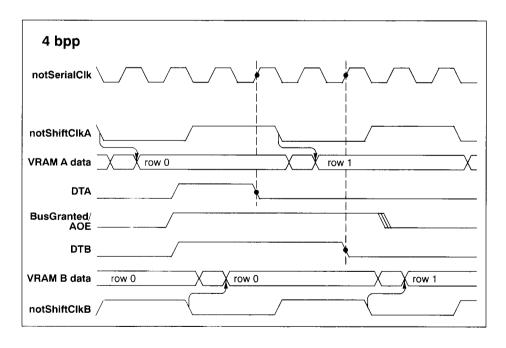

The data transfer sequence is shown in Figures 13.16 to 13.18 for 16, 8 and 4 bpp, the remaining modes being simply an extension of these waveforms.

In all cases, the beginning of the DMA cycle is identical to the non-interleaved case, the difference being that the falling edge of **DTB** is delayed by one half period of **notShiftClk(A or B)**, with **BusReq** remaining asserted until one period **notSerialClk** after the falling edge of **DTB**. Also, the reload address driven onto the ADbus remains valid until after the falling edge of **DTB**.

Note that all the VRAM controls and clocks, **DTA/B** and **notShiftClkA/B** must be buffered and inverted before use.

Use of an interleaved system affects the framestore description parameters in that the effective VRAM shift register length is doubled from that in non-interleaved mode. MemInit must therefore be modified to account for this, leaving TransferDelay the same.

Figure 13.16 Data transfer sequence - interleaved, 15/16bpp

Figure 13.17 Data transfer sequence - interleaved, 8bpp

Figure 13.18 Data transfer sequence - interleaved, 4bpp

### 13.7.4 FrameInactive

A further timing signal, **Framelnactive**, is provided which can be used to convey frame timing information to the host. This signal may be used in multiboard systems where frame swapping is used to implement animation, for example. **Framelnactive** is asserted whenever the timing generator enters frame flyback and is deasserted on entering active display.

## 13.7.5 Split SAM VRAM support

The use of split Serial Access Memory (SAM) Video RAM allows simplified system design and reduces bus control time significantly. Split SAM devices have their serial shift register split into two, one half being updated while the other half is shifting out. The transfer window for split SAM devices is increased from 1 shift clock period to half the period of the entire serial shift register, making the update timings much less critical and system design easier.

The IMS G335 split SAM mode provides support for VRAMs with a split SAM capability. In this mode the VRAM update timings are less critical than for seamless (synchronous) update; VRAM update being completed by the system after initiation by the IMS G335. Bus control time is reduced since the bus is cycled as fast as the system allows instead of being governed by worst-case timings programmed into TransferDelay.

In split SAM mode some pin functions are changed compared with their operation in synchronous mode, (see Table 13.8).

| Pin            | Synchronous mode                                               |                                                              |     | Split SAM mode                                                                                   |  |  |

|----------------|----------------------------------------------------------------|--------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------|--|--|

|                | I/O Function                                                   |                                                              | I/O | Function                                                                                         |  |  |

| DTA            | O Performs transfer of VRAM A data synchronous to notShiftClkA |                                                              | x   | not used <sup>1</sup>                                                                            |  |  |

| DTB            | 0                                                              | Performs transfer of VRAM B data synchronous to notShiftClkB |     | not used <sup>1</sup>                                                                            |  |  |

| BusReq         | 0                                                              | Requests DMA cycle                                           |     | Requests DMA cycle.                                                                              |  |  |

| BusGranted/AOE |                                                                | Grants DMA cycle, drives refresh address onto ADBus.         | ı   | Rising edge drives refresh address onto ADBus, falling edge tri-states ADBus and cancels BusReq. |  |  |

### Note:

1 The DTA and DTB pins are active during split SAM DMA cycles although not performing transfer of VRAM data. TransferDelay must still be programmed with a value satisfying the conditions given in Table 13.5, though not directly used.

Table 13.8 Pin functions in synchronous and split SAM modes

#### Operation of the split SAM mode

The split SAM mode works as follows:

At the start of each field, during the backporch of the first vertical blanked line, the IMS G335 requests a data transfer, using the Top of Screen pointer as the transfer address. At the conclusion of this transfer, it increments the transfer address by the amount specified in Control Register A. As soon as the displayed screen is reached and pixels are being clocked out of the VRAM serial port, the IMS G335 uses MemInit to set the period of data transfer requests.

At the point when MemInit expires, **BusReq** will go high, after which a rising edge on **BusGranted/AOE** will turn on the **ADBus** with the refresh address. The system is then free to perform the transfer cycle in any way it sees fit. On the falling edge of **BusGranted/AOE**, the **ADBus** will be tristated and **BusReq** driven low with a 1<sup>1</sup>/<sub>4</sub>SClk delay. No timing information will be supplied by the IMS G335 other than the initial bus request. At the conclusion of each transfer operation during display, the transfer address is incremented by **half** the amount specified in Control Register A, bits 12-13. The VRAM step length is shown in Table 13.9.

In interleaved mode, data transfer can occur in both banks simultaneously. The IMS G335 automatically delays the transfer request until bank B has finished clocking data out of the relevant shift register. This delay will vary depending on the bits per pixel mode and must be subtracted from the time available for transfer to occur.

| Register bit |    | Split SAM VRAM address increment |                         |  |  |  |

|--------------|----|----------------------------------|-------------------------|--|--|--|

| 13           | 12 | First backporch in VBlank        | During displayed screen |  |  |  |

| 0            | 0  | not allowed                      | not allowed             |  |  |  |

| 0            | 1  | 256                              | 128                     |  |  |  |

| 1            | 0  | 512                              | 256                     |  |  |  |

| 1            | 1  | 1024                             | 512                     |  |  |  |