PHAST<sup>®</sup>-12N Device STM-4/OC-12 SDH/SONET Overhead Terminator with **Telecom Bus Interface** TXC-06312

> DATA SHEET PRODUCT PREVIEW

# FEATURES

- Bit-serial LVPECL SDH/SONET line interface with integrated clock recovery and clock synthesis

- single 622.08 Mbit/s STM-4/OC-12 signal or

- four 155.52 Mbit/s STM-1/OC-3 signals

- Bit-serial LVDS 622.08 Mbit/s APS port

- Supports 1+1, 1:1 and 1:n APS for STM-1/OC-3 and STM-4/OC-12 signals using a serial port interface

- Complete RS/section and MS/line overhead processing

- Complete high order path overhead processing at VC-3/VC-4/VC-4-Xc/STS-1/STS-3c/STC-6c/STS-9c/STS-12c SPE level

- High order path cross-connect with VC-3/STS-1 SPE granularity

- Byte-wide 77.76 MHz Telecom Bus terminal interface

- MS/Line or RS/Section DCC access port per line

- Ring Ports for line/path ring applications

- TOH and POH access port

- 16-bit wide microprocessor interface, selectable between Motorola or Intel

- Software device driver is provided

- Boundary scan and line loopback

- +3.3V and +1.8V power supplies, 3.3V digital I/O leads

- 376-lead plastic ball grid array (PBGA) package (23 mm x 23 mm)

# DESCRIPTION

The PHAST<sup>®</sup>-12N is a highly integrated SDH/SONET overhead terminator device designed for TDM payload mappings. A single PHAST-12N can terminate four individual STM-1/OC-3 lines or a single STM-4/OC-12 line. Each SDH/SONET terminator has a line interface block that performs clock synthesis and clock recovery for four 155.52 Mbit/s signals or a single 622.08 Mbit/s serial signal.

The PHAST-12N device provides glueless 1+1, 1:1 and 1:n APS for STM-1/OC-3 and STM-4/OC-12 applications using a 622.08 Mbit/s serial APS port interface.

The PHAST-12N device provides RS (section) and MS (line) overhead processing, high order pointer tracking and retiming, and high order path overhead processing and performance monitoring. It provides full non-blocking cross connecting at the high order path level with VC-3/STS-1 SPE granularity allowing path loopbacks, MS or line protection and UPSR and SNC/P path protection.

A fully functional Device Driver is available through TranSwitch Applications Engineering.

# APPLICATIONS

SDH/SONET add/drop and terminal multiplexers

www.transwitch.com

- Linear MS/Line protection

- Multiservice applications

contain information on

**PREVIEW** information documents

PRODUCT products in

development. Features

ð

change. Contact

characteristic data and other specifications are subject to change. Contact TranSwitch Applications Engineering for current information on this product.

their formative or design phase c data and other specifications are

Line/Path TOH/POH DCC Clocks. LINE SIDE **TERMINAL SIDE Ring Ports** Ports Ports Control/Status +1.8V +3.3V PHAST-12N Tx/Rx Serial Line STM-4/OC-12 SDH/SONET 77.76 MHz Interfaces **Overhead Terminator** Telecom Bus (four 155.52 Mbit/s or with Telecom Bus Interface one 622.08 Mbit/s) TXC-06312 Microprocessor Boundary Tx/Rx Serial Interface **APS Port** Scan U.S. Patents No. 2,695,990; 4,967,405; 5,040,170; 5,142,529; 5,257,261; 5,265,096; 5,331,641; 5,724,362 U.S. and/or foreign patents issued or pending Copyright © 2004 TranSwitch Corporation Document Number: PRODUCT PREVIEW TXC-06312-MB, Ed. 4 EtherMap is a trademark of TranSwitch Corporation TranSwitch, TXC, TEMx28 and PHAST are registered trademarks of TranSwitch Corporation April 2004 TranSwitch Corporation • 3 Enterprise Drive Shelton, Connecticut 06484 USA •

Tel: 203-929-8810 • Fax: 203-926-9453 •

Proprietary TranSwitch Corporation Information for use Solely by its Customers

PHAST-12N TXC-06312

**DATA SHEET**

#### - IMPORTANT NOTICE -

TranSwitch Corporation reserves the right to make changes to its products, circuits or documentation described herein without notice.

EXCEPT AS SET FORTH IN A WRITTEN BINDING AGREEMENT BETWEEN TRANSWITCH CORPORATION AND A USER OF ITS PRODUCTS, TRANSWITCH CORPORATION ASSUMES NO LIABILITY FOR (A) CUSTOMER APPLICATIONS, INCLUDING CUSTOMER'S CIRCUITS, FIRMWARE AND SOFTWARE, (B) CUSTOMER PRODUCT DESIGN, (C) TRANSWITCH CORPORATION PRODUCT OR CUSTOMER PRODUCT SOFTWARE PERFORMANCE, (D) USE BY CUSTOMER OF ANY PRODUCT OR RELATED SAMPLE CIRCUIT OR APPLICATION PROVIDED HEREIN OR (E) INFRINGEMENT OF A THIRD PARTY'S PATENTS OR OTHER INTELLECTUAL PROPERTY RIGHTS ARISING OUT OF USE OF ANY AND ALL INFORMATION PROVIDED HEREIN. TRANSWITCH CORPORATION EXPRESSLY DISCLAIMS ALL REPRESENTATIONS AND WARRANTIES RELATED TO THE INFORMATION, PRODUCTS AND SAMPLE APPLICATIONS AND CIRCUITS CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF FITNESS FOR PURPOSE INTENDED, MERCHANTABILITY AND NON-INFRINGEMENT, AND WILL NOT BE LIABLE FOR DIRECT OR INDIRECT DAMAGES RESULTING FROM THEIR USE.

TRANSWITCH DOES NOT OFFER CUSTOMER EITHER AN EXPRESS OR AN IMPLIED LICENSE UNDER ANY PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT COVERING OR RELATED TO ANY DESIGN, COMBINATION, MACHINE OR PROCESS IN WHICH TRANSWITCH CORPORATION'S PRODUCTS OR SERVICES MIGHT BE OR ARE USED, INCLUDING BUT NOT LIMITED TO THE USES DESCRIBED HEREIN. THE CUSTOMER IS URGED TO CONSULT WITH LEGAL COUNSEL BEFORE DECIDING ON A PARTICULAR APPLICATION, CIRCUIT, FIRMWARE OR SOFTWARE WITH ANY OF TRANSWITCH'S PRODUCTS.

TRANSWITCH CORPORATION'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS (OR SIMILAR APPLICATIONS WHERE COMPONENT FAILURE COULD RESULT IN LOSS OF LIFE OR PHYSICAL HARM) WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF TRANSWITCH CORPORATION.

As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# PHAST-12N TXC-06312

# TABLE OF CONTENTS

| Section Pa                                             | age  |

|--------------------------------------------------------|------|

| List of Figures                                        | 6    |

| List of Tables                                         | 8    |

| Applicable Standards Documentation                     | . 10 |

| Overview                                               | . 11 |

| Features                                               | . 12 |

| Modes of Operation                                     | . 12 |

| Line Interface                                         | . 12 |

| APS Port Interface                                     | . 13 |

| RS/Section Layer Processing                            | . 13 |

| MS/Line Layer Processing                               | . 13 |

| High Order Path Layer Processing                       | . 13 |

| High Order Path Cross-Connect                          | . 14 |

| Telecom Bus Interface                                  | . 14 |

| Microprocessor Interface                               | . 15 |

| Testing                                                | . 15 |

| Device Driver                                          | . 15 |

| Block Diagram                                          | . 16 |

| Functional Model                                       | . 17 |

| Block Diagram Description                              | . 18 |

| Line Side                                              |      |

| APS Port Side                                          | . 18 |

| High Order Path Cross Connect                          | . 19 |

| Terminal Side                                          |      |

| Lead Diagram                                           |      |

| Lead Descriptions                                      |      |

| Selected Parameter Values                              |      |

| Absolute Maximum Ratings and Environmental Limitations |      |

| Thermal Characteristics                                |      |

| Power Requirements                                     |      |

| Power Supply Sharing, Filtering and Other Requirements |      |

| LVPECL I/O Recommendations:                            |      |

| Input, Output and Input/Output Parameters              |      |

| Timing Characteristics                                 |      |

| Operation                                              |      |

| Modes                                                  |      |

| Line Interface Mode                                    |      |

| SDH/SONET Mapping                                      |      |

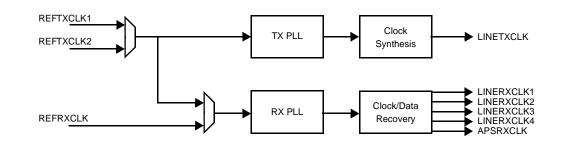

| Clock Architecture                                     |      |

| Clocks and Software-Access                             |      |

| Loss of Clock Detection                                |      |

| Powerup, Initialization and Startup                    |      |

| Reset                                                  |      |

| External Lead Controlled Hardware Reset                |      |

| Microprocessor Controlled Hardware Reset (RESETH)      |      |

| Microprocessor Controlled Reset Per Clockdomain        |      |

| Line Interface                                         |      |

| APS Interface                                          |      |

| APS Interface Generator                                |      |

| APS Interface Monitor                                  |      |

|                                                        |      |

# DATA SHEET

| Regenerator Section (section) Overhead Processing                   |     |

|---------------------------------------------------------------------|-----|

| Regenerator Section Overhead Generator                              | 88  |

| Regenerator Section Overhead Monitor                                | 89  |

| Multiplex Section (line) Overhead Processing                        | 89  |

| Multiplex Section Overhead Generator                                | 89  |

| Multiplex Section Overhead Monitor                                  | 90  |

| High Order Cross-Connect                                            | 92  |

| Automatic Protection Switching                                      | 93  |

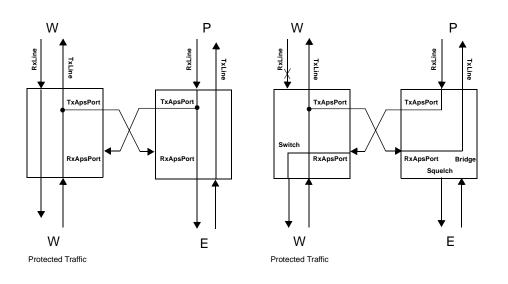

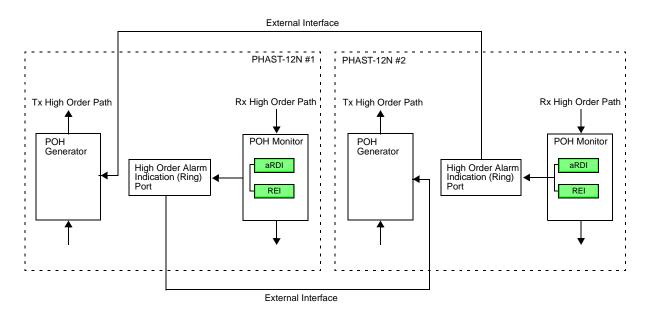

| Single Device Operation                                             | 93  |

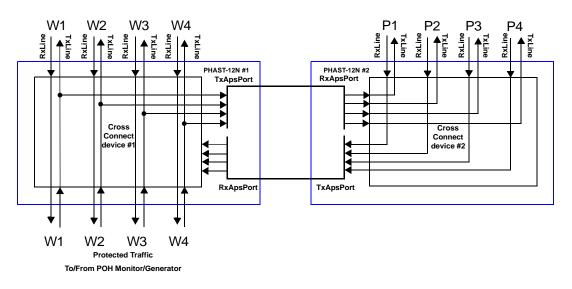

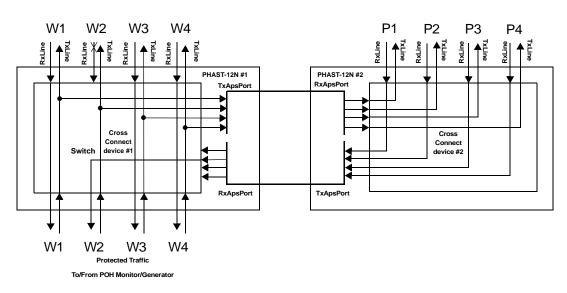

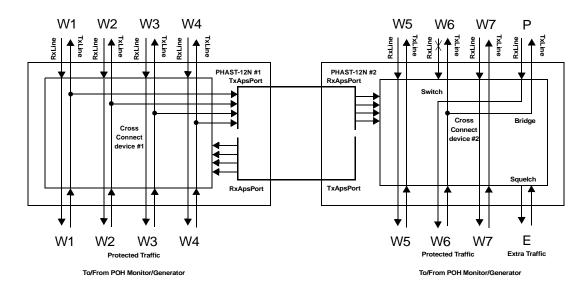

| Dual Device Operation                                               | 93  |

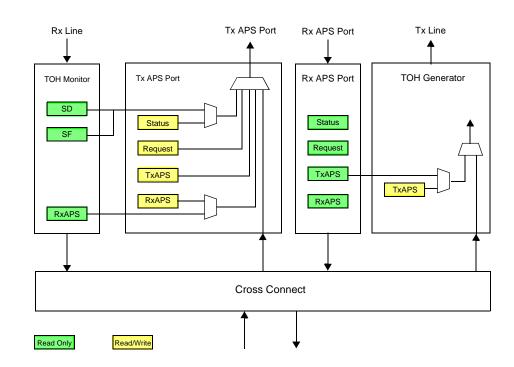

| APS Port Architecture                                               | 94  |

| Example: STM-4/OC-12 Mode, 1+1 APS Protection                       | 95  |

| Example: STM-4/OC-12 Mode, 1:1 APS Protection                       | 96  |

| Example: STM-1 Mode, 1+1 APS Protection                             |     |

| Example: STM-1 Mode, 1:1 APS Protection                             |     |

| Example: STM-1 Mode, 1:n APS Protection                             |     |

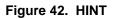

| High Order Pointer Tracking, Retiming and Pointer Generation        |     |

| Line and APS Side Pointer Tracking, Retiming and Pointer Generation |     |

| Detection of Concatenated Structures                                |     |

| Frame Reference Pulses                                              |     |

| Generation of Frame Reference Pulse                                 |     |

| Locking on External Frame Reference Pulse                           |     |

| Terminal Side Retiming and Pointer Generation                       |     |

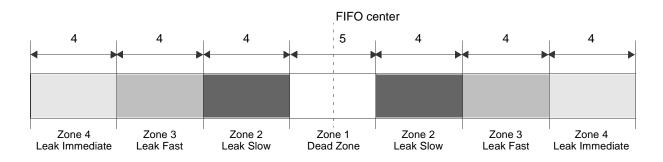

| Retimer FIFO Leak Registers.                                        |     |

| High Order Path Overhead Processing                                 |     |

| High Order Path Overhead Generator                                  |     |

| High Order Path Overhead Monitor                                    |     |

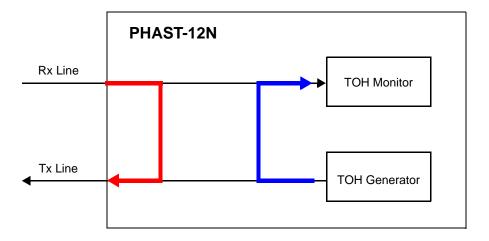

| TOH Port Interface                                                  |     |

| Transmit TOH Port Interface                                         |     |

| Receive TOH Port Interface                                          |     |

| DCC Port Interface                                                  |     |

| Transmit DCC Port Interface                                         |     |

| Receive DCC Port Interface                                          |     |

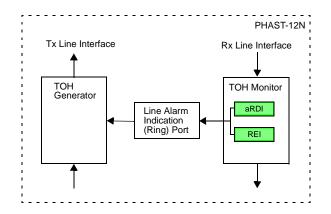

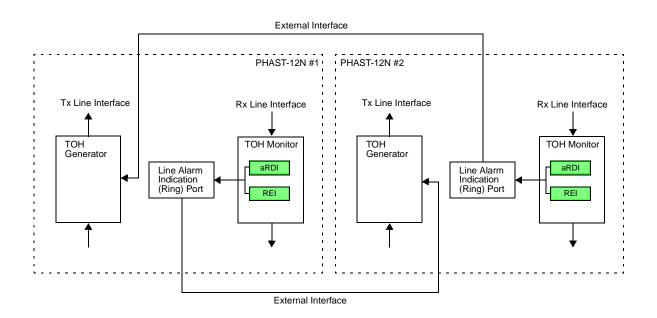

| Line Alarm Indication (Ring) Port Interface                         |     |

| Internal Line Alarm Indication (Ring) Port Interface                |     |

| External Line Alarm Indication (Ring) Port Interface                |     |

|                                                                     |     |

| High Order POH Port Interface                                       |     |

| Transmit High Order POH Port Interface                              |     |

| Receive High Order POH Port Interface                               |     |

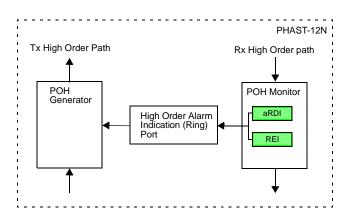

| High Order Alarm Indication (Ring) Port Interface                   |     |

| Internal High Order Alarm Indication (Ring) Port Interface          |     |

| External High Order Alarm Indication (Ring) Port Interface          |     |

| Telecom Bus                                                         | -   |

| Drop Bus Interface                                                  |     |

| Drop Bus Parity Selection                                           |     |

| Drop Bus Delay                                                      |     |

| Add Bus Interface                                                   |     |

| Add Bus Timing Modes                                                |     |

| Add Bus Parity Selection                                            |     |

| Add Bus Delay                                                       |     |

| BER Supervision for B2/B3                                           |     |

| Bursty Distribution of Errors                                       |     |

| Poisson Distribution of Errors                                      | 121 |

#### PHAST-12N TXC-06312

| Loopbacks                                 | 122 |

|-------------------------------------------|-----|

| Performance Counters                      | 123 |

| Trail Trace Identifier Process            | 124 |

| TTI Formats                               | 124 |

| TTI Mismatch Process                      | 124 |

| TTI Report Process                        | 124 |

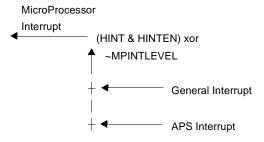

| Defects and Interrupts                    | 126 |

| Unlatched Defects (Correlated)            | 126 |

| Latched Defects                           | 126 |

| Defects Mask                              | 126 |

| Interrupts                                | 126 |

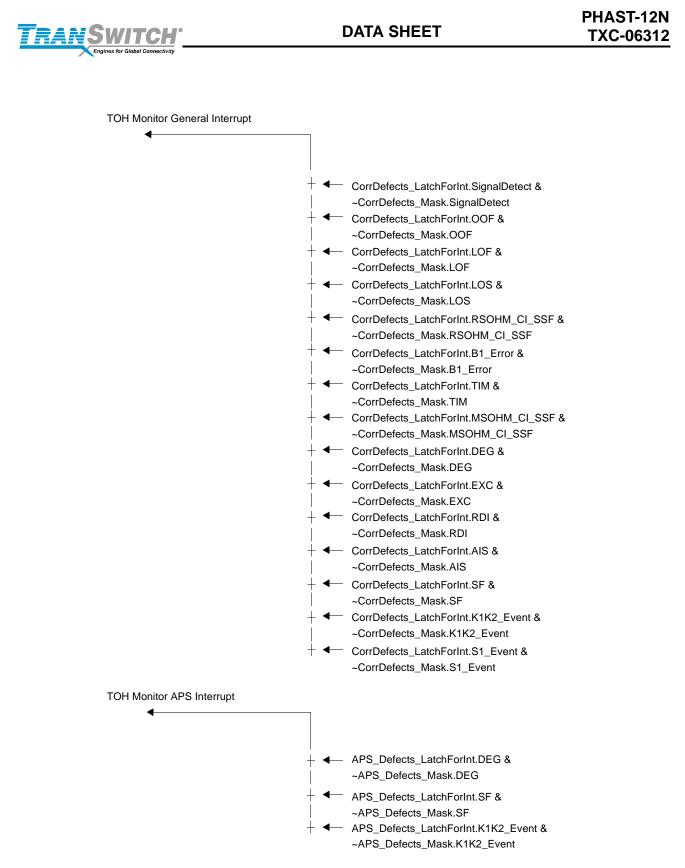

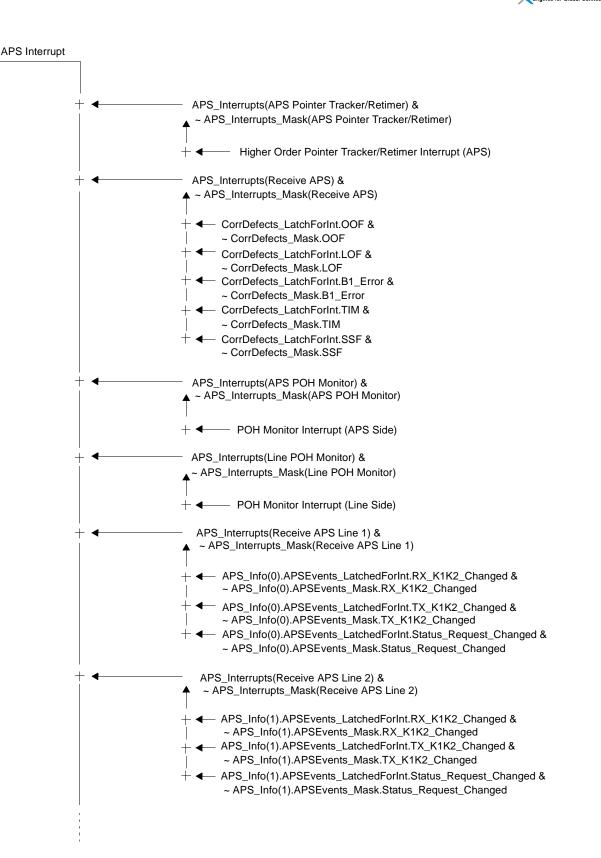

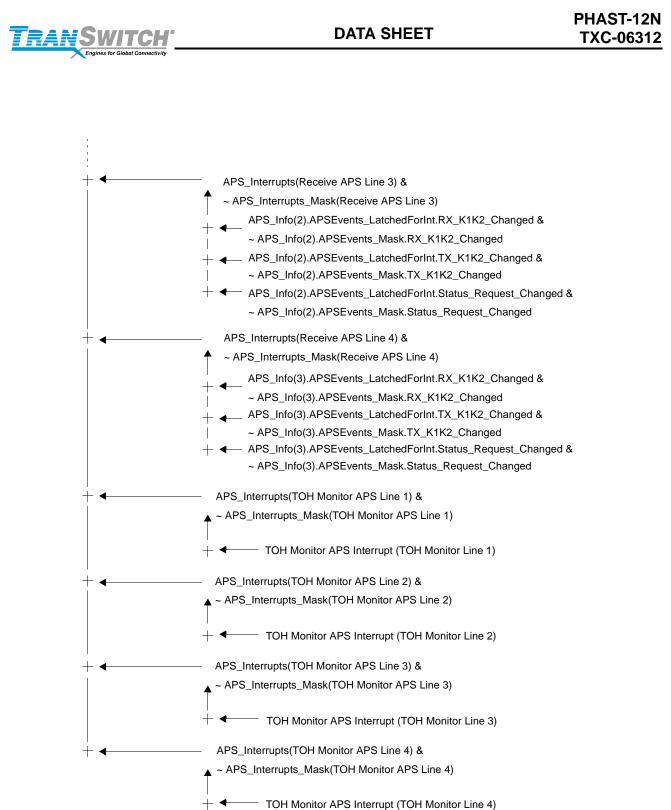

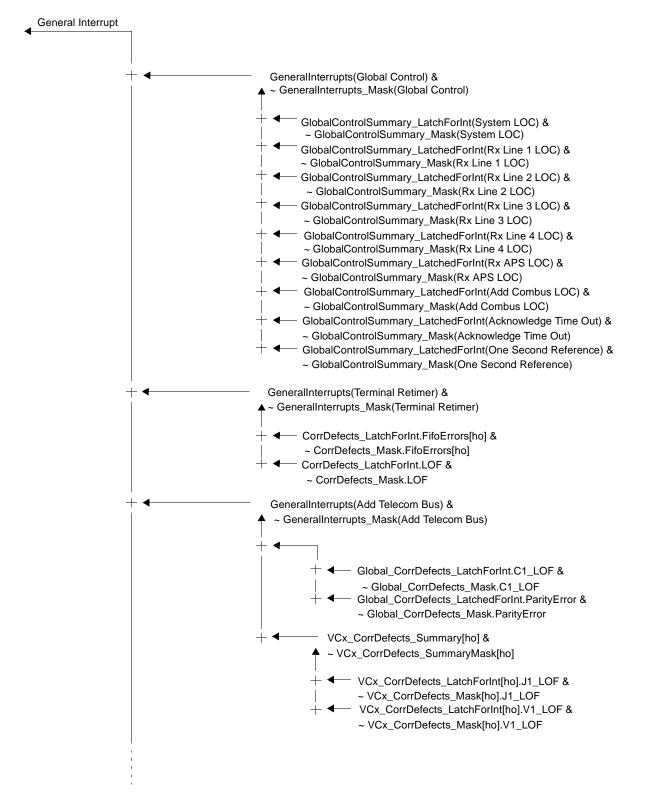

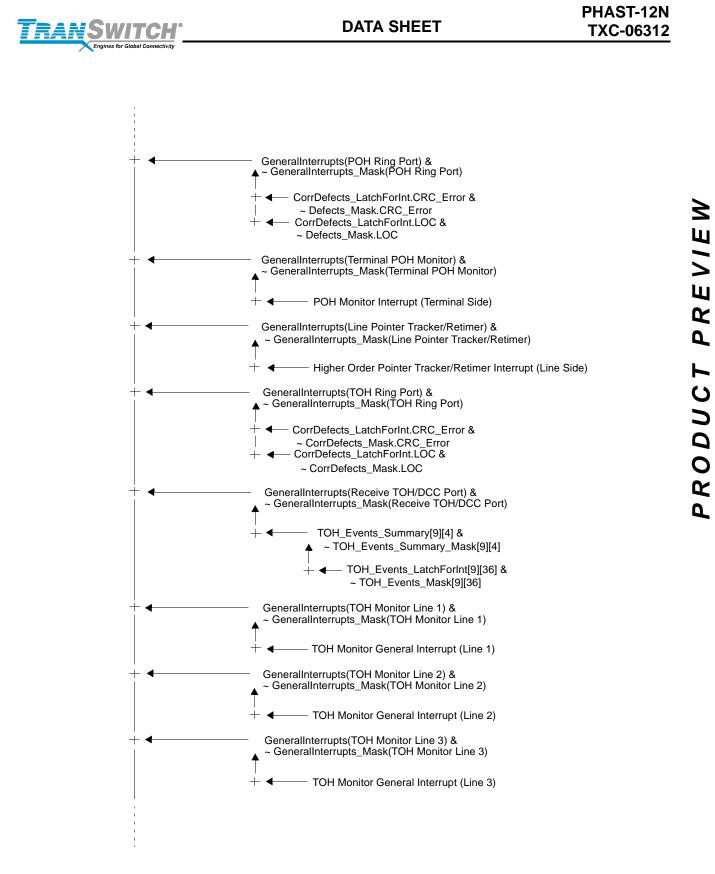

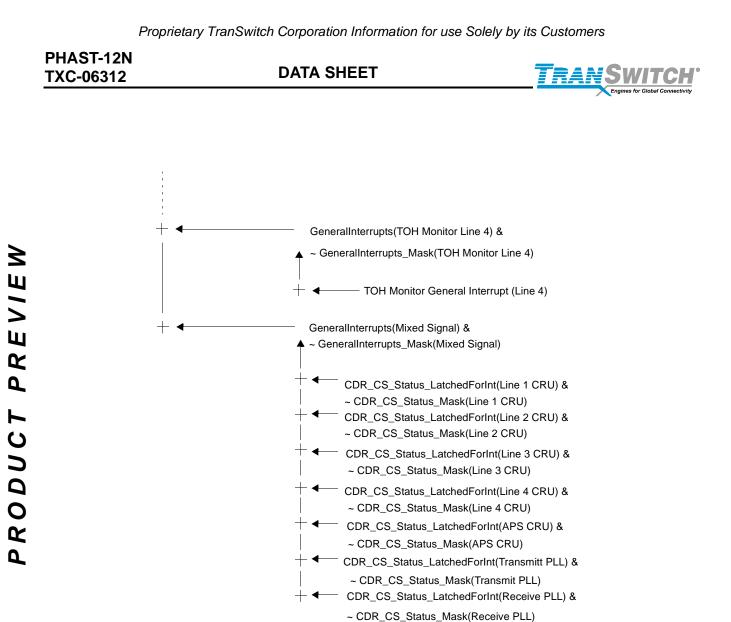

| Alarm Interrupt Tree                      | 127 |

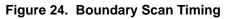

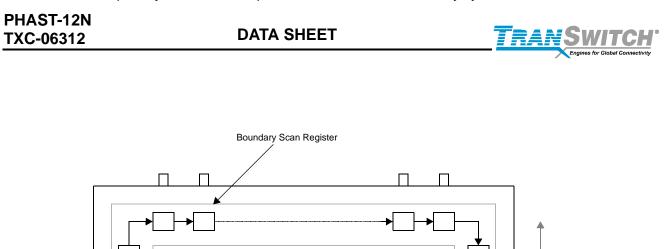

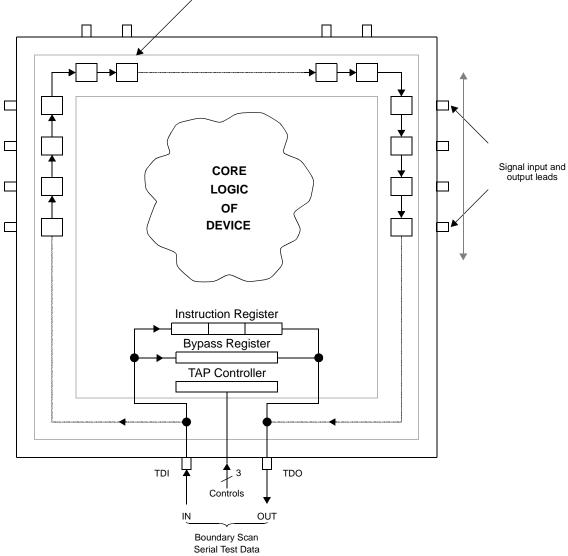

| Boundary Scan                             | 135 |

| Introduction                              | 135 |

| Boundary Scan Operation                   |     |

| Boundary Scan Reset                       |     |

| Boundary Scan Chain                       | 136 |

| Memory Maps and Bit Descriptions.         | 137 |

| Overview                                  | 137 |

| Global Control                            | 138 |

| Line Ring Port/Alarm Interface            | 140 |

| Reset Generator                           |     |

| Interrupt                                 | 141 |

| Transmit APS Port                         | 143 |

| POH Generator                             | 144 |

| TOH Monitor                               | 147 |

| TOH Generator                             | 151 |

| TOH and DCC Port                          | 153 |

| High Order Pointer Tracker and Retimer    | 155 |

| Retimer                                   | 158 |

| Clock Recovery/Clock Synthesis/Serdes     | 159 |

| Receive APS Port                          | 163 |

| Cross Connect                             | 165 |

| Add Telecom Bus                           | 166 |

| High Order Path Ring Port/Alarm Interface | 168 |

| JTAG Master                               | 169 |

| Drop Telecom Bus                          | 170 |

| POH Monitor                               | 171 |

| Package Information                       | 177 |

| Application Examples                      | 178 |

| Ordering Information                      | 180 |

| Related Products                          |     |

| Standards Documentation Sources           | 181 |

| List of Data Sheet Changes                | 183 |

Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at www.transwitch.com. Customers who are using a TranSwitch Product, or planning to do so, must register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They must also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

Figure

# **DATA SHEET**

Page

# LIST OF FIGURES

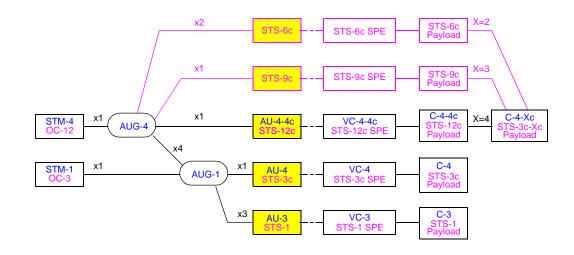

| 1  | Supported SDH/SONET Mapping                                               | . 12 |

|----|---------------------------------------------------------------------------|------|

| 2  | PHAST-12N TXC-06312 Block Diagram                                         |      |

| 3  | PHAST-12N Functional Model                                                | . 17 |

| 4  | PHAST-12N TXC-06312 376-Lead Plastic Ball Grid Array Package Lead Diagram | . 20 |

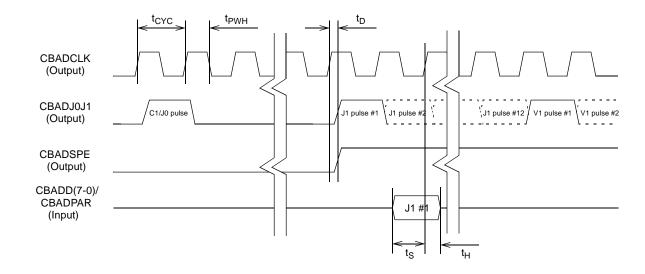

| 5  | DROP Bus Timing                                                           | . 51 |

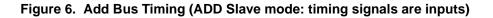

| 6  | Add Bus Timing (ADD Slave mode: timing signals are inputs)                | . 52 |

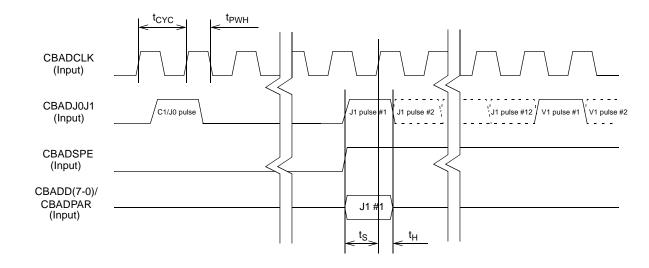

| 7  | ADD Bus Timing (ADD Master mode: timing signals are outputs)              | . 53 |

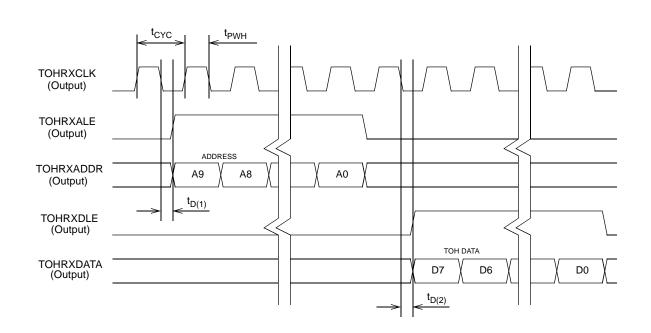

| 8  | RX TOH Byte Interface                                                     | . 54 |

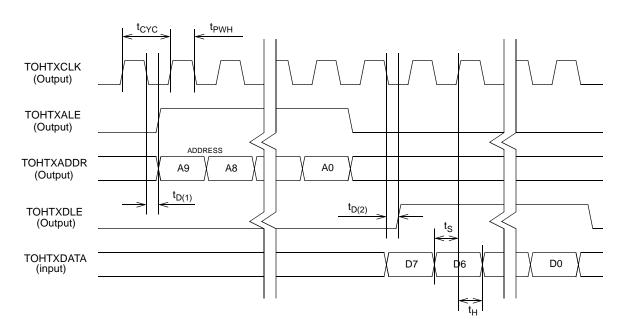

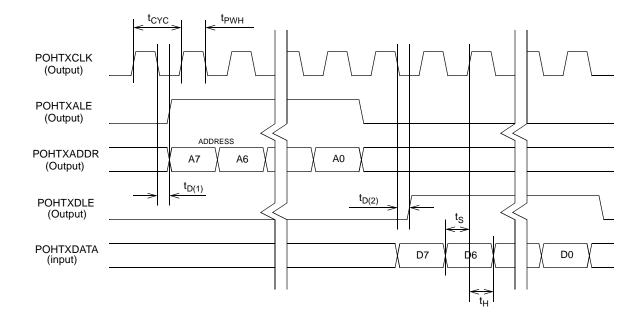

| 9  | TX TOH Byte Interface                                                     | . 55 |

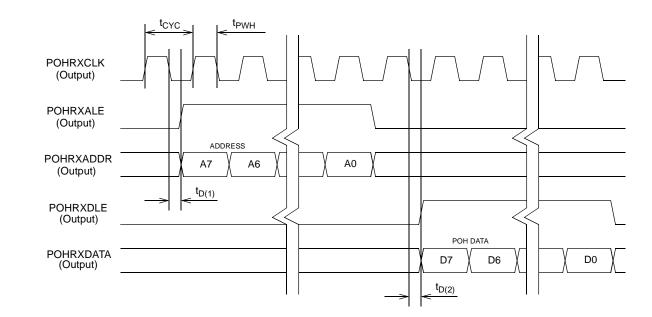

| 10 | RX High Order POH Byte Interface                                          | . 56 |

| 11 | TX High Order POH Byte Interface                                          | . 57 |

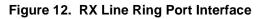

| 12 | RX Line Ring Port Interface                                               | . 58 |

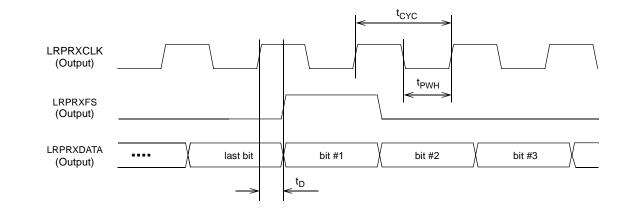

| 13 | TX Line Ring Port Interface                                               | . 59 |

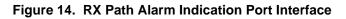

| 14 | RX Path Alarm Indication Port Interface                                   | . 60 |

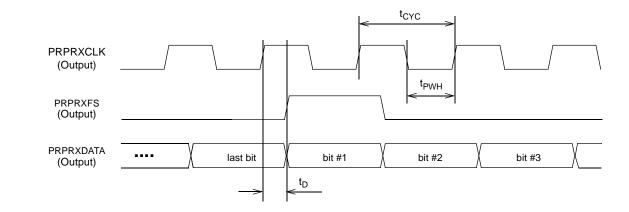

| 15 | TX Path Alarm Indication Port Interface                                   | . 61 |

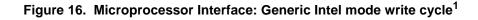

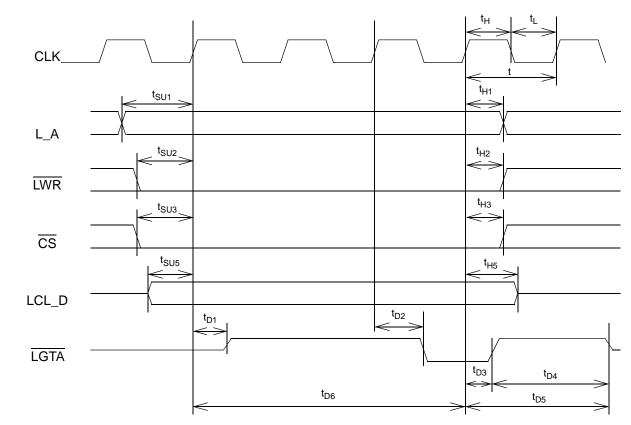

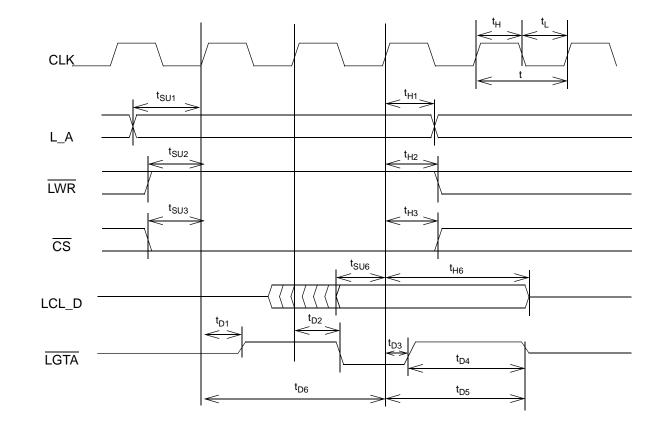

| 16 | Microprocessor Interface: Generic Intel mode write cycle                  | . 62 |

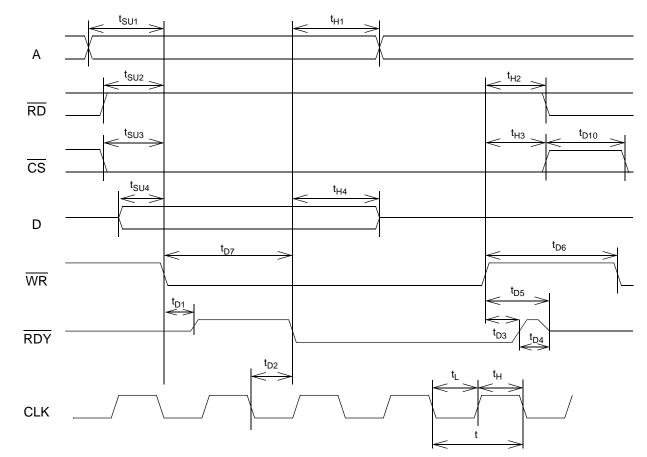

| 17 | Microprocessor Interface: Generic Intel mode read cycle                   | . 64 |

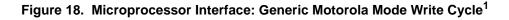

| 18 | Microprocessor Interface: Generic Motorola Mode Write Cycle               | . 66 |

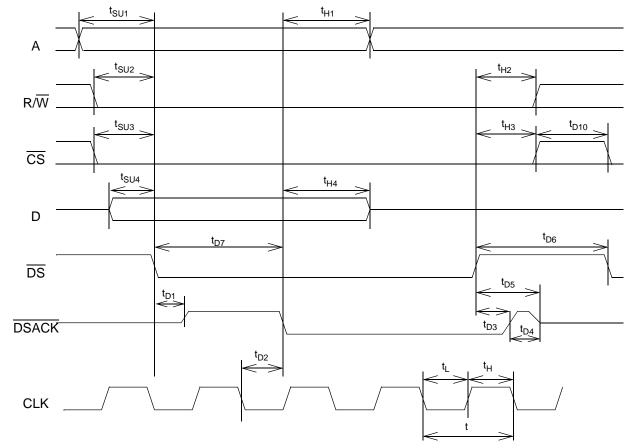

| 19 | Microprocessor Interface: Generic Motorola Mode Read Cycle                | . 68 |

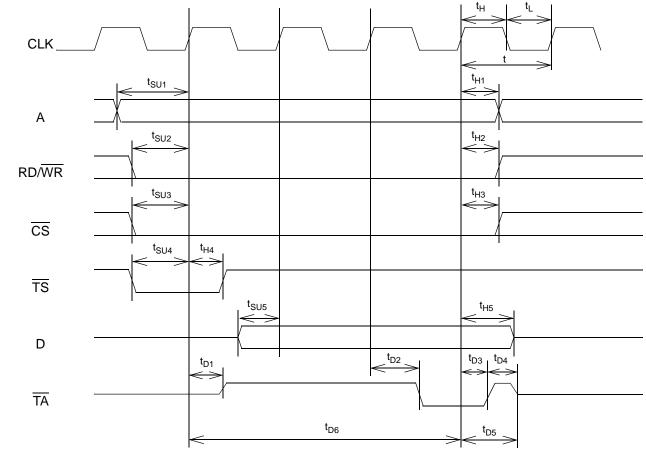

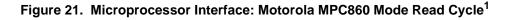

| 20 | Microprocessor Interface: Motorola MPC860 Mode Write Cycle                | . 70 |

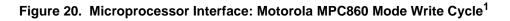

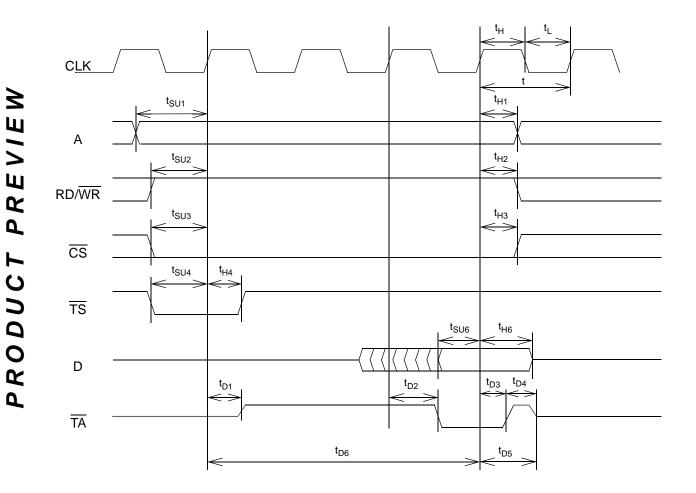

| 21 | Microprocessor Interface: Motorola MPC860 Mode Read Cycle                 | . 72 |

| 22 | Microprocessor Interface: Motorola MPC8260 Local Bus Mode Write Cycle     | . 74 |

| 23 | Microprocessor Interface: Motorola MPC8260 Local Bus Mode Read Cycle      | . 76 |

| 24 | Boundary Scan Timing                                                      | . 78 |

| 25 | Clock Recovery/Clock Synthesis                                            | . 82 |

| 26 | STM-1/OC-3, 1:3 APS with one PHAST-12N                                    | . 93 |

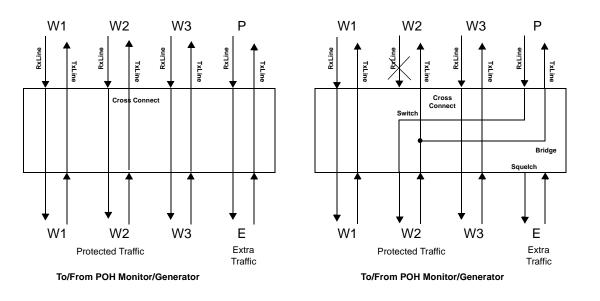

| 27 | APS Port Architecture                                                     | . 94 |

| 28 | STM-4/OC-12, 1+1 APS                                                      | . 95 |

| 29 | STM-4/OC-12, 1:1 APS                                                      | . 96 |

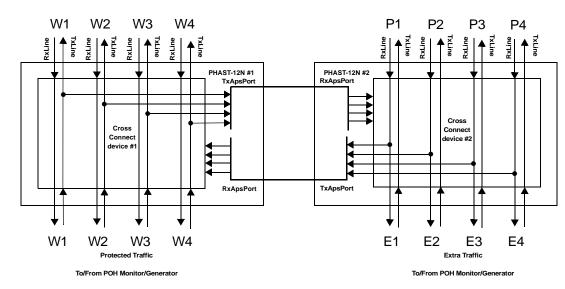

| 30 | STM-1/OC-3, 1+1 APS Idle State                                            | . 97 |

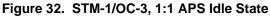

| 31 | STM-1/OC-3, 1+1 APS Switch State                                          | . 97 |

| 32 | STM-1/OC-3, 1:1 APS Idle State                                            | . 98 |

| 33 | STM-1/OC-3, 1:1 APS Switch State                                          | . 98 |

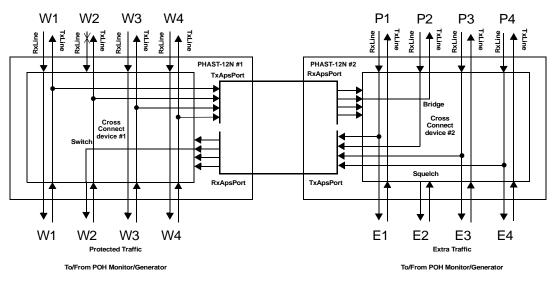

| 34 | STM-1/OC-3, 1:7 APS Idle State                                            | . 99 |

| 35 | STM-1/OC-3, 1:7 APS Switch State                                          | . 99 |

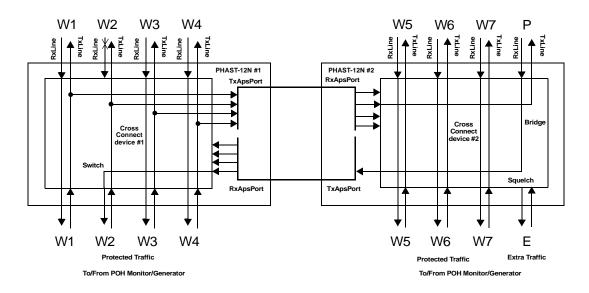

| 36 | STM-1/OC-3, 1:7 APS Switch State                                          | 100  |

|    | Retimer FIFO Filling Levels                                               |      |

| 38 | Internal Line Alarm Indication (Ring) Port Interface                      | 112  |

| 30 | External Line Alarm Indication (Ring) Port Interface                      | 112  |

| 7  | ADD Bus Timing (ADD Master mode: timing signals are outputs)          | . 53 |

|----|-----------------------------------------------------------------------|------|

| 8  | RX TOH Byte Interface                                                 | . 54 |

| 9  | TX TOH Byte Interface                                                 | . 55 |

| 10 | RX High Order POH Byte Interface                                      | . 56 |

| 11 | TX High Order POH Byte Interface                                      | . 57 |

| 12 | RX Line Ring Port Interface                                           | . 58 |

| 13 | TX Line Ring Port Interface                                           | . 59 |

| 14 | RX Path Alarm Indication Port Interface                               | . 60 |

| 15 | TX Path Alarm Indication Port Interface                               | . 61 |

| 16 | Microprocessor Interface: Generic Intel mode write cycle              | . 62 |

| 17 | Microprocessor Interface: Generic Intel mode read cycle               | . 64 |

| 18 | Microprocessor Interface: Generic Motorola Mode Write Cycle           | . 66 |

| 19 | Microprocessor Interface: Generic Motorola Mode Read Cycle            | . 68 |

| 20 | Microprocessor Interface: Motorola MPC860 Mode Write Cycle            | . 70 |

| 21 | Microprocessor Interface: Motorola MPC860 Mode Read Cycle             | . 72 |

| 22 | Microprocessor Interface: Motorola MPC8260 Local Bus Mode Write Cycle | . 74 |

| 23 | Microprocessor Interface: Motorola MPC8260 Local Bus Mode Read Cycle  | . 76 |

| 24 | Boundary Scan Timing                                                  | . 78 |

| 25 | Clock Recovery/Clock Synthesis                                        | . 82 |

| 26 | STM-1/OC-3, 1:3 APS with one PHAST-12N                                | . 93 |

| 27 | APS Port Architecture                                                 | . 94 |

| 28 | STM-4/OC-12, 1+1 APS                                                  | . 95 |

| 29 | STM-4/OC-12, 1:1 APS                                                  | . 96 |

| 30 | STM-1/OC-3, 1+1 APS Idle State                                        | . 97 |

| 31 | STM-1/OC-3, 1+1 APS Switch State                                      | . 97 |

| 32 | STM-1/OC-3, 1:1 APS Idle State                                        | . 98 |

| 33 | STM-1/OC-3, 1:1 APS Switch State                                      | . 98 |

| 34 | STM-1/OC-3, 1:7 APS Idle State                                        | . 99 |

| 35 | STM-1/OC-3, 1:7 APS Switch State                                      | . 99 |

| 36 | STM-1/OC-3, 1:7 APS Switch State                                      | 100  |

| 37 | Retimer FIFO Filling Levels                                           | 103  |

| 38 | Internal Line Alarm Indication (Ring) Port Interface                  | 112  |

| 39 | External Line Alarm Indication (Ring) Port Interface                  |      |

| 40 | Internal High Order Alarm Indication (Ring) Port Interface            | 116  |

| 41 | External High Order Alarm Indication (Ring) Port Interface            | 116  |

| 42 | HINT                                                                  |      |

| 43 | High Order Point Tracker Retimer Interrupt Tree                       | 127  |

| 44 | POH Monitor Interrupt Tree                                            | 128  |

| 45 | TOH Monitor Interrupt Tree                                            | 129  |

| 46 | APS Interrupt Tree (part 1)                                           | 130  |

| 47 | APS Interrupt Tree (part 2)                                           | 131  |

# PHAST-12N TXC-06312

| 48 | General Interrupt Tree (part 1)                              | 132 |

|----|--------------------------------------------------------------|-----|

| 49 | General Interrupt Tree (part 2)                              | 133 |

| 50 | General Interrupt Tree (part 3)                              | 134 |

| 51 | Boundary Scan Schematic                                      | 136 |

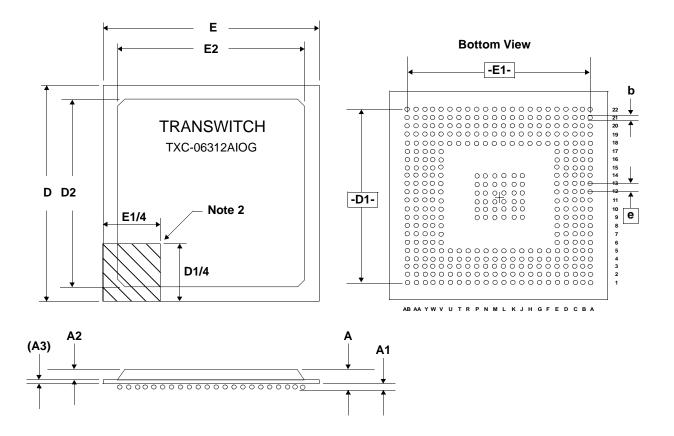

| 52 | PHAST-12N TXC-06312 376-Lead Plastic Ball Grid Array Package | 177 |

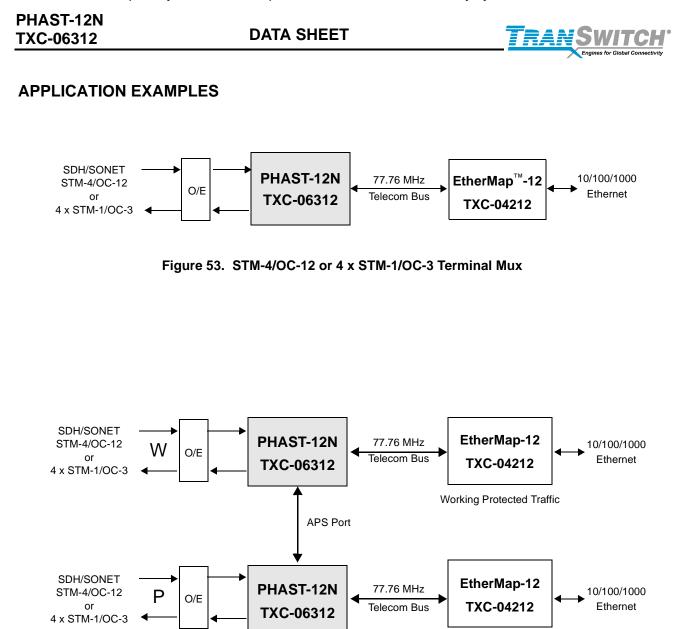

| 53 | STM-4/OC-12 or 4 x STM-1/OC-3 Terminal Mux                   | 178 |

| 54 | STM-4/OC-12 or 4 x STM-1/OC-3 1+1, 1:1 APS Terminal Mux      | 178 |

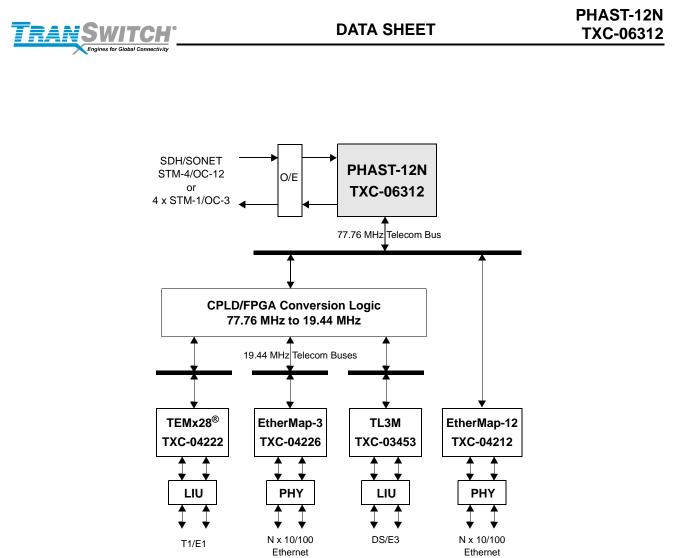

| 55 | STM-4/OC-12 or 4 x STM-1/OC-3 Ethernet and TDM Terminal Mux  | 179 |

# **DATA SHEET**

# LIST OF TABLES

# PRODUCT PREVIEW

| Tab      | ible Pa                                                                      |     |  |

|----------|------------------------------------------------------------------------------|-----|--|

| 1        | Memory Map Overview                                                          | 137 |  |

| 2        | Global Control (T_GLOBAL_CONTROL)                                            |     |  |

| 3        | Device Identification (T_DeviceIdentification)                               | 139 |  |

| 4        | Ring Port/Alarm Interface (T_TOH_RING_PORT)                                  |     |  |

| 5        | Ring Port/Alarm Interface Defects (T_TOH_RING_PORT_Defects)                  |     |  |

| 6        | Reset Generator (T_RGEN)                                                     |     |  |

| 7        | Interrupt (T_INTERRUPT)                                                      |     |  |

| 8        | Interrupt Configuration (T_InterruptCtrl_Config)                             |     |  |

| 9        | Transmit APS Port (T_TX_APS)                                                 |     |  |

| 10       | Transmit APS Port Configuration (T_TX_APS_Common_Config)                     |     |  |

| 11       | Transmit APS Port Line Configuration (T_TX_APS_Config)                       |     |  |

| 12       | POH Generator (T_POH_GENERATOR).                                             |     |  |

| 13       | POH Generator Common Configuration (T_VCXPG_Common_Config)                   |     |  |

| 14       | AUG-1 Mode Configuration (T_AUG1_Mode_Config)                                |     |  |

| 15       | POH Generator Path Configuration (T_VCXPG_VC_Config)                         |     |  |

| 16       | Transmit POH Byte RAM (T_VCXPG_RAMBytes)                                     |     |  |

| 17       | POH Generator Path Mode (T_VCXPG_Mode_record)                                |     |  |

| 18       | POH Byte Source Control (T_VCXPG_Control_record)                             |     |  |

| 19       | TOH Monitor (T_TOH_MONITOR)                                                  |     |  |

| 20       | TOH Monitor Performance Counters (T_TOH_MONITOR_Performance_Counters)        |     |  |

| 20       | TOH Monitor Status (T_TOH_MONITOR_Line_Status)                               |     |  |

| 22       | TOH Monitor Events/Defects (T_TOH_MONITOR_Defects)                           |     |  |

| 22       | TOH Monitor APS Events/Defects (T_TOH_MONITOR_APS_Defects)                   |     |  |

| 23<br>24 | TOH Monitor Configuration (T_TOH_MONITOR_Common_Config)                      |     |  |

| 24       | J0 TTI Configuration (T_TOH_MONITOR_TTI_Config)                              |     |  |

| 26       | BER Detection Configuration (T_BIP_Detector_Config)                          |     |  |

| 20       | Poisson Distribution BER Detection (T_BIP_PoissonDetector_Config)            |     |  |

| 28       | Bursty Distribution BER Detection (T_BIP_BurstyDetector_Config)              |     |  |

| 20<br>29 | TOH Generator (T_TOH_GENERATOR)                                              |     |  |

|          | Transmit TOH Port Configuration (T_TOHG_Common_Config)                       |     |  |

| 30<br>31 | TOH Configuration (T_TOHG_Line_Config)                                       |     |  |

|          | Receive TOH and DCC Port (T_RX_TOH_DCC_PORT)                                 |     |  |

| 32       | Receive TOH and DCC Folt (1_KA_TOH_DCC_FORT)                                 |     |  |

| 33<br>24 | Receive DCC Port Configuration (T_RXTDP_Line_Config)                         |     |  |

| 34<br>35 | Pointer Tracker and Retimer (T_HO_PTR_RETIMER)                               |     |  |

|          |                                                                              |     |  |

| 36       | Pointer Tracker and Retimer Defect/Event Summary (T_HOPTRRT_Defects_Summary) |     |  |

| 37       | Pointer Tracker and Retimer Common Configuration (T_HOPTRRT_Common_Config)   |     |  |

| 38       | Pointer Tracker and Retimer per path (T_HOPTRRT_VCx)                         |     |  |

| 39       | Pointer Tracker and Retimer Path Configuration (T_HOPTRRT_VC3_TUG3_Config)   |     |  |

| 40       | Pointer Tracker Path Status (T_HOPTR_VCx_Status)                             |     |  |

| 41       | Pointer Justification Counters (T_HOPTRRT_PerfCounters)                      |     |  |

| 42       | Pointer Tracker and Retimer Defects (T_HOPTRRT_Defects)                      |     |  |

| 43       | Retimer (T_RETIMER)                                                          |     |  |

| 44       | Retimer Defects (T_RT_Defects)                                               |     |  |

| 45       | Retimer Common Configuration (T_RT_Common_Config)                            |     |  |

| 46       | Retimer per Path (T_RT_VCx)                                                  |     |  |

| 47       | Retimer Path Configuration (T_RT_VC3_TUG3_Config)                            | 159 |  |

| 48 | Retimer Performance Counters (T_RT_PerfCounters)                           | 159   |

|----|----------------------------------------------------------------------------|-------|

| 49 | Clock Recovery/Clock Synthesis/SerDes (T_ANALOG)                           | 159   |

| 50 | Loopback Configuration (T_LoopbackSelect)                                  | . 160 |

| 51 | High Speed Interface Power Down (T_PadPowerDown)                           | . 161 |

| 52 | Setup of Clock Recovery/Clock Synthesis/SerDes (T_CDR_CS_Setup)            | . 161 |

| 53 | PLL Control (T_PLL_Control)                                                | 162   |

| 54 | Receive APS Port (T_RX_APS)                                                | . 163 |

| 55 | Receive APS Port Common Configuration (T_RX_APS_Common_Config)             | . 164 |

| 56 | Receive APS Port Defects (T_RX_APS_Defects)                                | . 164 |

| 57 | Receive APS Port per line (T_RX_APS_APSInfo)                               | . 164 |

| 58 | Receive APS Port Status (T_RX_APS_APSBytes_Status)                         |       |

| 59 | Receive APS Port Events (T_RX_APS_APSBytes_Event)                          | 165   |

| 60 | Cross Connect (T_VC_XCONNECT)                                              | 165   |

| 61 | Cross Connect Bus Configuration (T_XC_Bus_Config)                          | . 165 |

| 62 | Cross Connect Time Slot Configuration (T_XConnect_Config)                  | 165   |

| 63 | Add Telecom Bus (T_DI_COMBUS)                                              | 166   |

| 64 | Add Bus Common Defects (T_DICB_Global_CorrDefects)                         | . 166 |

| 65 | Add Bus Defect Summary (t_dicb_VCx_CorrDefects_Summary)                    | 166   |

| 66 | Add Bus Common Configuration (T_DICB_Common_Config)                        | . 167 |

| 67 | Telecom Bus Path Configuration (T_VC3_TUG3_Mode_Config)                    | . 167 |

| 68 | Add Bus Path Defects (T_DICB_VCx_CorrDefects)                              | . 167 |

| 69 | Path Ring Port/Alarm Interface (T_HO_POH_RING_PORT)                        | . 168 |

| 70 | Path Ring Port/Alarm Interface Common Configuration (T_HOPR_Common_Config) | . 168 |

| 71 | Path Ring Port/Alarm Interface Defects (T_HOPR_Defects)                    | . 168 |

| 72 | Path Ring Port/Alarm Interface Path Configuration (T_HOPR_VC_Config)       | . 168 |

| 73 | JTAG Master (T_JTAG_MASTER)                                                | . 169 |

| 74 | Drop Telecom Bus (T_DO_COMBUS)                                             | . 170 |

| 75 | Drop Bus Path Configuration (T_DOCB_VC3_TUG3_Config)                       | . 170 |

| 76 | Drop Bus Common Configuration (T_DOCB_Common_Config)                       | . 170 |

| 77 | Drop Bus AUG-1 Configuration (T_DOCB_AUG1_Config)                          | . 171 |

| 78 | POH Monitor (T_VC_POH_MONITOR)                                             | . 171 |

| 79 | POH Monitor Path Configuration (T_VCXPM_Config)                            | . 171 |

| 80 | POH Monitor Expected J1/C2 (T_VCXPM_ExpectedBytes)                         | . 172 |

| 81 | POH Monitor Defects (T_VCXPM_Defects)                                      | . 173 |

| 82 | POH Monitor Common Configuration (T_VCXPM_Common_Config)                   | . 173 |

| 83 | POH Monitor Status (T_VCXPM_Common_Status)                                 | . 174 |

| 84 | J1 TTI Stable (T_VCXPM_Report)                                             | 175   |

| 85 | POH Monitor per path (T_VCXPM_Status)                                      | . 175 |

| 86 | POH Monitor Path Status (T_VCXPM_POH_Status)                               |       |

| 87 | POH Monitor Performance Counters (T_VCXPM_PM)                              | . 176 |

**DATA SHEET**

# APPLICABLE STANDARDS DOCUMENTATION

Standards documents applicable to the functions of the PHAST<sup>®</sup>-12N device are listed below.

| Short Name            | Description                                                                                                                                                         |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ANSI T1.105           | SONET - Basic description including Multiplex structure, rates and formats, 2001                                                                                    |  |

| ANSI T1.105.02        | I T1.105.02 Synchronous Optical Networks (SONET), Payload Mappings, 2001                                                                                            |  |

| ANSI T1.107           | Digital Hierarchy - Formats Specifications, 1995                                                                                                                    |  |

| ETSI EN 300-417 1-1   | Transmission and Multiplexing (TM) - Generic requirements of transport functionality of equipment - Generic processes and performance                               |  |

| ETSI EN 300-417 2-1   | Transmission and Multiplexing (TM) - Generic requirements of transport functionality of equipment - SDH and PDH physical section layer functions                    |  |

| ETSI EN 300-417 3-1   | Transmission and Multiplexing (TM) - Generic requirements of transport functionality of equipment - STM-N regenerator and multiplex section layer functions         |  |

| ETSI EN 300-417 4-1   | Transmission and Multiplexing (TM) - Generic requirements of transport functionality of equipment - SDH path layer functions                                        |  |

| ETSI EN 300-417 9-1   | Transmission and Multiplexing (TM) - Generic requirements of transport functionality of equipment - SDH concatenated path layer functions; Sub-part 1: Requirements |  |

| IEEE 1149.1           | Standard Test Access Port and Boundary Scan Architecture (May 21, 1990)                                                                                             |  |

| IEEE 1596.3           | Standard for Low-Voltage Differential Signals (LVDS) for Scalable Coherent Interface (SCI) (March 21, 1996)                                                         |  |

| ITU-T G.707/Y.1322    | Network Node interface for the Synchronous Digital Hierarchy (SDH) (10/2000)                                                                                        |  |

| ITU-T G.783           | Characteristics of Synchronous Digital Hierarchy (SDH) equipment functional blocks (10/2001)                                                                        |  |

| ITU-T G.803           | Architecture of transport networks based on the SDH (03/2000).                                                                                                      |  |

| ITU-T G.805           | Generic functional architecture of transport networks (03/2000)                                                                                                     |  |

| ITU-T G.806           | Characteristics of transport equipment - Description methodology and generic functionality (10/2000)                                                                |  |

| Telcordia GR-253-CORE | SONET Common Generic Criteria, Rev 3, September 2000                                                                                                                |  |

| Telcordia GR-499-CORE | Transport Systems Generic Requirements: Common Requirements, Issue 2, December 1998                                                                                 |  |

#### PHAST-12N TXC-06312

# OVERVIEW

The TranSwitch PHAST-12N is a highly integrated STM-4/OC-12 rate SDH/SONET overhead termination device designed for TDM payload mappings.

A single PHAST-12N can terminate four individual STM-1/OC-3 lines or a single STM-4/OC-12 line. It can perform clock synthesis and clock recovery for four 155.52 Mbit/s signals or a single 622.08 Mbit/s serial signal.

The PHAST-12N device provides RS/section and MS/line overhead processing, high order AU-3/AU-4/AU-4-Xc/STS-1/STS-3c/STC-6c/STS-9c/STS-12c pointer tracking and retiming, and high order VC-3/VC-4/VC-4-Xc/STS-1/STS-3c/STS-6c/STS-9c/STS-12c SPE path overhead processing and performance monitoring. It provides full non-blocking cross connecting at the high order path level allowing path loopbacks, line/MSP protection and UPSR and SNC/P path protection.

The PHAST-12N device supports the following APS architectures:

- 1. STM-4/OC-12 mode: 1+1 or 1:1 APS using two devices connected via the APS port

- 2. STM-1/OC-3 mode: 1+1, 1:1 or 1:n (n<=3) APS using a single device without APS port

- 3. STM-1/OC-3 mode: 1+1, 1:1 or 1:n (n<=7) APS using two devices connected via the APS port

The device operates from 1.8V and 3.3V power supplies.

Major interfaces include:

- 1. Serial LVPECL line interfaces: single STM-4/OC-12 or four STM-1/OC-3

- 2. 77.76 MHz telecom bus interface

- 3. 622.08 Mbit/s serial LVDS APS port interface

- 4. Line/MS Alarm/Ring port selectable per line interface

- 5. SOH/TOH byte interface

- 6. DCC interface

- 7. High Order Path Alarm/Ring port selectable per SDH/SONET path

- 8. High Order POH byte interface

- 9. Motorola/Intel style microprocessor interface for configuration, alarms and performance monitoring

- 10.JTAG interface to IEEE 1149.1

- 11. Various reference clocks, and lead programmed HW configuration controls

The PHAST-12N software driver has the same architecture as other TranSwitch device drivers and is meant to be easily integrated with them. The application software calls the driver functions to configure, control and manage the PHAST-12N device. The device driver insulates the application from the internal details of the device register usage and provides a higher level of abstraction.

TRA

PHAST-12N TXC-06312

**DATA SHEET**

The following is a list of features supported by the PHAST-12N:

#### MODES OF OPERATION

- Line interfaces:

- Four STM-1/OC-3 line interfaces, or

- One STM-4/OC-12 line interface<sup>1</sup>

- SDH/SONET mapping:

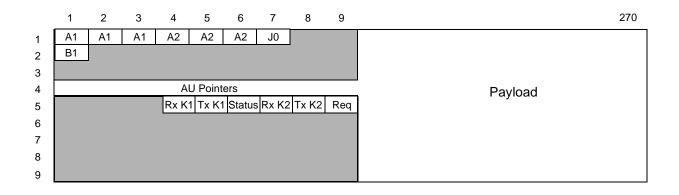

Figure 1. Supported SDH/SONET Mapping

#### LINE INTERFACE

- LVPECL serial line interfaces:

- Line Interface #1 can handle 155.52 Mbit/s (STM-1/OC-3 mode) or 622.08 Mbit/s (STM-4/OC-12 mode) signals

- Line Interfaces #2 to #4 handle 155.52 Mbit/s signals and are only used in STM-1/OC-3 mode

- Transmit clock synthesis

- Per line interface:

- Receive clock recovery

- Loss of Signal detection

- Receive 19.44 MHz (STM-1/OC-3 mode) or 77.76 MHz (STM-4/OC-12 mode) clock output reference

- General purpose input/output pins

<sup>1.</sup> The term STM-4c/OC-12c is sometimes used to denote a STM-4/OC-12 interface transporting a contiguous concatenated VC-4-4c/STS-12c SPE high order path. The STM-4/OC-12 mode of operation allows transport of any type of high order path container. ITU-T/ANSI compliant terminology will be used throughout this document.

PHAST-12N TXC-06312

#### **APS PORT INTERFACE**

- Single 622.08 Mbit/s LVDS serial interface:

- · Receive clock recovery

- Transmit clock synthesis

- Receive 77.76 MHz clock output reference

- Transport of high order path data for four STM-1/OC-3 signals or one STM-4/OC-12 signal between two PHAST-12N devices

- Transport of K1/K2 APS signal, signal fail and signal degrade indications for up to four lines between two PHAST-12N devices

- The APS port transports the payload and APS signaling between two mate devices. The APS finite state machine itself needs to be implemented by the external host software. The resulting bridge and switch requests are performed by configuring the cross-connect.

#### **RS/SECTION LAYER PROCESSING**

- A1/A2 frame alignment

- Out of frame and loss of frame detection

- J0 Trail Trace Identifier:

- Insertion and monitoring of single repeating byte and 16-byte trace messages

- Trace identifier mismatch detection

- Scrambling and descrambling

- B1 BIP-8 insertion and monitoring

- D1-D3 DCC accessible via the DCC port

- All received RSOH bytes are stored in on-chip memory and transmitted on the TOH port

- All RSOH bytes can be inserted from on-chip memory or from the TOH port

#### **MS/LINE LAYER PROCESSING**

- B2 BIP-24/96 insertion and monitoring

- Degraded signal and excessive bit error detection

- Block and bit error performance monitoring counters

- D4-D12 DCC can be accessible via the DCC port

- Insertion and monitoring of remote information (RDI, REI)

- Insertion and monitoring of MS/line AIS

- Insertion and monitoring of the K1/K2 APS signal

- Insertion and monitoring of the S1 synchronization status message (SSM)

- · All received MSOH bytes are stored in on-chip memory and transmitted on the TOH port

- All MSOH bytes can be inserted from on-chip memory or from the TOH port

#### HIGH ORDER PATH LAYER PROCESSING

- J1 Trail Trace Identifier:

- Insertion and monitoring of single repeating byte, 16-byte and 64-byte trace messages

- Trace identifier mismatch detection

| PHAST-12N |

|-----------|

| TXC-06312 |

- B3 BIP-8 insertion and monitoring

- · Degraded signal and excessive bit error detection

- Block and bit error performance monitoring counters

- C2 Trail Signal Label insertion and monitoring

- Unequipped, VC-AIS, payload mismatch detection

- G1 insertion and monitoring

- Single bit RDI and three bit E-RDI

- REI insertion and block/bit performance monitoring counter

- H4 insertion and monitoring

- Optionally insertion and monitoring of low order multiframe sequence

- Bypass mode

- K3 insertion and monitoring

- Automatic Protection Switching detection

- Unequipped and Supervisory Unequipped generation and detection

- Unidirectional mode

- Bypass mode

- · All received POH bytes are stored in on-chip memory and transmitted on the POH port

- All POH bytes can be inserted from on-chip memory except for B3, which is used as an errormask

#### HIGH ORDER PATH CROSS-CONNECT

- Non-blocking 36x36 cross-connect:

- 3 input and 3 output ports: line side, APS port and terminal side

- 12 time slot channels per port

- VC-3/STS-1 SPE granularity allowing cross connecting at VC-3/VC-4/VC-4-Xc/STS-1/STS-3c/STS-6c/STS-9c/STS-12c SPE level

- · Path loopbacks and multi-casts are supported

- Each individual output channel can be forced to source an AIS or unequipped maintenance signal

#### TELECOM BUS INTERFACE

- Independent ADD and DROP bus

- 8-bit wide data bus

- 77.76 MHz clock

- SPE indication

- J0/C1 and J1 indication

- Optional V1 indication

- ADD bus timing modes:

- ADD Slave mode: timing signals are inputs

- ADD Master mode: timing signals are outputs

PHAST-12N TXC-06312

#### MICROPROCESSOR INTERFACE

- Bidirectional 16-bit wide Data bus (allowing 16-bit word accesses only)

- 14-bit wide Address bus

- The following microprocessor interface modes are supported:

- Generic Motorola mode

- Generic Intel mode (with separate address/data bus)

- MPC860 mode,

- MPC8260 Local Bus mode

- Interrupt request lead

- Interrupt mask bits for controlling generation of hardware interrupt requests

#### TESTING

- Line loopbacks

- High order path loopbacks via the cross-connect

- Boundary scan

#### **DEVICE DRIVER**

- Device configuration

- Fault monitoring

- Performance monitoring

#### BLOCK DIAGRAM

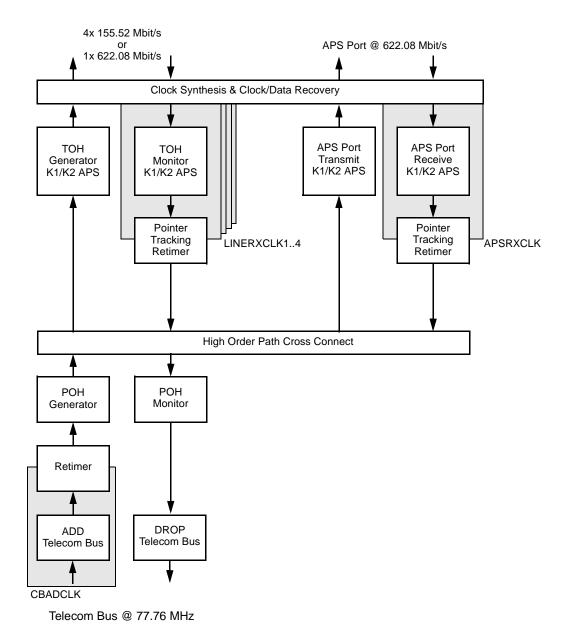

Telecom Bus @ 77.76 MHz

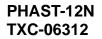

Figure 2. PHAST-12N TXC-06312 Block Diagram

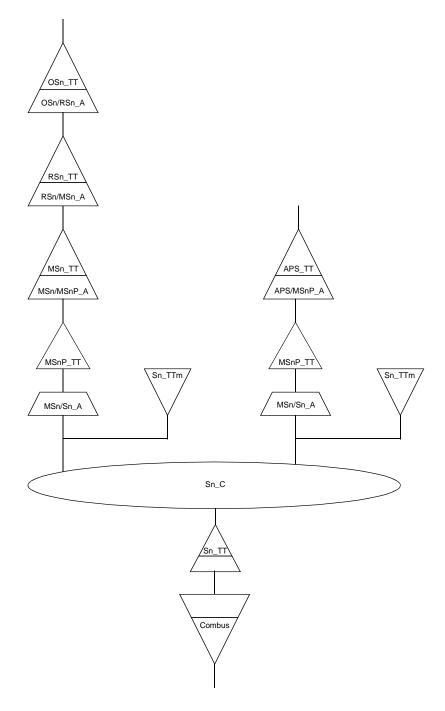

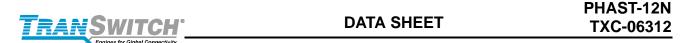

# FUNCTIONAL MODEL

#### Figure 3. PHAST-12N Functional Model

**DATA SHEET**

# **BLOCK DIAGRAM DESCRIPTION**

#### LINE SIDE

The PHAST-12N can terminate four individual STM-1/OC-3 lines or a single STM-4/OC-12 line. Each incoming line signal is monitored for loss of signal and clock and data recovery is performed. Reference clocks derived from each recovered clock are available.

The subsequent TOH Monitor will terminate all RS/section and MS/line overhead bytes compliant to the latest ITU/ETSI/ANSI standards. Additionally, the received raw TOH overhead bytes are stored in on-chip memory and output on the TOH port interface for external processing (except for BIP where the error mask is calculated). The received data communication channel bytes, selectable RS/section or MS/line, are output on a DCC port interface per line interface. The K1/K2 APS signal bytes are debounced and forwarded to the APS interface. RDI and REI are output on the external and internal line ring port interfaces for ring applications.

The PHAST-12N performs high order pointer processing on the H1/H2 bytes from the receive line interfaces. The high order path containers are retimed to the local System Clock.

High order POH monitoring is performed on all received high order path containers for SNC/P and UPSR applications.

In the transmit direction, the TOH Generator will insert all RS/section and MS/line overhead bytes. The TOH overhead bytes can be inserted from on-chip memory or the TOH port interface. Additionally the data communication channel bytes, selectable RS/section or MS/line, can be inserted from a DCC port interface. Remote information, RDI and REI can be inserted from the internal or external ring port interface. This selection can be made on a per line basis. The K1/K2 APS can be inserted from the APS port interface.

Finally four individual STM-1/OC-3 lines or a single STM-4/OC-12 line are transmitted using the device's System Clock.

#### **APS PORT SIDE**

The serial 622.08 Mbit/s APS port interface is monitored for loss of clock and data recovery is performed. A reference clock derived from the recovered clock is available.

The received APS port signal is monitored for signal quality and the APS information exchanged between two mate PHAST-12N devices, including K1/K2 APS signal, signal fail and signal degrade status, is stored for software access.

The PHAST-12N performs high order pointer processing on the H1/H2 bytes from the receive APS port. The high order path containers are retimed to the local System Clock.

High order POH monitoring is performed on all received high order path containers for SNC/P and UPSR applications.

In the transmit direction, the APS information exchanged between two mate PHAST-12N devices, including K1/K2 APS signal, signal fail and signal degrade status, is inserted either from on-chip memory or directly from the TOH monitor.

Finally, the serial 622.08 Mbit/s APS port signal is transmitted using the device's System Clock.

#### PHAST-12N TXC-06312

#### HIGH ORDER PATH CROSS CONNECT

The non-blocking high order path cross connect block can connect each output high order path time slot to each input high order path time slot. The presence of an active cross-connect does not 'block' a cross-connect to another output. AIS or unequipped maintenance signals can be inserted into each output time slot.

The cross connect has three input buses and three output buses: line side, APS port side and terminal side. Each bus contains the high order path containers equivalent to an STM-4/STS-12.

#### TERMINAL SIDE

The POH Monitor will terminate all path overhead bytes of the dropped high order path containers compliant to the latest ITU/ETSI/ANSI standards. Additionally, the received raw POH overhead bytes are stored in on-chip memory and output on the POH port interface for external processing (except for BIP where the error mask is calculated). The remote information, RDI and REI, is output on the external and internal path ring port interfaces for ring applications.

Finally, the high order path data is output on the Drop Telecom Bus interface.

In the transmit direction, the high order path data is input from the ADD telecom bus interface. The POH Generator will optionally insert all path overhead bytes. The POH overhead bytes can be inserted from on-chip memory or the POH port interface. The remote information, RDI and REI, can be inserted from the internal or external ring port interface. This selection can be made on a per high order path basis. PHAST-12N

TXC-06312

**DATA SHEET**

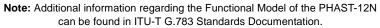

Note: This is the bottom view. The leads are solder balls. See Figure 52 for package information. This view is rotated relative to the bottom view in Figure 52. Some signal Symbols have been abbreviated to fit the space available. The Symbols are shown in full in the Lead Descriptions section.

22

Figure 4. PHAST-12N TXC-06312 376-Lead Plastic Ball Grid Array Package Lead Diagram

#### PHAST-12N TXC-06312

# LEAD DESCRIPTIONS

In the I/O/P column of the following tables, I = Input, O = Output, P = Power, T = Tristateable during normal operation. Entries in the Type column are defined in the Input, Output and Input/Output Parameters section.

All single-ended inputs (= LVTTL inputs) that are not used, must be connected to a low level.

Differential inputs (= LVPECL and LVDS inputs) that are not used can be left floating. They must be left in power-down mode, which is the default mode of these pads, after reset.

| Symbol        | Lead No.                                                                                                                                                                                                                                                  | I/O/P | Name/Function                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD18         | E7, E8, E11, E12, E15, E16, G5,<br>G18, H5, H18, L5, L18, M5,<br>M18, R5, R18, T5, T18, V7, V8,<br>V11, V12, V15, V16                                                                                                                                     | Ρ     | Digital Core 1.8V supply: +1.8V +/-5%                                                                                                                                                                                                                                                                                                                                |

| VDD33         | E6, E9, E10, E13, E14, E17, F5,<br>F18, J5, J18, K5, K18, N5, N18,<br>P5, P18, U5, U18, V6, V9, V10,<br>V13, V14, V17                                                                                                                                     | Р     | Digital I/O 3.3V supply: +3.3∨ +/-5%                                                                                                                                                                                                                                                                                                                                 |

| VDDA18LVDS    | AB7                                                                                                                                                                                                                                                       | Р     | LVDS analog 1.8V supply                                                                                                                                                                                                                                                                                                                                              |

| VDDA33LVPCDRV | AB11, W10                                                                                                                                                                                                                                                 | Р     | LVPECL driver analog 3.3V supply                                                                                                                                                                                                                                                                                                                                     |

| VDDA33LVPCIO  | AA17, W11                                                                                                                                                                                                                                                 | Р     | LVPECL pre-drive analog 3.3V supply                                                                                                                                                                                                                                                                                                                                  |

| VSSA18LVDS    | AA8                                                                                                                                                                                                                                                       | Р     | LVDS analog 1.8V return                                                                                                                                                                                                                                                                                                                                              |

| VSSA33LVPCPST | AA14, AA15                                                                                                                                                                                                                                                | Р     | LVPECL driver & pre-drive analog 3.3V returns                                                                                                                                                                                                                                                                                                                        |

| VSS           | A1, A22, AB1, AB22, D19, D4,<br>E18, E5, J10, J11, J12, J13, J14,<br>J9, K10, K11, K12, K13, K14,<br>K9, L10, L11, L12, L13, L14, L9,<br>M10, M11, M12, M13, M14, M9,<br>N10, N11, N12, N13, N14, N9,<br>P10, P11, P12, P13, P14, P9,<br>V18, V5, W19, W4 | Ρ     | Digital Core 1.8V & Digital I/O 3.3V returns                                                                                                                                                                                                                                                                                                                         |

| NC            | A10, A13, A15, A16, A18, A19,<br>A6, A7, A8, A9, AA9, B10, B13,<br>B14, B15, B17, B6, B7, B8, B9,<br>C10, C13, C14, C16, C7, C8,<br>C9, D10, D11, D12, D13, D3,<br>D8, D9, F19, Y20                                                                       |       | <b>No Connect:</b> These leads are not to be con-<br>nected, and must be left floating. Connection of<br>an NC lead may impair performance or cause<br>damage to the device. NC leads that are currently<br>unused may be assigned functions in a future ver-<br>sion of the device, affecting its usability in applica-<br>tions which have not left them floating. |

| Reserved_Low  | A11, A12, A14, A17, A20, A21,<br>B11, B12, B16, B18, B19, B20,<br>B22, C11, C12, C15, C17, C18,<br>C19, C20, C21, C22, D14, D15,<br>D16, D17, D18, D20, D21, D22,<br>E19, E20, E21, F20, G19                                                              |       | For Future Use: These leads are reserved for future use and should be tied to VSS.                                                                                                                                                                                                                                                                                   |

#### POWER SUPPLY, GROUND, AND NO CONNECT LEADS

#### CAUTION:

A number of Power, ground and No-connect leads have changed between Rev A and Rev B of the device. They are listed in the following two tables: first table applies to Rev A, second table to Rev B.

| PHAST-12N |

|-----------|

| TXC-06312 |

#### POWER SUPPLY, GROUND, AND NO CONNECT LEADS: REV A - DEVICE

| Symbol     | Lead No.  | I/O/P | Name/Function                                                                                                                                                                                                                                                                                                                                |

|------------|-----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDA18LVPC | AB13      | Р     | LVPECL analog 1.8V supply                                                                                                                                                                                                                                                                                                                    |

| VDDA33RPA  | AB15      | Р     | Rx PLL / Clock Recovery analog 3.3V supply                                                                                                                                                                                                                                                                                                   |

| VDDA33TPA  | Y9        | Р     | Tx PLL / Clock Synthesis analog 3.3V supply                                                                                                                                                                                                                                                                                                  |

| VSSA18LVPC | AB17      | Р     | LVPECL analog 1.8V return                                                                                                                                                                                                                                                                                                                    |

| VSSA33RPA  | AB16      | Р     | Rx PLL / Clock Recovery analog 3.3V return                                                                                                                                                                                                                                                                                                   |

| VSSA33TPA  | AB12      | Р     | Tx PLL / Clock Synthesis analog 3.3V return                                                                                                                                                                                                                                                                                                  |

| NC         | AA16, W16 |       | <b>No Connect:</b> These leads are not to be connected, and must be left floating. Connection of an NC lead may impair performance or cause damage to the device. NC leads that are currently unused may be assigned functions in a future version of the device, affecting its usability in applications which have not left them floating. |

### POWER SUPPLY, GROUND, AND NO CONNECT LEADS: REV B - DEVICE

| Symbol    | Lead No.   | I/O/P | Name/Function                                           |

|-----------|------------|-------|---------------------------------------------------------|

| VDDA18RPA | AB15, W16  | Р     | Rx PLL / Clock Recovery & Rx LVPECL analog 1.8V supply  |

| VDDA18TPA | AB13, Y9   | Р     | Tx PLL / Clock Synthesis & Tx LVPECL analog 1.8V supply |

| VSSA18RPA | AA16, AB16 | Р     | Rx PLL / Clock Recovery & Rx LVPECL analog 1.8V return  |

| VSSA18TPA | AB12, AB17 | Р     | Tx PLL / Clock Synthesis & Tx LVPECL analog 1.8V return |

#### REFERENCE VOLTAGES

| Symbol | Lead No. | I/O/P | Туре | Name/Function                                                                                                                 |

|--------|----------|-------|------|-------------------------------------------------------------------------------------------------------------------------------|

| VREF   | W12      |       |      | <b>1.2V Reference Voltage:</b> 1.2V reference voltage for all LVPECL and LVDS output drivers, and to bias the Rx and Tx PLLs. |

| VTERM  | AB10     |       |      | <b>1.2V Termination Voltage:</b> optional 1.2V termination voltage for the LVDS input buffer.                                 |

#### SDH/SONET RECEIVE LINE INTERFACE

| Symbol                       | Lead No.   | I/O/P | Туре | Name/Function                                                                                                                                                        |

|------------------------------|------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINERXDATA1P<br>LINERXDATA1N | Y14<br>W13 | I     |      | Serial SDH/SONET Receive Data #1: 622.08/155.52 Mbit/s<br>bit-serial data from electro/optical transceivers. Only<br>LINERXDATA1P/N can be used in STM-4/OC-12 mode. |

| LINERXDATA2P<br>LINERXDATA2N | Y15<br>W14 | I     |      | Serial SDH/SONET Receive Data #2: 155.52 Mbit/s bit-<br>serial data from electro/optical transceivers. Can not be used<br>in STM-4/OC-12 mode.                       |

| Symbol                       | Lead No.     | I/O/P | Туре          | Name/Function                                                                                                                                                                                    |

|------------------------------|--------------|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINERXDATA3P<br>LINERXDATA3N | W15<br>Y16   | Ι     | LVPECL        | Serial SDH/SONET Receive Data #3: 155.52 Mbit/s bit-<br>serial data from electro/optical transceivers. Can not be used<br>in STM-4/OC-12 mode.                                                   |

| LINERXDATA4P<br>LINERXDATA4N | AB18<br>AB19 | I     | LVPECL        | Serial SDH/SONET Receive Data #4: 155.52 Mbit/s bit-<br>serial data from electro/optical transceivers. Can not be used<br>in STM-4/OC-12 mode.                                                   |

| LINERXSIGDET1                | AA18         | Ι     | LVTTL         | <b>Signal Detect #1:</b> Signal from the optical receiver for line #1 indicating signal presence.                                                                                                |

| LINERXSIGDET2                | AB20         | I     | LVTTL         | <b>Signal Detect #2:</b> Signal from the optical receiver for line #2 indicating signal presence. Not used in STM-4/OC-12 mode.                                                                  |

| LINERXSIGDET3                | W17          | I     | LVTTL         | <b>Signal Detect #3:</b> Signal from the optical receiver for line #3 indicating signal presence. Not used in STM-4/OC-12 mode.                                                                  |

| LINERXSIGDET4                | Y18          | Ι     | LVTTL         | <b>Signal Detect #4:</b> Signal from the optical receiver for line #4 indicating signal presence. Not used in STM-4/OC-12 mode.                                                                  |

| LINERXCLK1                   | AA19         | 0     | LVCMOS<br>8mA | <b>Receive Divided Clock #1:</b> Clock output derived from the clock recovered from the serial data stream on LINERXDATA1P/N.<br>The clock rate is programmable to be either 19.44 or 77.76 MHz. |

| LINERXCLK2                   | AB21         | 0     | LVCMOS<br>8mA | <b>Receive Divided Clock #2:</b> Clock output derived from the clock recovered from the serial data stream on LINERXDATA2P/N.<br>The clock rate is fixed to 19.44 MHz.                           |

| LINERXCLK3                   | W18          | 0     | LVCMOS<br>8mA | <b>Receive Divided Clock #3:</b> Clock output derived from the clock recovered from the serial data stream on LINERXDATA3P/N.<br>The clock rate is fixed to 19.44 MHz.                           |

| LINERXCLK4                   | Y19          | 0     | LVCMOS<br>8mA | <b>Receive Divided Clock #4:</b> Clock output derived from the clock recovered from the serial data stream on LINERXDATA4P/N.<br>The clock rate is fixed to 19.44 MHz.                           |

| LINERXCAP                    | Y17          |       | Analog        | Capacitor for the Receive Line & APS Clock Recovery:<br>Optional external capacitor. Its value must be 25 100 nF<br>(Rev B) or larger than 1000 pF (Rev A).                                      |

#### SDH/SONET TRANSMIT LINE INTERFACE

| Symbol                       | Lead No.    | I/O/P | Туре   | Name/Function                                                                                                                                                    |

|------------------------------|-------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINETXDATA1P<br>LINETXDATA1N | AA10<br>Y10 | 0     |        | Serial SDH/SONET Transmit Data #1: 622.08/155.52<br>Mbit/s bit-serial data to electro/optical transceivers. Only<br>LINETXDATA1P/N is valid in STM-4/OC-12 mode. |

| LINETXDATA2P<br>LINETXDATA2N | AA11<br>Y11 | 0     | LVPECL | Serial SDH/SONET Transmit Data #2: 155.52 Mbit/s bit-<br>serial data to electro/optical transceivers. Not valid in<br>STM-4/OC-12 mode.                          |

**DATA SHEET**

| Symbol                       | Lead No.    | I/O/P | Туре          | Name/Function                                                                                                                                                        |

|------------------------------|-------------|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINETXDATA3P<br>LINETXDATA3N | Y12<br>AA12 | 0     | LVPECL        | Serial SDH/SONET Transmit Data #3: 155.52 Mbit/s bit-<br>serial data to electro/optical transceivers. Not valid in<br>STM-4/OC-12 mode.                              |

| LINETXDATA4P<br>LINETXDATA4N | Y13<br>AA13 | 0     | LVPECL        | <b>Serial SDH/SONET Transmit Data #4:</b> 155.52 Mbit/s bit-<br>serial data to electro/optical transceivers. Not valid in<br>STM-4/OC-12 mode.                       |

| LINETXCLK                    | Y7          | 0     | LVCMOS<br>8mA | <b>Transmit Divided Clock:</b> Clock output derived from the synthesized transmit lock.<br>The clock rate is programmable to be either 19.44 MHz or 77.76 MHz.       |

| LINETXCAP                    | AB14        |       | Analog        | Capacitor for the Transmit Line & APS Clock Synthe-<br>sizer: Optional external capacitor. Its value must be 25 nF<br>100 nF (Rev B) or larger than 1000 pF (Rev A). |

#### **RECEIVE APS PORT**

| Symbol                   | Lead No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                 |

|--------------------------|----------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APSRXDATAP<br>APSRXDATAN | W9<br>Y8 | I     | LVDS | Serial APS Port Receive Data: 622.08 Mbit/s bit-serial data from mate PHAST-12N.                                                                                                                              |

| APSRXCLK                 | AA6      | 0     |      | <b>Receive Divided APS Port Clock:</b> Clock output derived from the clock recovered from the serial APS port data stream on APSRXDATAP/N.<br>The clock rate is programmable to be either 19.44 or 77.76 MHz. |

#### TRANSMIT APS PORT

| Symbol     | Lead No. | I/O/P | Туре | Name/Function                                           |

|------------|----------|-------|------|---------------------------------------------------------|

| APSTXDATAP | AA7      | 0     | LVDS | Serial APS Port Transmit Data: 622.08 Mbit/s bit-serial |

| APSTXDATAN | AB6      |       |      | data to mate PHAST-12N.                                 |

#### **CLOCK/TIMING INTERFACE**

| Symbol                   | Lead No.   | I/O/P | Туре | Name/Function                                                                                                                                                                                                               |

|--------------------------|------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFTXCLK1                | AA20       | Ι     |      | <b>Transmit Reference Clock #1:</b> Reference clock for the transmit clock synthesizer.<br>The clock rate is programmable to be either 19.44 or 77.76 MHz.                                                                  |

| REFTXCLK2P<br>REFTXCLK2N | AB9<br>AB8 | I     |      | <b>Transmit Reference Clock #2:</b> Reference clock for the transmit clock synthesizer.<br>The clock rate is programmable to be 19.44, 77.76 or 155.52 MHz. A 622.08 MHz clock can be provided when the Tx PLL is bypassed. |

| Symbol       | Lead No. | I/O/P | Туре          | Name/Function                                                                                                                                                                                                                                                                                   |

|--------------|----------|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFRXCLK     | W8       | Ι     | LVTTL         | <b>Receive Reference Clock:</b> optional Reference clock for<br>the receive clock and data recovery units. This clock is<br>required for line/loop-time applications, when REFTXCLK1<br>and REFTXCLK2P/N are not present.<br>The clock rate is programmable to be either 19.44 or 77.76<br>MHz. |

| REFONESECCLK | R1       | I     | LVTTL         | <b>One Second Clock:</b> optional one second reference for performance monitoring counters.                                                                                                                                                                                                     |

| REFTXFS      | R2       | I     | LVTTL         | Transmit Reference Frame Sync: optional 8 kHz reference frame sync pulse.                                                                                                                                                                                                                       |

| REFSYSFS     | B21      | 0     | LVCMOS<br>8mA | System Reference Frame Sync: 8 kHz reference frame sync pulse.                                                                                                                                                                                                                                  |

| RESET        | A4       | I     | LVTTLp        | Hardware Reset (Active Low): The use of this lead at power-up is mandatory. Holding this lead low causes all the registers in the device to be reset.                                                                                                                                           |

# RECEIVE DCC INTERFACES

| Symbol     | Lead No. | I/O/P | Туре          | Name/Function                                                                                                                                                                                                                                                                    |

|------------|----------|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|