# 90-Mbps Single Chip Read Channel

# HITACHI

1st. Edition Sep. 1995

#### Description

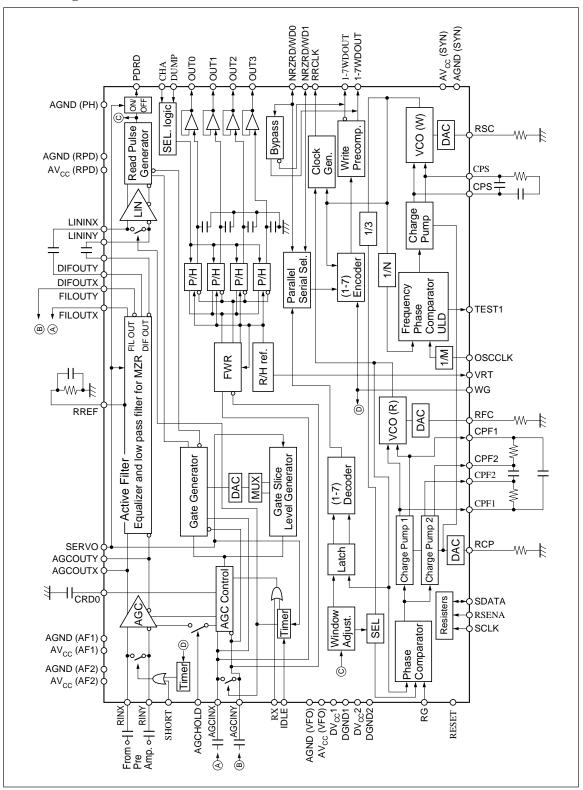

The HD153044TF is fully integrated single-chip Data Channel LSI for high performance magnetic disk drives. Function block include the automatic gain control (AGC) circuit, pulse detector, electric programmable filter, 4-burst servo demodulator, write clock synthesizer, data synchronizer, and 1,7RLL ENDEC with programmable write precompensation circuit. This LSI achieves from 32 Mbit/s to 90 Mbit/s data rate, supports both single and multiple zone recording.

The HD153044TF is fabricated in HITACHI 0.7  $\mu$ m Hi-Bi-CMOS process technology which achieves a high performance device with low power consumption. In powerdown mode, power consumption is 10 mW.

#### Features

#### General :

- 32 to 90 Mbit/s data transfer rate.

- A serial port for register access.

- User-selectable single zone recording or multiple zone recording options. The following are programmable for multiple zone recording : VCO center frequency, Read-PLL loop filter dumping factor, charge pump current levels (16 settings), active filter cut-off frequency for servo and data modes (128 settings).

- Power Management system (Servo = 400mW, Idle = 50mW, Sleep = 10mW)

- 2 bits parallel NRZ bus.

- Power consumption 680 mW typical.

- A single 5 V supply is required.

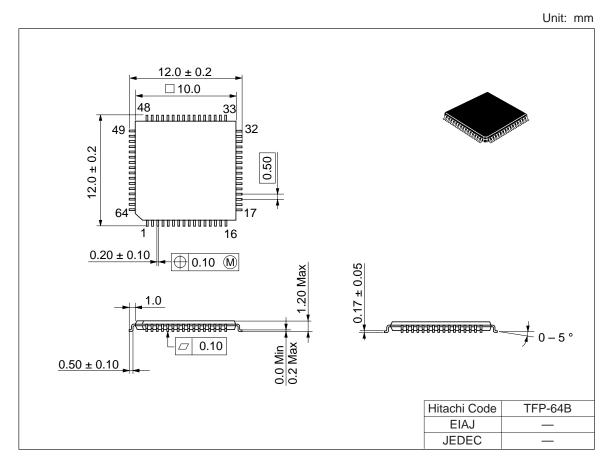

- This type 64 pin QFP package (1.2 mm height)

#### **Read Pulse Detector & Servo Functions :**

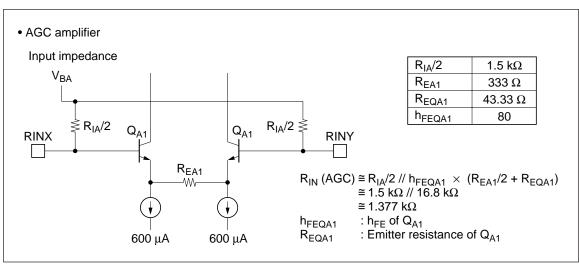

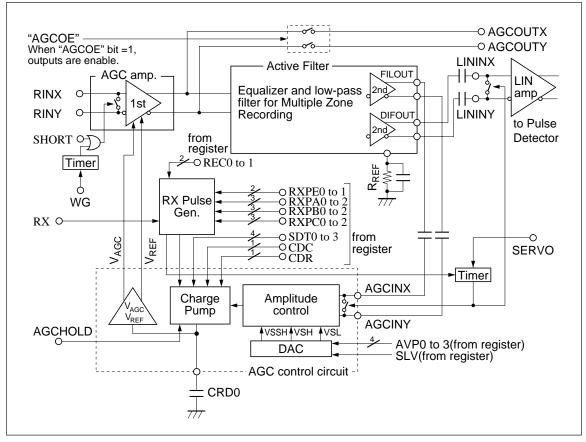

- Built-in AGC amplifier for stable operation in spite of varying media and head characteristics.

- AGC amplifier gain can be set to zero during writing.

- Fast AGC attack can be accomplished with RX function.

- AGC input's short time can be controlled by register. 0.25 ns typ. pulse pairing (sine wave input).

- 4-burst servo circuit (peak-hold) with buffer amp.

- Servo reference voltage output.

- Servo charge speed can be controlled by register.

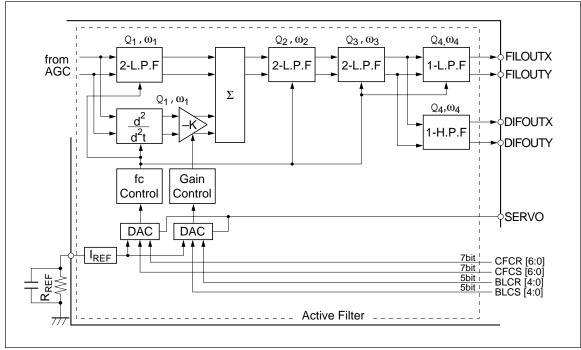

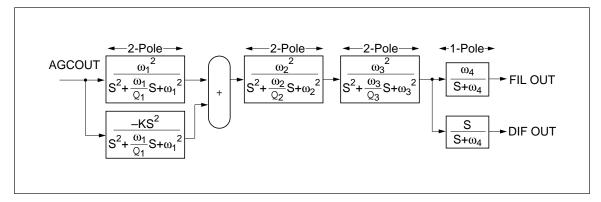

#### **Programmable Filter (AF) :**

- Programmable cut-off frequency of 6 to 33 MHz.

- Cutoff frequency and boost level can be setting independently each servo and data mode.

- 7th order equiripple filter.

- $\pm 10$  % fc accuracy.

- ±3 % group delay variation. (0.2 fc to fc)

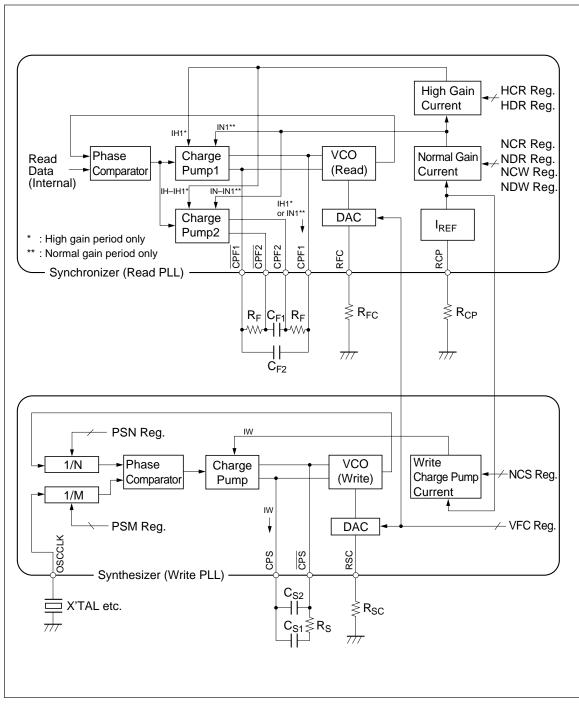

#### Write Clock Synthesizer :

- On-chip frequency synthesizer generates write clock.

- Independent M and N divide by registers.

- Unlock detect function.

- VCO center frequency matched to data synchronizer.

- VCO center frequency accuracy is less than  $\pm 5$  %.

#### Synchronizer :

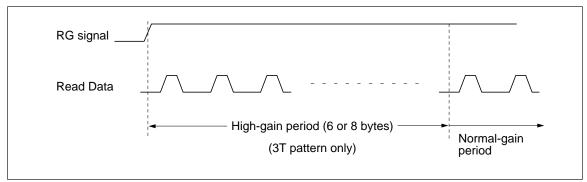

- High-speed acquisition can be accomplished with highly stable reproduction by switching between normal-gain and high-gain modes, and by switching loop filter constants.(6 bytes typ. acquisition time)

- Dual-mode phase detector compares both phase and frequency to ensure a wide capture range.

- VCO center frequency accuracy is less than  $\pm 5$  %.

#### **Data Separator :**

- Window center accuracy is 0 ± halfwindow × 27 % ns.

- Programmable window shift control. (1.5 %/step)

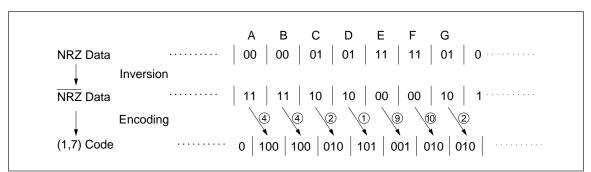

#### **Encoder/Decoder :**

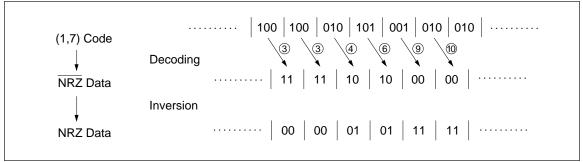

- IBM 1,7RLL code.

- 2 bits parallel NRZ bus.

- Bypass encoder function.

- 1,7 data to be written to disk can be programmed to be differential pseudo-ECL or TTL pair for high speed transfer without timing error.

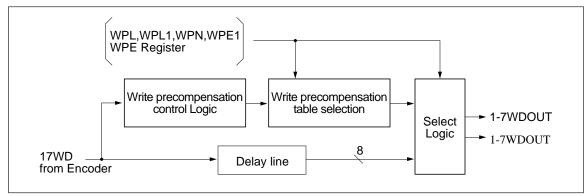

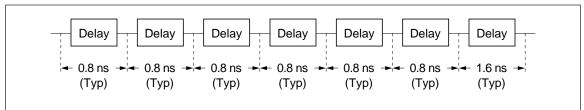

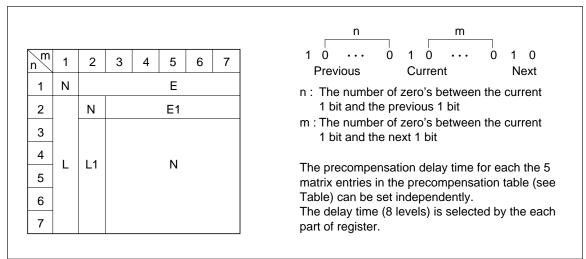

- On chip write precompensation function with programmable delay line.

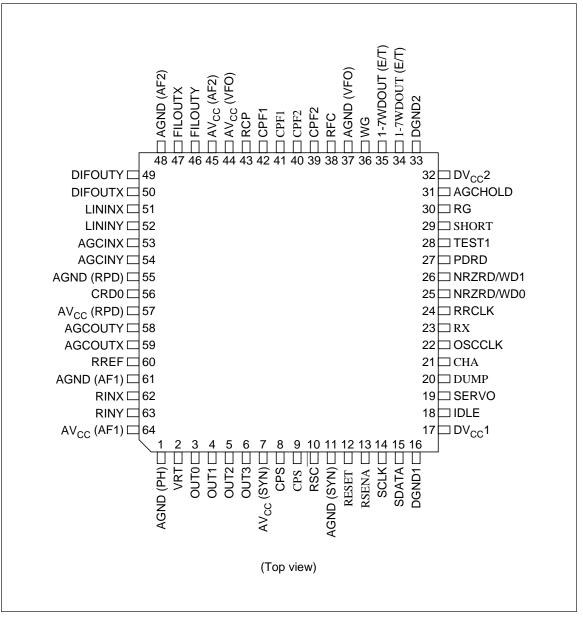

#### **Pin Arrangement**

#### **Pin Functions**

| Pin Name                        | Pin No.              | Туре                              | Function                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------|----------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RINX<br>RINY                    | 62<br>63             | Differential<br>input             | Differential input lines for the read signal from the recording medium.                                                                                                                                                                                                                                                                    |

| AGCOUTX<br>AGCOUTY              | 59<br>58             | Differential output               | Differential output lines for monitor from the AGC amplifier. The outputs are open-emitter type and would need external $3.9 \text{ k}\Omega$ pull down resistors.                                                                                                                                                                         |

| CRD0                            | 56                   | External component required       | The charge/discharge current output line for the AGC control circuit.                                                                                                                                                                                                                                                                      |

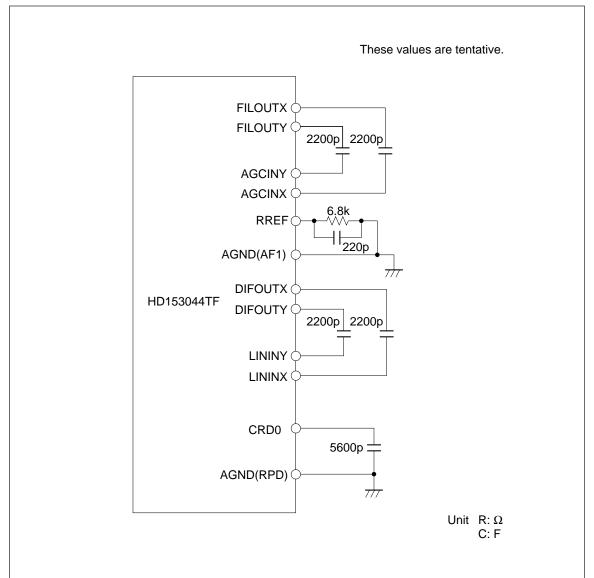

| FILOUTX<br>FILOUTY              | 47<br>46             | Differential output               | Differential output line from Active Filter. Connect to AGCINX, Y through bypass capacitors.                                                                                                                                                                                                                                               |

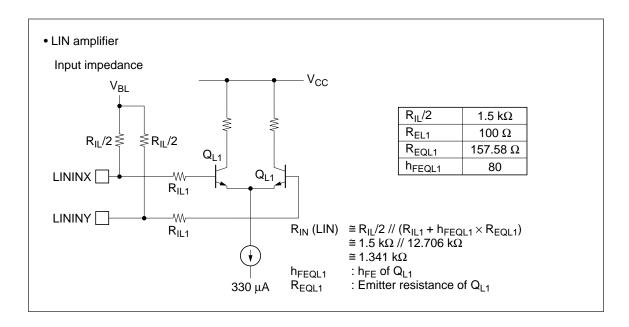

| DILOUTX<br>DILOUTY              | 50<br>49             | Differential output               | Differential output line from Active Filter. Connect to LININX, Y through bypass capacitors.                                                                                                                                                                                                                                               |

| AGCINX<br>AGCINY                | 53<br>54             | Differential input                | Differential input lines to the AGC output amplitude detector.<br>Connect to FILOUTX/Y outputs of the Active Filter with<br>bypass capacitors.                                                                                                                                                                                             |

| LININX<br>LININY                | 51<br>52             | Differential input                | Differential input lines for the zero-crossing comparator.<br>Normally connect to DIFOUTX/Y of the Active Filter with<br>bypass capacitors.                                                                                                                                                                                                |

| RREF                            | 60                   | External<br>component<br>required | Connect to a resistor to set the reference current for the Active Filter's DAC.                                                                                                                                                                                                                                                            |

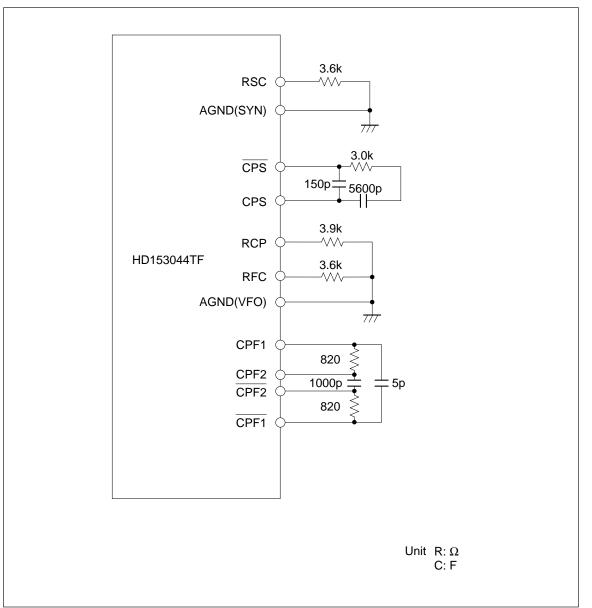

| CPF1<br>CPF1<br>CPF2<br>CPF2    | 42<br>41<br>39<br>40 | External<br>component<br>required | Current output to the external loop filter for read PLL.                                                                                                                                                                                                                                                                                   |

| RCP                             | 43                   | External<br>component<br>required | Connect to a resistor to set the charge pump output current<br>for the decode clock generator's VFO and write clock<br>synthesizer. The charge pump current level is set by HCR<br>[3:0], NCR[3:0], NCW[3:0] and NCS[3:0] registers.                                                                                                       |

| RFC                             | 38                   | External<br>component<br>required | Connect to a resistor to set the center frequency of the VCO in the decode clock generator's VFO. This pin must connect to 3.6 k $\Omega$ resistor.                                                                                                                                                                                        |

| RSC                             | 10                   | External<br>component<br>required | Connect to a resistor to set the center frequency of the VCO in the encode clock generator's frequency synthesizer. This pin must connect to $3.6 \text{ k}\Omega$ resistor.                                                                                                                                                               |

| CPS<br>CPS                      | 8<br>9               | External<br>component<br>required | Current output to an external loop filter for write clock synthesizer.                                                                                                                                                                                                                                                                     |

| OSCCLK<br>(Oscillator<br>clock) | 22                   | In (TTL)                          | Clock synthesizer's reference clock input. The frequency<br>synthesizer generates encode clock frequencies from the<br>input on this line. Data writing is synchronized with the<br>encode clock. When not reading data, the decode clock<br>generator's VFO is also synchronized to this frequency<br>(1.5 times the data transfer rate). |

## **Pin Functions** (cont)

| Pin Name                          | Pin No.       | Туре              | Function                                                                                                                                                                                                                                                                                                       |

|-----------------------------------|---------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST1<br>(ULD function<br>output) | 28            | Out (TTL)         | Error output from the encode clock generator's frequency<br>synthesizer. TEST1 goes low to indicate that the PLL in the<br>encode clock generator's frequency synthesizer has lost<br>lock. The disk controller should immediately half the write<br>operation. Data must be written again from the beginning. |

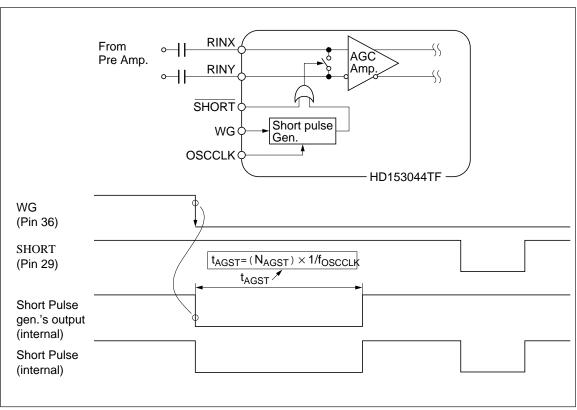

| SHORT                             | 29            | ln (TTL)          | When this terminal is "L", RINX and RINY are shorted together. This short timing can be generated both by the internal short pulse generate circuit or direct input by this pin.                                                                                                                               |

| RX                                | 23            | In (TTL)          | TTL-level input that switches the AGC loop on or off. When RX signal turn Low to High, AGC gain starts from maximum gain. HD153044TF has internal automatic RX pulse generate circuit.                                                                                                                         |

|                                   |               |                   | RX input AGC loop                                                                                                                                                                                                                                                                                              |

|                                   |               |                   | High AGC loop closed                                                                                                                                                                                                                                                                                           |

|                                   |               |                   | Low AGC loop open                                                                                                                                                                                                                                                                                              |

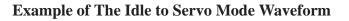

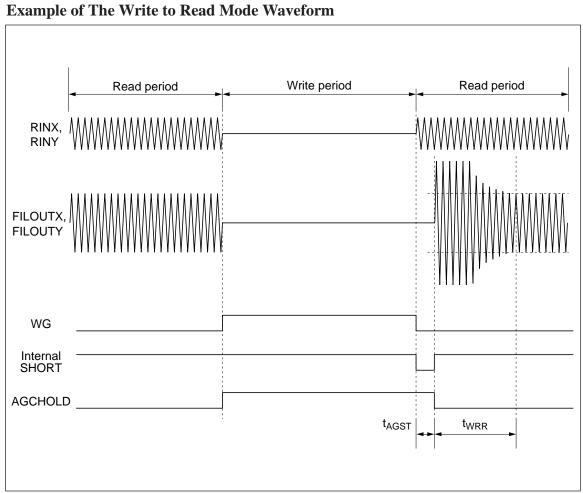

| AGCHOLD                           | 31            | In (TTL)          | TTL-level input that locks the AGC amplifier gain. When AGCHOLD goes High, the gain is locked at its immediately preceding value.                                                                                                                                                                              |

| SERVO                             | 19            | In (TTL)          | "H" : Servo mode, "L" : Read mode. In the servo mode,<br>"CFCS" register set the A/F's cut-off frequency and VGLS/<br>VGHS register set the gate slice level. In the read mode,<br>"CFCR" register set the A/F's cut-off frequency and VGLR/<br>VGHR register set the gate slice level.                        |

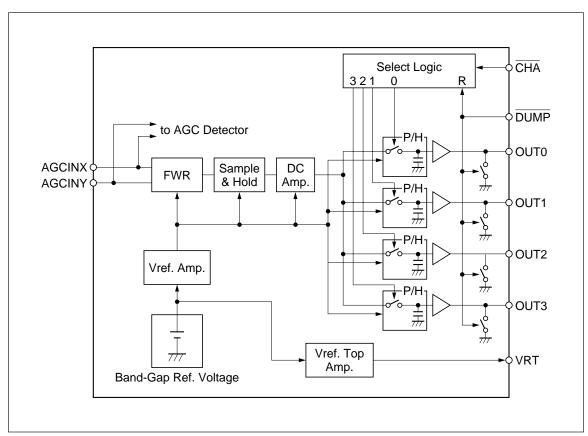

| OUT0, OUT1,<br>OUT2, OUT3         | 3, 4,<br>5, 6 | Analog<br>outputs | Servo burst's peak and hold outputs. Connect to A/D converter. Holding capacitors resides inside the chip with buffered outputs.                                                                                                                                                                               |

| VRT                               | 2             | Analog<br>outputs | Servo reference voltage output.                                                                                                                                                                                                                                                                                |

| CHA                               | 21            | In (TTL)          | Input pin of the sampling control signal for Servo Peak/Hold circuit (TTL level). Position signal is sampled by CHA = "L".                                                                                                                                                                                     |

| DUMP                              | 20            | In (TTL)          | Input pin of the discharge control signal of Servo Peak/Hold circuit (TTL level). DUMP = "L" is for discharge.                                                                                                                                                                                                 |

| PDRD                              | 27            | Out (TTL)         | Output line for the data read from disk as reshaped into digital data by the read pulse detector. When SERVO (pin19) goes high, PDRD outputs read data pulse. When SERVO goes low, PDRD is disable.                                                                                                            |

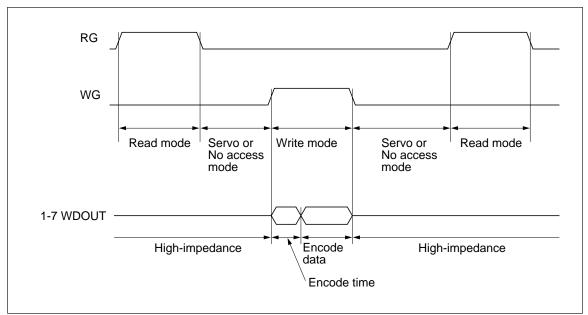

| WG                                | 36            | In (TTL)          | Write gate input signal. Set this pin high during writing.                                                                                                                                                                                                                                                     |

| RG<br>(Read Gate)                 | 30            | In (TTL)          | High level at this input selects read mode. This signal<br>switches the clock for counters and internal circuits, and<br>begins phase synchronization of the decode clock<br>generator's VFO with the 1-7 decode data.                                                                                         |

## Pin Functions (cont)

| Pin Name                                        | Pin No.  | Туре             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

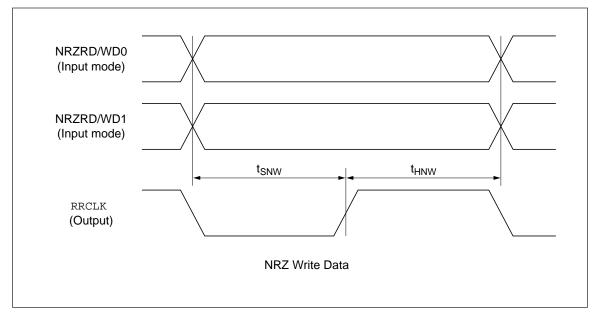

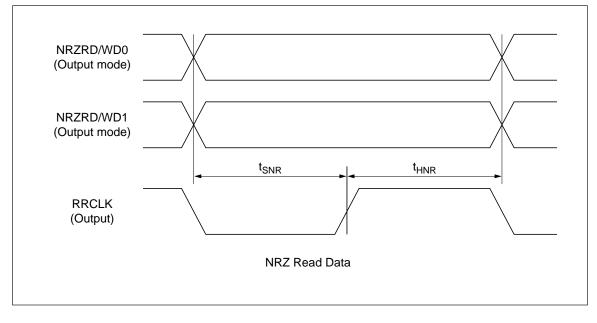

| NRZRD/WD1                                       | 26       | In/Out<br>(TTL)  | The parallel data I/O pin of NRZ signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NRZRD/WD0                                       | 25       | In/Out<br>(TTL)  | The parallel data I/O pin of NRZ signal. When the bypass encoder mode, provide the 1-7 write into this pin. Write data will be directory output from 1-7WDOUT and 1-7WDOUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RRCLK                                           | 24       | Out (TTL)        | Read reference clock output (TTL level). At read time, this<br>pin provides a clock which is synchronized with the<br>converted NRZRD signal. This controller should read<br>NRZRD by this clock. Other than read mode, reference<br>clock is provided to disk controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1-7WDOUT<br>1-7WDOUT<br>(Write data<br>outputs) | 35<br>34 | Out<br>(TTL/ECL) | 1-7 RLL Write Data Differential Output. Pseudo ECL/TTL are<br>available by bit 6 of register "\$h05". When this bit is "H",<br>these outputs are ECL. When this bit is "L", these outputs<br>are TTL. These pin provide the 1-7 write data that goes to<br>the Read/Write amplifier after the write pre-compensation.<br>When WG goes high, 1-7WDOUT and 1-7WDOUT pin are<br>output mode.                                                                                                                                                                                                                                                                                                                                                         |

| RESET                                           | 12       | In (TTL)         | Low input initializes internal logic circuits and registers.<br>When input low level, registers are initialized default value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

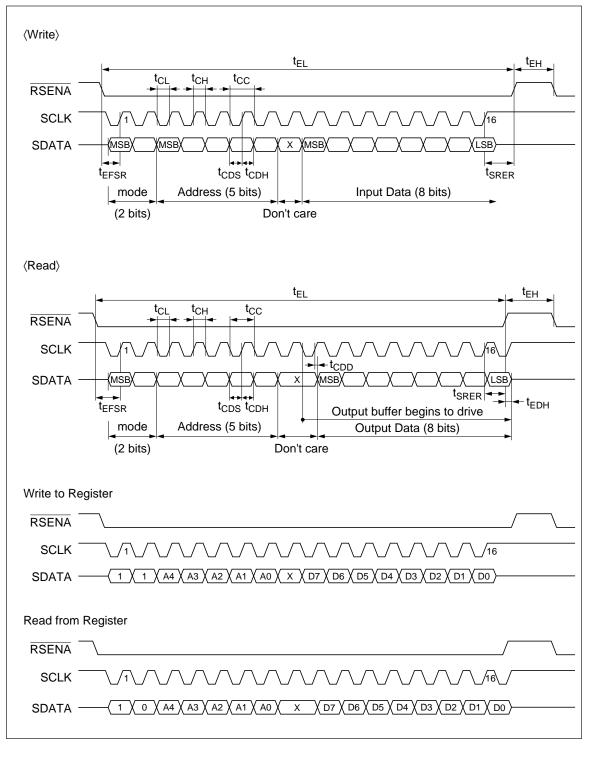

| RSENA                                           | 13       | In (TTL)         | This active low input selects the device and enables the serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SCLK                                            | 14       | In (TTL)         | This is the serial clock sent in by the hard disk controller or<br>other ASIC device. For either read or write transfer, a 16<br>clock burst is required for proper operation. Data is latched<br>in during write or sent out during read at the rising edge of<br>the SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SDATA                                           | 15       | In/Out<br>(TTL)  | Data is transmitted in 16-bit packet MSB first. The first 2 bits<br>is used to determine the read or write mode, the next 5 bits<br>are for the register address, followed by 1 "Don't Care" bit,<br>then the last 8 bits are for the Write or Read Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IDLE                                            | 18       | In (TTL)         | The input is used in combination with the two mode bits in<br>the PCNT register to reduce power consumption in the Idle<br>mode. When PCNT = 00, device is in the R/W normal mode,<br>all circuits are ON. When PCNT = 11, device is in the Sleep<br>mode, all circuits are OFF except the I/O and register. When<br>PCNT = 10, then depending on the logic level of the IDLE<br>pin; if it is High, then chip is in the Idle mode and all circuits<br>are OFF except for the I/O, register, and the bias circuits; if<br>it is low, then the device is in the Servo mode and the I/O,<br>logic, bias circuits, AGC, Active Filter, Read Pulse Detector,<br>and Servo circuit will be ON with only the RDVFO and the<br>WR synthesizer being OFF. |

## **Pin Functions** (cont)

| Pin Name                                         | Pin No.  | Туре   | Function                                                             |

|--------------------------------------------------|----------|--------|----------------------------------------------------------------------|

| DV <sub>CC</sub> 1<br>DV <sub>CC</sub> 2         | 17<br>32 | Power  | Digital V <sub>CC</sub> power supply.                                |

| DGND1<br>DGND2                                   | 16<br>33 | Ground | Digital ground.                                                      |

| AV <sub>CC</sub> (AF1)<br>AV <sub>CC</sub> (AF2) | 64<br>45 | Power  | Analog $V_{\mbox{\scriptsize CC}}$ power supplies for active filter. |

| AGND(AF1)<br>AGND(AF2)                           | 61<br>48 | Ground | Analog ground for active filter.                                     |

| AV <sub>CC</sub> (RPD)                           | 57       | Power  | Analog $V_{CC}$ power supply for read pulse detector.                |

| AGND(RPD)                                        | 55       | Ground | Analog ground for read pulse detector.                               |

| AGND(P/H)                                        | 1        | Ground | Analog ground for peak hold.                                         |

| AV <sub>CC</sub> (VFO)                           | 44       | Power  | Analog V <sub>CC</sub> power supply for synchronizer.                |

| AGND(VFO)                                        | 37       | Ground | Analog ground for synchronizer.                                      |

| AV <sub>CC</sub> (SYN)                           | 7        | Power  | Analog V <sub>CC</sub> power supply for synthesizer.                 |

| AGND(SYN)                                        | 11       | Ground | Analog ground for synthesizer.                                       |

## Registers

| Address | Name                                                             | Abbreviation    | Note                  |

|---------|------------------------------------------------------------------|-----------------|-----------------------|

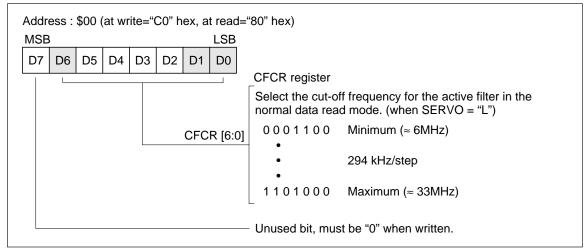

| 00h     | Low pass filter cut-off frequency control register (Read Mode)   | CFCR register   | fc = 6 to 33 MHz      |

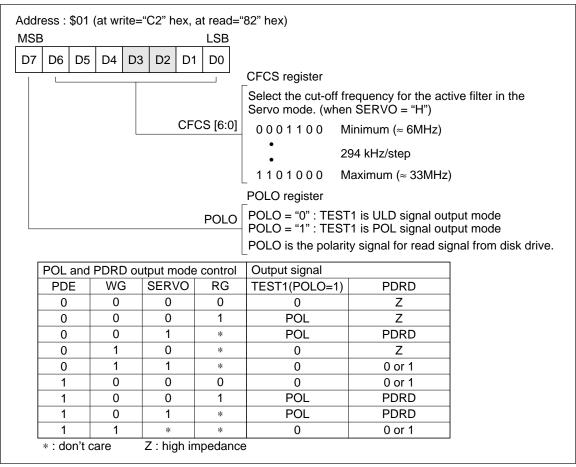

| 01h     | Low pass filter cut-off frequency control register (Servo Mode)  | CFCS register   | fc = 6 to 33 MHz      |

| 02h     | Reserve address                                                  |                 |                       |

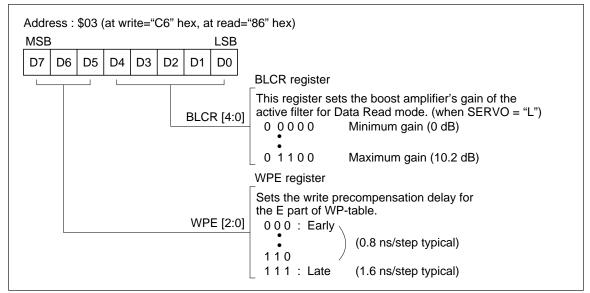

| 03h     | Low pass filter boost level control register (Read Mode)         | BLCR register   | 0 to 10 dB            |

|         | Write precompensation delay control register (Value E)           | WPE register    |                       |

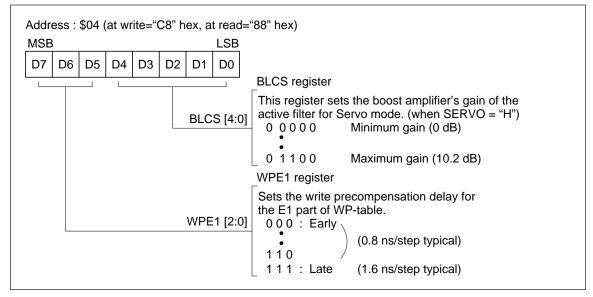

| 04h     | Low pass filter boost level control register (Servo Mode)        | BLCS register   | 0 to 10 dB            |

|         | Write precompensation delay control register (Value E1)          | WPE1 register   |                       |

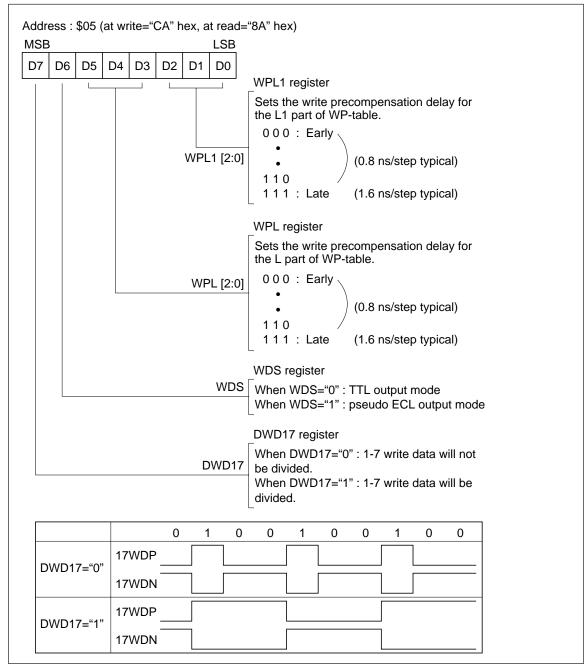

| 05h     | Write precompensation delay control register (Value L1)          | WPL1 register   |                       |

|         | Write precompensation delay control register (Value L)           | WPL register    |                       |

|         | 1-7 write data output type control register                      | WDS register    | Pseudo ECL or TTL     |

|         | 1-7 write data 1/2 divide mode select register                   | DWD17 register  |                       |

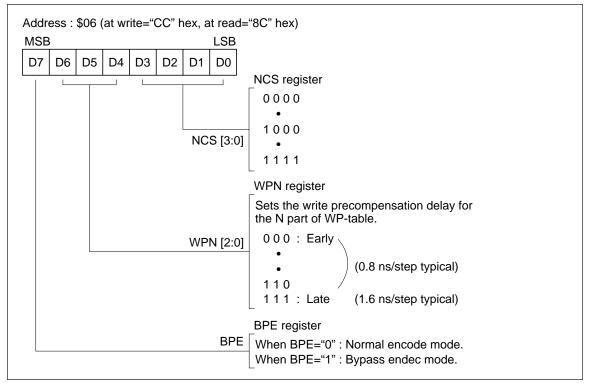

| 06h     | Write PLL charge pump gain control register                      | NCS register    |                       |

|         | Write precompensation delay control register (Value N)           | WPN register    |                       |

|         | Bypass encoder mode select register                              | BPE register    |                       |

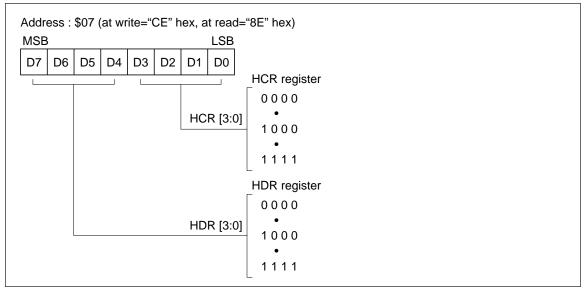

| 07h     | Read PLL (Synchronizer) charge pump gain control register        | HCR register    | High gain Mode        |

|         | Read PLL (Synchronizer) damping factor gain control register     | HDR register    | High gain Mode        |

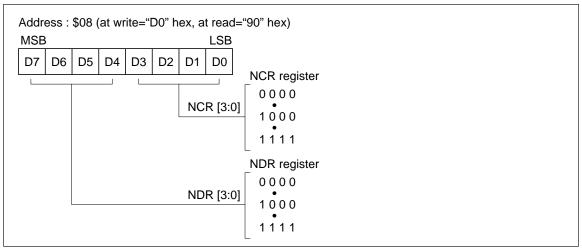

| 08h     | Read PLL (Synchronizer) charge pump gain control register        | NCR register    | Normal gain Mode      |

|         | Read PLL (Synchronizer) damping factor gain control register     | NDR register    | Normal gain Mode      |

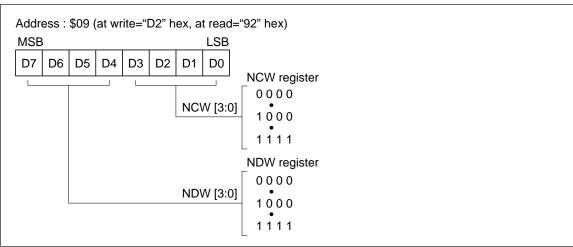

| 09h     | Read PLL (Synchronizer) charge pump gain control register        | NCW register    | Write clock Ref. Mode |

|         | Read PLL (Synchronizer) damping factor gain control register     | NDW register    | Write clock Ref. Mode |

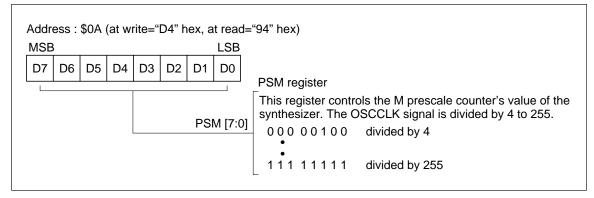

| 0Ah     | Pre-Scaler of write clock synthesizer control register (Value M) | PSM register    |                       |

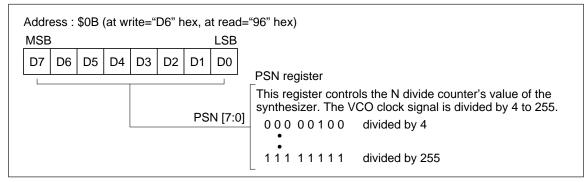

| 0Bh     | Pre-Scaler of write clock synthesizer control register (Value N) | PSN register    |                       |

| 0Ch     | VCO center frequency control register                            | VFC register    |                       |

|         | Unlock detect sensitivity control register                       | ULD register    |                       |

| 0Dh     | Envelope / DC level slice control register                       | EVSL register   |                       |

|         | Servo circuit's charge rate control register                     | PHG register    | ×1.0, ×1.5, ×2.5      |

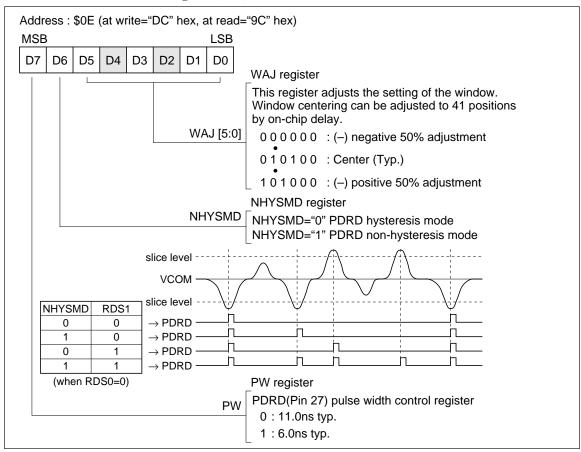

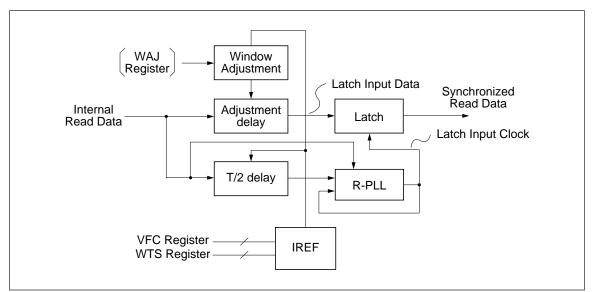

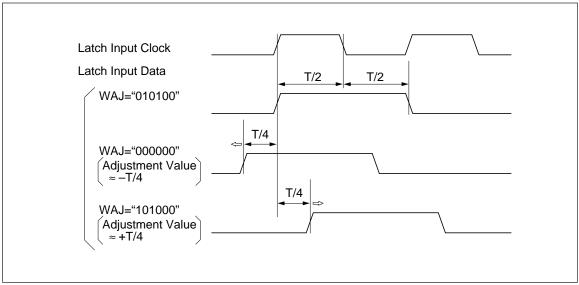

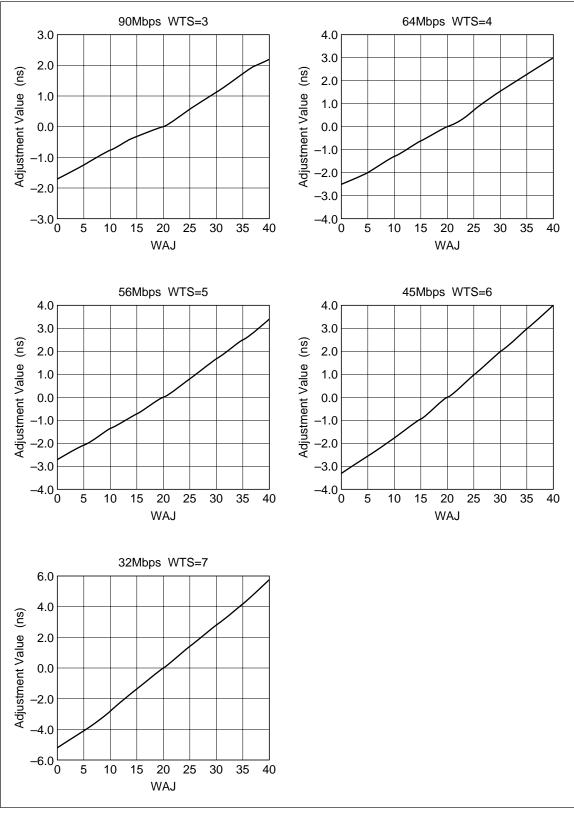

| 0Eh     | Decode window adjustment register                                | WAJ register    |                       |

|         | PDRD non-hysteresis mode control register                        | NHYSMD register |                       |

|         | PDRD pulse width control register                                | PW register     |                       |

| 0Fh     | Half window delay adjustment register                            | WTS register    |                       |

|         | ECL output buffer internal load connect control register         | ELS register    |                       |

|         | PDRD polarity control register                                   | RDS0 register   |                       |

|         | PDRD composite / non-composite control register                  | RDS1 register   |                       |

| Address | Name                                               | Abbreviation Note       |

|---------|----------------------------------------------------|-------------------------|

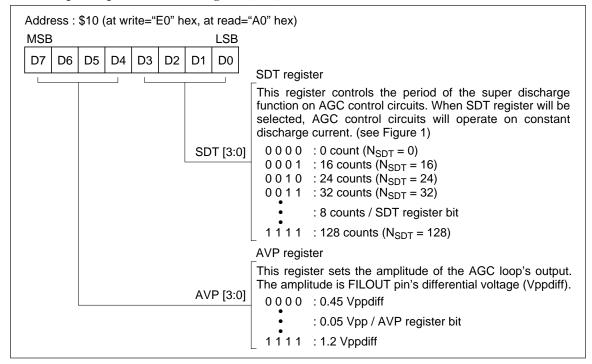

| 10h     | AGC loop amplitude setting register                | AVP register            |

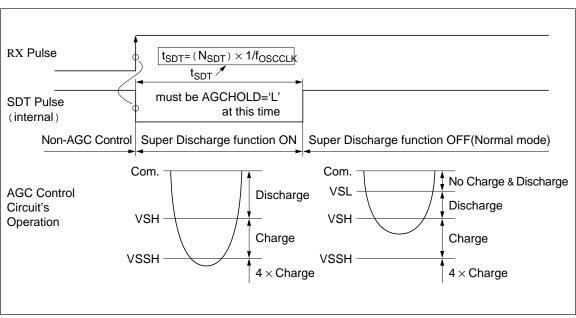

|         | AGC super discharge time control register          | SDT register            |

| 11h     | AGC amp. short timing control register             | AGST register           |

|         | AGC output enable register                         | AGCOE register          |

|         | PDRD enable register                               | PDE register            |

| 12h     | Internal RX pulse gen. enable register             | RXPE register           |

|         | Internal RX pulse width control register           | RXPA register           |

|         | AGC Det. charge discharge ratio setting register   | CDR register            |

|         | AGC Det. charge discharge current control register | CDC register            |

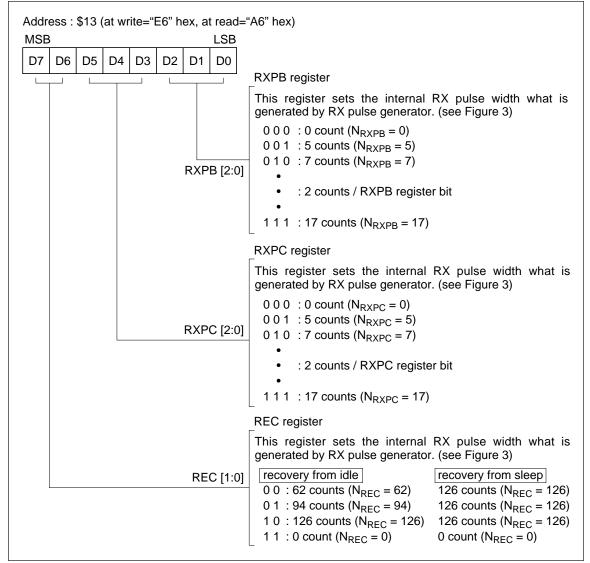

| 13h     | Internal RX pulse width control register           | RXPB register           |

|         | Internal RX pulse width control register           | RXPC register           |

|         | Recovery register                                  | REC register            |

| 14h     | Gate slice level setting register (Read Mode)      | VGLR / VGHR<br>register |

| 15h     | Gate slice level setting register (Servo Mode)     | VGLS / VGHS<br>register |

| 16h     | Negate counter setting register                    | RGN register            |

|         | Sync. byte counter setting register                | SYC register            |

|         | Power management control register                  | PCNT register           |

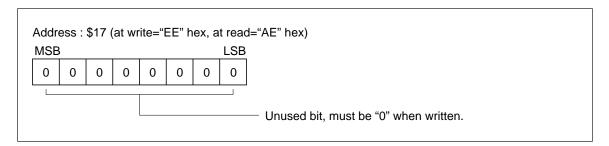

| 17h     | Reserve address                                    |                         |

| 18h     | AGC low slice level (VSL) ratio control register   | SLV register            |

## Registers (cont)

## **Mode Control Register Map**

| Address<br>Functions        | BIT7          | BIT6               | BIT5         | BIT4            | BIT 3                      | BIT2          | BIT1               | BIT0          | Resister                                                    |

|-----------------------------|---------------|--------------------|--------------|-----------------|----------------------------|---------------|--------------------|---------------|-------------------------------------------------------------|

| 0 0 0 0 0<br>filter         | " 0"          | CFCR6 <sup>3</sup> | *CFCR5       | CFCR4<br>cut-   |                            | CFCR2         | CFCR1 <sup>*</sup> | *CFCR0*<br>fo | CFCR: Active<br>frequency<br>rread mode                     |

| 0 0 0 0 1<br>filter         | POLO          | CFCS6              | CFCS5        | CFCS4<br>cut-   | CFCS3 <sup>*</sup><br>of f | *CFCS2        | *CFCS1             |               | CFCS: Active<br>frequency<br>rservo mode<br>Polarity signal |

| output control              |               |                    |              |                 |                            |               |                    |               |                                                             |

| 00010                       | " 0"          | " 0"               | " 0"         | " 0"            | " 0"                       | " 0"          | " 0"               | " 0" Re       | eserve address                                              |

| 00011<br>filter             | WPE2          | WPE1               | WPE0<br>Iow  | BLCR4           | BLCR3                      |               | BLCR1<br>ass       |               | BLCR: Active<br>boost<br>vel for read mode<br>rite precomp. |

| delay (E)                   | 14/554.0      |                    |              | <b>D</b> 1 00 ( | <b>DI 000</b>              | <b>DI 000</b> | <b>D</b> 1 00 (    | <b>DI 000</b> |                                                             |

| 0 0 1 0 0<br>filter         | WPE12         |                    | WPE10<br>low | BLCS4           | BLCS3                      |               | BLCS1<br>ass       |               | BLCS: Active<br>boost<br>vel for servo                      |

| mode                        |               |                    |              |                 |                            |               |                    | WPE1:         | Write precomp.                                              |

| delay (E1)                  |               |                    |              |                 |                            |               |                    |               |                                                             |

| 0 0 1 0 1<br>precomp. delay | DWD17<br>(L1) | WDS                | WPL2         | WPL1            | WPL0                       | WPL12         | WPL11              | -             | WPL1: Write                                                 |

| delay (L)                   |               |                    |              |                 |                            |               |                    |               |                                                             |

| sel.                        |               |                    |              |                 |                            |               |                    | WDS: 17       | WD PECL/ TTL                                                |

| mode sel.                   |               |                    |              |                 |                            |               |                    | DWD17:        | 17WD divide                                                 |

| 00110<br>synthesizer's      | BPE<br>s      | WPN2               | WPN1         | WPN0            | NCS3                       | NCS2          | NCS1               | NCS0 NO       | char ge                                                     |

| delay (N)                   |               |                    |              |                 |                            |               |                    |               | imp current<br>rite precomp.                                |

|                             |               |                    |              |                 |                            |               |                    | BPE: By       | pass encoder sel.                                           |

| 0 0 1 1 1<br>gain           | HDR3          | HDR2               | HDR1         |                 | HCR3<br>arge               | HCR2          | HCR1               | HCR0 HC       | CR: High<br>pump<br>urrent for read                         |

| mode                        |               |                    |              |                 |                            |               |                    |               |                                                             |

| d                           | а             |                    | m            |                 | р                          |               | i                  |               | gh gain PLL's<br>n g<br>actor for read                      |

| mode                        |               |                    |              |                 |                            |               |                    | 10            |                                                             |

| 0 1 0 0 0<br>gain           | NDR3          | NDR2               | NDR1         | NDR0<br>ch      | NCR3<br>arge               | NCR2          | NCR1               | NCR0 NO       | pump                                                        |

| mode                        |               |                    |              |                 |                            |               |                    | cl            | urrent for read                                             |

| d                           | а             |                    | m            |                 | р                          |               | i                  | NDR: No       | ormal gain PLL's<br>n g                                     |

| 10                          |               |                    |              | нп              | асн                        |               |                    |               |                                                             |

-

factor for read

| mode                         |               |               |       |      |               |        |                   |                                                    |

|------------------------------|---------------|---------------|-------|------|---------------|--------|-------------------|----------------------------------------------------|

| 0 1 0 0 1<br>gain            | NDW3          | NDW2          | NDW1  | -    | NCW3<br>narge | NCW2   | NCW1              | NCW0 NCW: Normal<br>pump<br>current for Ref.       |

| mode                         |               |               |       |      |               |        |                   |                                                    |

| -1                           | _             |               |       |      |               |        |                   | NDW: Normal gain PLL's                             |

| d                            | а             |               | m     |      | р             |        | i                 | n g<br>factor for Ref. mode                        |

| 0 1 0 1 0<br>clock           | PSM7          | PSM6          | PSM5  | PSM4 | PSM3          | PSM2   | PSM1              | PSM0 PSM: Write<br>synthesizer's<br>M divide value |

| 0 1 0 1 1<br>clock           | PSN7          | PSN6          | PSN5  | PSN4 | PSN3          | PSN2   | PSN1              | PSN0PSN: Write<br>synthesizer's<br>Ndividevalue    |

| 0 1 1 0 0<br>PLL             | ULD1          | ULD0          | VFC5* | VFC4 | VFC3          | VFC2   | VFC1              | VFC0 VFC: Read and write<br>center                 |

| sensitivity                  |               |               |       |      |               |        |                   | frequency<br>ULD:Unlock detector                   |

| 0 1 1 0 1<br>sampling gain d | EVSL          | " 0"          | " 0"  | " 0" | " 0"          | " 0"   | PHG1              | PHG0 PHG: P / H                                    |

| level                        |               |               |       |      |               |        |                   | EVSL: Envelope / DC slice                          |

|                              |               |               |       |      |               |        |                   | cont r ol                                          |

| 0 1 1 1 0<br>Decode window   | PW<br>adjustr | NHYSN<br>nent | 1D    | WAJ5 | WAJ4'         | * WAJ3 | WAJ2 <sup>3</sup> | *WAJ1 WAJ0 WAJ:                                    |

|                              |               |               |       |      |               |        |                   | NHYSMD: PDRD non                                   |

| hysteresis mode              | •             |               |       |      |               |        |                   | PW: PDRD pulse width                               |

Note: \* These bits are set "1" when register will be reseted.

#### **Register Descriptions**

#### Read Mode AF Cut-Off Frequency Register (CFCR)

#### Servo Mode AF Cut-Off Frequency Register (CFCS)

| Addre | ss : | \$02 ( | (at wr | ite="( | C4" h | ex, a | t read | ="84" hex)                                                |

|-------|------|--------|--------|--------|-------|-------|--------|-----------------------------------------------------------|

| MSB   |      |        |        |        |       |       | LSB    |                                                           |

| D7    | D6   | D5     | D4     | D3     | D2    | D1    | D0     |                                                           |

|       |      |        |        |        |       |       |        |                                                           |

|       |      |        |        |        |       |       |        | <ul> <li>Unused bit, must be "0" when written.</li> </ul> |

#### Read Mode AF Boost Level Control Register (BLCR) Write Precompensation Delay Control Register (WPE)

Servo Mode AF Boost Level Control Register (BLCS) Write Precompensation Delay Control Register (WPE1)

Write Precompensation Delay Control Register (WPL1) Write Precompensation Delay Control Register (WPL) 1-7Write Data Output Type Select Register (WDS) 1-7Write Data Divide Mode Select Register (DWD17)

Write Synthesizer's Charge Pump Output Current Control Register (NCS) Write Precompensation Delay Control Register (WPN) Bypass Encoder Mode Select Register (BPE)

#### Read PLL's Charge Pump Output Current Control Register for High Gain Mode (HCR) Read PLL's Damping Factor Control Register for High Gain Mode (HDR)

Read PLL's Charge Pump Output Current Control Register for Normal Gain Mode (NCR) Read PLL's Damping Factor Control Register for Normal Gain Mode (NDR)

Read PLL's Charge Pump Output Current Control Register for Write Clock Reference Mode (NCW) Read PLL's Damping Factor Control Register for Write Clock Reference Mode (NDW)

#### Prescaler of the Synthesizer Control Register (PSM) [M value]

#### Prescaler of the Synthesizer Control Register (PSN) [N value]

#### VCO Center Frequency Control Register (VFC) Unlock Detector Sensitivity Control Register (ULD)

| Addre<br>MSB |    | \$0C | (at w | rite=" | D8" h | iex, a | it read<br>LSB | ="98" hex)                                                                                                                                                                                                                                          |

|--------------|----|------|-------|--------|-------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7           | D6 | D5   | D4    | D3     | D2    | D1     |                |                                                                                                                                                                                                                                                     |

|              |    | -    |       | _      |       |        |                | _VFC register                                                                                                                                                                                                                                       |

|              |    |      |       |        |       |        |                | This register is used in multiple-zone recording to set the center frequency of the decode clock generator's VCO and the oscillation frequency of the decode clock generator's frequency synthesizer. Bit D5 is set "1" when reset pin is asserted. |

|              |    |      |       |        |       | VF     | C [5:0         | Resistors connected to the RFC and RSC lines set these values for the maximum data transfer rate. The VFC register decrease these values in step of 1.59%, permitting 42 settings down to a minimum transfer rate 0.35 times of the maximum rate.   |

|              |    |      |       |        |       |        |                | 010110 Minimum transfer rate                                                                                                                                                                                                                        |

|              |    |      |       |        |       |        |                | 111111 Maximum transfer rate                                                                                                                                                                                                                        |

|              |    |      |       |        |       |        |                | _ULD register                                                                                                                                                                                                                                       |

|              |    |      |       |        |       |        |                | Select the unlocked detect gain for the synthesizer to activate the TEST1 output when unlock condition occurs.                                                                                                                                      |

|              |    |      |       |        |       | UL     | D [1:0         | 0 0 : 2 OSCCLK<br>0 1 : 4 OSCCLK<br>1 0 : 6 OSCCLK<br>1 1 : 8 OSCCLK                                                                                                                                                                                |

|    |        |        |       |     |       | -     |        |        |                                                                                                            |

|----|--------|--------|-------|-----|-------|-------|--------|--------|------------------------------------------------------------------------------------------------------------|

| Ac | ldress | : \$0E | ) (at | wri | ite=" | DA" l | nex, a | at rea | d="9A" hex)                                                                                                |

| M  | SB     |        |       |     |       |       |        | LSB    |                                                                                                            |

|    | o   0  | 0      | 0     | )   | 0     | 0     | D1     | D0     |                                                                                                            |

|    |        |        |       |     |       |       |        |        | _PHG register                                                                                              |

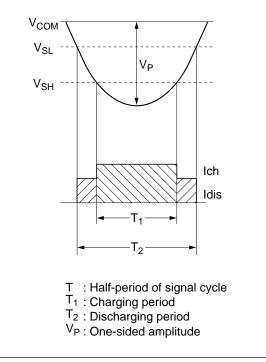

|    |        |        |       |     |       |       |        |        | This register controls the charge rate of the peak and hold circuit in the servo circuit.                  |

|    |        |        |       |     |       |       | PH     | G [1:0 | 0 0 ×2.5 charge rate (0.8µs at Typ. condition)<br>0 1 ×1.5 charge rate (1.5µs at Typ. condition)           |

|    |        |        |       |     |       |       |        | -      | <sup>1</sup> 0 1 ×1.5 charge rate (1.5μs at Typ. condition) 1 0 ×1.0 charge rate (2.0μs at Typ. condition) |

|    |        |        | Į     |     |       |       |        |        | <ul> <li>Unused bits, must be "0" when written.</li> </ul>                                                 |

|    |        |        |       |     |       |       |        |        | EVSL register                                                                                              |

|    |        |        |       |     |       |       |        |        | EVSL="0" : DC slice level setting mode for gate slice level. (read and servo mode)                         |

|    |        |        |       |     |       |       |        | EVS    | (read mode)<br>DC slice level mode for gate slice level.                                                   |

|    |        |        |       |     |       |       |        |        | _ (servo mode)                                                                                             |

Servo Circuits Control Register (PHG), Envelope Control Register (EVSL)

#### Decode Window Adjustment Register (WAJ), PDRD Non-Hysteresis Mode Control Register (NHYSMD) PDRD Pulse Width Control Register (PW)

Half Window Delay Adjustment Register (WTS), ECL Output Buffer Internal Load Connect Control Register (ELS) PDRD Signal Polarity Select Register (RDS0), PDRD Composite Polarity Register (RDS1)

| MSB        |          | LSB       |                                                                                                                                        |

|------------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| D7 D6 D5 D | D4 D3 D2 | D1 D0     | WTS register                                                                                                                           |

|            |          |           | This register selects the step's value of the half<br>window delay. Normally this register will be set<br>according to the following.  |

|            |          |           | Data Rate WTS Register N <sub>WTS</sub>                                                                                                |

|            |          | WTS [4:0] | 90 to 75 Mbps 0 0 0 1 1 3                                                                                                              |

|            |          |           | 75 to 60 Mbps 0 0 1 0 0 4                                                                                                              |

|            |          |           | 60 to 50 Mbps 0 0 1 0 1 5                                                                                                              |

|            |          |           | 50 to 42 Mbps 0 0 1 1 0 6                                                                                                              |

|            |          |           | 42 to 32 Mbps 0 0 1 1 1 7                                                                                                              |

|            |          |           | ELS register<br>When 1-7WDOUT, 1-7WDOUT are ECL output mode                                                                            |

|            |          | ELS       | (when WDS="1"), the following is valid.                                                                                                |

|            |          |           | "0": ECL output buffer internal load non-connect mode<br>"1": ECL output buffer internal load connect mode<br>(pull-down current 10mA) |

|            |          |           | RDS register                                                                                                                           |

|            |          | RDS [1:0] | RDS0 selects PDRD signal polarity<br>"0" : Signal value "1" = "H" (active high)<br>"1" : Signal value "1" = "L" (active low)           |

|            |          |           | RDS1 composite polarity signal<br>"0" : Non-composite (one side polarity output)                                                       |

|            |          |           | "1" : Composite (both polarity output)                                                                                                 |

#### AGC Super Discharge Time Control Register (SDT) AGC Loop's Amplitude Control Register (AVP)

#### AGC Amp. Short Time Control Register (AGST), AGCOUT Enable Register (AGCOE) PDRD Output Enable Control Bit (PDE)

| Addre<br>MSB<br>D7 |       | \$11 (<br>D5 | at wr<br>D4 | rite="l | E2" h<br>D2 | ex, a<br>D1      | t read:<br>LSB<br>D0 | ="A2" hex)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|-------|--------------|-------------|---------|-------------|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |       |              |             |         |             |                  |                      | _AGST register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |       |              |             |         |             | AGS <sup>-</sup> | r [5:0]              | This register controls the internal short timing generator.<br>The input stage of the AGC amp.(RINX/Y) will be shorted<br>when this register will be selected. The shorted period will<br>be according to this register's value. When the NAGST =<br>0, internal short timer is disenable and only SHORT (Pin<br>29) is valid. SHORT pin and internal short gen. are<br>connected OR logic.<br>$0000001 : 0 \text{ count } (N_{AGST} = 0)$<br>$000001 : 3 \text{ counts } (N_{AGST} = 3)$<br>$000010 : 4 \text{ counts } (N_{AGST} = 34)$ |

|                    |       |              |             |         |             |                  |                      | 1 1 1 1 1 1 : 65 counts (N <sub>AGST</sub> = 65)<br>(see Figure 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    |       |              |             |         |             |                  |                      | AGCOE register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | AGCOE |              |             |         |             |                  |                      | AGCOE = "0" AGCOUTX/Y (Pin 59, 58) are disenable<br>AGCOE = "1" AGCOUTX/Y (Pin 59, 58) are enable                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    |       |              |             |         |             |                  | PDE                  | PDE register<br>— When this bit sets "1", PDRD output is enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

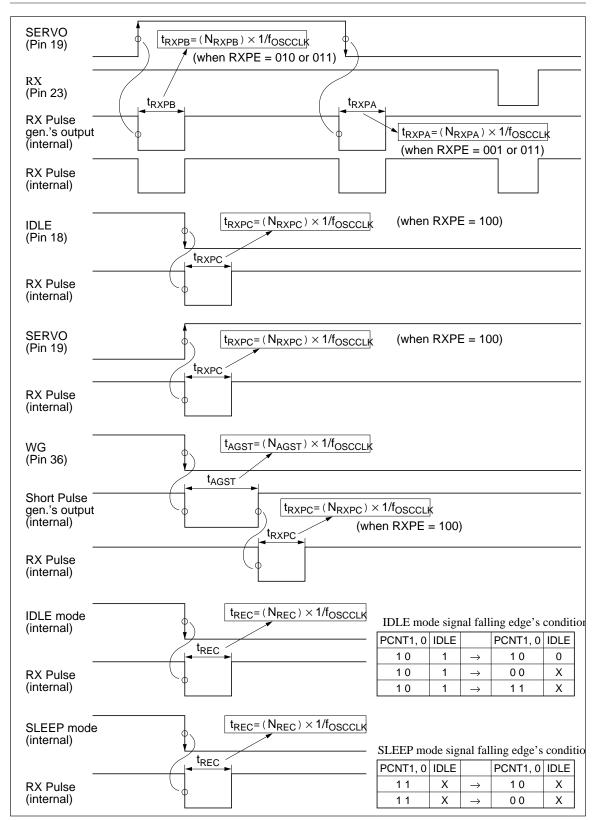

Internal RX Pulse Ganerator Enable Register (RXPE), Internal RX Pulse Width Control Register A (RXPA) AGC Control Circuit's Charge & Discharge Current Ratio Setting Register (CDR) AGC Control Circuit's Charge & Discharge Current Setting Register (CDC)

| Add | ress | s : \$12 | (at v | vrite=" | E4" | nex, a | t read= | "A4" hex) |                                                                                                                                                                                |

|-----|------|----------|-------|---------|-----|--------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MS  | B    |          |       |         |     |        | LSB     |           |                                                                                                                                                                                |

| D7  | D    | 6 D5     | D4    | D3      | D2  | D1     | D0      |           |                                                                                                                                                                                |

|     |      |          |       |         |     | I      |         | _RXPE re  | gister                                                                                                                                                                         |

|     |      |          |       |         |     |        |         |           | ster controls the internal RX pulse generator. RX pin and internal RX pulse gen. are connected OR                                                                              |

|     |      |          |       |         |     |        |         | 000       | : External RX pin mode.                                                                                                                                                        |

|     |      |          |       |         |     |        |         | 001       | : Internal RX pulse generate mode. RX pulse is<br>generated from falling edge of SERVO (Pin 19)<br>signal. Pulse width is determined RXPA register.                            |

|     |      |          |       |         |     | RXP    | E [2:0] | 010       | : Internal RX pulse generate mode. RX pulse is<br>generated from rising edge of SERVO (Pin 19)<br>signal. Pulse width is determined RXPB register.                             |

|     |      |          |       |         |     |        | - [2.0] | 011       | : Internal RX pulse generate mode. RX pulse is<br>generated from both rising & falling edge of<br>SERVO (Pin 19) signal. Pulse width are<br>determined RXPA and RXPB register. |

|     |      |          |       |         |     |        |         | 100       | : Internal RX pulse generate mode. Pulse width is determined RXPC register. (see Figure 3)                                                                                     |

|     |      |          |       |         |     |        |         | _RXPA re  | gister                                                                                                                                                                         |

|     |      |          |       |         |     |        |         |           | ister sets the internal RX pulse width what is d by RX pulse generator.                                                                                                        |

|     |      |          |       |         |     |        |         | 000       | : 0 count ( $N_{RXPA} = 0$ )                                                                                                                                                   |

|     |      |          |       |         |     | RXP    | A [2:0] | 001       | $: 5 \text{ counts } (N_{RXPA} = 5)$                                                                                                                                           |

|     |      |          | L     |         |     |        |         | •         | : 7 counts ( $N_{RXPA} = 7$ )                                                                                                                                                  |

|     |      |          |       |         |     |        |         | •         | : 2 counts / RXPA register bit                                                                                                                                                 |

|     |      |          |       |         |     |        |         | 111       | : 17 counts (N <sub>RXPA</sub> = 17)<br>(see Figure 3)                                                                                                                         |

|     |      |          |       |         |     |        |         | CDR reg   | ster                                                                                                                                                                           |

|     |      |          |       |         |     |        | CDR     | Г         | arge : Discharge = 5 : 1                                                                                                                                                       |

|     |      |          |       |         |     |        |         |           | arge : Discharge = 20 : 1                                                                                                                                                      |

|     |      |          |       |         |     |        |         | CDC reg   | ister                                                                                                                                                                          |

|     |      |          |       |         |     |        | CDC     |           | arge current is 500μA                                                                                                                                                          |

|     |      |          |       |         |     |        |         | _"1": Cha | arge current is 250µA                                                                                                                                                          |

|     |      |          |       |         |     |        |         |           |                                                                                                                                                                                |

#### Low Gate Slice Level Register for Read Mode (VGLR) High Gate Slice Level Register for Read Mode (VGHR)

| MSB |    |    |    |    |    |     | LSB     |                                                                                                                                                                        |

|-----|----|----|----|----|----|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | D6 | D5 | D4 | D3 | D2 | D1  | D0      |                                                                                                                                                                        |

|     |    |    |    |    |    |     |         | _VGLR register                                                                                                                                                         |

|     |    |    |    |    |    | VGL | R [3:0] | These are input to the internal DAC using VCOM a reference source to generate the low-slice level for the pulse detection circuit in the read mode. (when SERVO = "L") |

|     |    |    |    |    |    |     |         | EVSL="1" EVSL="0"                                                                                                                                                      |

|     |    |    |    |    |    |     |         | 0000 Minimum low-slice level 8% of V-peak 0.04V                                                                                                                        |

|     |    |    |    |    |    |     |         | 1111 Maximum low-slice level 71% of V-peak 0.36V                                                                                                                       |

|     |    |    |    |    |    |     |         | VGHR register                                                                                                                                                          |

|     |    |    |    |    |    | VGH | R [3:0] | These are input to the internal DAC using VCOM a reference source to generate the high-slice level for th pulse detection circuit in the read mode. (when SERVO "L")   |

|     | L  |    |    |    |    |     |         | EVSL="1" EVSL="0                                                                                                                                                       |

|     |    |    |    |    |    |     |         | 0000 Minimum high-slice level 29% of V-peak 0.15V                                                                                                                      |

|     |    |    |    |    |    |     |         |                                                                                                                                                                        |

#### Low Gate Slice Level Register for Servo Mode (VGLS) High Gate Slice Level Register for Servo Mode (VGHS)

| Addr | ess : | \$15 ( | at wr | ite=" | EA" h | nex, a | t read= | "AA" hex)                                                                                                                                                                 |  |  |

|------|-------|--------|-------|-------|-------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MSE  |       |        |       |       |       |        | LSB     |                                                                                                                                                                           |  |  |

| D7   | D6    | D5     | D4    | D3    | D2    | D1     | D0      | VGLS register                                                                                                                                                             |  |  |

|      |       |        | ]     |       |       | VGL    | S [3:0] | These are input to the internal DAC using VCOM as reference source to generate the low-slice level for the pulse detection circuit in the servo mode. (when SERVO = "H")  |  |  |

|      |       |        |       |       |       |        |         | 0 0 0 0 Minimum low-slice level 0.04V<br>1 1 1 1 Maximum low-slice level 0.36V                                                                                            |  |  |

|      |       |        |       |       |       |        |         | VGHS register                                                                                                                                                             |  |  |

|      |       |        |       |       |       |        |         | These are input to the internal DAC using VCOM as reference source to generate the high-slice level for the pulse detection circuit in the servo mode. (when SERVO = "H") |  |  |

|      |       |        |       |       |       |        |         | 0 0 0 0 Minimum high-slice level 0.15V                                                                                                                                    |  |  |

|      |       |        |       |       |       |        |         | •<br>1111 Maximum high-slice level 0.46V                                                                                                                                  |  |  |

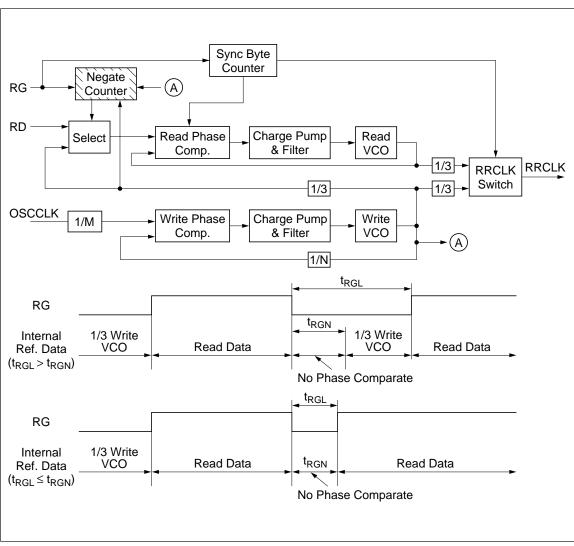

Negate Counter Setting Register (RGN), Sync. Control Register (SYC), Power Control Register (PCNT)

| D7       D6       D5       D4       D3       D2       D1       D0         RGN       RGN       register       This register sets the negoon read phase comparate t <sub>RGN</sub> , refference data of reswitched from read data to 0000 : 12 W-VCO cou 0001 : 24 W-VCO cou 0011 : 24 W-VCO cou 0011 : 48 W-VCO cou 0011 : 48 W-VCO cou 0011 : 48 W-VCO cou 0100 : 60 W-VCO cou 0101 : 120 W-VCO cou 0100 : 60 W-VCO cou 0100 : 60 W-VCO cou 0101 : 120 W-VCO cou 0100 : 60 W-VCO cou 0101 : 120 W-VCO cou 00 : 11111          SYC [1:0]       RGN [3:0]       PCNT register         Mode       PCNT [1:0]       PCNT register         PCNT [1:0]       PCNT register         0 0 : Normal mode. All circ       10 : Power save mode. In which of the two por 10LE = 1 then idle m will be powered dow the bias circuitries. If be selected and all b clock sythesizer (WR PLL).         11 : Sleep mode. Everyth I/O and the logic sect       YO and the logic sect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         |                   |         |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------|---------|----------|