# VERY FAST CMOS 8K x 8 CACHE TAGRAM

- 8K x 8 CMOS SRAM with ON BOARD COMPARATOR

- ADDRESS to COMPARE ACCESS TIME: 15, 17, 20, 25ns

- FAST CHIP SELECT COMPARE ACCESS: 8ns

- MATCH OUTPUT with FAST TAG DATA to COMPARE ACCESS of: 12, 15ns Max

- STATIC OPERATION-NO CLOCKS or TIMING STROBES REQUIRED

- FULL CMOS for LOW POWER OPERATION.

- TOTEM-POLE MATCH OUTPUT

- THREE-STATE OUTPUTS

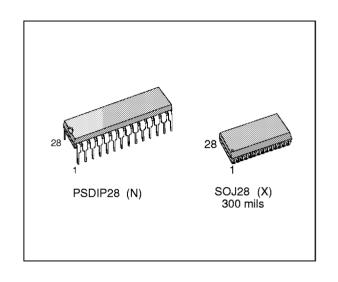

- 28 PIN 300 MIL DIP & 28 PIN 300 MIL SOJ

- HIGH SPEED ASYNCHRONOUS RAM CLEAR

### TRUTH TABLE

| $\overline{\mathbf{w}}$ | S | G | RS | Mode        | DQ               | Match |

|-------------------------|---|---|----|-------------|------------------|-------|

| Х                       | Х | Х | L  | Reset Clear | High-Z           | High  |

| Х                       | Ι | Х | Τ  | Deselect    | High-Z           | High  |

| Н                       | Ш | Η | Τ  | Miss        | D <sub>IN</sub>  | Low   |

| Н                       | L | Η | Ι  | Match       | D <sub>IN</sub>  | High  |

| Н                       | L | L | Τ  | Read        | Q <sub>OUT</sub> | High  |

| L                       | L | Х | Ι  | Write       | D <sub>IN</sub>  | High  |

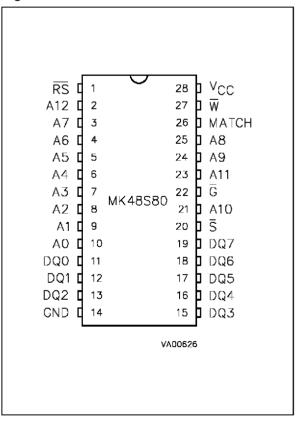

### **PIN NAMES**

| A0 - A12              | Address Inputs        |

|-----------------------|-----------------------|

| DQ0 - DQ7             | Data Inputs / Outputs |

| MATCH                 | Comparator Output     |

| s                     | Chip Select           |

| G                     | Output Enable         |

| $\overline{w}$        | Write Enable          |

| RS                    | Reset Flash Clear     |

| V <sub>CC</sub> , GND | 5 Volts, Ground       |

Figure 1. Pin Connection

July 1994 1/14

### **DESCRIPTION**

The MK48S80 is a 65,536 fast static cache TAGRAM™ organized as 8K x 8 bits. It is fabricated using SGS-THOMSON's low power, high performance HCMOS4 technology. The MK48S80 features fully static operation requiring no external clocks or timing strobes. The device requires a single 5V supply and is fully TLL compatible. The MK48S80 has a fast Chip Select control for high speed operation to the Match Compare valid, and device select/deselect operations. Additionally, the MK48S80 provides a Reset Clear, and MATCH compare pin. The Reset Clear input provides an asynchronous RAM clear control which clears all internal RAM bits to zero. The MATCH output is in a totem-pole configuration to minimize swtiching delays associated with open-drain devices. During a MATCH compare cycle, an on-board 8-bit comparator compares the Data Inputs (8-bit TAG) at the specified address index (A0-A12) to the internal RAM data. If a miss condition exists, where at least one bit of TAG data does not match the internal RAM, then the MATCH output issues a LOW miss signal.

# OPERATIONS READ MODE

The MK48S80 is in the read mode whenever Write Enable ( $\overline{W}$ ) is HIGH with Output Enable ( $\overline{G}$ ) LOW, and Chip Select ( $\overline{S}$ ) is active. This provides access to data from eight of 65,536 locations in the static memory array. The unique address specified by the 13 Address Inputs defines which one of the 8192 8-bit bytes is to be accessed. Valid data will be available at the eight Output pins within tavqv after the last stable address, providing  $\overline{G}$  is LOW, and  $\overline{S}$  is LOW. If Chip Enable or Output Enable access times are not met, data access will be measured from the limiting parameter (tslqv or tglqv) rather than the addresses. The state of the DQ pins is controlled by the  $\overline{S}$ ,  $\overline{G}$ , and  $\overline{W}$  control signals. Data out may be indeterminate at tslqx and tglqx, but data line will always be valid at tavqv.

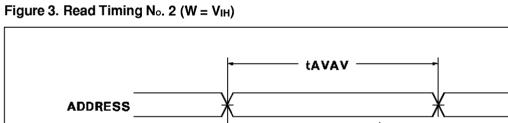

# READ CYCLE TIMING - Electrical Characteristics and Recommended AC Operating Conditions (0 °C $\leq$ TA $\leq$ +70 °C; V<sub>CC</sub> = 5V $\pm$ 5%)

| Sym               | ıbol             | Parameter                          | 1    | 5    | 1    | 7    | 2    | 0    | 2    | 5    | Unit | Note |

|-------------------|------------------|------------------------------------|------|------|------|------|------|------|------|------|------|------|

| Std               | Alt              | i arameter                         | Min. | Max. | Min. | Мах. | Min. | Max. | Min. | Max. | Onne |      |

| t <sub>AVAV</sub> | t <sub>RC</sub>  | Read Cycle Time                    | 20   |      | 20   |      | 20   |      | 25   |      | ns   |      |

| tavqv             | taa              | Address Access Time                |      | 20   |      | 20   |      | 20   | 25   |      | ns   | 1    |

| t <sub>SLQV</sub> | t <sub>CSA</sub> | Chip Select Access Time            |      | 15   |      | 15   |      | 15   |      | 15   | ns   |      |

| t <sub>GLQV</sub> | t <sub>OEA</sub> | Output Enable Access Time          |      | 10   |      | 10   |      | 10   |      | 15   | ns   | 1    |

| t <sub>SLQX</sub> | t <sub>CSL</sub> | Chip Select to Output Low-Z        | 0    |      | 0    |      | 0    |      | 0    |      | ns   |      |

| t <sub>GLQX</sub> | toel             | Output Enable to Low-Z             | 0    |      | 0    |      | 0    |      | 0    |      | ns   |      |

| tsHQZ             | tcsz             | Chip Select to High-Z              |      | 9    |      | 9    |      | 9    |      | 9    | ns   |      |

| t <sub>GHQZ</sub> | toez             | Output Enable to High-Z            |      | 8    |      | 8    |      | 8    |      | 8    | ns   | 2    |

| taxqx             | tон              | Output Hold From Address<br>Change | 3    |      | 3    |      | 3    |      | 3    |      | ns   | 1    |

- tavav -**ADDRESS** tAVQV ---tAXQX DQ PREVIOUS DATA DATA VALID VR001023

Figure 2. Read Timing No. 1 (Address Access)

Note: Chip Select and Output Enable are presumed Valid,  $\overline{W} = V_{IH}$

**tAVQV** \_ tsLQV \_ \_ tSHQZ \_ ISLQX \_ s tGLQV \_ tGHQZ . G \_tGLQX\_ DQ DATA VALID VR001024

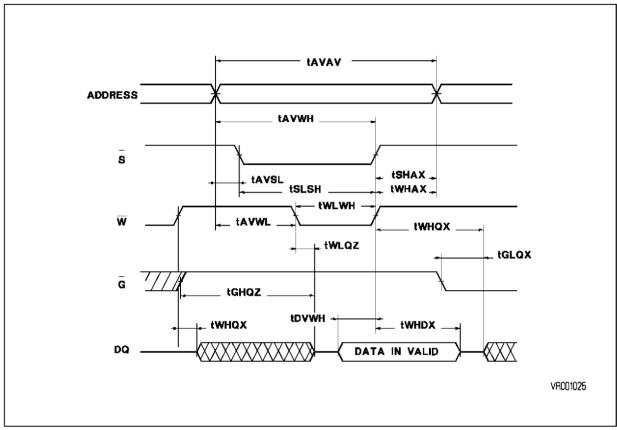

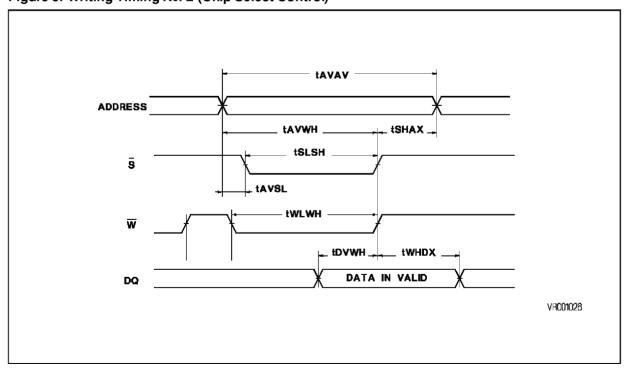

#### WRITE MODE

The MK48S80 is in the Write mode whenever the  $\overline{W}$  and  $\overline{S}$  pins are LOW. Chip Select or  $\overline{W}$  must be inactive during Address transitions. The Write begins with the concurrence of Chip Select being active with  $\overline{W}$  LOW. Therefore address setup times are referenced to Write Enable and Chip Select as  $t_{AVWL}$  and  $t_{AVSL}$ , and is determined to the latter occurring edge. The Write cycle can be terminated

by the earlier rising edge of  $\overline{S}$  or  $\overline{W}$ . If the output is enabled ( $\overline{S} = LOW$ ),  $\overline{G} = LOW$ ), then  $\overline{W}$  will return the outputs to high impedance within  $t_{WLQZ}$  of its falling edge. Care must be taken to avoid bus contention in this type of operation. Data-in must be valid for  $t_{DVWH}$  to the rising edge of W fite Enable, or to the rising edge of W, whichever occurs first, and remain valid  $t_{WHDX}$  after the rising edge of W or W

# WRITE CYCLE TIMING - Electrical Characteristics and Recommended AC Operating Conditions (0 °C $\leq$ T<sub>A</sub> $\leq$ +70 °C; V<sub>CC</sub> = 5V $\pm$ 5%)

| Sym               | ıbol             | Parameter                             | 1                  | 5    | 1    | 7    | 2    | 0    | 2    | :5   | Unit | Note |

|-------------------|------------------|---------------------------------------|--------------------|------|------|------|------|------|------|------|------|------|

| Std               | Alt              | Farameter                             | Min.               | Max. | Min. | Max. | Min. | Max. | Min. | Max. | OTIL | Note |

| t <sub>AVAV</sub> | twc              | Write Cycle Time                      | 20                 |      | 20   |      | 20   |      | 25   |      | ns   |      |

| tavwL             | t <sub>AS</sub>  | Address Set-up to Write<br>Enable Low | 0                  |      | 0    |      | 0    |      | 0    |      | ns   |      |

| tavsl             | t <sub>AS</sub>  | Address Set-up to Chip Select         | 0                  |      | 0    |      | 0    |      | 0    |      | ns   |      |

| t <sub>AVWH</sub> | t <sub>AW</sub>  | Address Valid to End of Write         | 15                 |      | 15   |      | 15   |      | 20   |      | ns   |      |

| twLwH             | tw∈w             | Write Pulse Width                     | 15                 |      | 15   |      | 15   |      | 20   |      | ns   |      |

| t <sub>WHAX</sub> | t <sub>AH</sub>  | Address Hold Time After End of Write  | 0                  |      | 0    |      | 0    |      | 0    |      | ns   |      |

| tslsh             | tcsw             | Chip Select to End of Write           | 15                 |      | 15   |      | 15   |      | 20   |      | ns   |      |

| tshax             | twR              | Write Recovery Time to Chip<br>Select | 0                  |      | 0    |      | 0    |      | 0    |      | ns   |      |

| t <sub>DVWH</sub> | tow              | Data Valid to End of Write            | 10                 |      | 10   |      | 10   |      | 13   |      | ns   |      |

| twHDX             | t <sub>DH</sub>  | Data Hold Time                        | 0                  |      | 0    |      | 0    |      | 0    |      | ns   |      |

| twHQX             | t <sub>WEL</sub> | Write High to Output Low-Z (Active)   | Output Low-Z 0 0 0 |      |      | 0    |      | ns   | 2    |      |      |      |

| t <sub>WLQZ</sub> | twez             | Write Enable to Output High-Z         |                    | 5    |      | 5    |      | 5    |      | 5    | ns   | 2    |

Figure 4. Writing Timing No. 1 (Write Control)

Figure 5. Writing Timing No. 2 (Chip Select Control)

Note:  $\overline{G} = V_{IH}$

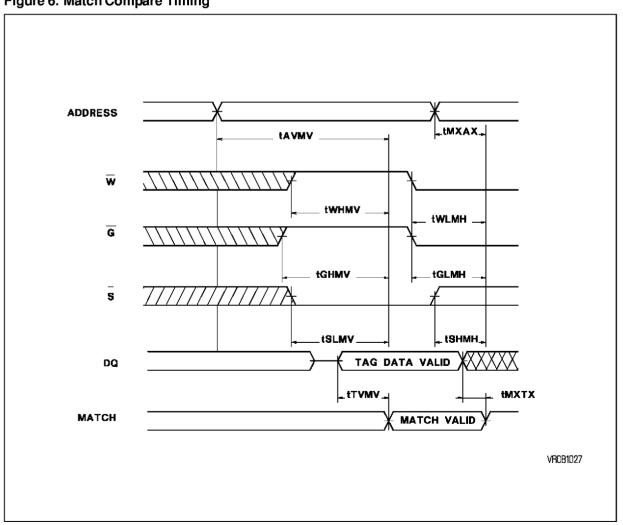

#### COMPARE MODE

The MK48S80 is in the Compare mode whenever  $\overline{W}$  and  $\overline{G}$  are HIGH provided Chip Select ( $\overline{S}$ ) is active LOW. The 13 index address inputs (A0-A12) define a unique location in the static RAM array. The data presented on the Data Inputs (DQ0-DQ7) as Tag Data is compared to the internal RAM data as specified by the index. If all bits are equal, then a hit condition occurs (MATCH = HIGH). When at least one bit is not equal, then MATCH will go LOW signifying a miss condition. The MATCH output will be valid taymy from stable address, or trymy from valid Tag Data when S is LOW. Should the address be stable with valid Tag Data, and the device is deselected ( $\overline{S} = HIGH$ ), then MATCH will be valid tslmv from the falling edge of Chip Select (S). When executing a write-to-compare cycle ( $\overline{W} = LOW$ ,  $\overline{G}$ = LOW or HIGH), MATCH will be valid twhmy or t<sub>GHMV</sub> from the latter rising edge of  $\overline{W}$  or  $\overline{G}$  respectively.

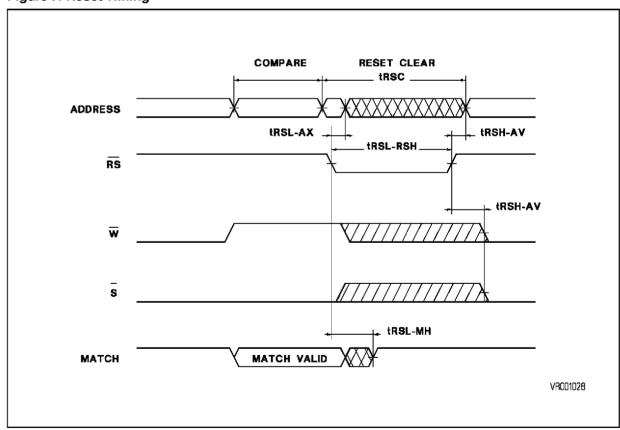

### **RESET MODE**

The MK48S80 allows an asynchronous reset clear whenever  $\overline{\text{RS}}$  is LOW regardless of the logic state on the other input pins. Reset clears all internal RAM bits (65,536 bits) to a logic zero as long as  $t_{\text{RSL-RSH}}$  is satisfied. The state of the outputs is

determined by the control logic input pins  $\overline{S}$ ,  $\overline{W}$ , and  $\overline{G}$  during reset (see Truth Table). The MATCH output will go HIGH t<sub>RSL-MH</sub> from the falling edge of  $\overline{RS}$ , and all inputs will not be recognized unit t<sub>RSH-AV</sub> from the rising edge of reset ( $\overline{RS}$ ).

#### **APPLICATION**

The MK48S80 operates from a 5V supply. It is compatible with all standard TTL families on all inputs and outputs. The device should share a solid ground plane with any other devices interfaced with it, particularly TTL devices. A pull-up resistor is also recommended for the RS input. This will ensure that any low going system noise, coupled onto the input does not drive RS below VIH minimum specifications. This will enhance proper device operation, and avoid possible partial flash clear cycles. Additionally, because the outputs can drive rail-torail into high impedance loads, the MK48S80 can also interface to 5V CMOS on all inputs and outputs. The MK48S80 provides the system designer with 64K fast static memory, a MATCH out-put, and a BYTEWIDE on-board comparator, all in one chip. The MK48S80 compares the contents of addressed RAM locations to the current data inputs. A logic one "1" output on the MATCH pin indicates that the input data and the RAM data

**COMPARE CYCLE TIMING - Electrical Characteristics and Recommended AC Operating Conditions**  $(0 \text{ °C} \le T_A \le +70 \text{ °C}; V_{CC} = 5V \pm 5\%)$

| Sym               | ıbol             | Parameter                      | 1    | 5    | 1    | 7    | 2    | :0   | 2    | :5   | Unit | Note |

|-------------------|------------------|--------------------------------|------|------|------|------|------|------|------|------|------|------|

| Std               | Alt              | i arameter                     | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | 5    |      |

| t <sub>AVMV</sub> | t <sub>AMA</sub> | Address to MATCH Valid         |      | 15   |      | 17   |      | 20   |      | 25   | ns   | 1    |

| t <sub>SLMV</sub> | tcsm             | Chip Select to MATCH Valid     |      | 8    |      | 8    |      | 10   |      | 15   | ns   | 1    |

| tsнмн             | tсsмн            | Chip Deselect to MATCH<br>High |      | 5    |      | 5    |      | 8    |      | 12   | ns   | 1    |

| t⊤vмv             | t <sub>DMA</sub> | Tag Data to MATCH Valid        |      | 12   |      | 12   |      | 12   |      | 15   | ns   | 1    |

| t <sub>GHMV</sub> | toem             | G High to MATCH Valid          |      | 10   |      | 10   |      | 10   |      | 15   | ns   | 1    |

| t <sub>GLMH</sub> | tоемн            | G Low to MATCH High            |      | 10   |      | 10   |      | 10   |      | 12   | ns   | 1    |

| twhmv             | tw∈м             | W High to MATCH Valid          |      | 10   |      | 10   |      | 10   |      | 20   | ns   | 1    |

| t <sub>WLMH</sub> | twemh            | W Low to MATCH High            |      | 10   |      | 10   |      | 10   |      | 15   | ns   | 1    |

| t <sub>MXAX</sub> | tмна             | MATCH Hold From Address        | 1    |      | 1    |      | 1    |      | 1    |      | ns   | 1    |

| t <sub>MXTX</sub> | t <sub>MHD</sub> | MATCH Hold From Tag Data       | 0    |      | 0    |      | 0    |      | 0    |      | ns   | 1    |

# RESET CYCLE TIMING - Electrical Characteristics and Recommended AC Operating Conditions (0 °C $\leq$ T<sub>A</sub> $\leq$ +70 °C; V<sub>CC</sub> = 5V $\pm$ 5%)

| Symbol               |                  | Parameter                             | 15   |      | 17   |      | 20   |      | 25   |      | Unit  |

|----------------------|------------------|---------------------------------------|------|------|------|------|------|------|------|------|-------|

| Std                  | Alt              | i alametei                            | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | OIIII |

| t <sub>RSC</sub>     | t <sub>RC</sub>  | Flash Clear Cycle Time                | 80   |      | 80   |      | 80   |      | 80   |      | ns    |

| t <sub>RSL-AX</sub>  | t <sub>RSX</sub> | Reset Clear (RS) to Inputs Don't Care | 0    |      | 0    |      | 0    |      | 0    |      | ns    |

| t <sub>RSH-AV</sub>  | t <sub>RSV</sub> | RS to Inputs Valid                    | 5    |      | 5    |      | 5    |      | 5    |      | ns    |

| t <sub>RSL-RSH</sub> | t <sub>RSP</sub> | Reset (RS) Pulse Width                | 75   |      | 75   |      | 75   |      | 75   |      | ns    |

| t <sub>RSL-MH</sub>  | t <sub>RSM</sub> | Reset (RS) to MATCH High              |      | 15   |      | 15   |      | 15   |      | 15   | ns    |

Figure 6. Match Compare Timing

match. Conversely, a logic zero "0" on the MATCH pin indicates at least one bit of difference between the RAM contents and the input TAG, generating a miss.

The MATCH output is constructed with a totempole arrangement. The totem-pole configuration allows the designer to minimize switching delays and noise problems associated with open-drain devices. In a cache subsystem, the MATCH signal provides the processor or CPU with the necessary information concerning wait state conditions. The purpose of a cache subsystem is to maintain a duplicate copy of portions of the main memory. When a valid match occurs, the system processor uses data from the fast cache memory, and avoids longer cycles to the main memory. Therefore, implementing cache subsystems with the MK48S80, and providing good hit or match ratio designs will

enhance overall system performance. Because high frequency current transients will be associated with the operation of the MK48S80, power line inductance must be minimized on the circuit board power distribution network. Power and ground trace gridding or separate power planes can be employed to reduce line inductance. Though often times not thought of as such, the traces of a memory board are basically unterminated, low impedance transmission lines. As such they are subject to signal reflections manifested as noise, undershoots and excessive ringing. Series termination in close proximity to the TTL drivers can improve driver/signal path impedance matching. While experimentation most often proves to be the only practical approach to selection of series resistors, values in the range of 10 to 33 ohms often prove most suitable.

Figure 7. Reset Timing

Note:  $\overline{G} = High$

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                             | Value      | Unit |

|------------------|---------------------------------------|------------|------|

| Vı               | Voltage on any Pin Relative to Ground | –0.3 to 6  | V    |

| T <sub>A</sub>   | Operating Temperature                 | 0 to 70    | °C   |

| T <sub>STG</sub> | Storage Temperature                   | -65 to 150 | °C   |

| P <sub>D</sub>   | Power Dissipation                     | 1          | W    |

| Гоит             | Output Current                        | 50         | mA   |

Note: This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

## **RECOMMENDED DC OPERATING CONDITIONS** (0 °C $\leq$ TA $\leq$ +70 °C)

| Symbol          | Parameter          | Min. | Max.                  | Unit | Notes |

|-----------------|--------------------|------|-----------------------|------|-------|

| Vcc             | Supply Voltage     | 4.75 | 5.25                  | ٧    | 3     |

| GND             | Ground             | 0    | 0                     | V    | 3     |

| V <sub>IH</sub> | Logic 1 All Inputs | 2.2  | V <sub>CC</sub> + 0.3 | ٧    | 3     |

| V <sub>IL</sub> | Logic 0 All Inputs | -0.3 | 0.8                   | V    | 3     |

## **DC ELECTRICAL CHARACTERISTICS** (0 °C $\leq$ T<sub>A</sub> $\leq$ +70 °C; V<sub>CC</sub> = 5V $\pm$ 5%)

| Symbol           | Parameter                                         | Min.       | Max. | Unit | Notes |

|------------------|---------------------------------------------------|------------|------|------|-------|

| lcc <sub>1</sub> | Average V <sub>CC</sub> Power Supply Current      |            | 160  | mA   | 4     |

| I <sub>IL</sub>  | Input Leakage Current                             | -1         | 1    | μΑ   | 5     |

| loL              | Output Leakage Current                            | <b>-</b> 5 | 5    | μΑ   | 6     |

| V <sub>OH</sub>  | Logic 1 Output Voltage (I <sub>OUT</sub> = -4 mA) | 2.4        |      | μА   | 3     |

| V <sub>OL</sub>  | Logic 0 Output Voltage (I <sub>OUT</sub> = 8 mA)  |            | 0.4  | V    | 3     |

# **CAPACITANCE** ( $T_A = 25 \, ^{\circ}C$ , f = 1 MHz)

| Symbol          | Parameter                     | Max. | Unit | Notes |

|-----------------|-------------------------------|------|------|-------|

| C <sub>IN</sub> | Capacitance on all Input pins | 4    | pF   | 7     |

| Соит            | Capacitance on Q Output pins  | 10   | pF   | 7     |

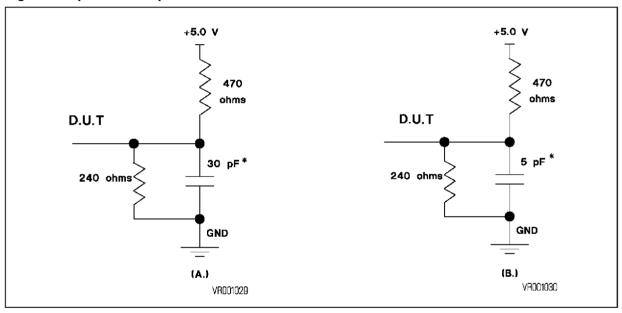

### **AC TEST CONDITIONS**

| Parameter                                      | Value   | Unit |  |

|------------------------------------------------|---------|------|--|

| Input Levels                                   | 0 to 3  | V    |  |

| Transition Time                                | 1.5     | ns   |  |

| Input and Output Signal Timing Reference Level | 1.5     | V    |  |

| Ambient Temperature                            | 0 to 70 | °C   |  |

| Supply Voltage                                 | 5 ± 5%  | V    |  |

Figure 8. Equivalent Output Load Circuits

#### Notes:

- 1. Measured with load shown in Figure 8A.

- 2. Measured with load shown in Figure 8B.

- 3. All voltages referenced to GND.

- 4.  $I_{CC1}$  is measured as the average AC current with  $V_{CC} = V_{CC}$  (max) and with the outputs open circuit.  $t_{AVAV} = t_{AVAV}$  (min) duty cycle 100%.

- 5. Input leakage current specifications are valid for all  $V_{IN}$  such that 0 V <  $V_{IN}$  <  $V_{CC}$ . Measured at  $V_{CC}$  =  $V_{CC}$  (max).

- 6. Output leakage current specifications are valid for all V<sub>OUT</sub> such that 0 V < V<sub>OUT</sub> < V<sub>CC</sub>,  $\overline{S}$  = V<sub>IH</sub> and V<sub>CC</sub> in valid operating range.

- 7. Sampled, not 100% tested.

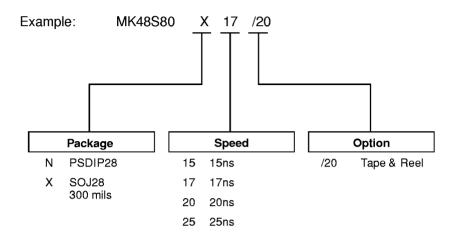

### **ORDERING INFORMATION SCHEME**

For a list of available options of Package and Speed, refer to the current Memory Shortform catalogue. For further information on any aspect of this device, please contact SGS-THOMSON Sales Office nearest to you.

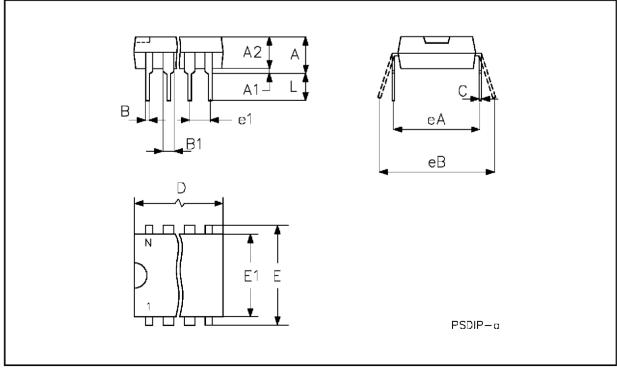

# PSDIP28 - 28 pin Plastic Skinny DIP, 300 mils width

| Symb       |      | mm    |       |       | inches |       |

|------------|------|-------|-------|-------|--------|-------|

| Symb       | Тур  | Min   | Max   | Тур   | Min    | Max   |

| А          |      |       | 4.57  |       |        | 0.180 |

| <b>A</b> 1 |      | 0.38  | -     |       | 0.015  | -     |

| A2         |      | 3.05  | 3.56  |       | 0.120  | 0.140 |

| В          |      | 0.38  | 0.53  |       | 0.015  | 0.021 |

| B1         |      | 1.14  | 1.27  |       | 0.045  | 0.050 |

| С          |      | 0.20  | 0.30  |       | 0.008  | 0.012 |

| D          |      | 34.54 | 34.80 |       | 1.360  | 1.370 |

| E          |      | 7.62  | 8.26  |       | 0.300  | 0.325 |

| E1         |      | 7.11  | 7.49  |       | 0.280  | 0.295 |

| e1         | 2.54 | _     | -     | 0.100 | _      | _     |

| eA         | 7.62 | _     | _     | 0.300 | _      | _     |

| eB         |      |       | 10.92 |       |        | 0.430 |

| L          |      | 3.18  | 3.43  |       | 0.125  | 0.135 |

| N          |      | 28    |       |       | 28     |       |

PSDIP28

Drawing is out of scale

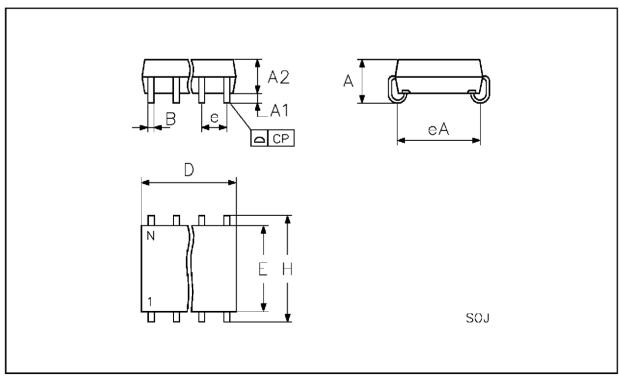

# SOJ28 - 28 lead Plastic Small Outline J-lead, 300 mils

| Symb | mm   |       |       | inches |       |       |

|------|------|-------|-------|--------|-------|-------|

|      | Тур  | Min   | Max   | Тур    | Min   | Max   |

| Α    |      | 3.05  | 3.56  |        | 0.120 | 0.140 |

| A1   |      | 0.71  | 0.91  |        | 0.028 | 0.036 |

| A2   |      | 2.29  | 2.39  |        | 0.090 | 0.094 |

| В    |      | 0.36  | 0.48  |        | 0.014 | 0.019 |

| D    |      | 17.81 | 18.06 |        | 0.701 | 0.711 |

| Е    |      | 7.42  | 7.59  |        | 0.292 | 0.299 |

| е    | 1.27 | _     | _     | 0.050  | _     | _     |

| eA   |      | 6.65  | 6.91  |        | 0.262 | 0.272 |

| Н    |      | 8.51  | 8.81  |        | 0.335 | 0.347 |

| N    |      | 28    |       |        | 28    |       |

| CP   |      |       | 0.10  |        |       | 0.004 |

SOJ28

Drawing is out of scale

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

™ TAGRAM is a trademark of SGS-THOMSON Microelectronics

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.