**TENTATIVE**

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC90A44P, TC90A44F

## NTSC 2-LINE DIGITAL Y/C SEPARATION IC

The TC90A44P, TC90A44F separates luminance (Y) and chrominance (C) signals from NTSC system composite video signal by using 2 horizontal (H) lines. It employs the Toshiba logical comb filter to reduce color dot interference and realizes high performance Y/C separation. The Y/C separation unit for TV and VCR set is able to assembled at low cost, because it requires few external parts and no adjustment.

#### **FEATURES**

- TV system : NTSC

- PLL4 x multiplication circuit

- sync. tip clamping circuit

- Internal 8bit A/D converter

- Internal 8bit D/A converters (2ch.)

- 1H line memory

- Dynamic comb filter

- Color killer mode (Y/C separation OFF)

- DIP16/SOP16 package

- 5V single power supply

Weight

DIP16-P-300-2.54A : 1.00g (Typ.) SOP16-P-300-1.27 : 0.18g (Typ.)

961001EBA

The products described in this document are subject to foreign exchange and foreign trade control laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

<sup>●</sup> TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

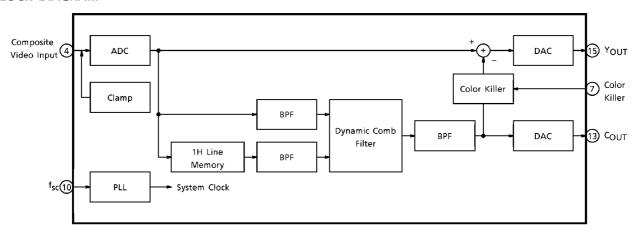

### **BLOCK DIAGRAM**

#### **TERMINAL CONNECTION DIAGRAM**

### **TERMINAL FUNCTION**

| PIN<br>No. | NAME   | FUNCTION                                                                                                                                                                                   | 1/0 | INTERFACE CIRCUIT |

|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|

| 1          | AVSS   | Ground for analog components.                                                                                                                                                              | _   | _                 |

| 2          | VRB    | ADC bias lower limit reference voltage. This defaults internally to approximately 2.25V, so this pin should normally be conected to ground (AVSS) through a $0.01\mu F$ capacitor.         |     | 2 W               |

| 3          | VRT    | ADC bias higher limit reference voltage. This defaults internally to approximately 2.8V, so this pin should normally be conected to ground (AVSS) through a $0.01\mu\mathrm{F}$ capacitor. | 1   | 3<br>3<br>1       |

| 4          | ADIN   | Composite video signal input.                                                                                                                                                              | ı   | 4                 |

| 5          | BIAS1  | ADC bias voltage. This defaults internally to approximately 1.3V, so this pin should normally be conected to ground (AVSS) through a $0.01\mu\mathrm{F}$ capacitor.                        | _   | (5) 1.3V          |

| 6          | TEST   | Test terminal. Normally connected to ground (DVss).                                                                                                                                        | _   | 6                 |

| 7          | KILLER | This pin is switch for color killer circuit.  H: For B/W signal, Y/C separation  OFF.  L: Normal Y/C separation                                                                            | I   | 7                 |

| PIN<br>No. | NAME             | FUNCTION                                                                                                                                                            | 1/0 | INTERFACE CIRCUIT                        |

|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------|

| 8          | DV <sub>DD</sub> | Power supply for digital components (+5V).                                                                                                                          | _   | _                                        |

| 9          | DVSS             | Ground for digital components.                                                                                                                                      |     | _                                        |

| 10         | CKIN             | Clock input. After applying capacitor for DC cut, input a color-burst-synchronized f <sub>sc</sub> clock signal to this pin.                                        | ı   | 10 10 10 10 10 10 10 10 10 10 10 10 10 1 |

| 11         | VFIL             | Connect a VCO filter to this pin.                                                                                                                                   | _   |                                          |

| 12         | BIAS3            | DAC bias voltage. This defaults internally to approximately 3.4V, so this pin should normally be conected to ground (AVSS) through a $0.01\mu F$ capacitor.         | _   | (2)<br>3.4V                              |

| 13         | СОПТ             | Chrominance signal output.                                                                                                                                          | 0   | 13                                       |

| 14         | BIAS2            | DAC bias voltage. This defaults internally to approximately 1.7V, so this pin should normally be conected to ground (AVSS) through a $0.01\mu\mathrm{F}$ capacitor. | I   | (4) 1.7V                                 |

| 15         | Youт             | Luminance signal output.                                                                                                                                            | 0   | 15                                       |

| 16         | $AV_{DD}$        | Power supply for analog components (+5V)                                                                                                                            |     | _                                        |

#### **FUNCTION BLOCK DESCRIPTIONS**

(1) Input clamp (CLAMP)

This is sync. tip clamp circuit for composite signal.

This circuit makes feedback so that the min. data after A/D converter at Y/C separation equal to internal DC bias level.

(2) A/D converter (ADC)

This is high speed series-parallel 8bit A/D converter. Input dynamic range is 1.0V<sub>p-p</sub> (Typ.)

(3) Line memory

This block is DRAM line memory for 1H delay.

(4) Band-pass filter (BPF)

This filter extracts the signal of chrominance band from composite video signal. The center frequency is  $f_{SC}$ .

(5) Dynamic comb filter (DCF)

This block is logical comb filter to extract the chrominance signal. Filtering logic applies a correlation of two lines to reduce color dot crawl and cross color.

(6) Color killer circuit (KILLER)

This block is applied for black and white (B/W) signal white have no color burst. When pin 10 (KILLER) is "H", logic stop Y/C separation and output composite video signal from pin 14 (Y<sub>OUT</sub>).

(7) PLL (4 times multiply clock generator)

This block is 4 times multiplier and makes 4f<sub>SC</sub> as system clock.

(8) RTIM (Clock/memory timing generator)

This block supplies system clock (4f<sub>SC</sub>) to each block via buffer and generates timing signal for memories.

(9) D/A converter (DAC)

This is high speed 8bit D/A converter. Output dynamic lange is  $2.3V_{p-p}$  (Typ.).

## **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERI         | CHARACTERISTIC |                                     | RATING                    | UNIT |

|--------------------|----------------|-------------------------------------|---------------------------|------|

| Power Supply Volta | ge             | $V_{DD}$ $V_{SS} \sim V_{SS} + 6.5$ |                           | <    |

| Input Voltage      |                | $v_{IN}$                            | -0.3~V <sub>DD</sub> +0.3 | <    |

| Dannar Dissipation | TC90A44P       | PD                                  | 600                       | mW   |

| Power Dissipation  | TC90A44F       | (Note)                              | 440                       | mvv  |

| Storage Temperatur | e              | T <sub>stg</sub>                    | <b>- 55∼125</b>           | °C   |

(Note)  $Ta = 70^{\circ}C$

#### RECOMMENDED OPERATING CONDITION

| CHARACTERISTIC        | SYMBOL           | TEST CONDITION | MIN. | TYP. | MAX.     | UNIT |

|-----------------------|------------------|----------------|------|------|----------|------|

| Power Supply Voltage  | $V_{DD}$         | _              | 4.75 | 5.00 | 5.25     | V    |

| Input Voltage         | VIN              | _              | 0    | _    | $V_{DD}$ | V    |

| Operating Temperature | T <sub>opr</sub> |                | - 10 | _    | 70       | °C   |

## **ELECTRICAL CHARACTERISTICS**

DC CHARACTERISTICS ( $Ta = 25^{\circ}C$ ,  $V_{DD} = 5V$ )

| CHARACT              | ERISTIC     | SYMBOL            | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                | MIN. | TYP.     | MAX.     | UNIT |

|----------------------|-------------|-------------------|----------------------|---------------------------------------------------------------|------|----------|----------|------|

| Power Supply         | Voltage     | $V_{\mathrm{DD}}$ | 1                    |                                                               | 4.75 | 5.00     | 5.25     | V    |

| Supply Current       |             | I <sub>DD</sub>   | 1                    |                                                               | 45   | 60       | 75       | mΑ   |

| Outrut Valta         | امنیما      | YOUT              | 4                    |                                                               | 3.55 | 3.70     | 3.85     | .,   |

| Output Voltage Level |             | COUT              | 1                    |                                                               | 3.70 | 3.85     | 4.00     | V    |

|                      |             | VRB               |                      |                                                               | 2.15 | 2.25     | 2.35     |      |

|                      |             | VRT               | 1                    | CLOCK = 3.579545MHz<br>V <sub>IN</sub> = 0.75V <sub>p-p</sub> | 2.7  | 2.8      | 2.9      | V    |

|                      |             | ADIN              |                      |                                                               | 2.35 | 2.45     | 2.55     |      |

| Tamainal Valt        | امتنما متمم | BIAS1             |                      |                                                               | 1.0  | 1.3      | 1.7      |      |

| Terminal Volt        | age Level   | BIAS2             |                      |                                                               | 1.2  | 1.7      | 2.1      |      |

|                      |             | BIA\$3            |                      |                                                               | 3.0  | 3.4      | 4.0      |      |

|                      |             | VFIL              | -                    |                                                               | 1.2  | 1.9      | 3.0      | 1    |

|                      |             | CKIN              |                      |                                                               | 1.8  | 2.3      | 2.8      |      |

| Input                | High Level  | $V_{IH}$          | 1                    |                                                               | 4    | <u> </u> | <u> </u> | V    |

| Voltage              | Low Level   | $V_{IL}$          | 1                    |                                                               | _    | _        | 1        | V    |

#### **AC CHARACTERISTICS**

(1) Y output (Ta = 25°C,  $V_{DD}$  = 5V, input clock : 3.579545MHz 0.4V<sub>p-p</sub>, S<sub>1</sub> = 1)

| CHARACTERISTICS                             |                                 | SYMBOL   | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                                                                                                  | MIN.  | TYP.  | MAX.  | UNIT              |

|---------------------------------------------|---------------------------------|----------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| Input Level                                 |                                 | $v_{IN}$ | 1                    | 0~140 IRE                                                                                                                                                                       | _     | 0.75  | _     | V <sub>p-p</sub>  |

| Low Frequency Gain                          |                                 | GV       | 1                    | $S_2 = 1$ , $S_3 = 1$ , $S_4 = 2$<br>$V_{IN} = 15.73426 \text{kHz}$ , $0.75 V_{p-p}$ ,<br>Vdc = 2.5 V                                                                           | 6.8   | 7.2   | 7.7   | dВ                |

| Frequency                                   | f <sub>2</sub> / f <sub>1</sub> | MTF1     | 1                    |                                                                                                                                                                                 | - 0.8 | - 1.0 | - 2.0 | dB                |

| Response                                    | f4/f1                           | MTF2     | '                    | $S_2 = 1$ , $S_3 = 1$ , $S_4 = 2$                                                                                                                                               | - 1.5 | - 2.0 | - 3.0 | ub                |

| Comb<br>Characteristics                     | f <sub>2</sub> / f <sub>3</sub> | СОМВҮ    | 1                    | $V_{IN} = 0.75V_{p-p}$ , $Vdc = 2.5V$                                                                                                                                           | _     | - 46  | - 40  | dB                |

| Output Impedance                            |                                 | Zo       | 1                    | $S_2 = 2$ , $S_4 = 2$<br>$V_{IN} = 15.73426 \text{kHz}$ , $0.75 V_{p-p}$ ,<br>$V_{dc} = 2.5 V$<br>$Z_0 = \frac{V_1 - V_2}{V_2} \times 400$<br>$V_1 : S_3 = 1$ , $V_2 : S_3 = 2$ | 250   | 400   | 700   | Ω                 |

| Clock Leak<br>(4f <sub>SC</sub> Components) |                                 | Lck      | 1                    | $S_2 = 1$ , $S_3 = 1$ , $S_4 = 1$<br>$V_{IN} = No input$                                                                                                                        | _     | 2     | 10    | mV <sub>rms</sub> |

| Clock Leak<br>(f <sub>sc</sub> Components)  |                                 | Lsc      | 1                    | $S_2 = 1$ , $S_3 = 1$ , $S_4 = 1$<br>$V_{IN} = No input$                                                                                                                        | _     | 1     | 3     | mV <sub>rms</sub> |

(Note)  $f_1 = fH = 15.73426 kHz$ ,  $f_2 = f_{SC} = 3.579545 MHz$ ,  $f_3 = f_{SC} + 1/2 fH = 3.587412 MHz$ ,  $f_4 = 1/3 \ (4 f_{SC}) = 4.772727 MHz$

## (2) C output (Ta = 25°C, $V_{DD}$ = 5V, input clock : 3.579545MHz 0.4V<sub>p-p</sub>, $S_1$ = 2)

| CHARACTERISTICS                                           | SYMBOL | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                                                                                     | MIN.  | TYP.  | MAX.  | UNIT              |

|-----------------------------------------------------------|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| Gain                                                      | CV     | 1                    | $S_2 = 1$ , $S_3 = 1$ , $S_4 = 1$<br>$V_{IN} = 0.75V_{p-p}$                                                                                                        | 5.7   | 6.2   | 6.7   | dB                |

| BPF Characteristics                                       | BWCW   | 1                    | $S_2 = 2$ , $S_3 = 1$ , $S_4 = 2$<br>$V_{IN} = 0.75V_{p-p}$ , $Vdc = 2.5V$<br>$(f_{SC} - 503496Hz) - (f_{SC})$                                                     | - 2.5 | - 1.9 | - 1.5 | dB                |

| Comb Characteristics                                      | сомвс  | 1                    | $S_2 = 1$ , $S_3 = 1$ , $S_4 = 2$<br>$V_{IN} = 0.75V_{p-p}$ , $Vdc = 2.5V$                                                                                         |       | - 38  | - 35  | dB                |

| Differential Gain                                         | DG     | 1                    | $S_2 = 1$ , $S_3 = 1$ , $S_4 = 1$<br>Modulated lamp signal                                                                                                         | 0     | 2     | 5     | %                 |

| Differential Phase                                        | DP     | '                    | 140 IRE : 0.75V                                                                                                                                                    | 0     | 2     | 5     | ٥                 |

| Output Impedance                                          | Zo     | 1                    | $S_2 = 2$ , $S_4 = 2$<br>$V_{IN} = 15.73426 kHz$ , $0.75 V_{p-p}$ ,<br>Vdc = 2.5 V<br>$Zo = \frac{V_1 - V_2}{V_2} \times 400$<br>$V_1 : S_3 = 1$ , $V_2 : S_3 = 2$ | 250   | 400   | 700   | Ω                 |

| Clock Leak<br>(4f <sub>sc</sub> Components)               | Lck    | 1                    | $S_2 = 1$ , $S_3 = 1$ , $S_4 = 1$<br>$V_{IN} = No input$                                                                                                           |       | 2     | 10    | mV <sub>rms</sub> |

| Fundamental Clock<br>Leak<br>(f <sub>SC</sub> Components) | Lsc    | 1                    | S <sub>2</sub> = 1, S <sub>3</sub> = 1, S <sub>4</sub> = 1<br>V <sub>IN</sub> = No input                                                                           | _     | 1     | 3     | mV <sub>rms</sub> |

## (3) PLL circuit characteristics

| CHARACTERISTICS                              | SYMBOL | TEST<br>CIR-<br>CUIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT             |

|----------------------------------------------|--------|----------------------|----------------|------|------|------|------------------|

| Pull-In Frequency<br>Range                   | fck    | 1                    | _              | 3.5  | 3.6  | 3.7  | MHz              |

| Input Amplitude (f <sub>SC</sub> Components) | Vck    | 1                    |                | 0.35 | 0.5  | 1    | V <sub>p-p</sub> |

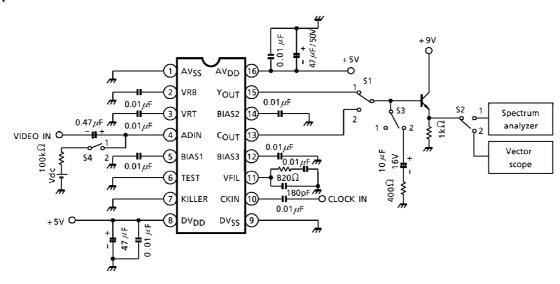

### **TEST CIRCUIT 1**

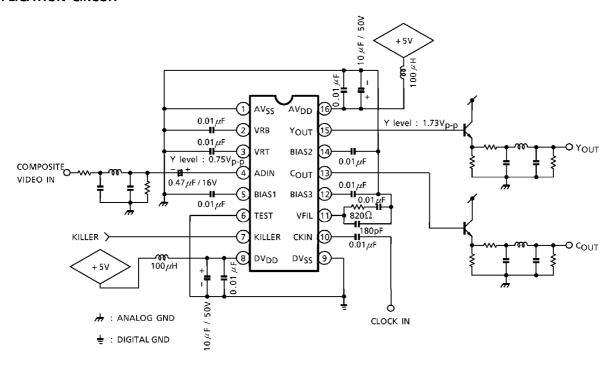

#### **APPLICATION CIRCUIT**

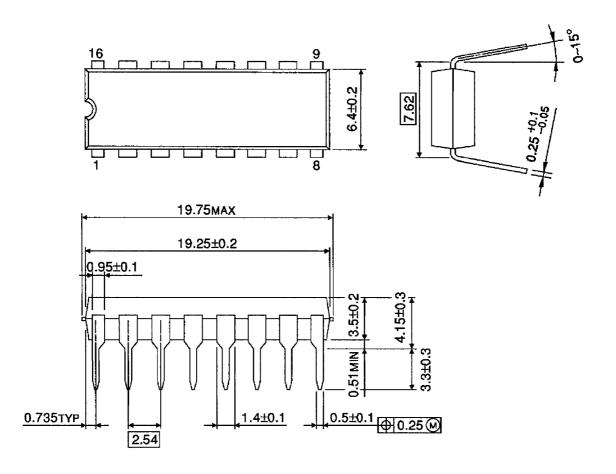

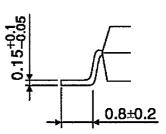

### **OUTLINE DRAWING**

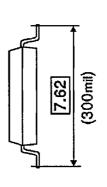

DIP16-P-300-2.54A Unit: mm

Weight: 1.00g (Typ.)

Unit: mm

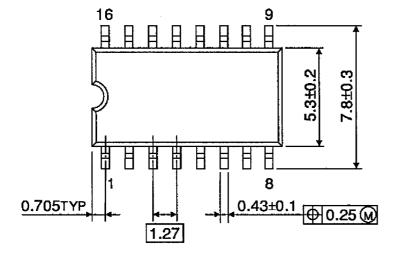

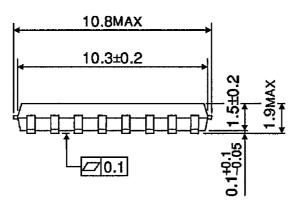

## **OUTLINE DRAWING**

SOP16-P-300-1.27

Weight: 0.18g (Typ.)