SN54HC677 . JT PACKAGE

SN74HC677 . .. DW OR NT PACKAGE

D2833, MARCH 1984-REVISED SEPTEMBER 1987

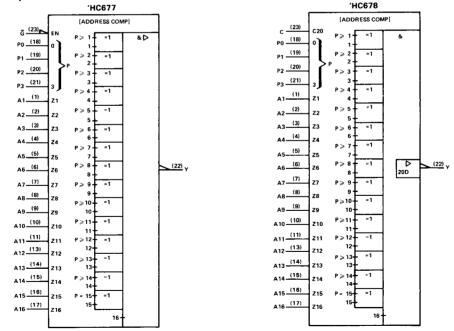

- 'HC677 is a 16-Bit Address Comparator with Enable

- 'HC678 is a 16-Bit Address Comparator with Latch

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs

- Dependable Texas Instruments Quality and Reliability

#### description

The 'HC677 and 'HC678 address comparators simplify addressing of memory boards and/or other peripheral devices. The four P inputs are normally hard wired with a preprogrammed address. An internal decoder determines what input information applied to the 16 A inputs must be low or high to cause a low state at the output (Y). For example, a positive-logic bit combination of 0111 (decimal 7) at the P input determines that inputs A1 through A7 must be low and that inputs A8 through A16 must be high to cause the output to go low. Equality of the address applied at the A inputs to the preprogrammed address is indicated by the output being low.

The 'HC677 features an enable input  $(\overline{G})$ . When  $\overline{G}$  is low, the device is enabled. When  $\overline{G}$  is high, the device is disabled and the output is high regardless of the A and P inputs. The 'HC678 features a transparent latch and a latch enable input (C). When C is high, the device is in the transparent mode. When C is low, the previous logic state of Y is latched.

The SN54HC677 and SN54HC678 are characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C. The SN74HC677 and SN74HC678 are characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C.

(TOP VIEW) U24□ VCC A2 [ 23 C ДЗ ПЗ 22 N 21 T P3 A6 🗍 A7 🗍 A8 [ 17 A 16 ΔΦ 16 A 15 A10 110 15 A 14 A11 | 111 14 A 13 GND 712 SN54HC677 . VFK PACKAGE (TOP VIEW) P2 Α5 24 F 23[ Α6 NC 22[ NC PO 21 A8 20[ A16 Α9 SN54HC678 . . T PACKAGE SN74HC678 . . DW OR NT PACKAGE (TOP VIEW) 23 G 22 Y A2 2 A3 🛚 3 21 P3 20 P2 A4 | | | | Α5 A6 [ Α7 18 PO 17 A 16 16 A15 A9 🗌 A10 10 15 A14 14 A13 A11 111 GND II12 13DYA12 SN54HC678 .V. FK PACKAGE (TOP VIEW) A5 | 6 24 P2 A6 Fi 7 23

NC-No internal connection

NC

A7 A8

Α9

Copyright © 1984, Texas Instruments Incorporated

22 NC 21 PO

20 A16

|        |        |                                    |    |    |    |            |    |    | FUN | CTIO   | N TA  | BLE  | _     |       |     |        |     |     |     |     |     |         |

|--------|--------|------------------------------------|----|----|----|------------|----|----|-----|--------|-------|------|-------|-------|-----|--------|-----|-----|-----|-----|-----|---------|

| 'HC677 | 'HC678 | INPUTS COMMON TO 'HC677 AND 'HC678 |    |    |    |            |    |    |     |        |       |      |       |       |     | OUTPUT |     |     |     |     |     |         |

| G      | c      | Р3                                 | P2 | P1 | PO | <b>A</b> 1 | A2 | АЗ | Α4  | A5     | A6    | A7   | A8    | A9    | A10 | A11    | A12 | A13 | A14 | A15 | A16 | Y       |

| L      | Н      | L                                  | L  | L  | L  | H          | Н  | Н  | Н   | Н      | н     | Н    | Н     | Н     | Н   | Н      | Н   | Н   | Н   | Н   | Н   | L       |

| L      | н      | L                                  | L  | L  | н  | L          | н  | н  | Н   | н      | н     | н    | н     | Н     | н   | Н      | Н   | Н   | Н   | Н   | Н   | L       |

| L      | н      | L                                  | L  | Н  | L  | L          | L  | н  | н   | н      | Н     | н    | н     | Н     | н   | Н      | Н   | н   | Н   | H   | н   | L       |

| L      | н      | L                                  | L  | н  | н  | L          | L  | L  | н   | Н      | н     | н    | Н     | Н     | Н   | Н      | Н   | Н   | Н   | Н   | н   | L       |

|        | Н      | L                                  | Н  | L  | L  | L          | L  | L  | L   | Н      | Н     | Н    | Н     | Н     | Н   | Н      | Н   | Н   | н   | Н   | Н   | L       |

| L      | н      | L                                  | н  | L  | н  | L          | L  | L  | L   | L      | Н     | Н    | н     | Н     | Н   | Н      | Н   | Н   | Н   | Н   | Н   | L       |

| L      | н      | L                                  | н  | н  | L  | L          | L  | Ł  | L   | L      | L     | н    | н     | Н     | Н   | Н      | Н   | Н   | Н   | Н   | Н   | L       |

| L      | н      | L                                  | н  | н  | н  | L          | L  | L  | L   | L      | L     | L    | Н     | Н     | Н   | Н      | н   | Н   | Н   | Н   | н   | L       |

| L      | н      | н                                  | L  | L  | L  | L          | L  | L  | L   | L      | Ĺ     | L    | L     | Н     | Н   | Н      | Н   | Н   | Н   | Н   | Н   | L       |

| L      | Н      | н                                  | L  | L  | Н  | L          | L  | L  | L   | L      | L     | L    | L     | L     | Н   | н      | н   | Н   | Н   | Н   | Н   | L       |

| L      | H.     | H                                  | L  | н  | L  | L          | L  | L  | L   | L      | L     | L    | L     | L     | L   | н      | Н   | Н   | н   | Н   | н   | l L     |

| L      | н      | н                                  | L  | н  | н  | L          | L  | L  | L   | L      | L     | L    | L     | L     | L   | L      | Н   | Н   | Н   | Н   | Н   | L       |

| L      | н      | Н                                  | Н  | Ľ  | L  | L          | L  | L  | L   | L      | L     | L    | L     | L     | Ĺ   | Ĺ      | L   | Н   | Н   | Н   | Н   | L       |

| L      | н      | н                                  | н  | L  | н  | L          | L  | L  | L   | L      | L     | L    | L     | L     | L   | L      | L   | L   | Н   | Н   | Н   | L       |

| L      | н      | н                                  | н  | н  | L  | L          | L  | L  | L   | L      | L     | L    | L     | L     | L   | L      | L   | L   | L   | Н   | Н   | L       |

| Ł      | н      | н                                  | Н  | Н  | н  | L          | L  | L  | Ł   | L      | L     | L    | L     | L     | L   | L      | L   | L   | L   | L   | Н   | L       |

| L      | Н      |                                    |    |    |    |            |    |    |     | All ot | her c | ombi | natio | ns    |     |        |     |     |     |     |     | Н       |

| н      |        |                                    |    |    |    |            |    |    | 'H  | C677   | 7: An | у со | mbina | ation |     |        |     |     |     |     |     | Н       |

|        | L      | $\vdash$                           |    |    |    |            |    |    | 'H  | C678   | 3: An | у со | mbin  | ation | ı   |        |     |     |     |     |     | Latched |

## logic symbols†

$<sup>^\</sup>dagger$  These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for DW, JT, and NT packages.

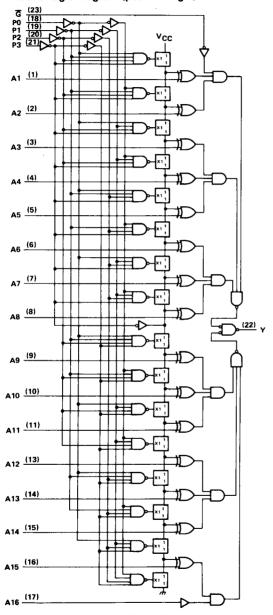

### 'HC677 logic diagram (positive logic)

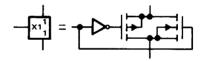

In order to understand the implementation of this device, it is essential that the function of the vertical string of transmission gates be understood. A schematic of one of these gates is shown below. If the input to the transmission gate labeled "X1" is high, then the transmission path between the two ports labeled "1" is on. If the "X1" input is low, then the transmission path between the two ports labeled "1" is off. Only one of the 16 transmission gates can be off while the device is operating; which one is off is determined by inputs PO through P3. The lines going from the string of transmission gates to the exclusive-OR gates located above the transmission gate that is off will be high. The lines going to the exclusive-OR gates located below that transmission gate will be low.

Pin numbers shown are for DW, JT, and NT packages

'HC678 logic diagram (positive logic) C (23) P0 (18) P1 (19) P2 (20) P3 (21) vcc A1 (1) A2 (2) A3 (3) A4 (4) A5 (5) A6 (6) A7 (7) A8 (8) C1 (22) A9 (9) A10 (10) A11 (11) A12 (13) A13 (14) A14 (15) A15 (16) A16 (17)

An explanation of the function of the string of transmission gates appears with the 'HC677 logic diagram on the previous page.

Pin numbers shown are for DW, JT, and NT packages.

# absolute maximum ratings over operating free-air temperature range<sup>†</sup>

| Supply voltage, VCC                                                    |

|------------------------------------------------------------------------|

| Input clamp current, IjK (Vj < 0 or Vj > VCC) ± 20 mA                  |

| Output clamp current, IOK (VO < 0 or VO > VCC ± 20 mA                  |

| Continuous output current, IO (VO = 0 to VCC) ± 25 mA                  |

| Continuous current through VCC or GND pins                             |

| Lead temperature 1,6 mm (1/16 in) from case for 60 s: FK or JT package |

| Lead temperature 1,6 mm (1/16 in) from case for 10 s: DW or NT package |

| Storage temperature range65°C to 150°C                                 |

<sup>†</sup>Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|                                           |                          | SN54HC677<br>SN54HC678 |     |      | SI<br>SI | UNIT |      |    |

|-------------------------------------------|--------------------------|------------------------|-----|------|----------|------|------|----|

|                                           |                          | MIN                    | NOM | MAX  | MIN      | NOM  | MAX  | 1  |

| V <sub>CC</sub> Supply voltage            |                          | 2                      | 5   | 6    | 2        | 5    | 6    | ٧  |

|                                           | V <sub>CC</sub> = 2 V    | 1.5                    |     |      | 1.5      |      |      |    |

| VIH High-level input voltage              | $V_{CC} = 4.5 V$         | 3.15                   |     |      | 3.15     |      |      | V  |

|                                           | V <sub>CC</sub> = 6 V    | 4.2                    |     |      | 4.2      |      |      |    |

|                                           | V <sub>CC</sub> = 2 V    | 0                      |     | 0.3  | 0        |      | 0.3  |    |

| VIL Low-level input voltage               | $V_{CC} = 4.5 \text{ V}$ | 0                      |     | 0.9  | 0        |      | 0.9  | V  |

|                                           | V <sub>CC</sub> = 6 V    | 0                      |     | 1.2  | 0        |      | 1.2  |    |

| V <sub>I</sub> Input voltage              |                          | 0                      |     | Vcc  | 0        |      | Vcc  | V  |

| VO Output voltage                         |                          | 0                      |     | Vcc  | 0        |      | Vcc  | V  |

|                                           | V <sub>CC</sub> = 2 V    | 0                      |     | 1000 | 0        |      | 1000 |    |

| tt Input transition (rise and fall) times |                          | 0                      |     | 500  | 0        |      | 500  | ns |

| •                                         | V <sub>CC</sub> = 6 V    | 0                      |     | 400  | 0        |      | 400  | ļ  |

| TA Operating free-air temperature         |                          | - 55                   |     | 125  | -40      |      | 85   | °C |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER      | TEST CONDITIONS                                                                | Vcc      | т    | A = 25 | °C   | SN54HC677<br>SN54HC678 |        | SN74HC677<br>SN74HC678 |                   | UNIT |

|----------------|--------------------------------------------------------------------------------|----------|------|--------|------|------------------------|--------|------------------------|-------------------|------|

|                |                                                                                |          | MIN  | TYP    | MAX  | MIN                    | MAX    | MIN                    | MAX               | 1    |

|                |                                                                                | 2 V      | 1.9  | 1.998  |      | 1.9                    |        | 1.9                    |                   |      |

|                | $V_I = V_{IH}$ or $V_{IL}$ , $I_{OH} = -20 \mu A$                              | 4.5 V    | 4.4  | 4.499  |      | 4.4                    |        | 4.4                    |                   |      |

| VoH            |                                                                                | 6 V      | 5.9  | 5.999  |      | 5.9                    |        | 5.9                    |                   | ٧    |

| • •            | $V_I = V_{IH}$ or $V_{IL}$ , $I_{OH} = -4$ mA                                  | 4.5 V    | 3.98 | 4.30   |      | 3.7                    |        | 3.84                   |                   |      |

| T T            | $V_I = V_{IH}$ or $V_{IL}$ , $I_{OH} = -5.2$ mA                                | 6 V      | 5.48 | 5.80   |      | 5.2                    |        | 5.34                   |                   |      |

|                |                                                                                | 2 V      |      | 0.002  | 0.1  |                        | 0.1    |                        | 0.1               |      |

|                | $V_I = V_{IH}$ or $V_{IL}$ , $I_{OL} = 20 \mu A$                               | 4.5 V    |      | 0.001  | 0.1  |                        | 0.1    |                        | 0.1               |      |

| Vol            |                                                                                | 6 V      |      | 0.001  | 0.1  |                        | 0.1    |                        | 0.1               | V    |

| <u> </u>       | V <sub>I</sub> = V <sub>IH</sub> or V <sub>IL</sub> , I <sub>OL</sub> = 4 mA   | 4.5 V    |      | 0.17   | 0.26 |                        | 0.4    |                        | 0.33              |      |

| T I            | V <sub>I</sub> = V <sub>IH</sub> or V <sub>IL</sub> , I <sub>OL</sub> = 5.2 mA | 6 V      |      | 0.15   | 0.26 |                        | 0.4    |                        | 0.1<br>0.1<br>0.1 |      |

| l <sub>l</sub> | V <sub>I</sub> = V <sub>CC</sub> or 0                                          | 6 V      |      | ±0.1   | ±100 | :                      | ± 1000 |                        | ± 1000            | nA   |

| icc            | V <sub>I</sub> = V <sub>CC</sub> or 0, I <sub>O</sub> = 0                      | 6 V      |      |        | 8    |                        | 160    |                        | 80                | μΑ   |

| c <sub>i</sub> |                                                                                | 2 to 6 V |      | 3      | 10   |                        | 10     |                        | 10                | pF   |

## switching characteristics over recommended operating free-air temperature range (unless otherwise noted), CL = 50 pF (see Note 1)

|                 | FROM    | то       | V     | TA  | - 25 | °C  | SN54 | HC677 | SN74HC677 |     | UNIT  |  |

|-----------------|---------|----------|-------|-----|------|-----|------|-------|-----------|-----|-------|--|

| PARAMETER       | (INPUT) | (OUTPUT) | vcc   | MIN | TYP  | MAX | MIN  | MAX   | MIN       | MAX | 0.411 |  |

|                 |         |          | 2 V   |     | 130  | 625 |      | 937   |           | 781 |       |  |

| t <sub>pd</sub> | Any P   | Y        | 4.5 V | ł   | 50   | 125 |      | 187   |           | 156 | ns    |  |

| μ.              |         |          | 6 V   |     | 40   | 112 |      | 169   | l         | 141 |       |  |

| ***             |         |          | 2 V   |     | 90   | 150 |      | 225   |           | 187 |       |  |

| tpd             | Any A   | Y        | 4.5 V |     | 18   | 30  |      | 45    |           | 37  | ns    |  |

| P-0             |         |          | 6 V   |     | 15   | 27  |      | 40    | l         | 34  |       |  |

|                 |         |          | 2 V   |     | 70   | 125 |      | 187   |           | 156 |       |  |

| tpd             | ਫ       | Y        | 4.5 V | 1   | 14   | 25  |      | 37    |           | 31  | ns    |  |

| F               |         |          | 6 V   | 1   | 12   | 22  |      | 33    |           | 27  |       |  |

|                 |         | Ť        | 2 V   |     | 38   | 75  |      | 110   |           | 95  |       |  |

| tt              |         | Y        | 4.5 V |     | 8    | 15  | Į.   | 22    |           | 19  | ns    |  |

| ,               |         |          | 6 V   |     | 6    | 13  |      | 19    |           | 16  |       |  |

| C <sub>pd</sub> | Power dissipation capacitance | No load, TA = 25°C | 40 pF typ |

|-----------------|-------------------------------|--------------------|-----------|

NOTE 1: Load circuit and voltage waveforms are shown in Section 1.

### timing requirement over recommended operating free-air temperature range (unless otherwise noted)

|                    |                                          | V     | T <sub>A</sub> | - 25 | °C  |     |  | SN74HC678 |     | UNIT  |

|--------------------|------------------------------------------|-------|----------------|------|-----|-----|--|-----------|-----|-------|

|                    |                                          | vcc   | MIN            | TYP  | MAX |     |  | MIN       | MAX | 0.411 |

|                    |                                          | 2 V   | 75             |      |     | 112 |  | 94        |     |       |

| t <sub>w</sub> Pul | Pulse duration, enable C high            | 4.5 V | 15             |      |     | 23  |  | 19        |     | ns    |

|                    |                                          | 6 V   | 13             |      |     | 19  |  | 16        |     |       |

|                    |                                          | 2 V   | 500            |      |     | 750 |  | 625       |     |       |

| tsu                | Setup time, P0 thru P3 before enable C1  | 4.5 V | 100            |      |     | 150 |  | 125       |     | ns    |

|                    |                                          | 6 V   | 85             |      |     | 128 |  | 106       |     |       |

|                    |                                          | 2 V   | 100            |      |     | 150 |  | 125       |     |       |

| t <sub>su</sub>    | Setup time, A1 thru A16 before enable CI | 4.5 V | 20             |      |     | 30  |  | 25        |     | ns    |

|                    |                                          | 6 V   | 18             |      |     | 27  |  | 22        |     |       |

|                    | Hold time, P0 thru P3 or                 | 2 V   | 5              |      |     | 5   |  | 5         |     |       |

| th                 | A1 thru A16 after enable Cl              | 4.5 V | 5              |      |     | 5   |  | 5         |     | ns    |

|                    | AT thru A to after enable C1             | 6 V   | 5              |      |     | 5   |  | 5         |     |       |

#### switching characteristics over recommended operating free-air temperature range (unless otherwise noted), C<sub>L</sub> = 50 pF (see Note 1)

| PARAMETER       | FROM    | то       |       | Τø  | _ 25 | °C  | SN54HC678 |     | SN74HC678 |     |      |  |

|-----------------|---------|----------|-------|-----|------|-----|-----------|-----|-----------|-----|------|--|

| PARAMETER       | (INPUT) | (OUTPUT) | Vcc   | MIN | TYP  | MAX | MIN       | MAX | MIN       | MAX | UNIT |  |

|                 |         |          | 2 V   |     | 130  | 625 |           | 937 |           | 781 |      |  |

| t <sub>pd</sub> | Any P   | Y        | 4.5 V |     | 50   | 125 |           | 187 |           | 156 | ns   |  |

| i               |         |          | 6 V   |     | 40   | 112 |           | 169 | 1         | 141 |      |  |

|                 |         | 1        | 2 V   |     | 115  | 175 |           | 262 |           | 219 |      |  |

| t <sub>pd</sub> | Any A   | Y        | 4.5 V |     | 23   | 35  |           | 52  |           | 44  | ns   |  |

|                 |         |          | 6 V   |     | 21   | 31  |           | 46  | ĺ         | 39  |      |  |

|                 |         |          | 2 V   |     | 95   | 150 |           | 225 |           | 187 |      |  |

| t <sub>pd</sub> | С       | Y        | 4.5 V |     | 19   | 30  |           | 45  |           | 37  | ns   |  |

|                 |         |          | 6 V   |     | 17   | 27  |           | 40  |           | 34  |      |  |

|                 |         |          | 2 V   |     | 38   | 75  |           | 110 |           | 95  |      |  |

| tt              |         | Y        | 4.5 V |     | 8    | 15  |           | 22  |           | 19  | ns   |  |

|                 |         |          | 6 V   |     | 6    | 13  |           | 19  |           | 16  |      |  |

Power dissipation capacitance No load, TA = 25°C 40 pF typ

NOTE 1: Load circuit and voltage waveforms are shown in Section 1.

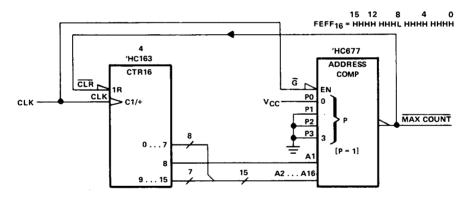

#### TYPICAL APPLICATION INFORMATION

The 'HC677 and 'HC678 can be wired to recognize any one of 216 addresses. The number of "lows" in the address determines the input pattern for the P inputs. Then those system address lines that are low in the address to be recognized are connected to the lowest numbered A inputs of the address comparator and the system address lines that are high are connected to the highest numbered A inputs.

For example, assume the comparator is to enable a device when the 16-bit system address is:

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 Н Н Н Н Н L Н L L

Since the address contains 6 lows and 10 highs, the following connections are made.

P3 to 0 V, P2 to VCC, P1 to VCC, and P0 to 0 V.

System address lines A13, A12, A9, A8, A5, and A4 to comparator inputs A1 through A6 in any convenient order.

The remaining eight system address lines to comparator inputs A7 through A16 in any convenient order.

The output provides an active-low enabling signal.

The following circuit is a modulo-N synchronous counter. The 'HC163 is connected to provide a low-level clear signal when N = FEFF16.

MODULO-N SYNCHRONOUS COUNTER