# MPY016K

# **VLSI Multiplier**

16 x 16 Bit, 40ns

The TRW MPY016K is a video-speed 16 x 16 bit parallel multiplier which operates at a 40ns cycle time (25MHz multiplication rate). The multiplicand and the multiplier may be independently specified as two's complement or unsigned magnitude, yielding a full precision 32-bit product.

Individually clocked input and output registers are provided to maximize system throughput and simplify bus interfacing. These registers are positive-edge-triggered D-type flip-flops. The Most Significant Product (MSP) and Least Significant Product (LSP) can be multiplexed through a dedicated output port, or the LSP can share a bidirectional port with the Y input. All outputs are three-state.

Built with TRW's OMICRON-B  $^{\rm IM}$  1-micron bipolar process, the MPY016K is pin compatible with the industry standard MPY016H and operates with three times the speed at comparable power dissipation. The MPY016K is the industry's first true video-speed 16-bit multiplier.

#### **Features**

- 40ns Multiply Time: MPY016K-1 (Worst Case)

- 45ns Multiply Time: MPY016K (Worst Case)

- Pin Compatible With TRW MPY016H

- 16 x 16 Bit Parallel Multiplication With 32-Bit Output

- Two Least Significant Product Output Modes: Multiplexed With Most Significant Product Or Multiplexed With Y Input

- Output Registers Can Be Made Transparent

- Three-State TTL Output

- Two's Complement, Unsigned Magnitude, Or Mixed Mode Multiplication

- Fully TTL Compatible

- Proven High-Reliability Radiation Hard Bipolar Process

- Single +5V Power Supply

- Available In A 64 Pin Ceramic DIP

# **Applications**

- Array Processors

- Video Processors

- Radar Signal Processors

- FFT Processors

- General Purpose Digital Signal Processors

- Microcomputer/Minicomputer Accelerators

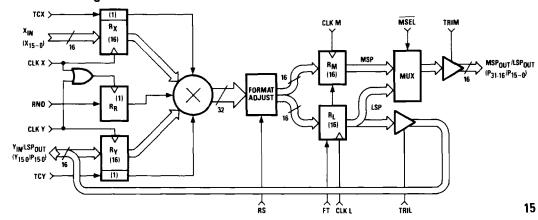

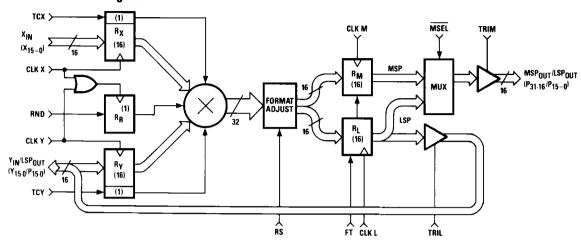

# **Functional Block Diagram**

# **Functional Block Diagram**

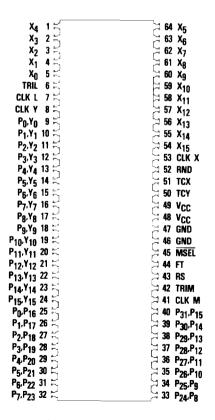

# Pin Assignments

64 Lead DIP - J1 Package

## **Functional Description**

#### **General Information**

The MPY016K has three functional sections: Input registers, an asynchronous multiplier array, and output registers. The input registers store the two 16-bit numbers which are to be multiplied and the instruction which controls the output rounding. The rounding control is used when a single-word output is desired. Each input operand is stored independently, simplifying multiplication by a constant. The asynchronous multiplier array is a network of AND gates and adders,

designed to handle two's complement or unsigned magnitude numbers. The output registers hold the product as two 16-bit words, the Most Significant Product (MSP) and the Least Significant Product (LSP). Three-state output drivers allow the MPY016K to be used on a bus, or allow the least and most significant outputs to be multiplexed over the same 16-bit output lines. The Least Significant Product (LSP) is multiplexed with the Y input.

#### Power

The MPY016K operates from a single +5.0V supply. All power and ground lines must be connected. Note that the device is pin-compatible with the MPY016H, which has an additional

ground pin; this is a control lead in the MPY016K. A ground on this pin (which must exist in all MPY016H applications) will cause the MPY016K to function like an MPY016H.

| Name            | Function                | Value | J1 Package  |

|-----------------|-------------------------|-------|-------------|

| V <sub>CC</sub> | Positive Supply Voltage | +5.0V | Pins 48, 49 |

| GND             | Ground                  | 0.0V  | Pins 46, 47 |

#### **Data Inputs**

The MPY016K has two 16-bit two's complement or unsigned magnitude data inputs, labeled X and Y. The Most Significant Bits (MSBs), denoted  $X_{15}$  and  $Y_{15}$ , carry the sign information for the two's complement notation. The remaining bits are denoted  $X_{0}$  through  $X_{14}$  and  $Y_{0}$  through  $Y_{14}$  (with  $X_{0}$  and  $Y_{0}$  the Least Significant Bits). The input and output formats for fractional two's complement, fractional unsigned magnitude,

fractional mixed mode, integer two's complement, integer unsigned magnitude, and integer mixed mode notation are shown in Figures 1 through 6, respectively. The Y inputs are multiplexed with the LSP outputs, and hence can only be used when the TRIL control is in a HIGH state. This is true whether or not the LSP is also multiplexed out through the MSP output port.

| 1 |  |

|---|--|

| • |  |

| Name            | Function   | Value | J1 Package |

|-----------------|------------|-------|------------|

| x <sub>15</sub> | X Data MSB | TTL   | Pin 54     |

| X <sub>14</sub> |            | ΠL    | Pin 55     |

| x <sub>13</sub> |            | ΠL    | Pin 56     |

| X <sub>12</sub> |            | ΤΤL   | Pin 57     |

| x <sub>11</sub> |            | TTL   | Pin 58     |

| x <sub>10</sub> |            | TTL   | Pin 59     |

| X <sub>g</sub>  |            | TTL   | Pin 60     |

| x <sub>8</sub>  |            | TTL   | Pin 61     |

| x <sub>7</sub>  |            | TTL   | Pin 62     |

| x <sub>6</sub>  |            | TTL   | Pin 63     |

| x <sub>5</sub>  |            | TTL   | Pin 64     |

| x <sub>4</sub>  |            | TTL   | Pin 1      |

| x <sub>3</sub>  |            | TTL   | Pin 2      |

| x <sub>2</sub>  |            | TTL   | Pin 3      |

| x <sub>1</sub>  |            | TTL   | Pin 4      |

| x <sub>0</sub>  | X Data LSB | TTL   | Pin 5      |

MPY016K TRUE

#### Data Inputs (Cont.)

| Name            | Function   | Value | J1 Package |

|-----------------|------------|-------|------------|

| Y <sub>15</sub> | Y Data MSB | TTL   | Pin 24     |

| Y <sub>14</sub> |            | TTL ( | Pin 23     |

| Y <sub>13</sub> |            | TTL   | Pin 22     |

| Y <sub>12</sub> |            | TTL   | Pin 21     |

| Y <sub>11</sub> | }          | TTL   | Pin 20     |

| Y <sub>10</sub> |            | TTL ) | Pin 19     |

| Y9 Y9           |            | TTL   | Pin 18     |

| Y <sub>8</sub>  |            | TTL   | Pin 17     |

| Y <sub>7</sub>  |            | TTL   | Pin 16     |

| Y <sub>6</sub>  |            | TTL   | Pin 15     |

| Y <sub>5</sub>  |            | TTL   | Pin 14     |

| Y <sub>4</sub>  |            | TTL   | Pin 13     |

|                 |            | TTL   | Pin 12     |

| Y <sub>3</sub>  |            | TTL   | Pin 11     |

| Y <sub>2</sub>  |            | TTL   | Pin 10     |

| Y <sub>1</sub>  | V Date (50 | TTL   | Pin 9      |

| Y <sub>0</sub>  | Y Data LSB | FIL   |            |

#### **Data Outputs**

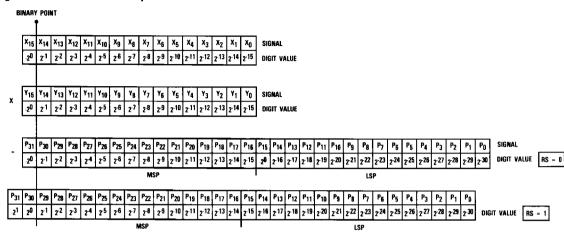

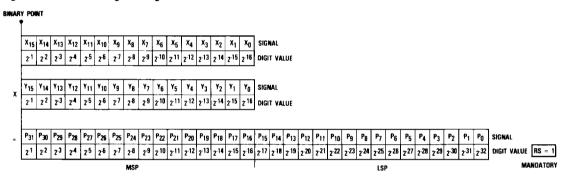

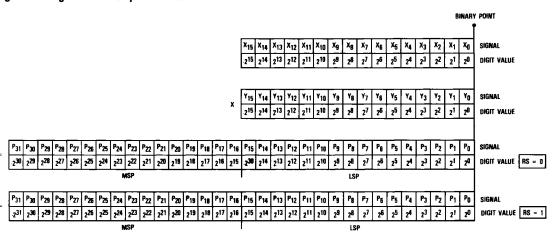

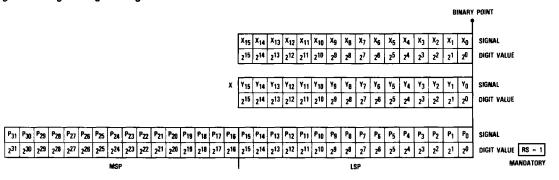

The MPY016K has a 32-bit two's complement or unsigned magnitude output which is the product of the two input data values. This output is divided into two 16-bit output words, the Most Significant Product (MSP) and Least Significant Product (LSP). The Most Significant Bit (MSB) of both the MSP and the LSP is the sign bit if fractional two's complement notation is used (TCX = TCY = 1, RS = 0). The input and output formats for fractional two's complement, fractional unsigned magnitude, fractional mixed mode, integer two's complement, integer unsigned magnitude, and integer mixed mode notation are shown in Figures 1 through 6, respectively.

If MSEL is LOW, the LSP output can be taken from the Y input pins only when TRIL is LOW. Care must be taken to enable these shared input lines only at the proper time. If MSEL is HIGH, the LSP output is made available at the MSP lines, as well as at the Y input pins. For an output from the MSP lines to be read, the TRIM control must be active.

RS is an output format control. A HIGH on RS deletes the sign bit from the LSP and shifts the MSP down one bit. This is mandatory for unsigned magnitude, mixed mode, or integer two's complement operation.

| Name            | Function    | Value | J1 Package |

|-----------------|-------------|-------|------------|

| P <sub>31</sub> | Product MSB | ΠL    | Pin 40     |

| P <sub>30</sub> |             | ΠL    | Pin 39     |

| P <sub>29</sub> |             | ΤΤL   | Pin 38     |

| P <sub>28</sub> |             | ΤΤL   | Pin 37     |

| P <sub>27</sub> |             | ΤΤL   | Pin 36     |

| P <sub>26</sub> |             | TTL   | Pin 35     |

| P <sub>25</sub> |             | TTL   | Pin 34     |

| P <sub>24</sub> |             | TTL   | Pin 33     |

| P <sub>23</sub> |             | ΤΤL   | Pin 32     |

| P <sub>22</sub> | İ           | TTL   | Pin 31     |

| P <sub>21</sub> |             | πι    | Pin 30     |

| P <sub>20</sub> |             | Πι    | Pin 29     |

| P <sub>19</sub> |             | ττι   | Pin 28     |

| P <sub>18</sub> |             | ττι   | Pin 27     |

| P <sub>17</sub> |             | TTL   | Pin 26     |

| P <sub>16</sub> |             | TTL   | Pin 25     |

#### Data Outputs (Cont.)

| Name            | Function    | Value | J1 Package    |

|-----------------|-------------|-------|---------------|

| -               |             |       | MUXED         |

|                 |             |       | Input/Ouput   |

| P <sub>15</sub> |             | TTL   | Pin 24/Pin 40 |

| P <sub>14</sub> |             | TTL   | Pin 23/Pin 39 |

| P <sub>13</sub> |             | TTL   | Pin 22/Pin 38 |

| P <sub>12</sub> |             | TTL   | Pin 21/Pin 37 |

| P <sub>11</sub> |             | TTL   | Pin 20/Pin 36 |

| P <sub>10</sub> |             | TTL   | Pin 19/Pin 35 |

| Pg              |             | TTL   | Pin 18/Pin 34 |

| P <sub>8</sub>  |             | TTL   | Pin 17/Pin 33 |

| P <sub>7</sub>  |             | TTL   | Pin 16/Pin 32 |

| P <sub>6</sub>  |             | πι    | Pin 15/Pin 31 |

| P <sub>5</sub>  |             | TTL   | Pin 14/Pin 30 |

| P <sub>4</sub>  |             | TTL   | Pin 13/Pin 29 |

| P <sub>3</sub>  |             | πι    | Pin 12/Pin 28 |

| P <sub>2</sub>  |             | πι    | Pin 11/Pin 27 |

| P <sub>1</sub>  |             | πι    | Pin 10/Pin 26 |

| P <sub>0</sub>  | Product LSB | πι    | Pin 9/Pin 25  |

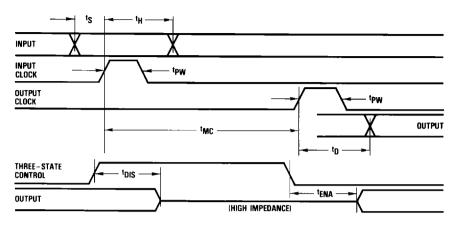

#### Clocks

The MPY016K has four clock lines, one for each input register and one for each product register. Data and two's complement instructions present at the inputs of these registers are loaded into the registers at the rising edge of the appropriate clock. The RND input is registered, clocked in at the rising edge of

the logical OR of both CLK X and CLK Y. Special attention to the clock signals is required if normally HIGH clock signals are used. Problems with loading this control signal can be avoided by the use of normally LOW clocks.

| Name  | Function           | Value | J1 Package |

|-------|--------------------|-------|------------|

| CLK X | Clock Input Data X | ΤΤL   | Pin 53     |

| CLK Y | Clock Input Data Y | ΠL    | Pin 8      |

| CLK L | Clock LSP Register | ΠL    | Pin 7      |

| CLK M | Clock MSP Register | TTL   | Pin 41     |

MPY016K 7787

#### **Controls**

The MPY016K has eight control lines.

FT

A control line which makes the output register

transparent if it is HIGH.

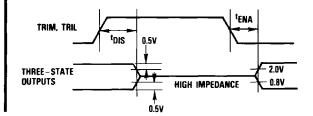

TRIM, TRIL

Three-state enable lines for the MSP and the LSP. The output driver is in the high-impedance state when TRIM or TRIL is HIGH, and enabled when the appropriate control is LOW.

RS

RS is an output format control. A HIGH level on RS deletes the sign bit from the LSP and shifts the MSP down one bit. This is mandatory for unsigned magnitude, mixed mode, and two's complement integer operations.

MSEL

MSEL is an output multiplex control. When MSEL is LOW, the MSP is available to the output three-state drivers at the MSP port, and the LSP is available to the output three-state drivers at the LSP/Y input port. When MSEL is HIGH, the LSP is available to both three-state drivers and the MSP is not available.

RND

When RND is HIGH, a one is added to the MSB of the LSP. Note that this bit depends on the state of the RS control. If RS is LOW when RND is HIGH, a one will be added to the  $2^{-16}$  bit (P<sub>14</sub>). If RS is HIGH when RND is HIGH, a one will be added to the  $2^{-15}$  bit (P<sub>15</sub>). In either case, the LSP output will reflect this addition when RND is HIGH. Note also that rounding always occurs in the positive direction; in some systems this may introduce a systematic bias.

TCX, TCY

Control how the device interprets data on the X and Y inputs. A HIGH on TCX or TCY makes the appropriate input a two's complement input, while a LOW makes the appropriate input a magnitude only input.

FT, RS, MSEL, TRIM, and TRIL are not registered. The TCX input is registered, and clocked in at the rising edge of the X clock signal, CLK X. The TCY input is also registered, and clocked in at the rising edge of the Y clock signal, CLK Y. The RND input is registered, and clocked in at the rising edge of the logical OR of both CLK X and CLK Y. Special attention is required if normally HIGH clock signals are used. Problems with loading of these control signals can be avoided by the use of normally LOW clocks.

| Name | Function                    | Value | J1 Package |

|------|-----------------------------|-------|------------|

| RND  | Round Control Bit           | TTL   | Pin 52     |

| TCX  | X Input Two's Complement    | TTL   | Pin 51     |

| TCY  | Y Input Two's Complement    | TTL   | Pin 50     |

| FT   | Output Register Feedthrough | ΤΤL   | Pin 44     |

| RS   | Output Register Shift       | TTL   | Pin 43     |

| MSEL | Output Select               | TTL   | Pin 45     |

| TRIM | MSP Three-State Control     | TTL   | Pin 42     |

| TRIL | LSP Three - State Control   | TTL   | Pin 6      |

Figure 1. Fractional Two's Complement Notation

Figure 2. Fractional Unsigned Magnitude Notation

Figure 3. Fractional Mixed Mode Notation

| BIR | IARY            | POH             | NT              |                 |                 |                 |                 |                    |                 |                 |                 |                 |                  |                 |                 |                  |                 |                  |                 |                 |                 |                 |       |      |      |                |      |      |                  |                |                |      |                    |

|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|-----------------|------------------|-----------------|------------------|-----------------|-----------------|-----------------|-----------------|-------|------|------|----------------|------|------|------------------|----------------|----------------|------|--------------------|

|     | 1               |                 |                 |                 |                 |                 |                 |                    |                 |                 |                 |                 |                  |                 |                 |                  |                 |                  |                 |                 |                 |                 |       |      |      |                |      |      |                  |                |                |      |                    |

| ſ   | X <sub>15</sub> | X <sub>14</sub> | X <sub>13</sub> | X <sub>12</sub> | X <sub>11</sub> | X <sub>10</sub> | Χg              | X <sub>8</sub>     | X <sub>7</sub>  | X <sub>6</sub>  | X <sub>5</sub>  | X4              | Х3               | X <sub>2</sub>  | X <sub>1</sub>  | ΧO               | SIG             | NAL              | (TWO            | s co            | MPLE            | MENT            | n)    |      |      |                |      |      |                  |                |                |      |                    |

| Ī   | 20              | 21              | 2.2             | 2-3             | 24              | 2.5             | 2-6             | 2.7                | 2-8             | 2.9             | 2-10            | 2-11            | 2-12             | 2.13            | 2-14            | 2 <sup>-15</sup> | DIG             | IT V             | LUE             |                 |                 |                 |       |      |      |                |      |      |                  |                |                |      |                    |

|     | x               | Y <sub>15</sub> | Y <sub>14</sub> | Y <sub>13</sub> | Y <sub>12</sub> |                 | Y <sub>10</sub> | Yg 2 <sup>-7</sup> | Y <sub>8</sub>  | Y <sub>7</sub>  | Y <sub>6</sub>  | Y <sub>5</sub>  | Y <sub>4</sub>   | Y <sub>3</sub>  | Y <sub>2</sub>  | ¥ <sub>1</sub>   | Y <sub>0</sub>  |                  | INAL<br>SIT V   |                 | GNED            | MAG             | INITU | DE)  |      |                |      |      |                  |                |                |      |                    |

| _ [ | P <sub>31</sub> | P30             | P <sub>29</sub> | P <sub>28</sub> | P <sub>27</sub> | P <sub>26</sub> | P <sub>25</sub> | P <sub>24</sub>    | P <sub>23</sub> | P <sub>22</sub> | P <sub>21</sub> | P <sub>20</sub> | P <sub>19</sub>  | P <sub>18</sub> | P <sub>17</sub> | P <sub>18</sub>  | P <sub>15</sub> | P <sub>14</sub>  | P <sub>13</sub> | P <sub>12</sub> | P <sub>11</sub> | P <sub>10</sub> | Pg    | P8   | P7   | P <sub>6</sub> | ₽5   | P4   | P <sub>3</sub>   | P <sub>2</sub> | P <sub>1</sub> | Po   | SIGNAL             |

|     | ·2 <sup>0</sup> | 2-1             | 2.2             | 2.3             | 2-4             | 2.5             | 2.6             | 2.7                | 2.8             | 2.9             | 2-10            | 2-11            | 2 <sup>.12</sup> | 2-13            | 2-14            | 2 <sup>-15</sup> | 2-16            | 2 <sup>-17</sup> | 2-18            | 2-19            | 2-20            | 2-21            | 2.22  | 2.23 | 2.24 | 2.25           | 2.26 | 2-27 | 2 <sup>-28</sup> | 2:29           | 2:30           | 2.31 | DIGIT VALUE RS = 1 |

|     | MSP             |                 |                 |                 |                 |                 |                 |                    |                 |                 |                 | LSP             |                  |                 |                 |                  |                 |                  |                 |                 | MANDATORY       |                 |       |      |      |                |      |      |                  |                |                |      |                    |

Figure 4. Integer Two's Complement Notation

Figure 5. Integer Unsigned Magnitude Notation

Figure 6. Integer Mixed Mode Notation

|   |      |                 |                 |                 |                 |                 |                 |                 |                 |     |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |    |                |    |                |                |                |                |                | В              | NARY           | Y POINT                     |

|---|------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----|----------------|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------------|

|   |      |                 |                 |                 |                 |                 |                 |                 |                 |     |                 |                 |                 |                 |                 |                 | X <sub>15</sub> | X <sub>14</sub> | X <sub>13</sub> | X <sub>12</sub> | X <sub>11</sub> | X <sub>10</sub> | Χg | ΧB             | X7 | X <sub>6</sub> | X <sub>5</sub> | X4             | хэ             | x <sub>2</sub> | X <sub>1</sub> | x <sub>0</sub> | SIGNAL (TWO'S COMPLEMENT)   |

|   |      |                 |                 |                 |                 |                 |                 |                 |                 |     |                 |                 |                 |                 |                 |                 | 215             | 214             | 213             | 212             | 211             | 210             | 29 | 28             | 27 | 26             | 25             | 24             | 23             | 22             | 21             | 20             | DIGIT VALUE                 |

|   |      |                 |                 |                 |                 |                 |                 |                 |                 |     |                 |                 |                 |                 |                 | x               | Y 15            | Y <sub>14</sub> | Y <sub>13</sub> | Y <sub>12</sub> | Y <sub>11</sub> | Y <sub>10</sub> | Yg | Υg             | ¥7 | Y <sub>6</sub> | Y <sub>5</sub> | Y4             | <b>Y</b> 3     | Y2             | Υ1             | Yo             | SIGNAL (UNSIGNED MAGNITUDE) |

|   |      |                 |                 |                 |                 |                 |                 |                 |                 |     |                 |                 |                 |                 |                 | 1               | 2 <sup>15</sup> | 214             | 213             | 212             | 211             | 210             | 29 | 28             | 27 | 26             | 25             | 24             | 23             | 22             | 21             | 20             | DIGIT VALUE                 |

| 2 | P31  | P <sub>30</sub> | P <sub>29</sub> | P <sub>28</sub> | P <sub>27</sub> | P <sub>26</sub> | P <sub>25</sub> | P <sub>24</sub> | P <sub>23</sub> | P22 | P <sub>21</sub> | P <sub>20</sub> | P <sub>19</sub> | P <sub>18</sub> | P <sub>17</sub> | P <sub>15</sub> | P <sub>15</sub> | P <sub>14</sub> | P <sub>13</sub> | P <sub>12</sub> | P <sub>11</sub> | P10             | Pg | P <sub>8</sub> | P7 | Pe             | P <sub>5</sub> | P <sub>4</sub> | P <sub>3</sub> | P <sub>2</sub> | P <sub>1</sub> | Po             | Signal                      |

| - | .231 |                 | 229             | _               | -               |                 |                 | _               | -               | 222 |                 | ₩               |                 | -               | _               |                 | —               | -               | -               | -               | -               | -               |    | 28             | 27 | <b>2</b> 6     | 25             | 24             | 23             | 22             | 21             | 20             | DIGIT VALUE RS = 1          |

|   |      |                 |                 |                 |                 |                 |                 | MSP             | ,               |     |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |    | LS             | P  |                |                |                |                |                |                |                | MANDATORY                   |

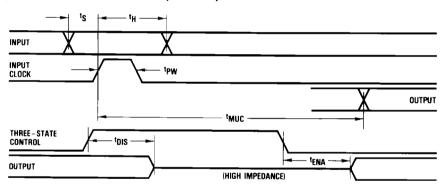

Figure 7. Timing Diagram, Non-Multiplexed Output

Figure 8. Timing Diagram, Unclocked Mode, Non-Multiplexed Output

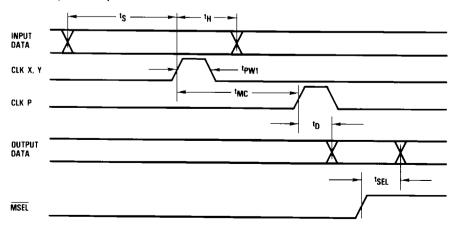

Figure 9. Timing Diagram, Multiplexed Output

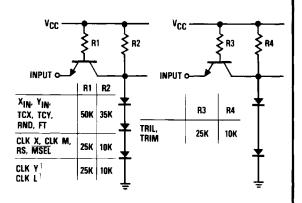

Figure 10. Equivalent Input Circuit

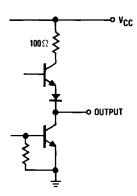

Figure 11. Equivalent Output Circuit

Note 1. CLK Y and CLK L each drive two equivalent inputs.

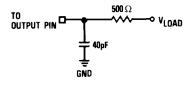

Figure 12. Test Load

Figure 13. Transition Levels For Three-State Measurements

MPY016K TRV

# **Application Notes**

#### Mixed Mode Multiplication

There are several applications in which mixed mode multiplication may be advantageous. For example, inputs to a digital signal processor are often generated as unsigned magnitude numbers (e.g., data from an analog—to—digital converter). These numbers are effectively all positive values. In contrast, filter coefficients must often be negative. As a result, either the data must be converted to two's complement

notation (which requires an additional bit), or the multiplier must be capable of mixed mode operation. The MPY016K provides this capability by independently specifying the mode of the multiplicand (X) and the multiplier (Y) on the TCX and TCY pins. No additional circuitry is required and the resulting product is in two's complement notation.

#### Multiplication By A Constant

Multiplication by a constant requires that the constant be loaded into the desired input register, and that the desired register not be loaded again until a new constant is desired.

The multiply cycle then consists of loading new data and strobing the output register.

#### Selection Of Numeric Format

Essentially, the difference between integer, mixed, and fractional notation in system design is only conceptual. For example, the MPY016K does not differentiate between this operation:

$6 \times 2 = 12$

and this operation:

$(6/8) \times (2/8) = 12/64.$

The difference lies in constant scale factors (in this case, a factor of 8 in the multiplier and multiplicand and a factor of 64 in the product). However, these scale factors do have

implications for hardware design. Because common good design practice assigns a fixed value to any given line land input and output signals often share the same line), the scale factors determine the connection of the output pins of any multiplier in a system. As a result, only two choices are normally made: integer and fractional notation. If integer notation is used, the Least Significant Bits of the multiplier, multiplicand, and product all have the same value. If fractional notation is used, the Most Significant Bits of the multiplier, multiplicand, and product all have the same value. These formats are illustrated in detail in Figures 1 through 6.

#### Register Shift (RS) Control

In two's complement notation, the acceptable range of values for a given word size is not the same for positive and negative numbers. The largest negative number is one LSB larger than the largest positive number. This is true for either fractional or integer notation. A problem can arise when the largest representable negative number is multiplied by itself. This should give a positive number of the same magnitude. However, the largest representable positive number is one LSB less than this value. As a result, this product cannot be correctly represented without using one additional output bit.

The MPY016K has a Register Shift (RS) control that permits shifting of the result to provide a correct answer for every two's complement multiplication. When RS is active, the value of all bits in the MSP is doubled (i.e. shifted left one position), which provides the capability to represent the largest possible product. The MSB of the Least Significant Product is changed from a duplicate of the sign bit to the necessary bit to fill in the output word. The effects of this control are illustrated in Figures 1 and 4. Note that for unsigned magnitude operation, the RS control must be HIGH.

Absolute maximum ratings (beyond which the device will be damaged) 1

| Supply Voltag | e0.5 to +7.0V                                                  |

|---------------|----------------------------------------------------------------|

| Input         |                                                                |

|               | Applied voltage0.5 to +5.5V <sup>2</sup>                       |

|               | Forced current                                                 |

| Output        |                                                                |

|               | Applied voltage0.5 to +5.5V <sup>2</sup>                       |

|               | Forced current                                                 |

|               | Short-circuit duration (single output in high state to ground) |

| Temperature   |                                                                |

|               | Operating, case                                                |

|               | junction                                                       |

|               | Lead, soldering (10 seconds)                                   |

|               | Storage                                                        |

Notes:

- Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range, and measured with respect to GND.

- 3. Forcing voltage must be limited to specified range

- 4. Current is specified as conventional current flowing into the device.

#### **Operating conditions**

|                  |                                | Temperature Range |          |      |      |          |       |       |  |  |  |  |  |  |

|------------------|--------------------------------|-------------------|----------|------|------|----------|-------|-------|--|--|--|--|--|--|

|                  |                                |                   | Standard |      |      | Extended |       |       |  |  |  |  |  |  |

| Paran            | neter                          | Min               | Nom      | Max  | Min  | Nom      | Max   | Units |  |  |  |  |  |  |

| v <sub>cc</sub>  | Supply Voltage                 | 4.75              | 5.0      | 5.25 | 4.5  | 5.0      | 5.5   | ٧     |  |  |  |  |  |  |

| t <sub>PWL</sub> | Clock Pulse Width, LOW         | 15                |          |      | 22   |          |       | ns    |  |  |  |  |  |  |

| <sup>t</sup> PWH | Clock Pulse Width, HIGH        | 15                |          |      | 22   |          |       | ns    |  |  |  |  |  |  |

| ls               | Input Setup Time (MPY016K)     | 20                |          |      | 25   |          |       | ns    |  |  |  |  |  |  |

|                  | (MPY016K - 1)                  | 20                |          |      | 20   |          |       | ns    |  |  |  |  |  |  |

| t <sub>H</sub>   | Input Hold Time                | 0                 |          |      | 2    |          |       | ns    |  |  |  |  |  |  |

| /IL              | Input Voltage, Logic LOW       |                   |          | 0.8  |      |          | 0.8   | ٧     |  |  |  |  |  |  |

| VIH              | Input Voltage, Logic HIGH      | 2.0               |          |      | 2.0  |          |       | V     |  |  |  |  |  |  |

| 0L               | Output Current, Logic LOW      |                   |          | 4.0  |      |          | 4.0   | mA    |  |  |  |  |  |  |

| l <sub>ОН</sub>  | Output Current, Logic HIGH     |                   |          | -400 |      |          | -400  | μΑ    |  |  |  |  |  |  |

| TA               | Ambient Temperature, Still Air | 0                 |          | 70   |      |          |       | °C    |  |  |  |  |  |  |

| T <sub>C</sub>   | Case Temperature               |                   |          |      | - 55 |          | + 125 | °C    |  |  |  |  |  |  |

27

# Electrical characteristics within specified operating conditions

|                  |                                          |                                                                                                        | Temperature Range |      |          |      |       |

|------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|------|----------|------|-------|

|                  |                                          |                                                                                                        | Standard          |      | Extended |      | ĺ     |

| Parar            | meter                                    | Test Conditions                                                                                        | Min               | Max  | Min      | Max  | Units |

| Icc              | Supply Current                           | V <sub>CC</sub> - MAX, Static <sup>1</sup>                                                             |                   |      |          |      |       |

|                  |                                          | TA - 0°C to 70°C                                                                                       |                   | 875  |          |      | mA    |

|                  |                                          | T <sub>A</sub> > 25°C <sup>2</sup>                                                                     |                   | 860  |          |      | mA    |

|                  |                                          | T <sub>A</sub> - 0°C to 70°C<br>T <sub>A</sub> > 25°C <sup>2</sup><br>T <sub>C</sub> = -55°C to +125°C |                   |      | -        | 1050 | mΑ    |

|                  |                                          | T <sub>C</sub> > 35°C                                                                                  |                   |      |          | 960  | mA    |

|                  |                                          | V <sub>CC</sub> - 5.0V                                                                                 |                   |      |          |      |       |

|                  |                                          | T <sub>A</sub> > 25°C                                                                                  |                   | 840  |          |      | mA    |

|                  |                                          | T <sub>C</sub> > 35°C                                                                                  |                   |      |          | 920  | mA    |

| l <sub>IL</sub>  | Input Current, Logic LOW                 | V <sub>CC</sub> - MAX, V <sub>I</sub> - 0.4V                                                           |                   | ĺ    |          |      |       |

|                  |                                          | X <sub>IN</sub> , Y <sub>IN</sub> , TCY, TCX, FT, RND                                                  |                   | -0.2 |          | -0.2 | mA    |

|                  |                                          | CLK Y, CLK L                                                                                           |                   | -1.2 | -        | -1.2 | mA    |

|                  |                                          | CLK X, CLK M, MSEL, TRIM, TRIL, RS                                                                     |                   | -0.6 |          | -0.6 | mΑ    |

| lн               | Input Current, Logic HIGH                | V <sub>CC</sub> - MAX, V <sub>I</sub> - 2.4V                                                           |                   |      |          |      |       |

|                  |                                          | X <sub>IN</sub> , Y <sub>IN</sub> , TCY, TCX, FT, RND                                                  |                   | 50   |          | 50   | μА    |

|                  |                                          | CLK Y, CLK L                                                                                           |                   | 100  |          | 100  | μΑ    |

|                  |                                          | CLK X, CLK M, MSEL, TRIM, TRIL, RS                                                                     |                   | 50   |          | 50   | μA    |

| <u> </u>         | Input Current, Max Input Voltage         | V <sub>CC</sub> - MAX, V <sub>I</sub> - 5.5V                                                           |                   | 1.0  |          | 1.0  | mA    |

| V <sub>OL</sub>  | Output Voltage, Logic LOW                | V <sub>CC</sub> - MAX, I <sub>DL</sub> - MAX                                                           |                   | 0.5  |          | 0.5  | ٧     |

| VOH              | Output Voltage, Logic HIGH               | V <sub>CC</sub> - MIN, I <sub>OH</sub> - MAX                                                           | 2.4               |      | 2.4      |      | ٧     |

| l <sub>OZL</sub> | Hi~Z Output Leakage Current, Output LOW  | V <sub>CC</sub> - MAX, V <sub>I</sub> - 0.4V                                                           |                   |      |          |      |       |

|                  |                                          | Non-Shared Pins                                                                                        |                   | -40  |          | -50  | μA    |

|                  |                                          | Shared Pins                                                                                            |                   | -200 |          | -200 | μΑ    |

| lozh             | Hi-Z Output Leakage Current, Output HIGH | V <sub>CC</sub> - MAX, V <sub>I</sub> - 2.4V                                                           |                   |      |          |      |       |

|                  |                                          | Non - Shared Pins                                                                                      |                   | 40   |          | 50   | μA    |

|                  |                                          | Shared Pins                                                                                            |                   | 50   |          | 50   | μA    |

| los              | Short Circuit Output Current             | V <sub>CC</sub> - MAX, One pin to ground,                                                              | -4                | -50  | -4       | -50  | mA    |

|                  |                                          | one second duration, output HIGH.                                                                      |                   |      |          |      |       |

| Cį               | Input Capacitance                        | T <sub>A</sub> - 25°C, F - 1MHz                                                                        |                   | 10   |          | 10   | pF    |

| $\overline{c_0}$ | Output Capacitance                       | T <sub>A</sub> = 25°C, F = 1MHz                                                                        |                   | 10   |          | 10   | pF    |

Notes:

<sup>1.</sup> Worst case, all inputs and outputs LOW.

<sup>2.</sup> Part has a negative temperature coefficient, i.e., power consumption falls as temperature increases.

## Switching characteristics within specified operating conditions 1

|                  |                                  | Temperature Range                                          |                 |     |        | ge       |       |  |

|------------------|----------------------------------|------------------------------------------------------------|-----------------|-----|--------|----------|-------|--|

|                  |                                  |                                                            | Standard Extend |     | nded   | ed       |       |  |

| Parameter        |                                  | Test Conditions                                            | Min Ma          | Max | ax Min | Max      | Units |  |

| <sup>t</sup> MC  | Multiply Time, Clocked           | V <sub>CC</sub> = Min,                                     |                 |     |        |          |       |  |

|                  |                                  | MPY016K                                                    |                 | 45_ |        | 50       | ns    |  |

|                  |                                  | MPY016K-1                                                  |                 | 40  |        | 45       | пѕ    |  |

| tMUC             | Multiply Time, Unclocked         | V <sub>CC</sub> = Min                                      |                 |     |        |          |       |  |

|                  |                                  | MPY016K                                                    |                 | 75  |        | 85       | ns    |  |

|                  |                                  | MPY016K-1                                                  |                 | 70  |        | 75       | ns    |  |

| t <sub>D</sub>   | Output Delay                     | V <sub>CC</sub> = Min, Test Load: V <sub>LOAD</sub> = 2.2V |                 |     |        |          |       |  |

| -                |                                  | MPY016K                                                    |                 | 30  |        | 35       | ns    |  |

|                  |                                  | MPY016K-1                                                  |                 | 30  |        | 30       | ns    |  |

| t <sub>SEL</sub> | Output Multiplex Select Delay    | V <sub>CC</sub> = Min, Test Load: V <sub>LOAD</sub> = 2.2V |                 | 20  |        | 25       | ns    |  |

| tENA             | Three-State Output Enable Delay  | V <sub>CC</sub> = Min, Test Load: V <sub>LOAD</sub> = 1.8V |                 | 30  |        | 35       | ns    |  |

| tDIS             | Three-State Output Disable Delay | V <sub>CC</sub> = Min,                                     |                 | 30  |        | 35       | ns    |  |

| - /-             |                                  | Test Load: VLOAD = 2.6V (tDISO) 2                          |                 |     |        |          |       |  |

|                  |                                  | V <sub>LOAD</sub> = 0.0V (t <sub>DIS1</sub> ) <sup>2</sup> |                 |     |        | <u> </u> |       |  |

Notes: 1

#### **Ordering Information**

| Product<br>Number | Temperature Range                                | Screening        | Package            | Package<br>Marking |

|-------------------|--------------------------------------------------|------------------|--------------------|--------------------|

| MPY016KJ1C        | $STD - T_{\Delta} = 0^{\circ}C$ to $70^{\circ}C$ | Commercial       | 64 Pin Ceramic DIP | 016KJ1C            |

| MPY016KJ1C1       | $STD - T_{\Delta} = 0^{\circ}C$ to $70^{\circ}C$ | Commercial       | 64 Pin Ceramic DIP | 016KJ1C1           |

| MPY016KJ1A        | EXT – T <sub>C</sub> = – 55°C to 125°C           | High Reliability | 64 Pin Ceramic DIP | 016KJ1A            |

| MPY016KJ1A1       | EXT – T <sub>C</sub> = – 55°C to 125°C           | High Reliability | 64 Pin Ceramic DIP | 016KJ1A1           |

All parameters contained in this specification are guaranteed by design, characterization, sample testing or 100% testing as appropriate. TRW reserves the right to change products and specifications without notice. This information does not convey any license under patent rights of TRW Inc. or others.

Life Support Policy — TRW LSI Products Inc. components are not designed for use in life support applications, wherein a failure or malfunction of the component can reasonably be expected to result in personal injury. The user of TRW LSI Products Inc. components in life support applications assumes all risk of such use and indemnifies TRW LSI Products Inc. against all damages.

<sup>1</sup> All transitions are measured at a 1.5V level except for  $t_{DIS}$  and  $t_{ENA}$ , which are shown in Figure 13.

to three-state.

to ISO denotes the transition from logical 1 to three-state.

to ISO denotes the transition from logical 0 to three-state.