### **FEATURES**

- DUAL POSITIVE-LOGIC NAND TTL-TO-MOS DRIVER

- VERSATILE INTERFACE CIRCUIT FOR USE BETWEEN TTL AND HIGH-CURRENT, HIGH-VOLTAGE SYSTEMS

- CAPABLE OF DRIVING HIGH-CAPACITANCE LOADS

- . COMPATIBLE WITH MANY POPULAR MOS RAMS

- ◆ V<sub>CC2</sub> SUPPLY VOLTAGE VARIABLE OVER WIDE RANGE TO 24 **VÕLTS MAXIMUM**

- TTL AND DTL COMPATIBLE DIODE-CLAMPED INPUTS

- OPERATES FROM STANDARD BIPOLAR AND MOS SUPPLY **VOLTAGES**

- HIGH-SPEED SWITCHING

- TRANSIENT OVERDRIVE MINIMIZES POWER DISSIPATION

- . LOW STANDBY POWER DISSIPATION

## **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage range of VCC1 (Note 1) Supply voltage range of VCC2 Input voltage Inter-input voltage (Note 2) Continuous total dissipation at (or below) 25°C free-air temperature (Note 3): | -0.5V to 7V<br>-0.5V to 25V<br>5.5V<br>5.5V       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| F package V package Operating free-air terperature range Storage temperature range                                                                                                           | 1300mW<br>1000mW<br>0°C to 70°C<br>–65°C to 150°C |

| Lead temperature 1/16 inch<br>from case for 60 seconds: F package<br>Lead temperature 1/16 inch                                                                                              | 300°C                                             |

| from case for 10 seconds: V package                                                                                                                                                          | 260°C                                             |

- NOTES:

1. Voltage values are with respect to network ground terminal.

2. This rating applies between the A input of either driver and the common E input.

- 3. For operation above 25 C free-air temperature, refer to Dissipation Derating Curve,

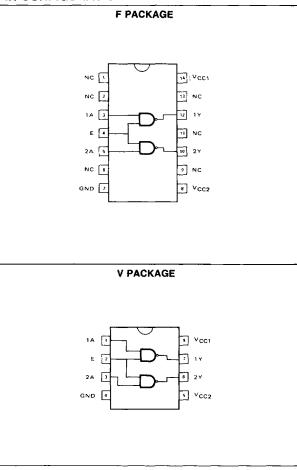

# **PIN CONFIGURATION**

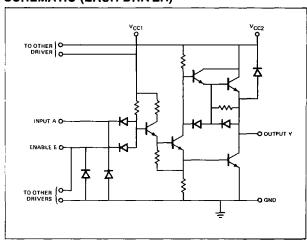

# SCHEMATIC (EACH DRIVER)

# SWITCHING CHARACTERISTICS, $v_{CC1}$ = 5V, $v_{CC2}$ = 20V, TA = 25°C

|                                | DADAMETED                                                                                                                                                                                                                                                       | TEST COMPLETIONS                                                               | LIMITS   |                                  |                                  | UNIT                       |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|----------------------------------|----------------------------------|----------------------------|

| PARAMETER                      |                                                                                                                                                                                                                                                                 | TEST CONDITIONS                                                                | MIN      | TYP                              | MAX                              | UNIT                       |

| tDLH tDHL tTLH tTHL t PLH tPHL | Delay time, low-to-high-level output Delay time, high-to-low-level output Transition time, low-to-high-level output Transition time, high-to-low-level output Propagation delay time, low-to-high-level output Propagation delay time, high-to-low-level output | $C_L = 390 pF$ , $R_D = 10 \Omega$<br>See Figure 1, Unused gate input grounded | 10<br>10 | 11<br>10<br>25<br>21<br>36<br>31 | 20<br>18<br>40<br>35<br>55<br>47 | ns<br>ns<br>ns<br>ns<br>ns |

# PARAMETER MEASUREMENT INFORMATION

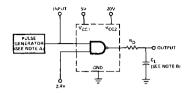

#### **TEST CIRCUIT**

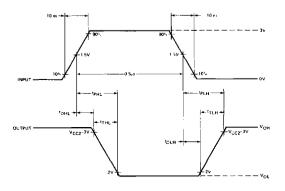

# VOLTAGE WAVEFORM

- NOTES: A. THE PULSE GENERATOR HAS THE FOLLOWING CHARACTERISTICS: PRR  $\,\pm\,$  1MHz.  $Z_{OUT} < 50\Omega$

- B. CL INCLUDES PROBE AND JIG CAPACITANCE

FIGURE 1—SWITCHING TIMES, EACH DRIVER

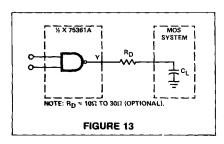

#### **DESIGN PRECAUTIONS** - USE OF DAMPING RESISTOR TO REDUCE OR ELIMINATE OUTPUT TRANSIENT OVER-SHOOT IN CERTAIN 75361A APPLICATIONS

The fast switching speeds of this device may produce undesirable output transient overshoot because of load or wiring inductance. A small series damping resistor may be used to reduce or eliminate this output transient overshoot. The optimum value of the damping resistor to use depends on the specific load characteristics and switching speed. A typical value would be between  $10\Omega$  and  $30\Omega$ . See Figure 13.

#### POWER DISSIPATION PRECAUTIONS

Significant power may be dissipated in the 75361A driver when charging and discharging high-capacitance loads over a wide voltage range at high frequencies. Figure 5 shows the power dissipated in a typical 75361A as a function of load capacitance and frequency. Average power dissipated by this driver can be broken into three components:

$$PT(AV) = PDC(AV) + PC(AV) + PS(AV)$$

where PDC(AV) is the steady-state power dissipation with the output high or low, PC(AV) is the power level during charging or discharging of the load capacitance, and  $P_{S(AV)}$  is the power dissipation during switching between the low and high levels. None of these include energy transferred to the load and all are averaged over a full cycle.

The power components per driver channel are:

PDC(AV) =

$$\frac{PL \frac{t}{L} + PH \frac{t}{H}}{T}$$

PC(AV) =

$$\frac{PL \frac{t}{L} + PH \frac{t}{H}}{T}$$

PS(AV) =

$$\frac{PLH \frac{t}{L}H + PHL \frac{t}{H}L}{T}$$

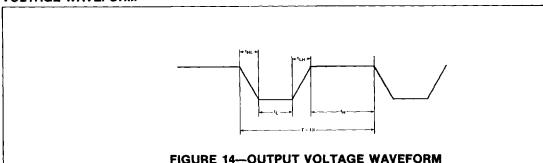

where the times are as defined in Figure 14.

PL, PH, PLH, and PHL are the respective instantaneous levels of power dissipation and C is load capacitance.

The 75361A is so designed that PS is a negligible portion of PT in most applications. Except at very high frequencies,  $t_L+t_H\gg t_{LH}+t_{HL}$  so that Ps can be neglected. Figure 5 for no load demonstrates this point. The power dissipation contributions from both channels are then added together to obtain total device power.

The following example illustrates this power calculation technique. Assume both channels are operating identically with C = 200pF, f = 2MHz, VCC1 = 5V, VCC2 = 20V, and duty cycle = 60% outputs high (th'T = 0.6). Also, assume VOH = 19.3V, VOL = 0.1V, PS is negligible, and that the current from VCC2 is negligible when the output is high.

On a per-channel basis using data sheet values:

$$PDC(AV) = \left[ (5V) \left( \frac{2mA}{2} \right) + (20V) \left( \frac{OmA}{2} \right) \right] (0.6) + \left[ (5V) \left( \frac{16mA}{2} \right) + (20V) \left( \frac{7mA}{2} \right) \right] (0.4)$$

PDC(AV) = 47mW per channel

PC(AV) ≈ (200pF) (19.2V)² (2MHz) PC(AV) ≈ 148mW per channel.

For the total device dissipation of the two channels:

$P_{T(AV)} \approx 2 (47 + 148)$

P<sub>T(AV)</sub> ≈ 390mW typical for total package.

### **VOLTAGE WAVEFORM**