SLWS087B - JUNE 1999 - REVISED MARCH 2000

- Complete Discrete Multitone (DMT)-Based Asymmetric Digital Subscriber Line (ADSL) Coder/Decoder (CODEC) Solution

- Complies With ANSI T1.413 Issue II and ITU G.992.1

- Supports up to 8 MBPS Downstream and 800 KBPS Upstream Duplex

- Integrated 14-Bit Converters for Transmitter/Echo-Canceller/Receiver (TX/EC/RX)

- Integrated 12-Bit DAC for VCXO Control

- Integrated TX/EC/RX Channel Filters

- Integrated TX/EC/RX Attenuation/Gain

- Integrated Voltage Reference

- High-Speed Parallel Interface

- 16-bit 2s Complement Data Format

- Selectable 2.2 MSPS or 4.4 MSPS Parallel Data Transfer Rate

- Serial Configuration Port

- Eight General-Purpose Output Pins

- Single 3.3-V Supply

- Hardware/Software Power Down

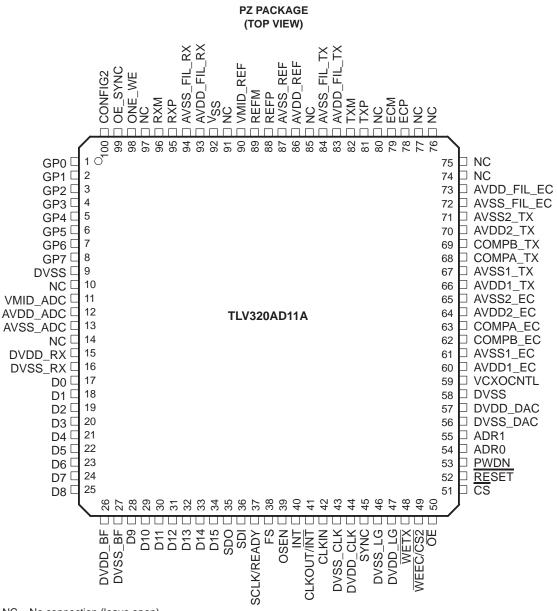

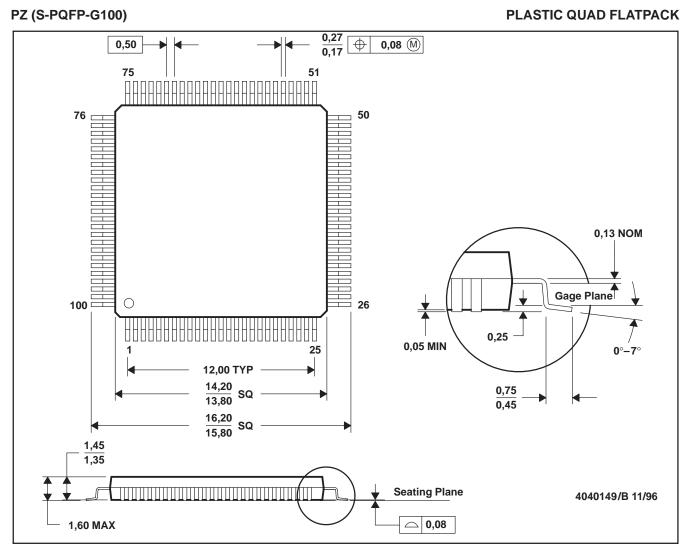

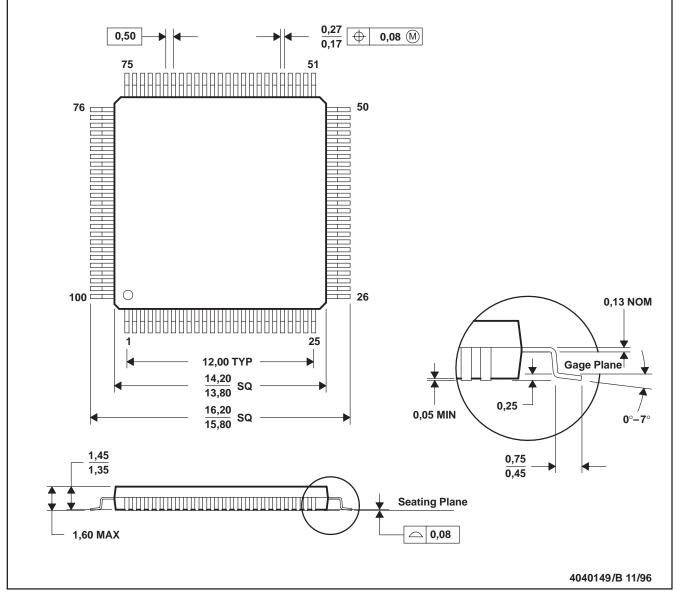

- 100-Pin PQFP (PZ) Package

- –40°C to 85°C Operation

## description

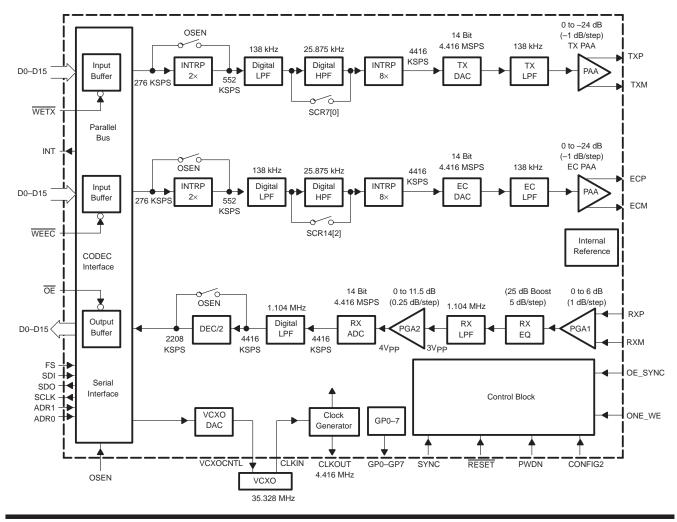

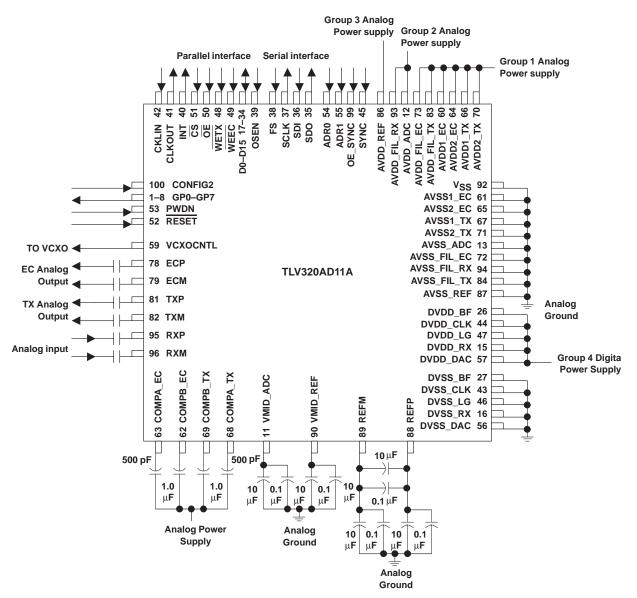

The TLV320AD11A is a high-speed codec for remote terminal-side (RT) modems that support the ANSI T1.413 [Issue 2 discrete multi-tone (DMT) asymmetric digital subscriber line (ADSL) access] and ITU G.992.1 standards. It is a low-power device that includes five major functional blocks: transmitter, receiver, clock, reference, and host interface. It is designed to work with the Texas Instruments TLV320AD12 central office-side (CO) codec.

The device's transmit channel consists of the following functional blocks: 138 kHz digital low-pass filter, bypassable 25.875 kHz digital high-pass filter, 14-bit high speed DAC, 138 kHz analog low-pass filter, transmit attenuator, and an echo cancellation channel. The receiver channel consists of two programmable-gain amplifiers, a frequency equalizer, a 1.104-MHz low-pass analog filter, a 14-bit high speed ADC, and a 1.104-MHz low-pass digital filter. The clock circuit divides a 35.328-MHz frequency from an external VCXO down to the necessary frequencies used throughout the device. The frequency of the external VCXO is controlled by a 12-bit onboard voltage output DAC. An onboard reference circuit generates a 1.5-V reference for the converters.

The device has a parallel port for data transfer and a serial port for control. The parallel port is 16 bits wide and is reserved for moving data between the codec and a DSP such as the Texas Instruments TMS320C6XX. Configuration is done via a serial port. The device can be powered down via a dedicated pin, or through software control, to reduce heat dissipation. Additionally, there is a general-purpose (GP) port consisting of eight output terminals for control of external circuitry.

The TLV320AD11A codec is available in a 100-pin PZ PQFP package and is characterized for operation in the temperature range of –40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2000, Texas Instruments Incorporated

SLWS087B - JUNE 1999 - REVISED MARCH 2000

NC - No connection (leave open)

SLWS087B - JUNE 1999 - REVISED MARCH 2000

## **Terminal Functions**

| IAL                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NO.                                                                                                      | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 54<br>55                                                                                                 | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | Serial port chip ID address bits, ADR0 is the least significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 60                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | EC channel analog power supply #1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 64                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | EC channel analog power supply #2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 66                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | TX channel analog power supply #1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 70                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                | TX channel analog power supply #2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 12                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                | Receive channel analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 73                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                | EC channel filter analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 93                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | Receive channel filter analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 83                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transmit channel filter analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 86                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reference analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 61                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | EC channel analog ground # 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 65                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | EC channel analog ground #2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 67                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | TX channel analog ground #1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 71                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | TX channel analog ground #2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 13                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | Receive channel analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 72                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | EC channel filter analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 94                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | Receive channel filter analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 84                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transmit channel filter analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 87                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reference analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 42                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35.328 MHz VCXO clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 41                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                | If CONFIG2 (pin 100) is low, this pin is 4.416 MHz clock output. If CONFIG2 is high, this pin functions as INT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 63                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                | EC channel cap input A. Add 500 pF X7R ceramic capacitor to AVDD1_EC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 62                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                | EC channel cap input B. Add 1 μF X7R ceramic capacitor to AVDD1_EC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 68                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                | TX channel decoupling cap input A. Add 500 pF ceramic capacitor to AVDD1_TX.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 69                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                | TX channel decoupling cap input B. Add 1 μF ceramic capacitor to AVDD1_TX.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

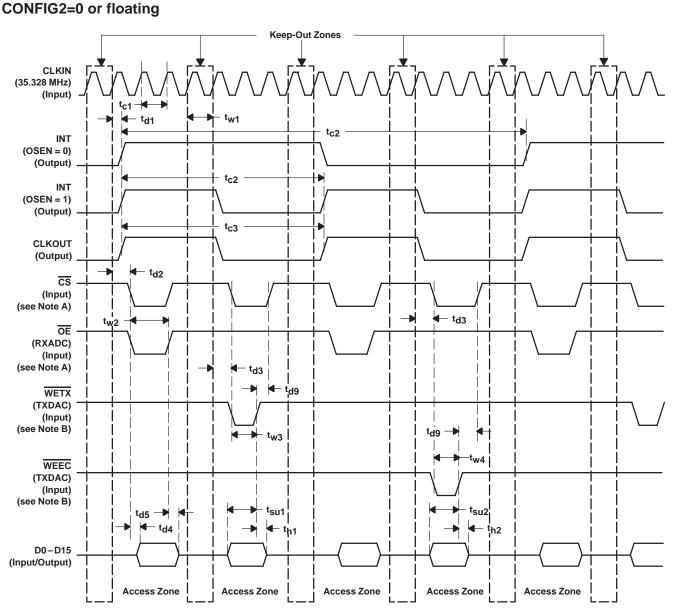

| 100                                                                                                      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O configuration input pin. A high on this pin redefines the function of pins 37 and 41. The default state of this pin is low. Refer to Figure 3 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 51                                                                                                       | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                | Parallel port chip select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 34 (MSB)<br>33<br>32<br>31<br>30<br>29<br>28<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17 (LSP) | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                              | Parallel port data bits D0=LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                                                                                                          | 54         55         60         64         66         70         12         73         93         83         86         61         65         67         71         13         72         94         84         87         42         41         63         62         68         69         100         51         33         32         31         30         29         28         25         24         23         21         20         19 | NO.         I/O           54         1           60         1           64         1           66         1           70         1           70         1           73         1           93         1           83         1           65         1           61         1           65         1           67         1           71         1           65         1           71         1           72         1           94         1           84         1           84         1           84         1           63         0           64         0           63         0           64         0           63         0           64         0           63         0           64         1           33         2           31         1           33         1           34         1           94         1 |  |  |  |  |  |

SLWS087B - JUNE 1999 - REVISED MARCH 2000

## **Terminal Functions(Continued)**

| TERMI      | NAL                        | I/O | DESCRIPTION                                                                                                                                          |  |  |  |  |  |

|------------|----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME       | NO.                        |     |                                                                                                                                                      |  |  |  |  |  |

| DVDD_BF    | 26                         | 1   | Digital I/O buffer supply                                                                                                                            |  |  |  |  |  |

| DVDD_CLK   | 44                         | 1   | Digital clock supply                                                                                                                                 |  |  |  |  |  |

| DVDD_LG    | 47                         | 1   | Digital logic supply                                                                                                                                 |  |  |  |  |  |

| DVDD_RX    | 15                         | 1   | Receive channel digital power supply                                                                                                                 |  |  |  |  |  |

| DVDD_DAC   | 57                         | 1   | Digital power supply for DAC                                                                                                                         |  |  |  |  |  |

| DVSS       | 9, 58                      | 1   | Digital ground                                                                                                                                       |  |  |  |  |  |

| DVSS_BF    | 27                         | 1   | Digital I/O buffer ground                                                                                                                            |  |  |  |  |  |

| DVSS_CLK   | 43                         | 1   | Digital clock ground                                                                                                                                 |  |  |  |  |  |

| DVSS_LG    | 46                         | 1   | Digital logic ground                                                                                                                                 |  |  |  |  |  |

| DVSS_RX    | 16                         | 1   | Receive channel ground                                                                                                                               |  |  |  |  |  |

| DVSS_DAC   | 56                         | 1   | DAC ground                                                                                                                                           |  |  |  |  |  |

| ECM        | 79                         | 0   | EC output minus                                                                                                                                      |  |  |  |  |  |

| ECP        | 78                         | 0   | EC output plus                                                                                                                                       |  |  |  |  |  |

| FS         | 38                         | 1   | Frame sync input                                                                                                                                     |  |  |  |  |  |

| GP7        | 8                          |     |                                                                                                                                                      |  |  |  |  |  |

| GP6        | 7                          |     |                                                                                                                                                      |  |  |  |  |  |

| GP5<br>GP4 | 6<br>5                     |     |                                                                                                                                                      |  |  |  |  |  |

| GP3        | 5<br>4                     | 0   | General-purpose output port                                                                                                                          |  |  |  |  |  |

| GP2        | 3                          |     |                                                                                                                                                      |  |  |  |  |  |

| GP1        | 2                          |     |                                                                                                                                                      |  |  |  |  |  |

| GP0        | 1                          |     |                                                                                                                                                      |  |  |  |  |  |

| INT        | 40                         | 0   | Data rate clock (INT is 4.4 MHz when OSEN=1, 2.2 MHz when OSEN=0)                                                                                    |  |  |  |  |  |

| NC         | 10, 14, 74,                |     | No connection. All the NC pins should be left open.                                                                                                  |  |  |  |  |  |

|            | 75, 76, 77,<br>80, 85, 91, |     |                                                                                                                                                      |  |  |  |  |  |

|            | 97                         |     |                                                                                                                                                      |  |  |  |  |  |

| OE         | 50                         | 1   | Parallel port output enable from host processor                                                                                                      |  |  |  |  |  |

| OE_SYNC    | 99                         | 1   | OE synchronized input. A high input will optimize the read operation from keep-out zone. The default                                                 |  |  |  |  |  |

|            |                            |     | state of this pin is low. See Figure 5 for details.                                                                                                  |  |  |  |  |  |

| ONE_WE     | 98                         | I   | TX and EC write combined input. A high on this pin allows pin 48, WETX, to be used to write to both the                                              |  |  |  |  |  |

|            |                            |     | EC and TX channels. In this case, after a hardware reset or write to SCR14[0], the first low-going pulse of                                          |  |  |  |  |  |

|            |                            |     | WETX will be a write to TX channel and the second one will be a write to EC channel. The default state of this pin is low.                           |  |  |  |  |  |

| OSEN       | 39                         | 1   | Over-sampling enable input. OSEN=1 enables over-sampling mode (INT = 4.4 MHz).                                                                       |  |  |  |  |  |

| PWDN       | 53                         |     | Power-down input. When PWDN=0, device is in normal operating mode. When PWDN=1, device is in                                                         |  |  |  |  |  |

|            | 00                         | '   | power-down mode.                                                                                                                                     |  |  |  |  |  |

| REFM       | 89                         | 0   | Decoupling reference REF voltage minus. Add 10 $\mu$ F tantalum and 0.1 $\mu$ F ceramic capacitors to                                                |  |  |  |  |  |

|            |                            |     | AVSS_REFP. The nominal dc voltage at this terminal is 0.5 V. See figure 9 for detail.                                                                |  |  |  |  |  |

| REFP       | 88                         | 0   | Decoupling reference REF voltage plus. Add 10 $\mu F$ tantalum and 0.1 $\mu F$ ceramic capacitors to                                                 |  |  |  |  |  |

|            |                            |     | AVSS_REFM. The nominal dc voltage at this terminal is 2.5 V See figure 9 for detail.                                                                 |  |  |  |  |  |

| RESET      | 52                         | 1   | H/W system reset. An low level will reset the device.                                                                                                |  |  |  |  |  |

| RXM        | 96                         | I   | Receive RX input minus. RXM is self-biased to AVDD_FIL_RX/2.                                                                                         |  |  |  |  |  |

| RXP        | 95                         | I   | Receive RX input plus. RXP is self-biased to AVDD_FIL_RX/2.                                                                                          |  |  |  |  |  |

| SCLK/READY | 37                         | 0   | If CONFIG2 (pin 100) is low, this pin is serial clock output. If CONFIG2 is high, it indicates the period in which parallel data can be transferred. |  |  |  |  |  |

|            |                            |     | Which parallel data can be transferred.                                                                                                              |  |  |  |  |  |

SLWS087B - JUNE 1999 - REVISED MARCH 2000

## **Terminal Functions(Continued)**

| TERMI    | NAL |                                                                                                                                                                                                                    | DECODIDITION                                                                                                                                                                                                                                                                                   |  |  |  |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO. | 1/0                                                                                                                                                                                                                | DESCRIPTION                                                                                                                                                                                                                                                                                    |  |  |  |

| SDO      | 35  | 0                                                                                                                                                                                                                  | Serial data output                                                                                                                                                                                                                                                                             |  |  |  |

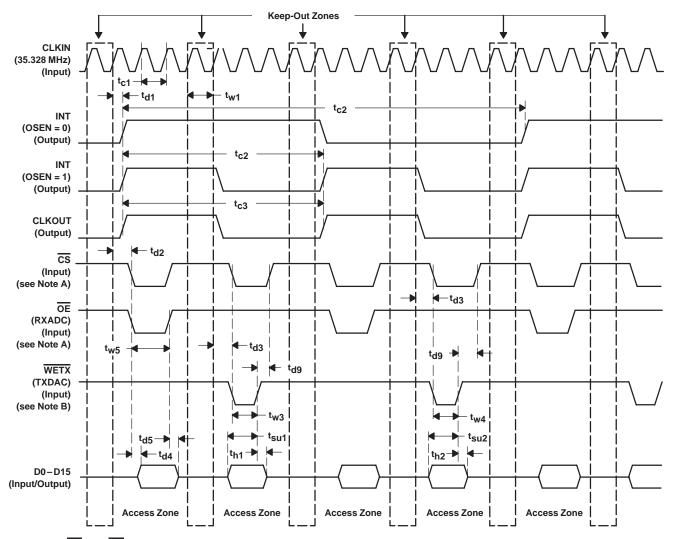

| SYNC     | 45  | I                                                                                                                                                                                                                  | SYNC pulse for clock synchronization. A high pulse to the pin synchronizes the clock operation. T default state of the pin is low. Refer to Figure 4 for detail.                                                                                                                               |  |  |  |

| ТХМ      | 82  | 0                                                                                                                                                                                                                  | Transmit output minus                                                                                                                                                                                                                                                                          |  |  |  |

| ТХР      | 81  | 0                                                                                                                                                                                                                  | Transmit output plus                                                                                                                                                                                                                                                                           |  |  |  |

| VCXOCNTL | 59  | 0                                                                                                                                                                                                                  | VCXO DAC output                                                                                                                                                                                                                                                                                |  |  |  |

| VMID_ADC | 11  | 0                                                                                                                                                                                                                  | Decoupling 1.5 V for ADC. Add 10 $\mu$ F tantalum and 0.1 $\mu$ F ceramic capacitors to AVSS_ADC.                                                                                                                                                                                              |  |  |  |

| VMID_REF | 90  | 0                                                                                                                                                                                                                  | Decoupling 1.5 V reference voltage. Add 10 $\mu F$ tantalum and 0.1 $\mu F$ ceramic capacitors to AVSS_REF.                                                                                                                                                                                    |  |  |  |

| VSS      | 92  | 1                                                                                                                                                                                                                  | Substrate. V <sub>SS</sub> needs to connect to analog ground.                                                                                                                                                                                                                                  |  |  |  |

| WEEC/CS2 | 49  | I Write enable to EC channel from host processor, when ONE_WE (pin 98) is low. If ONE_<br>functions as second chip select, CS2, and both CS and CS2 need to be low in order to<br>access data on the parallel bus. |                                                                                                                                                                                                                                                                                                |  |  |  |

| WETX     | 48  | I                                                                                                                                                                                                                  | Write enable for TX channel from host processor. If ONE_WE is high, it functions as write enable for both TX and EC after hardware reset or write to SCR14[0]. In this case, the first low-going pulse of WETX will be a write to TX channel, and the second one will be a write to EC channel |  |  |  |

## functional block diagram

SLWS087B - JUNE 1999 - REVISED MARCH 2000

## PRINCIPLES OF OPERATION

#### communication channels

#### transmitter channel/echo-cancellation channel

The transmitter channel is powered by a high performance DAC. This is a 4.416-MHz, 14-bit DAC that provides a 16X over-sampling to reduce DAC noise. The input buffer is sampled at either 276 KSPS (pin OSEN = low, default), or 552 KSPS (pin OSEN = high). A low-pass filter limits its output to 138 kHz. A programmable attenuator, with a range between 0 and -24 dB in -1-dB steps, drives the output into the external ADSL line driver.

A second transmitter is used to perform pre-echo cancellation. This analog echo cancellation helps reduce the dynamic range requirements of the RT receiver. It has the same function as the first transmitter channel. It drives a separate external line driver to perform the cancellation.

#### receiver channel

The receiver channel has two PGAs and an equalizer to match the loop loss and flatten the spectrum. This results in a reduction in dynamic range requirement for the high resolution ADC. The receiver channel also has a 1.104-MHz low-pass filter with a 4.416 MSPS and a 14-bit ADC to provide a 2X over-sampling. The output buffer is updated at either 2208 KSPS (pin OSEN = low, default), or 4416 KSPS (pin OSEN = high).

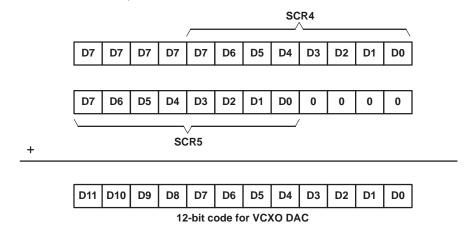

#### VCXO-control DAC

A 12-bit DAC is used to control the external 35.328-MHz VCXO (voltage control oscillator) that provides the system clock to the codec. In a typical application, the typical update rate of the DAC is about 4 kHz, depending on the ADSL frame rate. The host DSP initiates the update through the serial interface. The two 8-bit registers SCR4 and SCR5 (each 2s complement) are used to generate the 12-bit code for the DAC. This requires the use of 16 bits to obtain a 12-bit number. So the lower 4 bits of the MSB register (SCR5[3:0]) are added (2s complement) to the higher 4 bits of the LSB register (SCR4[7:4]). Refer to Figure 1 for code generation. The updated code is sent to the DAC two SCLKs after the SCR4 register is received. Notice that if SCR5 does not need to be updated, only one write cycle to SCR4 is needed to update the VCXO DAC. In this case, the lower 8 bits of the 12-bit word will be updated.

Figure 1. 12-Bit Code Generation for VCXO DAC

## PRINCIPLES OF OPERATION

## communication channels (continued)

#### clock generation

The clock generation block provides the necessary clock signals for the device, with minimum skew and jitter. This is closely dependent on the performance of the external VCXO. The external VCXO specifications are:

- 3.3 V supply

- 35.328 MHz ± 50 PPM

- Minimum duty cycle is 60/40 (50/50 is optimum)

The major clocks generated internally are shown in Table 1.

| CLOCK  | FREQUENCY<br>(MHz) |        |  |  |  |

|--------|--------------------|--------|--|--|--|

|        | OSEN=0             | OSEN=1 |  |  |  |

| INT    | 2.208              | 4.416  |  |  |  |

| CLKOUT | 4.416              | 4.416  |  |  |  |

| SCLK   | 4.416              | 4.416  |  |  |  |

## Table 1. Clock Description

#### INT

The interrupt (INT) to the host processor is 4.416 MHz when OSEN = 1 and 2.208 MHz when OSEN = 0.

#### SCLK

The serial clock used in the serial codec interface has a fixed frequency of 4.416 MHz and is synchronous with the master clock (35.328 MHz).

## CLKOUT

CLKOUT is a 4.416-MHz clock output, and is synchronous with the master clock (35.328 MHz).

## interface

#### parallel interface

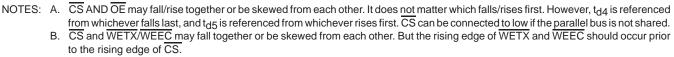

The device has a 16-bit parallel interface for transmitter and receiver data. Strobes  $\overline{OE}$ ,  $\overline{WETX}$ , and  $\overline{CS}$  from the host DSP are edge-triggered signals. An incoming signal is registered on the rising edge of  $\overline{WETX}/\overline{WEEC}$ . When  $ONE_WE$  is enabled, only  $\overline{WETX}$  is needed for both the transmit channel and the echo-cancellation channel write operation. After D0 of register SCR14 is programmed, the data from the first pulse of  $\overline{WETX}$  goes to the transmit channel, while the data from the second pulse of  $\overline{WETX}$  goes to the echo-cancellation channel. Output data from the codec is enabled after the falling edge of the  $\overline{OE}$  strobe, and disabled after the rising edge of the  $\overline{OE}$  strobe. The INT cycle time is hardware-configurable to 4.416 MHz (2X over-sampling mode, OSEN=1), or to 2.208 MHz (1X over-sampling mode, OSEN=0). SYNC is used to synchronize the operation between the codec and the host transceiver. SCLK/READY is used to indicate the parallel data transfer period in configuration mode 2. See Figure 3 for details.

OE\_SYNC is used to synchronize the codec timing to  $\overline{OE}$ . See Figure 5 for details.

For the 16-bit parallel data, D0 is the LSB and D15 is the MSB. The parallel TX and RX data contains 16 valid bits. All 16 bits are used in the digital filtering.

SLWS087B - JUNE 1999 - REVISED MARCH 2000

## PRINCIPLES OF OPERATION

## interface (continued)

#### keep-out zones

The last CLKIN cycle before a transition of CLKOUT is defined as a keep-out zone. These zones are reserved for the sampling of analog signals. All digital I/O (except for CLKIN) should be quiet during these keep-out zones.

#### over-sampling mode

The OSEN pin selects 2X over-sampling mode (INT running at 4.416 MHz), or 1X over-sampling mode (INT running at 2.208 MHz).

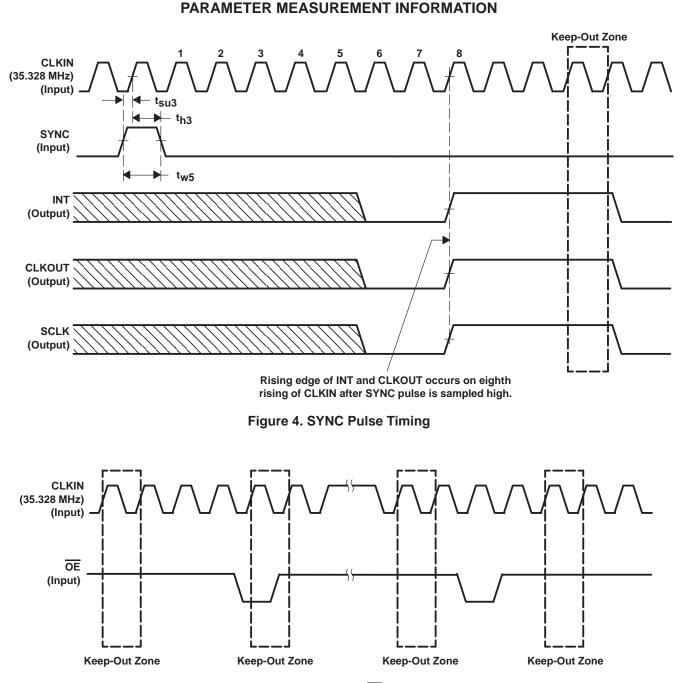

#### serial interface

The serial port is used for codec configuration and register reading. The word length is 16-bit. Two hardware configuration terminals, ADR[1:0], are used to configure the device ID. Up to four codecs can be identified for each common serial port. Refer to figure 6 for timing and format.

The master codec (ADR[1:0] = [0,0]) provides the SCLK to the host processor. The SCLK terminals on the other codecs are left unconnected. All the codecs in a multi-codec system should be synchronized so that their SCLK signals are in phase, even though the signals themselves are not being used. This ensures that, even though the individual SCLK signals of each codec are not being used, the data is being latched into the codec properly.

The SCLK is a continuously running 4.416-MHz fixed-frequency clock, synchronized to the codec internal events and CLKOUT (to the host) so that the keep-out zones may be monitored. A host DSP can drive the FS (synchronized to the CLKOUT from the codec) into the codec to initiate a 16-bit serial I/O frame.

If SCR5 needs to be updated, the host controller (DSP) must first write the SCR5 of the VCXO DAC data, and then the SCR4 of the VCXO DAC data. The VCXO DAC only gets updated after the SCR4 is written.

#### **GP** port

The general-purpose port provides eight outputs, each capable of delivering 0.5 mA, for control of external circuitry such as LEDs, gain control, and power down.

## voltage reference

The built-in reference provides the required reference voltage and current to individual analog blocks. It is also brought out to external terminals for noise decoupling.

SLWS087B - JUNE 1999 - REVISED MARCH 2000

# **PRINCIPLES OF OPERATION**

## register programming (see Figure 6 for timing and format details)

## Table 2. System Control Registers (SCR)

| REGISTER                  |                           |          | DEFAULT                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|---------------------------|---------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                      | ADDRESS<br>S3, S2, S1, S0 | MODE     | DEFAULT<br>VALUE                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FUNCTION                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 0000                      | 0000                      | R        | 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| SCR0                      | 0000                      | W        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D0: S/W RESET (self clearing)                                                                                                                                                                                                                                                                                                              |  |  |  |

| SCR1                      | 0001                      | R/W      | 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D[4:0]=TX channel PAA gain select. D[4:0]=00000 for 0 dB<br>D[4:0]=11000 for -24 dB                                                                                                                                                                                                                                                        |  |  |  |

| SCR2                      | 0010                      | R/W      | 00000000 D[5:0]=RX PGA2. D[5:0]=000000 for 0 dB. D[5:0]=101110 for 11.5 dB.                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                            |  |  |  |

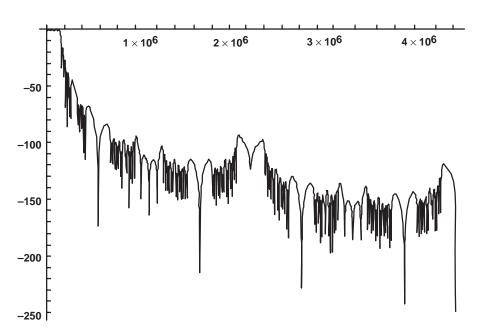

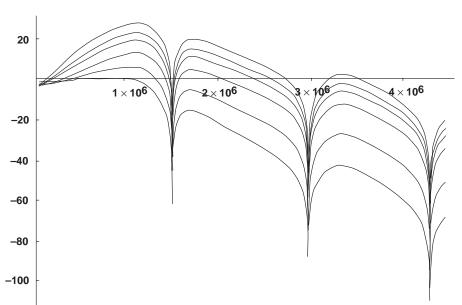

| SCR3                      | 0011                      | R/W      | 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D[2:0]= RX EQ slope select. D[2:0]=000 for 0dB/MHz, D[2:0]=001 for 5 dB/MHz, D[2:0]=101 for 25 dB/MHz                                                                                                                                                                                                                                      |  |  |  |

| SCR4                      | 0100                      | R/W      | 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D[7:0]=VCXODAC (low 8 bits of 12-bit DAC code)                                                                                                                                                                                                                                                                                             |  |  |  |