# 212A/V.22 Modem Filter With Equalizers & Analog Loopback

S35212A

### **Features**

- Bell 212A/V.22/V.22BIS Compatible

- Usable for Bell 103/113 Applications

- High and Low Band Filters With Compromise Group Delay Equalizers and Smoothing Filters

- Guard Tone Notch Filters for CCITT V.22/V.22BIS Applications

- Originate/Answer Operating Modes

- Low Power CMOS: 75 mW Typ.

- Two Uncommitted Operational Amps

- Choice of Clocking Frequencies: 2.4576 MHz, 1.2288 MHz, or 153.6 kHz

- · Call Progress Tone Filter Capability

- Analog Loopback Test Capability

# **General Description**

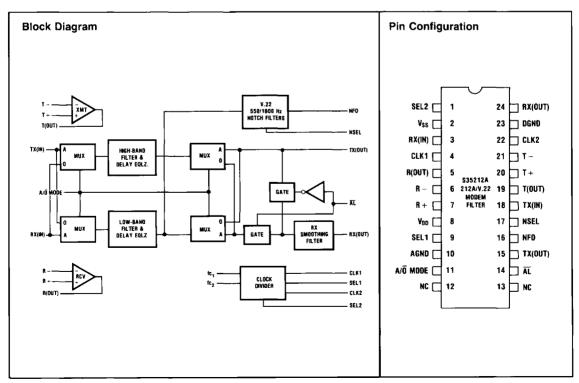

The S35212A Modem Filter is a monolithic CMOS integrated circuit. It does the filter/equalizing functions of Bell 212A and CCITT V.22 (or V.22BIS) modems. The S35212A includes high band and low band filters. It features on-chip originate/answer mode selection. Included are compromise amplitude and group delay equalizers for full compromise equalization. There is a CCITT notch filter included. It provides rejection at 1800 Hz or 550 Hz. Two uncommitted operational amplifiers are available to use for gain control or anti-aliasing filters. A continuous low pass filter is also included on the RX(OUT) pin to act as a smoothing filter. SEL2 switches the S35212A between the normal data mode

Analog Loopback capability to switch the transmit carrier output back through the receive output for testing.

and the call progress monitoring mode. For maximum flexibility the S35212A will operate from a 2.4576 MHz, 1.2228 MHz or 153.6 kHz clock. The S35212A has

# **Pin Functional Description**

| Pin Name   | Pin Number | Function                                                                                                                                                                                                |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEL2       | 1          | Logic '0' for normal operation. Logic '1' scales down the frequency response by a factor of 6 for Call Progress Tone Detection through the high-band filter                                             |

| $V_{SS}$   | 2          | Negative Supply Voltage (-5 Volts).                                                                                                                                                                     |

| RX(IN)     | 3          | Receive Signal Input.                                                                                                                                                                                   |

| CLK1       | 4          | 2.4576 MHz or 1.2288 MHz Clock Input. This input is TTL and CMOS compatible. Leave open when using CLK2.                                                                                                |

| R(OUT)     | 5          | Receive Uncommitted Op Amp Output (10 kΩ load maximum).                                                                                                                                                 |

| R-         | 6          | Receive Uncommitted Op Amp Negative Input.                                                                                                                                                              |

| R+         | 7          | Receive Uncommitted Op Amp Positive Input.                                                                                                                                                              |

| $V_{DD}$   | 8          | Positive Supply Voltage (+5 Volts).                                                                                                                                                                     |

| SEL1       | 9          | Logic '0' selects 1 2288 MHz. Logic '1' selects 2.4576 MHz clock into Pin 4.                                                                                                                            |

| AGND       | 10         | Analog Ground.                                                                                                                                                                                          |

| MODE (A∕Ō) | 11         | Originate: Answer Mode Control Input. A logic '0' sets the device in Originate Mode with the transmit signal in the low-band and receive signal in the high-band. A logic '1' reverses the connections. |

| N/C        | 12         | Do not connect to this pin.                                                                                                                                                                             |

| N/C        | 13         | Do not connect to this pin.                                                                                                                                                                             |

| ĀĹ         | 14         | Analog Loopback Control Input. A logic '0' sets the device in Loopback Mode. A logic '1' sets the device in Normal Mode.                                                                                |

| TX(OUT)    | 15         | Transmit Signal Output. This output will drive a 20k load.                                                                                                                                              |

| NFO        | 16         | Notch Filter Output This output will drive a 20k load.                                                                                                                                                  |

| NSEL       | 17         | A logic '0' on this input programs the notch filter to reject 500 Hz. A logic '1' programs it to reject 1800 Hz.                                                                                        |

| TX(IN)     | 18         | Transmit Signal Input.                                                                                                                                                                                  |

| T(OUT)     | 19         | Transmit Uncommitted Op Amp Output (10 kΩ load maximum).                                                                                                                                                |

| T+         | 20         | Transmit Uncommitted Op Amp Positive Input.                                                                                                                                                             |

| T-         | 21         | Transmit Uncommitted Op Amp Negative Input.                                                                                                                                                             |

| CLK2       | 22         | 153.6 kHz Clock Input. This input is TTL and CMOS compatible Leave open when using CLK1                                                                                                                 |

| DGND       | 23         | Digital Ground.                                                                                                                                                                                         |

| RX(OUT)    | 24         | Receive Signal Output. This output will drive a 20k load.                                                                                                                                               |

# AMI \*Semiconductors

# S35212A

# **Absolute Maximum Ratings**

| DC Supply Voltage (V <sub>DD</sub> - V <sub>SS</sub> ) | + 13.5V                                      |

|--------------------------------------------------------|----------------------------------------------|

| Operating Temperature                                  |                                              |

| Storage Temperature                                    |                                              |

| Analog Input                                           | $V_{SS} - 0.3V \le V_{IN} \le V_{DD} + 0.3V$ |

# **D.C. Electrical Operating Characteristics:** $T_A = 0$ °C to +70°C; $V_{DD} = +5V \pm 10\%$ ; $V_{SS} = -5V \pm 10\%$ unless otherwise specified

| Symbol          | Parameter/Conditions                                                         | Min.            | Тур. | Max.            | Units |

|-----------------|------------------------------------------------------------------------------|-----------------|------|-----------------|-------|

| V <sub>iH</sub> | High Level Logic Input (Pins 1, 9, 11, 17, 14)<br>SEL2, SEL1, MODE, NSEL, AL | 4               |      | V <sub>DD</sub> | V     |

| V <sub>IH</sub> | High Level Logic Input (Pins 4 and 22) CLK1, CLK2                            | 2.0             |      | V <sub>DD</sub> | V     |

| V <sub>IL</sub> | Low Level Logic Input (Pins 1, 4, 9, 11, 17, 22, 14)                         | V <sub>SS</sub> |      | 0.8             | V     |

| R <sub>IN</sub> | Input Resistance (Pins 3 and 18) RX(IN), TX(IN)                              |                 | 5    |                 | MΩ    |

| CIN             | Input Capacitance (Pins 3 and 18) RX(IN), TX(IN)                             |                 | 10   |                 | pF    |

| P <sub>D</sub>  | Power Dissipation @ ± 5.25V                                                  |                 | 75   | 150             | mW    |

# **A.C. System Specifications:** $T_A = 25^{\circ}C$ ; $V_{DD} = +5V \pm 10\%$ ; $V_{SS} = -5V \pm 10\%$ unless otherwise specified

| Symbol           | Parameter/Conditions                           | Min. | Typ. | Max. | Units  |

|------------------|------------------------------------------------|------|------|------|--------|

| ٧0               | Reference Signal Level Input                   |      | 1    |      | VRMS   |

| V <sub>MAX</sub> | Maximum Signal Level Input                     |      | 1 4  |      | VRMS   |

| BW               | Bandwidth (both bands; - 3dB)                  |      | 960  |      | Hz     |

| A <sub>FO</sub>  | Gain at Center Frequencies                     | - 1  | 0    | +1   | dB     |

| 1CN <sub>L</sub> | Idle Channel Noise-Low Band Filter             |      | 22   | 33   | dBrnC0 |

| ICN <sub>H</sub> | Idle Channel Noise-High Band Filter            |      | 23   | 33   | dBrnCO |

| N <sub>FT</sub>  | Clock Feedthrough with Respect to Signal Level | TX   | - 23 |      | dB     |

|                  |                                                | RX   | - 60 |      | dB     |

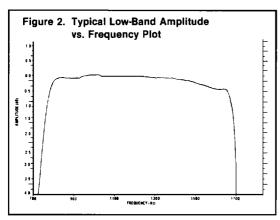

### Frequency vs. Amplitude Performance of Low- and High- Band Filters

| Frequency (Hz)  | Relative Gain (dB) |             |  |

|-----------------|--------------------|-------------|--|

| Low-Band Filter | Min.               | Max.        |  |

| 400             |                    | - 35        |  |

| 800             | -1                 | +1          |  |

| 1200            | Ó                  |             |  |

| 1600            | -15                | +1          |  |

| 1800            |                    | <b>-18</b>  |  |

| 2000            | ļ                  | <b>– 48</b> |  |

| 2400            |                    | <b>-</b> 55 |  |

| 2800            |                    | - 50        |  |

|                 |                    |             |  |

| Frequency (Hz)   | Relative Gain (dB) |      |  |

|------------------|--------------------|------|--|

| High-Band Filter | Min.               | Max. |  |

| 800              |                    | - 50 |  |

| 1200             |                    | - 53 |  |

| 1600             |                    | - 50 |  |

| 2000             | -2.5               | +0.5 |  |

| 2400             | Ó                  |      |  |

| 2800             | 0                  | +25  |  |

| 3200             |                    | 10   |  |

| 3500             |                    | -20  |  |

#### **Notch Filter Response**

| Francisco (Un)                                                  | Relative Gain (dB) |            |  |

|-----------------------------------------------------------------|--------------------|------------|--|

| Frequency (Hz)                                                  | Min.               | Max.       |  |

| Low-Band Filter +<br>1800 Hz Notch Filter<br>1200 Hz<br>1800 Hz | -1                 | + 1<br>-32 |  |

| Low-Band Filter +<br>550 Hz Notch Filter<br>1200 Hz<br>550 Hz   | -1                 | + 1<br>-32 |  |

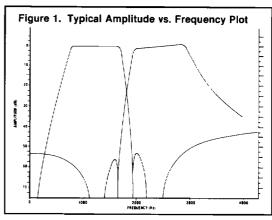

# **Frequency Response Characteristics**

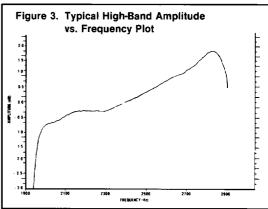

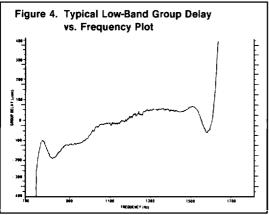

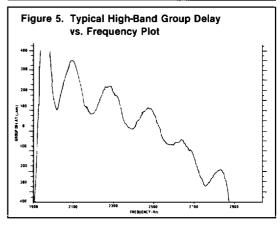

The curves on this page illustrate typical filter responses of the S35212A. Figure 1 shows the basic band split function. This allows full duplex operation within a voice channel. Figures 2 and 3 show the frequency response of the two filters. These curves include the compromise equalizers. Figures 4 and 5 show the typical group delay response of the filters and equalizers.

#### **Call Progress Monitoring (Pin 1)**

The center frequencies of the two filters shift down to one-sixth of their original values when pin 1 goes high. The high-band 2400 Hz filter centers around 400 Hz. Its passband is approximately 300 to 480 Hz. Precision dial tone (350/440 Hz) will pass. Ringback (440/480 Hz) and half of busy/reorder (480/620 Hz) will also pass.

The modem's energy detector software can determine the cadence or timing of the information to identify the proper status of the call.

#### V.22 Notch Filter (Pins 16, 17)

The S35212A includes a notch filter for CCITT V.22 modem operation. This filter notches out the guard tone required in V.22 operation. When a V.22 modem answers, it sends the 2100 Hz answer tone, and then the 2400 Hz data carrier. It is also required to send along with the data carrier a guard tone of 1800 Hz. (Some administrations require 550 Hz.) The purpose of this tone is to prevent the network from disconnecting. It provides energy at another point in the spectrum other than 2400 Hz. This simulates speech and will not trigger signaling receivers. The tone is only 3 dB below the data carrier. It is 600 Hz closer to the desired receive frequency of 1200 Hz, requiring additional filtering to maintain performance.

Pin 17, NSEL, when high, provides 1800 Hz notching. When low, it provides 550 Hz notching.

The output of the low-band filter, through the notch filter, is always available at pin 16, Notch Filter Out.

#### Analog Loopback (ALB) (Pin 14)

When pin 14,  $\overline{AL}$ , is low, the signal at pin 18, TX(IN), passes through the filter selected by pin 11, A/ $\overline{O}$ , and out through pin 5, RX(OUT).

Analog Loopback tests the local modem and terminal/computer hardware and software. Any character sent from the keyboard echoes back to the screen after being sent to the modem. It is modulated by the modem and sent out to the filter. If pin 14 is low, the

#### **Call Progress Tones**

| Frequencies  | Timing/Cadence                       | Condition<br>Indicated      |

|--------------|--------------------------------------|-----------------------------|

| 350 + 440 Hz | Constant Tone                        | Dial Tone                   |

| 440 + 480 Hz | 2sec on, 4sec off                    | Audible Ringing             |

| 480 + 620 Hz | 0.5sec on, 0.5sec off<br>(60 ppm)    | Line Busy<br>(Station Busy) |

| 480 + 620 Hz | 0.25sec on, 0.25sec off<br>(120 ppm) | Trunk Busy<br>(Reorder)     |

analog signal passes back through the RX(OUT) pin to the modem. It is demodulated and returned to the terminal/computer as received data.

#### Clock Input Selection (Pins 4, 9, 22)

The filter uses one of three possible clock frequencies. Either 2.4576 MHz or 1.2288 MHz can be applied to pin 4, CLK1. Pin 9, SEL1, when high, selects the divider for 2.4576 MHz. When low, it selects the divider for 1.2288 MHz. When using the S35212A with the S35213 modem chip, or if a 153.6 kHz clock is available, the clock is applied to pin 22, CLK2. Leave pins 4 and 9 open.

Compatibility with Previous Filters (Pins 12, 13, 14) The S35212A plugs directly into any socket that previously held an S35212. It functions exactly as the S35212 as long as pin 14 is high. Pins 12 and 13 should be left open.

#### Answer/Originate Mode Selection (Pin 11)

Pin 11 selects the filters for the particular mode of operation. When it is low for the originate mode, the transmit path is through the low-band filter. Receive is through the high-band filter. When this pin is high for the answer mode, the transmit path is through the high-band filter. Receive is through the low-band filter. An internal pull-down resistor keeps the chip in the originate mode when this pin is not connected.

#### **Uncommitted Operational Amplifiers**

The two operational amplifiers are available to use as gain stages or anti-aliasing filters for the complete modern circuit. These are CMOS op amps. They do not have low impedance drive capability. Do not load by less than 10 k $\Omega$ . The open loop voltage gain is typically about 86 dB and the unity gain frequency is about 1.5 MHz with < 5 pF loading. Input offset voltages will be 10 mV or less.

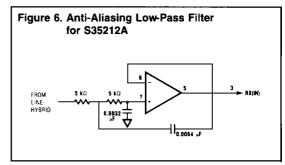

Using one of the op amps for anti-aliasing is a good idea. The receive input to the filters must be band limited to avoid aliasing. The telephone network band limits the incoming signals from distant modems. Nevertheless, local noise or noise on the modem board itself can create problems. Figure 6 shows a second-order

low-pass filter constructed around the receive op amp. It is a critically-damped, unity-gain, Sallen-Key filter with a cutoff frequency of 6 kHz.