## 54F/74F784

## 8-Bit Serial/Parallel Multiplier with Adder/Subtractor

## **General Description**

The 'F784 is an 8-bit by 1-bit sequential logic element that multiplies two numbers represented in twos complement notation. The device implements Booth's algorithm internally to produce a twos complement product that needs no subsequent correction. In addition to the serial product output (SP), an S $\pm$ B output is obtained with an internal adder/subtractor stage which adds a B bit to the SP product. Parallel inputs accept and store an 8-bit multiplicand  $(X_0-X_7)$ . The add/subtract (\$\overline{A}/S), \$B\_n\$ and \$B\_{n-1}\$ inputs control the internal adder/subtractor stage. The multiplier word is then applied to the Y input in a serial bit stream, least significant bit first. The product is clocked out at the SP output and the product  $\pm$ B at the S $\pm$ B output delayed by one clock cycle. Both appear least significant bit first.

The K input is used for expansion to longer X words, using two or more 'F784 devices by connecting the output (SP) of

one device to the K input of the other device. The Mode Control (M) input is used to establish the most significant device. An asynchronous Parallel Load ( $\overline{\text{PL}}$ ) input clears the internal flip-flops to the start condition and enables the X latches to accept new multiplicand data. The Parallel Load ( $\overline{\text{PL}}$ ) also clears the outputs (SP and S $\pm$ B).

#### **Features**

- Twos complement multiplication

- 8-bit by 1-bit sequential logic element

- Includes product output (SP) and product ±B output (S±B)

- Parallel inputs accept and store an 8-bit multiplicand (X<sub>0</sub>-X<sub>7</sub>)

- K input is used for expansion to longer X words

- Combines the 'F384 and 'F385 in one chip

#### Ordering Code: See Section 5

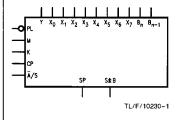

### **Logic Symbol**

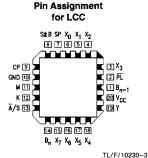

## Connection Diagrams

## Input Loading/Fan-Out: See Section 2

| Pin<br>Names                   | Description                                   | 54F/74F (U.L.)<br>High/Low | l <sub>IH</sub> /l <sub>IL</sub><br>l <sub>OH</sub> /l <sub>OL</sub> |  |  |

|--------------------------------|-----------------------------------------------|----------------------------|----------------------------------------------------------------------|--|--|

| CP                             | Clock Pulse Input (Active Rising Edge)        | 1.0/1.0                    | 20 μA/ – 0.6 mA                                                      |  |  |

| K                              | Serial Expansion Input                        | 1.0/1.0                    | 20 μA/-0.6 mA                                                        |  |  |

| М                              | Mode Control Input                            | 1.0/1.0                    | 20 μA/ – 0.6 mA                                                      |  |  |

| PL                             | Asynchronous Parallel Load Input (Active LOW) | 1.0/2.0                    | 20 μA/ – 1.2 mA                                                      |  |  |

| X <sub>0</sub> -X <sub>7</sub> | Multiplicand Data Inputs                      | 1.0/1.0                    | 20 μA/ – 0.6 mA                                                      |  |  |

| Υ                              | Serial Multiplier Input                       | 1.0/1.0                    | 20 μA/ – 0.6 mA                                                      |  |  |

| Ā/S                            | Add/Subtract                                  | 1.0/1.0                    | 20 μA/-0.6 mA                                                        |  |  |

| B <sub>n</sub>                 | Serial B Input                                | 1.0/1.0                    | 20 μA/-0.6 mA                                                        |  |  |

| B <sub>n-1</sub>               | Delayed Serial B Input                        | 1.0/1.0                    | 20 μA/-0.6 mA                                                        |  |  |

| S±B                            | Serial X • Y ± B Output                       | 50/33.3                    | - 1 mA/20 mA                                                         |  |  |

| SP                             | Serial X ◆ Y Product Output                   | 50/33.3                    | -1 mA/20 mA                                                          |  |  |

## **Functional Description**

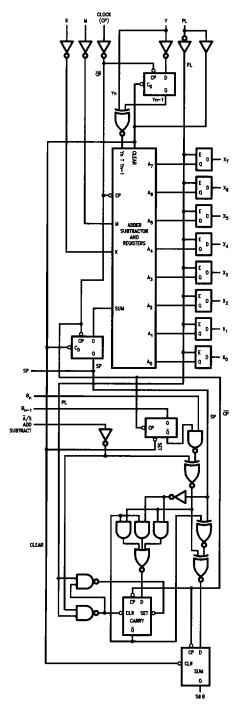

The 'F784 is a serial-parallel 8-bit multiplier. Also included is an adder/subtractor stage. The X word (multiplicand) is loaded into a register while simultaneously clearing the arithmetic cell flip-flops in preparation for a multiplication. The Y word (multiplier) is clocked in serially. (See *Figure A*).

Expansion capability is provided via the M and K inputs. The K (cascade) input is connected to the S<sub>0</sub> output of the more significant chip. The M (mode) input is used to determine whether the multiplicand is to be treated as a two's complement or unsigned number.

The 'F784 has logic to enable complex arithmetic to be performed. A serial adder/subtractor enables constants to be added to the product. Typically this feature would be used in FFT butterfly networks to reduce package count and power.

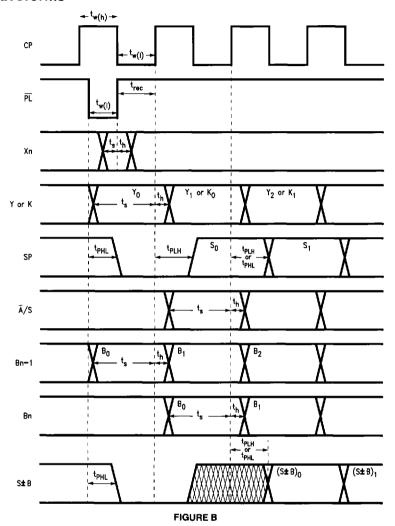

Two outputs are provided: the product XY and the product XY  $\pm$ B. Because of the internal adder/subtractor, a speed advantage is gained when using the 'F784 over using a separate adder and multiplier chip. (Refer to Figure B).

During a multiplication operation, the first clock cycle is used to load both the X word (multiplicand) and the first bit

of the Y word (operand) into the input registers. At this time there is no valid data at the SP output so that B bits added will not give the correct sum output. In order to load the first B bit on the same clock as X and Y, a  $B_{n-1}$  input is provided which delays the B data by one clock cycle. Thus, a valid output results.

|     | Input          | s                | Function                                                                                         |

|-----|----------------|------------------|--------------------------------------------------------------------------------------------------|

| Ā/S | Bn             | B <sub>n-1</sub> | Tullonon                                                                                         |

| L   | Н              | Cn               | Add $C_n$ to product ( $C_n$ loaded at the same time as $Y_n$ )                                  |

| L   | Cn             | H                | Add C <sub>n</sub> to product (C <sub>n</sub> must be delayed one clock cycle)                   |

| Н   | Н              | C <sub>n</sub>   | Subtract C <sub>n</sub> from product (C <sub>n</sub> loaded at the same time as Y <sub>n</sub> ) |

| Н   | C <sub>n</sub> | Н                | Subtract C <sub>n</sub> from product (C <sub>n</sub> must be delayed one clock cycle)            |

$L = LOW Voltage Level H = HIGH Voltage Level C_n = Constant$

#### **Function Table**

| Inputs |             |    |    |    |                  | Internal | Ot  | utputs   | Function                                                            |  |  |

|--------|-------------|----|----|----|------------------|----------|-----|----------|---------------------------------------------------------------------|--|--|

| PL     | PL CP K M X |    | Xi | Υ  | Y <sub>a-1</sub> | SP       | S±B | Function |                                                                     |  |  |

| Х      | ×           | L  | L  | Х  | Х                | Х        | X   | Х        | Most Significant Multiplier Device                                  |  |  |

| χ _    | Х           | cs | Н  | Х  | Х                | Х        | Х   | х        | Devices Cascaded in Multiplier String                               |  |  |

| L      | Х           | X  | Х  | OP | Х                | L        | L   | L        | Load New Multiplicand and Clear<br>Internal Sum and Carry Registers |  |  |

| н      | Х           | х  | Х  | Х  | Х                | Х        | Х   | ×        | Device Enabled                                                      |  |  |

| Н      | 1           | ×  | Х  | Х  | L                | L        | Р   | P±B      | Shift Sum Register                                                  |  |  |

| н      | 1           | X  | Х  | Х  | L                | Н        | Р   | P±B      | Add Multiplicand to Sum<br>Register and Shift                       |  |  |

| н      | 1           | Х  | Х  | Х  | Н                | L        | Р   | P±B      | Subtract Multiplicand from Sum<br>Register and Shift                |  |  |

| Н      | <u></u> ↑   | X  | Х  | X  | I                | Н        | Р   | P±B      | Shift Sum Register                                                  |  |  |

H = HIGH Voltage Level

L = LOW Voltage Level

<sup>↑ =</sup> LOW-to-HIGH Transition

CS = Connected to SP output of high order device

$OP = X_i$  latches open for new data (i = 0-7)

P = Output as required per Booth's algorithm

P±B = Product ± a constant (delayed one clock cycle)

X = Immaterial

# **Logic Diagram**

TL/F/10230-4

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

# **Timing Waveforms**

TL/F/10230-5

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$

Ambient Temperature under Bias -55°C to +125°C Junction Temperature under Bias -55°C to +175°C

V<sub>CC</sub> Pin Potential

to Ground Pin -0.5V to +7.0V

Input Voltage (Note 2) -0.5V to +7.0V Input Current (Note 2) -30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State (with V<sub>CC</sub> = 0V)

Standard Output

TRI-STATE® Output

-0.5V to  $V_{CC}$ -0.5V to +5.5V Current Applied to Output

in LOW State (Max)

twice the rated IOL (mA)

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

# Recommended Operating Conditions

Free Air Ambient Temperature

Military  $-55^{\circ}\text{C to} + 125^{\circ}\text{C}$

Commercial 0°C to +70°C

Supply Voltage

Military + 4.5V to + 5.5V Commercial + 4.5V to + 5.5V

## **DC Electrical Characteristics**

| Symbol           | Parameter -                          |                                                                              |                   | 54F/74 | =            | Units    | Vcc                        | Conditions                                                                                               |  |

|------------------|--------------------------------------|------------------------------------------------------------------------------|-------------------|--------|--------------|----------|----------------------------|----------------------------------------------------------------------------------------------------------|--|

|                  |                                      |                                                                              | Min               | Тур    | Max          | Omis     | ¥66                        |                                                                                                          |  |

| V <sub>IH</sub>  | Input HIGH Voltage                   | 2.0                                                                          |                   | ·      | ٧            |          | Recognized as a HIGH Signa |                                                                                                          |  |

| V <sub>IL</sub>  | Input LOW Voltage                    | Ī                                                                            |                   |        | 0.8          | ٧        |                            | Recognized as a LOW Signal                                                                               |  |

| V <sub>CD</sub>  | Input Clamp Diode Vo                 | oltage                                                                       |                   |        | -1.2         | ٧        | Min                        | I <sub>IN</sub> = -18 mA                                                                                 |  |

| V <sub>OH</sub>  | Output HIGH<br>Voltage               | 54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub><br>74F 5% V <sub>CC</sub> | 2.5<br>2.5<br>2.7 |        |              | ٧        | Min                        | $I_{OH} = -1 \text{ mA}$<br>$I_{OH} = -1 \text{ mA}$<br>$I_{OH} = -1 \text{ mA}$                         |  |

| V <sub>OL</sub>  | Output LOW<br>Voltage                | 54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub>                           |                   |        | 0.5<br>0.5   | ٧        | Min                        | I <sub>OL</sub> = 20 mA<br>I <sub>OL</sub> = 20 mA                                                       |  |

| l <sub>IH</sub>  | Input HIGH<br>Current                | 54F<br>74F                                                                   |                   |        | 20.0<br>5.0  | μА       | Max                        | V <sub>IN</sub> = 2.7V                                                                                   |  |

| I <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test | 54F<br>74F                                                                   |                   |        | 100<br>7.0   | μА       | Max                        | V <sub>IN</sub> = 7.0V                                                                                   |  |

| ICEX             | Output HIGH<br>Leakage Current       | 54F<br>74F                                                                   |                   |        | 250<br>50    | μΑ       | Max                        | V <sub>OUT</sub> = V <sub>CC</sub>                                                                       |  |

| V <sub>ID</sub>  | Input Leakage<br>Test                | 74F                                                                          | 4.75              |        |              | ٧        | 0.0                        | $I_{\text{ID}} = 1.9  \mu\text{A}$ All Other Pins Grounded                                               |  |

| lod              | Output Leakage<br>Circuit Current    | 74F                                                                          | ,                 |        | 3.75         | μΑ       | 0.0                        | V <sub>IOD</sub> = 150 mV<br>All Other Pins Grounded                                                     |  |

| I <sub>IL</sub>  | Input LOW Current                    | -                                                                            |                   |        | -0.6<br>-1.2 | mA<br>mA | Max<br>Max                 | $V_{IN} = 0.5V \text{ (Except } \overline{PL}\text{)}$<br>$V_{IN} = 0.5V \text{ (}\overline{PL}\text{)}$ |  |

| los              | Output Short-Circuit Current         |                                                                              | -60               |        | <b>- 150</b> | mA       | Max                        | V <sub>OUT</sub> = 0V                                                                                    |  |

| Icc              | Power Supply Curren                  | t                                                                            |                   | 70     | 100          | mA       | Max                        | V <sub>O</sub> = HIGH                                                                                    |  |

# AC Characteristics: See Section 2 for Waveforms and Load Configurations

| Symbol           | Parameter                      | 54F/74F<br>T <sub>A</sub> = +25°C<br>V <sub>CC</sub> = +5.0V<br>C <sub>L</sub> = 50 pF |            |             | 54F  T <sub>A</sub> , V <sub>CC</sub> =  Mil  C <sub>L</sub> = 50 pF |     | 74F  T <sub>A</sub> , V <sub>CC</sub> =  Com  C <sub>L</sub> = 50 pF |              | Units | Fig.<br>No. |

|------------------|--------------------------------|----------------------------------------------------------------------------------------|------------|-------------|----------------------------------------------------------------------|-----|----------------------------------------------------------------------|--------------|-------|-------------|

|                  |                                | Min                                                                                    | Тур        | Max         | Min                                                                  | Max | Min                                                                  | Max          | ]     |             |

| f <sub>max</sub> | Maximum Clock Frequency        | 50                                                                                     | 65         |             |                                                                      |     | 50                                                                   |              | MHz   | 2-1         |

| t <sub>PHL</sub> | Propagation Delay PL to SP     | 6.0                                                                                    | 10.0       | 13.0        |                                                                      |     | 5.0                                                                  | 14.5         | ns    | 2-3         |

| t <sub>PHL</sub> | Propagation Delay PL to S ± B  | 5.5                                                                                    | 9.5        | 12.0        |                                                                      | ·   | 4.5                                                                  | 13.5         | ns    | 2-3         |

| t <sub>PLH</sub> | Propagation Delay<br>CP to SP  | 4.0<br>4.5                                                                             | 6.5<br>8.0 | 9.0<br>10.5 |                                                                      |     | 3.5<br>4.0                                                           | 10.0<br>12.0 | ns    | 2-3         |

| t <sub>PLH</sub> | Propagation Delay<br>CP to S±B | 4.0<br>4.0                                                                             | 7.0<br>7.0 | 9.0<br>9.0  |                                                                      |     | 3.5<br>3.5                                                           | 10.0<br>10.0 | ns    | 2-3         |

# AC Operating Requirements: See Section 2 for Waveforms

| Symbol                                   |                                                 | 54F/74F      |                              |     | 5   | 4F            | 7                                         | 4F  |       |             |

|------------------------------------------|-------------------------------------------------|--------------|------------------------------|-----|-----|---------------|-------------------------------------------|-----|-------|-------------|

|                                          | Parameter                                       |              | $A = +25^{\circ}$ $CC = +5.$ |     |     | /cc =<br>/iii | T <sub>A</sub> , V <sub>CC</sub> =<br>Com |     | Units | Fig.<br>No. |

|                                          |                                                 | Min          | Тур                          | Max | Min | Max           | Min                                       | Max |       |             |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>K to CP              | 9.0<br>9.0   |                              |     |     |               | 10.0<br>10.0                              |     | ns    | 2-6         |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>K to CP               | 2.0<br>2.0   |                              |     |     |               | 2.0<br>2.0                                |     |       |             |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>Y to CP              | 15.0<br>15.0 |                              |     |     |               | 15.0<br>15.0                              |     | _ ns  | 2-6         |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>Y to CP               | 2.0<br>2.0   |                              |     |     |               | 2.0<br>2.0                                |     |       |             |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>X to PL              | 3.0<br>6.0   |                              |     |     |               | 4.0<br>7.0                                |     | _ ns  | 2-6         |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>X to PL               | 2.0<br>4.0   |                              |     |     |               | 2.0<br>4.0                                |     |       |             |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>B <sub>n</sub> to CP | 7.0<br>7.0   |                              |     |     |               | 8.0<br>8.0                                |     | ns    | 2-6         |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>B <sub>n</sub> to CP  | 0<br>0       |                              |     |     |               | 0<br>0                                    |     | . 115 |             |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>A/\$ to CP           | 12.0<br>12.0 |                              |     |     |               | 13.0<br>13.0                              |     | ns    | 2-6         |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>A/S to CP             | 0<br>0       |                              |     |     |               | 0<br>0                                    |     |       |             |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW $B_{n-1}$ to CP         | 5.0<br>5.0   |                              |     |     |               | 5.0<br>5.0                                |     | ns    | 2-6         |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW $B_{n-1}$ to CP          | 1.0<br>1.0   |                              |     |     |               | 2.0<br>2.0                                |     |       |             |

| t <sub>W</sub> (L)                       | PL Pulse Width, LOW                             | 6.5          |                              |     |     |               | 7.0                                       |     | ns    | 2-4         |

| t <sub>W</sub> (H)<br>t <sub>W</sub> (L) | CP Pulse Width<br>HIGH or LOW                   | 7.0<br>7.0   |                              |     |     |               | 7.0<br>7.0                                |     | ns    | 2-4         |

| t <sub>rec</sub>                         | Recovery Time PL to CP                          | 6.0          |                              |     |     |               | 10.0                                      |     | ns    | 2-6         |