## SN10KHT5562, SN100KT5562 **OCTAL TTL/ECL BUS TRANSCEIVERS** WITH 3-STATE OUTPUTS

下5Z-11 D3538, JUNE 1990

- **ECL and TTL Output-Enable Inputs**

- Flow-Through Architecture Optimizes PCB Layout

- Center-Pin V<sub>CC</sub>, V<sub>EE</sub>, and GND **Configurations Minimize High-Speed Switching Noise**

- Package Options Include "Small Outline" Packages and Standard Plastic 300-mil

## description

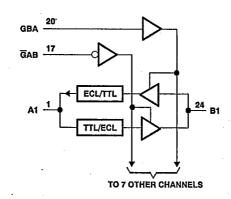

The SN10KHT5562 and SN100KT5562 are noninverting TTL/ECL transceivers designed to translate signals between ECL and TTL environments. The A port (TTL port) is designed to source 15 mA and sink 48 mA. The B port (ECL. port) is designed to drive a 50- $\Omega$  load terminated to -2 V.

The A and B ports have complementary outputenable inputs, both of which are ECL-compatible. When the A-port output enable (GBA) is high, the device transmits data from the B bus to the A bus. When GBA is low, the A outputs are in the high-impedance state. When GAB is low, the device transmits data from the A bus to the B bus; when GAB is high, the B outputs are in the high-impedance state.

When GAB is low and GBA is high, the device is in the isolation mode.

The \$N10KHT5562 is compatible with 10KH ECL and is characterized for operation from 0°C to

The SN100KT5562 is compatible with 100K ECL and is characterized for operation from 0°C to 85°C,

| DW OR NT PACKAGE<br>(TOP VIEW)                                         |                                                 |                                  |                                                                                        |

|------------------------------------------------------------------------|-------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------|

| A1[<br>A2]<br>A3[<br>A4[<br>Vcc[<br>GND[<br>GND[<br>GND[<br>A5[<br>A6[ | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | 24<br>23<br>22<br>21<br>20<br>19 | B1<br>  B2<br>  B3<br>  B4<br>  GBA<br>  VEE<br>  GND<br>  GAB<br>  B5<br>  B6<br>  B7 |

| A8[                                                                    | 12                                              | 13                               | B8                                                                                     |

## logic diagram (positive logic)

PRODUCT PREVIEW documents contain information on products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas instruments reserves the right to change or discontinue these products without notice.

Copyright @ 1990, Texas Instruments Incorporated

7-38

PRODUCT PREVIEW

POST OFFICE BOX 655303 \* DALLAS, TEXAS 75265