# **MP8831**

Single 10-Bit ADC with Digitally Controlled References

July 1997-1

#### **FEATURES**

- 1.67 MSPS Sampling Rate

- 10 bit ADC with  $< \pm 0.75$  LSB DNL

- Independent, Digitally Controlled ADC Offset & Full Scale Adjustments

- ADC Full Scale Range: 0V to 2.82V, with 10-Bit Resolution

- ADC Offset Range: 0.175V to 0.345V, with 6-Bit Resolution

- Update Rate: Pixel-by-pixel

- Single 5V Supply

- Low Power CMOS: 175mW (typ.)Power Down Mode: 1.0mW (typ.)

- Latch-up Free

- ESD Protection to over 2000V

#### **APPLICATIONS**

- Precision B/W & Color CCD Scanners

- Digital Copiers

- Digital Cameras

- Infra-Red Image Digitizers

### **BENEFITS**

- Improved Pixel-to-Pixel Calibration Accuracy Compared to Software Corrections

- Reduced Part Count & System Cost

- Lower Power Consumption & Power Down for Battery Applications

#### **GENERAL DESCRIPTION**

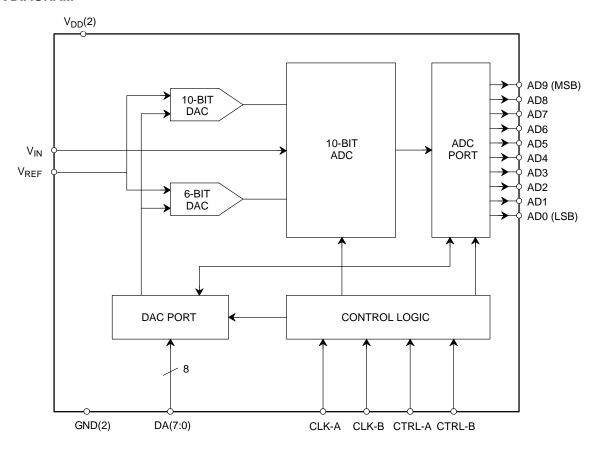

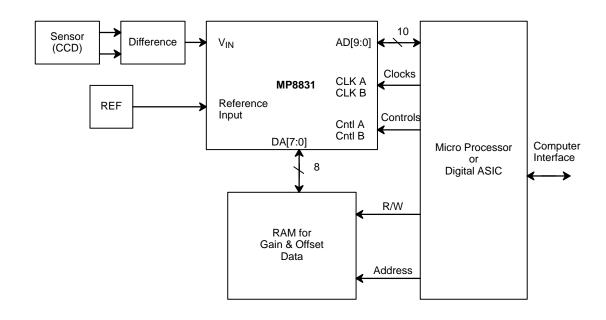

The MP8831 is a 1.67MSPS image digitizing chip that includes a 10-bit A/D Converter with digitally controlled references. This allows imaging systems to calibrate for individual pixel offset and gain errors. The offset can be adjusted from 0.175V to 0.345V in 64 steps (6 bit resolution), while the full scale range (i.e. peak to peak input range) is adjustable up to 2.82V in 1024 steps (10 bit resolution).

The A/D converter uses a subranging architecture to achieve high sample rates and low power consumption.

Our patented comparator design performs an on chip track & hold function with a low input capacitance. Our proprietary high speed DAC design is used to drive and update the ADC reference ladder at a 1.67MHz rate.

The MP8831 operates from a single +5V supply and an external 1V reference. Power consumption is typically only 180mW during conversion operation, and less than 1.0mW in power down mode. Specified for operation between -40°C to +85°C, the MP8831 is available in 28 lead SOIC (JEDEC) and PDIP packages.

#### ORDERING INFORMATION

| Part No. | Package                    | Operating<br>Temperature Range |

|----------|----------------------------|--------------------------------|

| MP8831AN | 28 Lead 300 Mil PDIP       | -40°C to +85°C                 |

| MP8831AS | 28 Lead 300 Mil JEDEC SOIC | -40°C to +85°C                 |

///////////

#### **BLOCK DIAGRAM**

Figure 1. Block Diagram

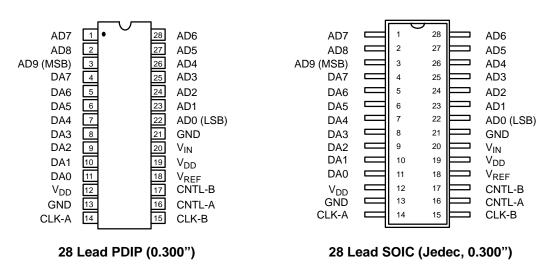

#### **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| Pin# | Symbol    | Description                                           |

|------|-----------|-------------------------------------------------------|

| 1    | AD7       | ADC Bus Bit 7.                                        |

| 2    | AD8       | ADC Bus Bit 8.                                        |

| 3    | AD9       | ADC Bus Bit 9 (MSB).                                  |

| 4    | DA7       | DAC Bus Bit 7 (MSB).                                  |

| 5    | DA6       | DAC Bus Bit 6.                                        |

| 6    | DA5       | DAC Bus Bit 5.                                        |

| 7    | DA4       | DAC Bus Bit 4.                                        |

| 8    | DA3       | DAC Bus Bit 3.                                        |

| 9    | DA2       | DAC Bus Bit 2.                                        |

| 10   | DA1       | DAC Bus Bit 1.                                        |

| 11   | DA0       | DAC Bus Bit 0 (LSB).                                  |

| 12   | $V_{DD}$  | Power Supply.                                         |

| 13   | GND       | Ground.                                               |

| 14   | CLK-A     | Controls Timing of ADC & DAC.                         |

| 15   | CLK-B     | Controls Timing of ADC & DAC.                         |

| 16   | CNTL-A    | Control The Operating Mode Of The Chip (See Table 1.) |

| 17   | CNTL-B    | Control The Operating Mode Of The Chip (See Table 1.) |

| 18   | $V_{REF}$ | Reference Input (1V) Sets Range of DACs.              |

| 19   | $V_{DD}$  | Power Supply.                                         |

| 20   | $V_{IN}$  | Analog Input.                                         |

| 21   | GND       | Ground.                                               |

| 22   | AD0       | ADC Bus Bit 0 (LSB).                                  |

| 23   | AD1       | ADC Bus Bit 1.                                        |

| 24   | AD2       | ADC Bus Bit 2.                                        |

| 25   | AD3       | ADC Bus Bit 3.                                        |

| 26   | AD4       | ADC Bus Bit 4.                                        |

| 27   | AD5       | ADC Bus Bit 5.                                        |

| 28   | AD6       | ADC Bus Bit 6.                                        |

## DC ELECTRICAL CHARACTERISTICS

Test Conditions:  $V_{DD}$  = 5V, GND = 0V and  $T_A$  = 25°C Unless Otherwise Specified

| Symbol            | Parameter                        | Min. | Тур.                     | Max.     | Unit | Conditions                                                                                                                |  |

|-------------------|----------------------------------|------|--------------------------|----------|------|---------------------------------------------------------------------------------------------------------------------------|--|

| ADC               |                                  |      |                          |          |      |                                                                                                                           |  |

| n                 | Number of Bits                   | 10   |                          |          | Bits |                                                                                                                           |  |

| FS                | Max Effective Sample Rate        | 1.67 |                          |          | MSPS |                                                                                                                           |  |

| DNL               | Differential Non-Linearity       | -1.0 | <u>+</u> 0.75            | 2.0      | LSB  | Gain DAC=1/2 scale, offset DAC=ZS                                                                                         |  |

| DNL               | Differential Non-Linearity       | -1.0 |                          | 2.0      | LSB  | Gain DAC=FS, offset DAC=ZS                                                                                                |  |

| INL               | Integral Non-Linearity           | -3   |                          | 3        | LSB  | Gain DAC=1/2 scale, offset DAC=ZS, best fit straight line                                                                 |  |

| INL               | Integral Non-Linearity           | -2   |                          | 2        | LSB  | Gain DAC=FS, offset DAC=ZS, best fit straight line                                                                        |  |

| EZS               | Zero Scale Error                 |      | -30                      |          | mV   |                                                                                                                           |  |

| EFS               | Full Scale Error                 |      | 20                       |          | mV   |                                                                                                                           |  |

| A <sub>INPP</sub> | DC input Range                   | GND  |                          | $V_{DD}$ | V    | A <sub>IN</sub> can swing from GND to V <sub>DD</sub> .<br>Digitizing range is set by DAC<br>codes.                       |  |

| C <sub>IN</sub>   | Input Capacitance                |      | 10                       | 20       | pF   |                                                                                                                           |  |

| Offset DAC        |                                  |      |                          |          |      |                                                                                                                           |  |

| n                 | Number of Bits                   | 6    |                          |          | Bits |                                                                                                                           |  |

| DNL               | Differential Non-Linearity       | -0.5 |                          | 0.5      | LSB  | Measured at bottom of ADC reference ladder through a switch.                                                              |  |

| INL               | Integral Non-Linearity           | -1   |                          | 1        | LSB  | Measured at bottom of ADC reference ladder through a switch.                                                              |  |

| VO <sub>ZS</sub>  | Effective Zero Scale Voltage     |      | 0.178                    |          | V    | Measured at bottom of ADC reference ladder through a switch.                                                              |  |

| VO <sub>FS</sub>  | Effective Full Scale Voltage     |      | 0.348                    |          | V    | Measured at bottom of ADC reference ladder through a switch.                                                              |  |

| MOC               | Maximum Change per<br>Conversion |      |                          | 100      | % FS | After specified change in DAC setting, the ADC should output the same code $\pm$ 2LSB, assuming analog input is constant. |  |

| ts-od             | Settling Time                    |      | 300                      |          | ns   | Not tested. Guaranteed by design.                                                                                         |  |

| Gain DAC          |                                  |      |                          |          |      |                                                                                                                           |  |

| n                 | Number of Bits                   | 10   |                          |          | Bits |                                                                                                                           |  |

| DNL               | Differential Non-Linearity       | -1   |                          | 1        | LSB  | Measured at top of ADC reference ladder through a switch.                                                                 |  |

| INL               | Integral Non-Linearity           | -2   |                          | 2        | LSB  | Measured at top of ADC reference ladder through a switch, (BFSL).                                                         |  |

| VG <sub>ZS</sub>  | Effective Zero Scale Voltage     |      | VO <sub>FS</sub><br>0.00 |          | V    | Measured at top of ADC reference ladder through a switch. Offset DAC = ZS                                                 |  |

# DC ELECTRICAL CHARACTERISTICS (CONT'D)

| Symbol             | Parameter                                                           | Min. | Тур.                     | Max.   | Unit | Conditions                                                                                                                 |  |

|--------------------|---------------------------------------------------------------------|------|--------------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------|--|

| Gain DAC (C        | Gain DAC (Cont'd)                                                   |      |                          |        |      |                                                                                                                            |  |

| VG <sub>FS</sub>   | Effective Full Scale Voltage                                        |      | VO <sub>FS</sub><br>2.82 |        | V    | Measured at top of ADC reference ladder through a switch. Offset DAC = ZS                                                  |  |

| MGC                | Maximum Change per<br>Conversion                                    |      |                          | 20     | % FS | After specified change in DAC setting, the ADC should output the same code $\pm$ 1 LSB, assuming analog input is constant. |  |

| ts-od              | Settling Time                                                       |      | 300                      |        | ns   | Not Tested. Guaranteed by design.                                                                                          |  |

| Digital Char       | acteristics                                                         |      |                          |        |      |                                                                                                                            |  |

| V <sub>IH</sub>    | Digital Input High Voltage                                          | 3.5  |                          |        | V    |                                                                                                                            |  |

| $V_{IL}$           | Digital Input Low Voltage                                           |      |                          | 1.5    | V    |                                                                                                                            |  |

| V <sub>OH</sub>    | Digital Output High Voltage                                         | 4.5  |                          |        | V    | While sourcing 2mA.                                                                                                        |  |

| $V_{OL}$           | Digital Output Low Voltage                                          |      |                          | 0.5    | V    | While sinking 2mA.                                                                                                         |  |

| l <sub>OZ</sub>    | High-Z Leakage                                                      |      |                          | 10     | μΑ   | When inputs are idle or reading DAC data.                                                                                  |  |

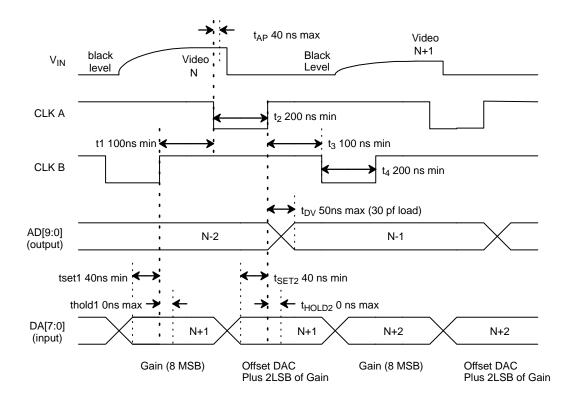

| Digital Timir      | ng Specifications (Convert Mode)                                    |      |                          |        |      |                                                                                                                            |  |

| t <sub>DV</sub>    | Data Valid Delay (Rising Edge<br>CLK-A to AD[9:0]<br>New Data Valid |      | 30                       | 50     | ns   | With 30 pF load on each pin.<br>AD[9:0]                                                                                    |  |

| t <sub>SET1</sub>  | DAbus Setup Time 1                                                  | 40   |                          |        | ns   | DA[7:0] to rising edge CLK-B.                                                                                              |  |

| t <sub>SET2</sub>  | DAbus Setup Time 2                                                  | 40   |                          |        | ns   | DA[7:0] to rising edge CLK-A.                                                                                              |  |

| t <sub>HOLD1</sub> | DAbus Hold Time 1                                                   |      |                          | 0      | ns   | Rising edge CLK-B to DA[7:0].                                                                                              |  |

| t <sub>HOLD2</sub> | DAbus Hold Time 2                                                   |      |                          | 0      | ns   | Rising edge CLK-A to DA[7:0].                                                                                              |  |

| t <sub>1</sub>     | Clock Timing                                                        | 100  | 200                      |        | ns   | Rising edge CLK-B to falling edge CLK-A.                                                                                   |  |

| t <sub>2</sub>     | Clock Timing                                                        | 200  | 200                      | 25,000 | ns   | Negative pulse width CLK-A.                                                                                                |  |

| t <sub>3</sub>     | Clock Timing                                                        | 100  | 200                      | 25,000 | ns   | Rising edge CLK-A to falling edge CLK-B.                                                                                   |  |

| t <sub>4</sub>     | Clock Timing                                                        | 200  | 200                      | 25,000 | ns   | Negative pulse width CLK-B.                                                                                                |  |

# DC ELECTRICAL CHARACTERISTICS (CONT'D)

| Symbol                   | Parameter                                                  | Min. | Тур. | Max. | Unit | Conditions                                                                                                                               |  |

|--------------------------|------------------------------------------------------------|------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------|--|

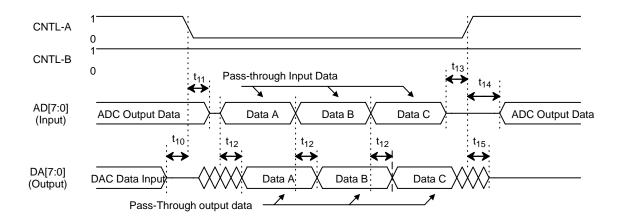

| Pass-Through Mode AD=>DA |                                                            |      |      |      |      |                                                                                                                                          |  |

| t <sub>10</sub>          | DAbus Release to CNTL-A Falling Edge                       | 0    |      |      | ns   | External ckts must stop driving DA-bus by the time CNTL-A falls.                                                                         |  |

| t <sub>11</sub>          | CNTL-A Falling Edge to ADbus<br>Release                    |      | 20   | 40   | ns   | Delay from falling edge CNTL-A until chip stops driving ADC data on ADbus. External ckts may not drive data onto ADbus before this time. |  |

| t <sub>12</sub>          | Pass-Through Mode Propagation<br>Delay From ADbus to DAbus |      | 17   | 30   | ns   | CNTL-A=low, CNTL-B=high; 30 pF load.                                                                                                     |  |

| t <sub>13</sub>          | ADbus Release to CNTL-A<br>Rising Edge                     | 0    |      |      | ns   | External ckts must stop driving AD-bus by the time CNTL-A rises.                                                                         |  |

| t <sub>14</sub>          | CNTL-A Rising Edge to ADbus Enable                         |      | 30   | 50   | ns   | After this time ADbus will output previous ADC data again.                                                                               |  |

| t <sub>15</sub>          | CNTL-A Rising Edge to DAbus<br>Release                     |      | 20   | 40   | ns   | Delay from rising edge CNTL-A until chip stops driving data on DAbus. External ckts may not drive data onto DAbus before this time.      |  |

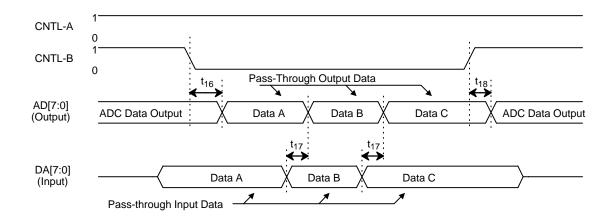

| Pass-Through             | gh Mode DA=>AD                                             |      |      |      |      |                                                                                                                                          |  |

| t <sub>16</sub>          | CNTL-B Falling Edge to ADbus<br>Pass-through Data Valid    |      | 30   | 50   | ns   | Time required for ADbus change from ADC data to DAbus pass-through data.                                                                 |  |

| t <sub>17</sub>          | Pass-Through Mode Propagation Delay From DAbus to ADbus    |      | 19   | 35   | ns   | CNTL-A=high, CNTL-B=low; 30 pF load.                                                                                                     |  |

| t <sub>18</sub>          | CNTL-B Rising Edge to ADbus<br>ADC Data Valid              |      | 30   | 50   | ns   | Time required for ADbus change from DAbus pass-through data to ADC data.                                                                 |  |

| Power Supply             |                                                            |      |      |      |      |                                                                                                                                          |  |

| $V_{DD}$                 | Operating Voltage                                          | 4.5  | 5    | 5.5  | V    |                                                                                                                                          |  |

| $I_{DD}$                 | Operating Current                                          | 30   | 35   | 40   | mA   |                                                                                                                                          |  |

|                          | Power Down I <sub>DD</sub>                                 |      | 0.2  | 0.5  | mA   |                                                                                                                                          |  |

#### Specifications are subject to change without notice

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND0.3 to           | o 6 V | Lead Temperature (soldering, 10 sec) | +300°C     |

|----------------------------------------|-------|--------------------------------------|------------|

| All Inputs                             | 0.5   | ESD Rating/Latch-up 20               | 000V/100mA |

| All Inputs V <sub>DD</sub> +0.5 to GND | 0.5   | Package Power Dissipation            | 850mW      |

| Storage Temperature65°C to +1          | 50°C  | Derate above 75°C                    | 12mW/°C    |

| A                                      |       |                                      |            |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

<sup>&</sup>lt;sup>2</sup> Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. All inputs have protection diodes which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

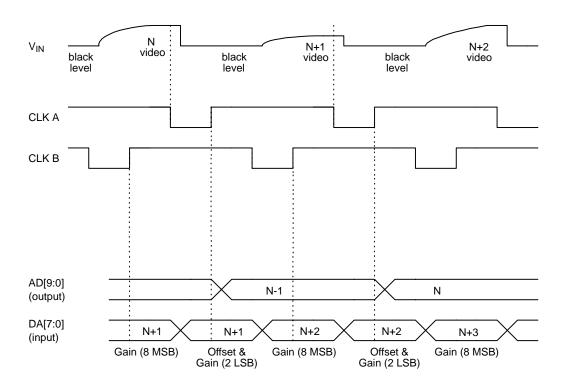

**Figure 2. Convert Mode Operation**

| Cntl A | Cntl B | Operation Mode                                                   |  |  |  |

|--------|--------|------------------------------------------------------------------|--|--|--|

| 0      | 0      | Test mode ( $V_{RT} \Rightarrow AD[9]; V_{RB} \Rightarrow AD[8]$ |  |  |  |

| 0      | 1      | Pass-through mode AD[7:0] ⇒ DA[7:0]                              |  |  |  |

| 1      | 0      | Pass-through mode DA[7:0] ⇒ AD[7:0]                              |  |  |  |

| 1      | 1      | Convert mode                                                     |  |  |  |

**Table 1. Truth Table**

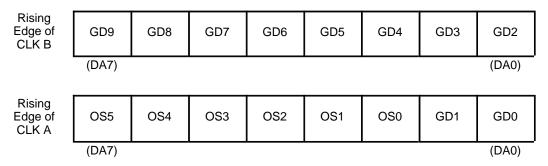

- (GD9-GD0 is the gain DAC data, OS5-OS0 is the offset DAC data)

- Forcing GD1 & GD0 to 0 gives an 8 bit resolution gain DAC, but will simplify the I/O.

**Table 2. DAC Data Format**

Figure 3. Convert Mode Timing Diagram

Figure 4. Pass-Through Mode (AD=>DA) Timing Diagram

Figure 5. Pass-Through mode (DA=>AD) Timing Diagram

#### **OPERATION MODES**

The two signals CNTL-A & CNTL-B are used to put the chip into one of the four operation modes.

# Convert Mode (CNTL-A=high, CNTL-B=high)

This is the normal operation mode. Data for the offset & gain DACs is read in from the DA bus, and ADC data is output on the AD bus.

Pass-Through Mode

AD => DA (CNTL-A=low, CNTL-B=high)

DA => AD (CNTL-A=high, CNTL-B=low)

The pass-through modes are intended to allow the digital ASIC (or  $\mu$ processor, DSP, etc) to read from and write to the memory bank which holds the gain and offset DAC data, without requiring a separate data bus between the ASIC and the memory. In the AD => DA mode, pins AD[7:0] are programmed as digital inputs, and they simply pass data (through an internal bus) to pins DA[7:0] which are programmed as digital outputs. In the DA => AD mode things are reversed, DA[7:0] are programmed as

digital inputs and AD[7:0] are programmed as digital outputs. Please note that when DA[7:0] are used as inputs they accept TTL level signals, when AD[7:0] are used as inputs they accept CMOS level inputs.

While in either of the pass-through modes, CLK-A & CLK-B should both be held high.

#### Test Mode (CNTL-A=low, CNTL-B=low)

This mode is used to test the gain and offset DACs. The ADC reference voltages are output on the two MSB pins of the AD bus,  $V_{RT}$  on pin AD9 and  $V_{RB}$  on pin AD8. The data from the DA bus is read in to the DACs the same as during normal conversion operation (i.e. on the rising edges of CLK-A & CLK-B).

### **Controlling ADC Gain and Offset**

The input range of the ADC is set by the voltages at its top  $(V_{RT})$  and bottom  $(V_{RB})$  reference nodes. The Offset DAC sets the voltage at the  $V_{RB}$  node. The Gain DAC sets the span  $V_{RT}$ - $V_{RB}$ . The following equations relate the DAC codes to the voltages at  $V_{RB}$  &  $V_{RT}$ :

$V_{REF}$  = voltage at  $V_{REF}$ , pin 18

D<sub>OFFSET</sub> = Offset DAC code, 6 bits, OS[5:0]

D<sub>GAIN</sub> = Gain DAC code, 10 bits, GD[9:0]

$$V_{RB} = \left(0.178 + \frac{D_{OFFSET}}{64} \cdot 0.170\right) \cdot V_{REF}$$

$$V_{RT} - V_{RB} = \left(\frac{D_{GAIN}}{1024}\right) \cdot 2.82 \cdot V_{REF}$$

$$V_{RT} \; = \; \left\{ \left( \frac{D_{GAIN}}{1024} \right) \; \cdot \; 2.82 \; \cdot \; V_{REF} \; \right\} \; + \; \; V_{RB}$$

#### Note:

The output of the Gain DAC becomes non-linear when  $V_{RT}$ , calculated using the above equations, is higher than  $V_{DD}$ -1.6V. The ADC itself remains linear, but its input range, set by the DACs, deviates from the calculated values. This can only happen if  $V_{REF}$  is larger than 1.068V.

Figure 6. General Scanner System Using the MP8831

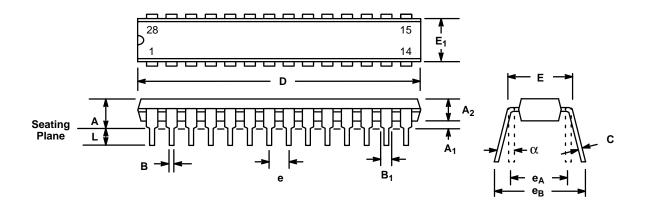

# 28 LEAD PLASTIC DUAL-IN-LINE (300 MIL PDIP)

Rev. 1.00

|                | INC   | HES       | MILLIN | METERS |

|----------------|-------|-----------|--------|--------|

| SYMBOL         | MIN   | MAX       | MIN    | MAX    |

| Α              | 0.145 | 0.210     | 3.68   | 5.33   |

| A <sub>1</sub> | 0.015 | 0.070     | 0.51   | 1.78   |

| A <sub>2</sub> | 0.115 | 0.195     | 2.92   | 4.95   |

| В              | 0.014 | 0.024     | 0.36   | 0.56   |

| B <sub>1</sub> | 0.030 | 0.070     | 0.76   | 1.78   |

| С              | 0.008 | 0.014     | 0.20   | 0.38   |

| D              | 1.345 | 1.400     | 34.16  | 35.56  |

| Е              | 0.300 | 0.325     | 7.62   | 8.26   |

| E <sub>1</sub> | 0.265 | 0.310     | 7.11   | 7.49   |

| е              | 0.10  | 00 BSC    | 2.5    | 4 BSC  |

| e <sub>A</sub> | 0.30  | 0.300 BSC |        | 2 BSC  |

| e <sub>B</sub> | 0.310 | 0.430     | 7.87   | 10.92  |

| L              | 0.115 | 0.150     | 2.92   | 3.81   |

| α              | 0°    | 15°       | 0°     | 15°    |

Note: The control dimension is the inch column

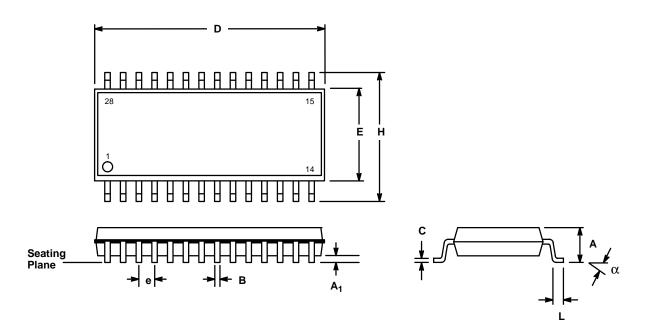

# 28 LEAD SMALL OUTLINE (300 MIL JEDEC SOIC)

Rev. 1.00

|        | INC   | HES    | MILLIN | METERS |

|--------|-------|--------|--------|--------|

| SYMBOL | MIN   | MAX    | MIN    | MAX    |

| Α      | 0.093 | 0.104  | 2.35   | 2.65   |

| A1     | 0.004 | 0.012  | 0.10   | 0.30   |

| В      | 0.013 | 0.020  | 0.33   | 0.51   |

| С      | 0.009 | 0.013  | 0.23   | 0.32   |

| D      | 0.697 | 0.713  | 17.70  | 18.10  |

| Е      | 0.291 | 0.299  | 7.40   | 7.60   |

| е      | 0.0   | 50 BSC | 1.2    | 7 BSC  |

| Н      | 0.394 | 0.419  | 10.00  | 10.65  |

| L      | 0.016 | 0.050  | 0.40   | 1.27   |

| α      | 0°    | 8°     | 0°     | 8°     |

Note: The control dimension is the millimeter column

### **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1996 EXAR Corporation Datasheet July 1997

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

**T©**M<sup>™</sup>