262,144 x 4 CMOS Fully Featured Video RAM

#### **Features**

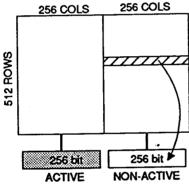

DRAM organized as 262,144 words x 4 bits. SAM organized as 512 words x 4 bits.

RAM Access Times of 100,120 ns. SAM Access Time of 25,30 ns.

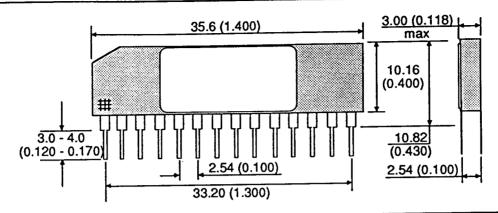

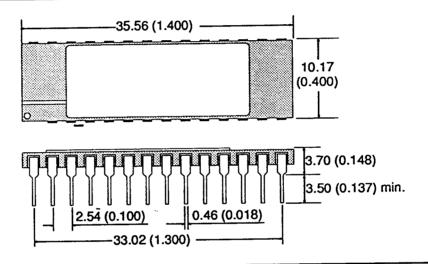

Available in Pinned and Surface Mount Packages.

Operating Power 715 mW (maximum) Low Power Standby 55 mW (maximum)

Dual Port Accessibility - Simultaneous and Asynchronous Access from the DRAM and SAM Ports

Bi-directional Data Transfer Function between the DRAM and the Serial Data Register.

$4 \times 4$  Block Write feature for Fast Area Fill Operations. As Many as Four Locations Written Per Cycle from an On-chip Colour Register.

Mask Write function for Selective Write to each RAM I/O, with two Write-per-bit Modes to Simplify System Design.

Split Serial Data Register for Simplified Real-time Register Reload.

RAM Output Enable Allows Direct Connection of W/IO and Address Lines to Simplify System Design.

CAS-before-RAS and Hidden Refresh, with 512 Refresh Cycles every 8 ms.

Up to 33 MHz Uninterrupted Serial Data Streams.

Fast Page-mode Operation for faster access.

All Inputs and Outputs Directly TTL Compatible (except QSF pin which is open drain type).

May be Processed to MIL-STD-883D Method 5004.

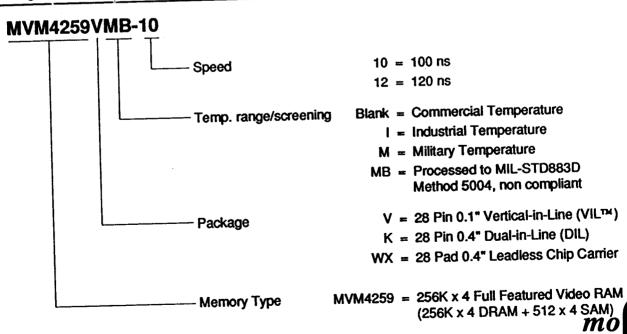

# 256K x 4 VideoRAM

MVM4259-10/12

Issue 2.0 : February 1992

#### **PRELIMINARY**

| Pin Definiti                                                                                                    | on                                                                                                                       |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SC C<br>SIO1 C<br>SIO2 C<br>DT/OE C<br>W1/IO1 C<br>W2/IO2 C<br>WB/WE C<br>NC C<br>RAS C<br>A8 C<br>A6 C<br>A5 C | 3 26 SIO3 4 25 SE 5 24 W4/IO4 6 23 W3/IO3 7 V,K,WX 22 DSF 8 PACKAGE 21 CAS 9 TOP VIEW 20 QSF* 10 19 A0 11 18 A1 12 17 A2 |  |  |  |  |  |

| Pin Function                                                                                                    | ons                                                                                                                      |  |  |  |  |  |

| A0~A8                                                                                                           | Address inputs                                                                                                           |  |  |  |  |  |

| W/IO1~4                                                                                                         | RAM Data Input/Output                                                                                                    |  |  |  |  |  |

| SIO1~4                                                                                                          | SAM Data Input/Output                                                                                                    |  |  |  |  |  |

| RAS                                                                                                             | Row Address Strobe                                                                                                       |  |  |  |  |  |

| CAS                                                                                                             | Column Address Strobe                                                                                                    |  |  |  |  |  |

| D1/OE                                                                                                           | Data Transfer/Output Enable                                                                                              |  |  |  |  |  |

| WB/WE                                                                                                           | Write per bit/Write Enable                                                                                               |  |  |  |  |  |

SC Serial Clock

SE Serial Enable

DSF Special Function Select

DSF Special Function SelectQSF\* Split-Register Activity Status

V<sub>∞</sub> Power (+5V)

GND Ground

NC No Connect

THIS PIN IS OPEN DRAIN

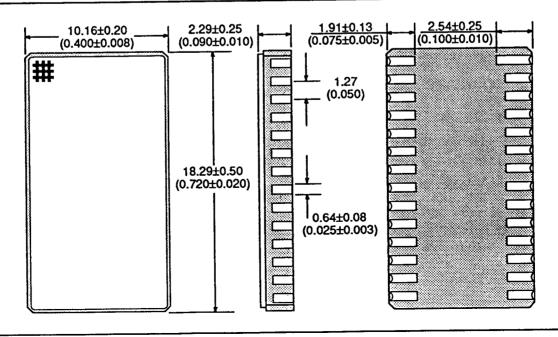

Package Details Package Dimensions and details on page 39.

| Pin Count       | Description                            | Package Type       | Material | Pinout       |

|-----------------|----------------------------------------|--------------------|----------|--------------|

| 28              | 0.1" Vertical-in-Line(VIL™)            | V                  | Ceramic  | <b>JEDEC</b> |

| 28              | 0.4" Leadless Chip carrier (LCC)       | wx                 | Ceramic  | <b>JEDEC</b> |

| 28              | 0.4" Dual-in-Line (DIL)                | Κ                  | Ceramic  | JEDEC        |

| VIL™ is a trade | emark of Mosaic Semiconductor Inc. U.S | . Patent Number 31 | 6,251.   |              |

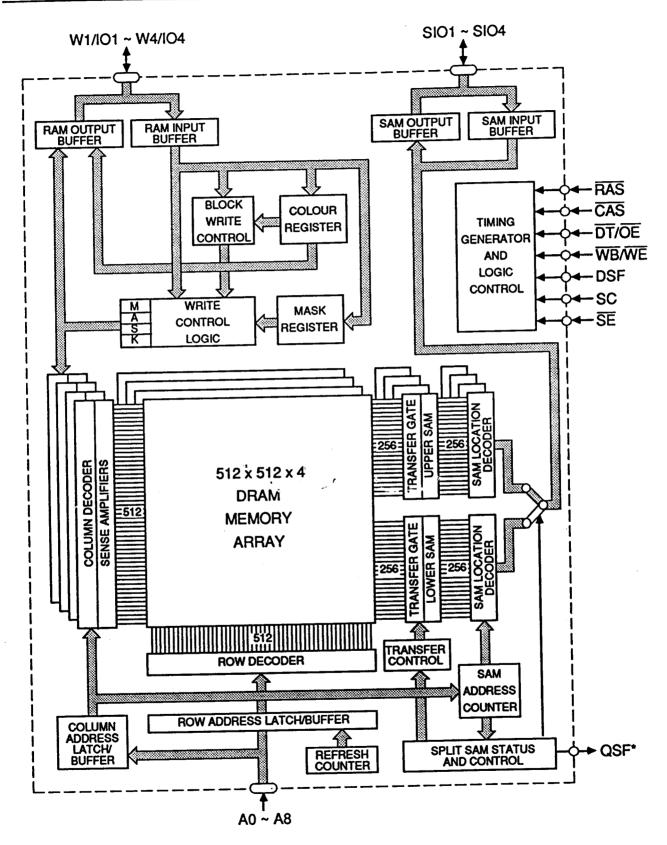

#### **Block Diagram**

\* Note that the QSF pin is an Open Drain output (see page 8 for details).

## MVM4259 Operation Modes

# MVM4259 Operation Truth Table

|     |     |       |     | IAI A IAI 4 C         | o operation tre       |                       | ,                           |

|-----|-----|-------|-----|-----------------------|-----------------------|-----------------------|-----------------------------|

| ſ   | DSF | at CA | S Ł | L                     | L                     | Н                     | Н                           |

| Ì   |     | at RA |     | L                     | Н                     | L                     | Н                           |

| L   | Х   | X     | Х   | CAS Before            | RAS Refresh           |                       |                             |

| Н   | L   | L     | L   | Write Transfer        | Write Transfer        | Write Transfer        | Write Transfer              |

| H   | L   | L     | Н   | Pseudo Write Transfer | AALITE LITERISIE      | Pseudo Write Transfer |                             |

| Н   | L   | Н     | X   | Read Transfer         | Split Read Transfer   | Read Transfer         | Split Read Transfer         |

| Н   | Н   | L     | X   | Mask Read / Write     | Persistent Mask Write | Mask Block Write      | Persistent Mask Block Write |

| H   | Н   | Н     | X   | Normal Read / Write   | Load Mask             | Block Write           | Load Colour                 |

| CAS | DT/ |       | SE  |                       |                       |                       |                             |

|     | ŌE  | WE    |     |                       |                       |                       |                             |

# MVM4259 Functional Truth Table

| (1)<br>Ш     |     | •   | RAS | ,   | _  | CAS | ADDF               | RESS              | W/            |                 |                                                      |

|--------------|-----|-----|-----|-----|----|-----|--------------------|-------------------|---------------|-----------------|------------------------------------------------------|

| TYPE         |     | DT/ | WB/ |     |    |     |                    |                   | 5.6.          | CAS             | FUNCTION                                             |

| $\mathbf{F}$ | CAS | ŌĒ  | WE  | DSF | SE | DSF | RASI               | <u>CAS</u> ↓      | RAS           | WEI             |                                                      |

| R            | L   | X   | Х   | Х   | X  | Х   | Х                  | X                 | X             | Х               | CAS Before RAS Refresh                               |

| T            | Н   | L   | L   | L   | L  | Х   | Row<br>Address     | Tap<br>Point      | Х             | Х               | Register to Memory Transfer (Write Transfer)         |

| Т            | Н   | L   | L   | Н   | X, | Х   | Row<br>Address     | Tap<br>Point      | X             | X               | Alternate Transf <u>er</u> Write (Independent of SE) |

| T            | Н   | L   | L   | L   | 7  | Х   | Refresh<br>Address | Tap<br>Point      | Х             | X               | Serial Write Mode Enable<br>(Pseudo Transfer Write)  |

| ī            | Н   | L   | Н   | L   | Х  | Х   | Row<br>Address     | Tap<br>Point      | Х             | Х               | Memory to Register Transfer (Read Transfer)          |

| Т            | Н   | L   | Н   | Н   | Х  | Х   | Row<br>Address     | Tap<br>Point      | Х             | Х               | Split Register Transfer Read<br>(Must Reload Tap)    |

| R            | Н   | Н   | L   | L   | Х  | L   | Row<br>Address     | Column<br>Address | Write<br>Mask | Valid<br>Data   | Load and use Write Mask,<br>Write Data to DRAM       |

| R            | Н   | Н   | L   | L   | Х  | Н   | Row<br>Address     | Column<br>A2 - A8 | Write<br>Mask | Address<br>Mask | Load and use Write Mask,<br>Block Write to DRAM      |

| R            | Н   | Н   | L   | Н   | Х  | L   | Row<br>Address     | Column<br>Address | Х             | Valid<br>Data   | Persistent Mask Write,<br>Write Data to DRAM         |

| R            | H   | Н   | L   | Н   | Х  | Н   | Row<br>Address     | Column<br>A2 - A8 | Х             | Address<br>Mask | Persistent Mask Write<br>Block Write to DRAM         |

| R            | Н   | Н   | Н   | L   | X  | L   | Row<br>Address     | Column<br>Address | X             | Valid<br>Data   | Normal DRAM Read/Write (Non Masked)                  |

| R            | Н   | Н   | Н   | L   | Х  | Н   | Row<br>Address     | Column<br>A2 - A8 | Х             | Address<br>Mask | Block Write to DRAM (Non Masked)                     |

| R            | Н   | Н   | Н   | Н   | X  | L   | Refresh<br>Address | Х                 | X             | Write<br>Mask   | Load Write Mask                                      |

| R            | Н   | Н   | Н   | Н   | X  | Н   | Refresh<br>Address |                   | Х             | Colour<br>Data  | Load Colour Register                                 |

Note R = Random access operation <math>T = Transfer operation.

## **GENERAL DESCRIPTION**

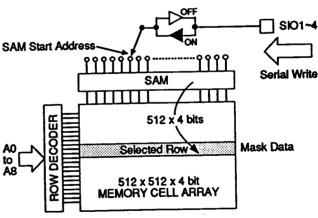

The MVM4259 multiport video RAM is a fully featured dual ported memory device consisting of a 262,144 word by 4 bit dynamic Random Access Memory (RAM), and a 512 word by 4 bit Serial Access Memory (SAM). Three basic types of operation are supported: random access to and from the RAM, serial access to and from the SAM and bidirectional transfer between any row in the RAM and the SAM. Except during transfer operations, the MVM4259 can be accessed simultaneously and asynchronously from the RAM and SAM ports.

The MVM4259 is provided with several advanced features which allow higher system level bandwidth and simplify design on both the RAM and SAM ports. On the RAM port greater pixel draw rates can be achieved by using the Block Write mode, allowing as many as 16 bits of data to be written to the RAM in each CAS cycle. Also on the RAM port, a Write Mask Register provides a persistent write per bit mode without repeated mask loading.

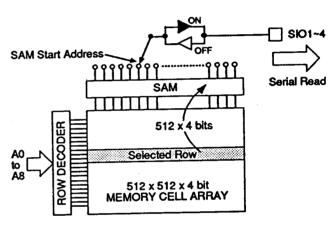

The SAM is divided into two halves, so while one half is being read from the SAM port the other half can be loaded from the RAM. The QSF output pin indicates which half of the SAM is currently being accessed. The SAM can also be configured in input mode to accept serial data from an external device and can operate at clock rates of upto 33MHz.

#### **PIN FUNCTIONS**

## Data Transfer/Output Enable (DT/OE)

This pin is a multifunction pin, selecting either register or random access operation as RAS falls. In random access DRAM mode, DT/OE must be high as RAS falls, and DT/OE is used as an Output Enable pin. When DT/OE is held high, the W/IO outputs are in the high impedance state to prevent overlap between the address and the DRAM data. This allows multiplexed address/data, but does not allow the use of the early Write Cycle.

If DT/OE is low as RAS falls, a data transfer operation is initiated between the RAM and SAM ports, in which the 512 bit positions in the serial register are connected to the bit lines.

## Address Inputs (A0~A8)

The 18 bits required to decode one of 262,144 cell locations within the DRAM array of the MVM4259 are multiplexed onto nine address input pins. Nine row address bits are latched on the falling edge of RAS, and the nine column address bits are latched on the falling edge of CAS. All addresses must be stable on or before these falling edges.

## Row Address Strobe (RAS)

The RAS control input latches the states of the row address, WB/WE, DT/OE, SE and CAS onto the chip to begin the various DRAM and transfer functions of the MVM4259 as shown in the Function Table. RAS has minimum and maximum pulse widths and a minimum precharge requirements which must be met for correct device operation. The RAM port is placed in standby mode when RAS is held high.

## Column Address Strobe (CAS)

The CAS input latches the column address and DSF states to control either Read/Write operations or special Block Write features. CAS has minimum and maximum pulse widths and a minimum precharge requirements which must be met for correct device operation. CAS also acts as an output enable for the output buffers on the RAM port.

## Mask Write/Write Enable (WB/WE)

This pin is also multifunction. When it is high at the falling edge of RAS during RAM port operations, the data in the memory array can be written in the same way as a standard DRAM. If it is low at RAS fall during RAM port operations, the Mask Write function is enabled. This pin also determines the direction of data transfer between the RAM and the SAM.

When WB/WE is high at RAS fall the data is transferred from RAM to SAM (Read Transfer); when it is low, the transfer is from the SAM to the RAM (Write Transfer).

# Mask Data/Data Input and Output (W/IO1 ~ W/IO4)

When the Mask Write mode is enabled, the data on the W/IO pins is latched into the Mask Register at the falling edge of RAS. Data is only written into the DRAM on data lines where the mask data is a "1" and writes are inhibited on lines where the mask data is "0". The mask data is valid for only one cycle.

DRAM data is written during Write or Read-Modify-Write Cycles, with the falling edge of WB/WE latching the data. In an early Write Cycle, WB/WE is brought low before CAS and the data is latched by CAS. In a delayed Write or Read-Modify-Write Cycle, CAS is already low, so the data is strobed in by WB/WE.

The three state output buffers are controlled by CAS and DT/OE. If CAS or DT/OE is held high the outputs remain in the high impedance (floating) state. Data will not appear on the outputs until both CAS and DT/OE are low, and the outputs will remain valid while they are low. In an early Write Cycle or a register transfer operation the outputs remain in the high impedance state for the entire cycle.

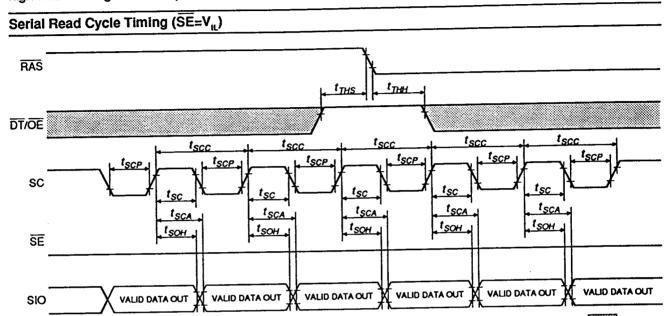

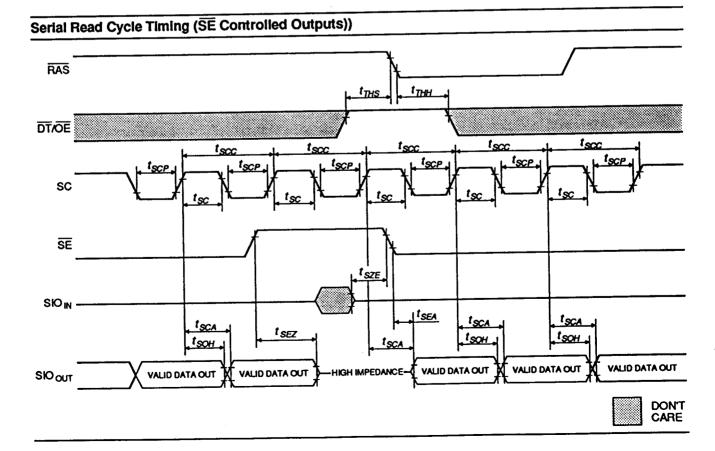

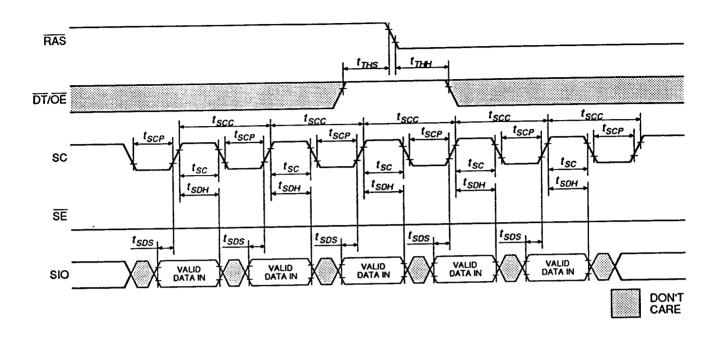

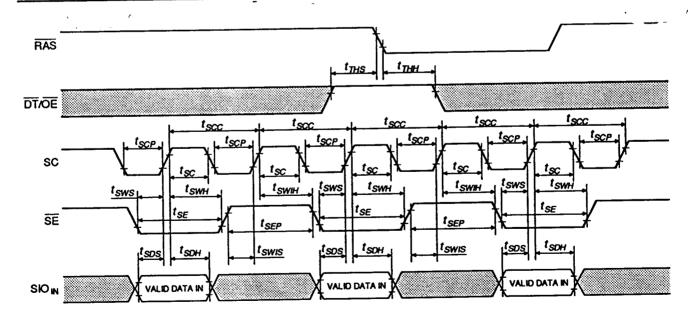

### Serial Clock (SC)

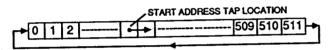

All operations of the SAM port are synchronised with the SC pin, with data being shifted in or out of the SAM registers at the rising edge of SC. In a Serial Read, the output data becomes valid on the SIO pins after t<sub>SCA</sub> from the rising edge of SC. The serial clock also increments the 9 bit (8 bit in Split Register mode) serial pointer which is used to select the SAM address. The pointer operates in wrap-around mode (when it reaches location 511 the next SC clock places it at location 0) through the SAM to select sequential locations after the starting location (or Tap Point), which is determined by the column address in the Read Transfer Cycle.

IMPORTANT NOTE: While SE is held high the serial clock is NOT DISABLED. Thus, any SC pulses will increment the internal serial address counter regardless of the state of SE. This ungated clock design minimizes the access time for serial output from SE low since the SC input buffer and serial address counter are not disabled by SE.

#### Serial Enable (SE)

This pin allows serial access operation. In a Read Cycle, SE is used as an output control, while in a Write Cycle it is used as a write enable control. Note that if SE is high serial access is disabled, but the SAM pointer is still incremented when SC is clocked.

# Special Function Control Input (DSF)

DSF is latched at the falling edge of RAS and CAS and enables the selection of various RAM and data transfer

operating modes. As well as normal DRAM modes, the MVM4259 special features of Persistent Mask Write, Block Write, Mask Block Write, Persistent Mask Block Write, Load Mask/Colour Register and Split Read Transfer can be invoked.

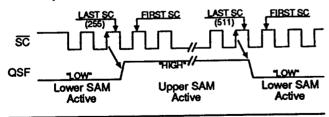

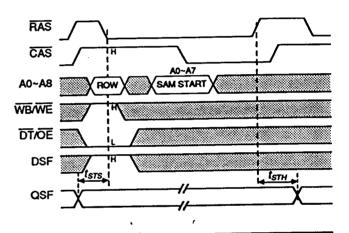

## Special Function Output (QSF)

This pin is an OPEN DRAIN output pin. During the split-register mode, QSF indicates which half of the SAM is being accessed. If QSF is on (low state), then the serial address pointer is accessing the lower 256 bits (0 to 255) of the SAM, while QSF off indicates that the pointer is accessing the upper 256 bits (256 to 511). After QSF has toggled a delay of  $t_{\rm STS}$  must be met before a Split Read Transfer operation can be performed on the inactive half of the split SAM.

If the detection of the zero to one transition of QSF is required an external pull-up resistor is needed, and the output rise time is determined by the load capacitance and the value of the resistor. The specification of the QSF switching time assumes a resistor value of  $820\Omega$  and a load capacitance of 50pF.

## Serial Data Input/Output (SIO1 ~ SIO4)

Serial input and output share common pins. The mode of these pins is determined by the most recent Read, Write or Pseudo Write Transfer Cycle. When a Read Transfer is inititaed, the SAM is in the output mode; when a Write or Pseudo Write cycle is now invoked, the SAM port switches from output to input, and during subsequent writes the SAM remains in the input mode.

# **Detailed Pin Description vs Operational Mode**

| PIN     | DRAM                                                                                                          | TRANSFER                                                 | SAM                   |

|---------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------|

| A0~A8   | Row and Column Address                                                                                        | Row and Tap Address                                      |                       |

| W/IO1~4 | Write Mask / Data IN, OUT                                                                                     |                                                          |                       |

| SIO1~4  |                                                                                                               |                                                          | Serial Data VO        |

| CAS     | Column Enable, Output Enable                                                                                  | Tap Address Strobe                                       |                       |

| RAS     | Row Enable                                                                                                    | Row Enable                                               |                       |

| WB/WE   | Write per bit/Write Enable                                                                                    | Transfer Write Enable                                    |                       |

| DSF     | Block Write Enable Persistent Write-per-Bit Enable Colour Register Load Enable Write per Bit Mask Load Enable | Split-register Enable<br>Alternate Write Transfer Enable |                       |

| QSF     |                                                                                                               |                                                          | Split Register Status |

| SE      |                                                                                                               | Serial in Mode Enable                                    | Serial Enable         |

| SC      |                                                                                                               |                                                          | Serial Clock          |

| DT/OE   | Output Enable                                                                                                 | Data Transfer                                            |                       |

### **RAM PORT OPERATION**

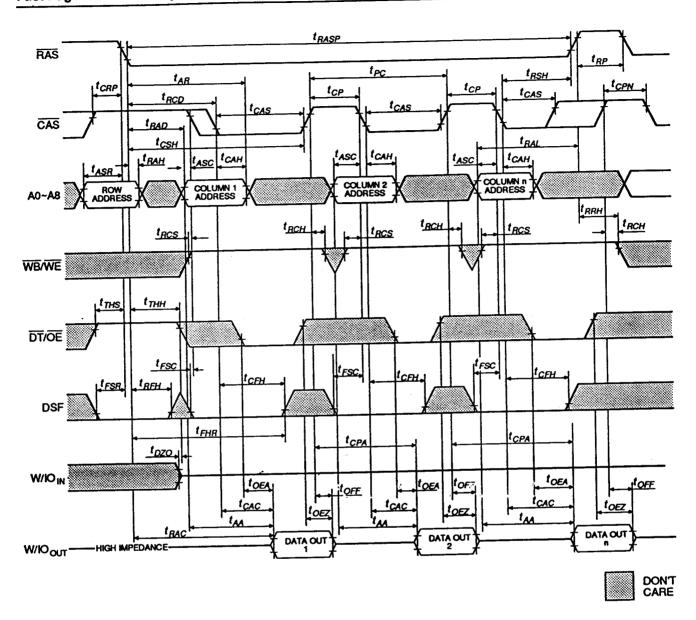

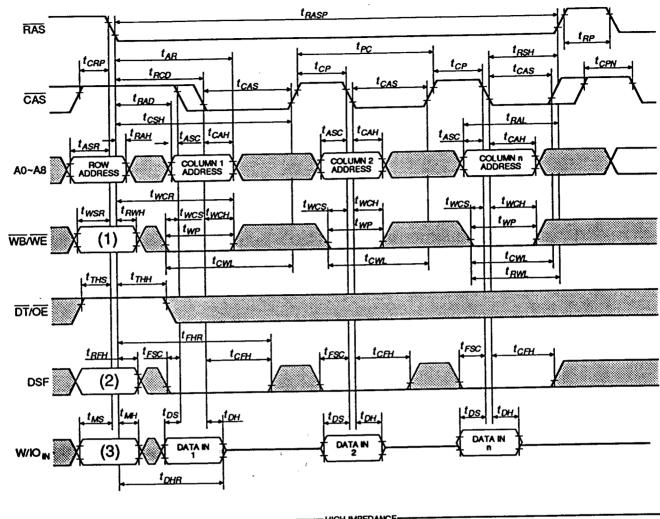

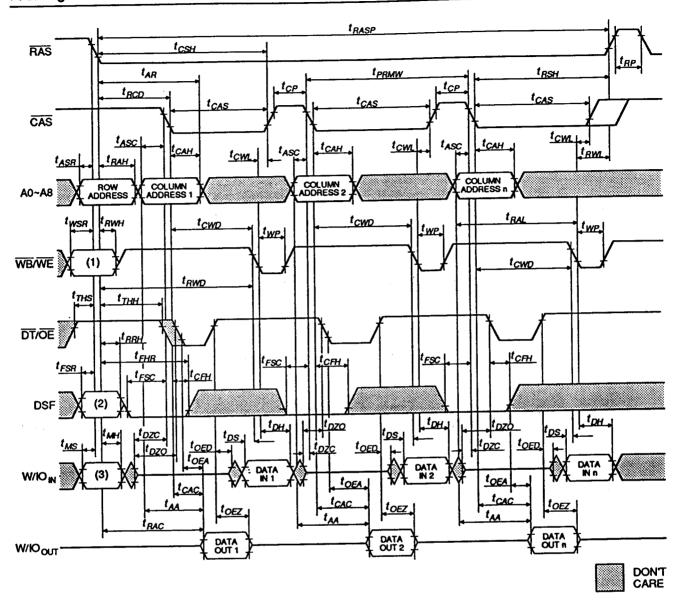

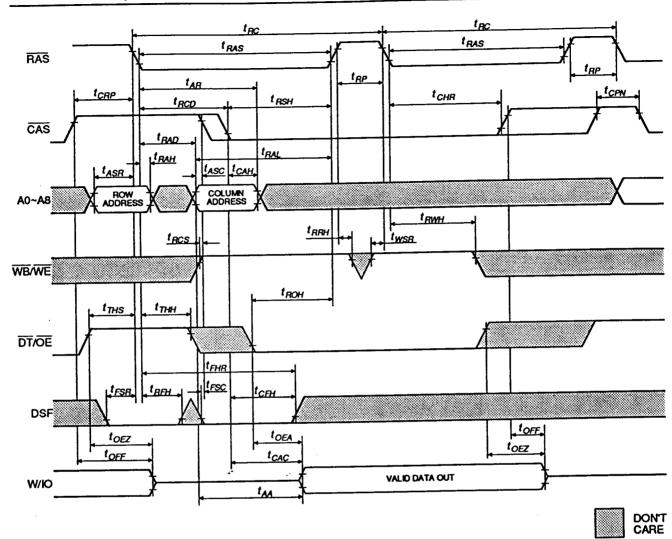

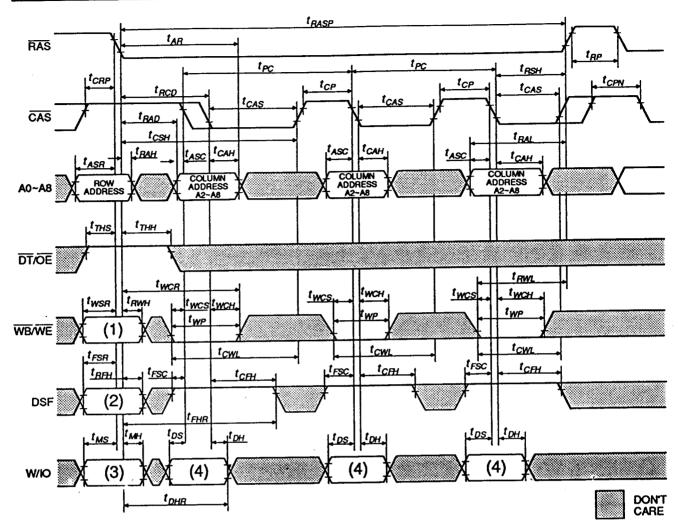

#### **Fast Page Mode Cycle**

Fast Page-mode operation allows faster access by keeping the same row address while selecting random column addresses. The times for row address setup, row address hold and address multiplex are eliminated, and the memory cycle time can be reduced by up to a third. The maximum number of columns which can be accessed is limited by the maximum RAS low time of 100µs.

For the initial page mode access, the output data is valid after the specified access times from RAS, CAS, column address and DT/OE. For all subsequent page read operations, the output data is valid after the specified access times from CAS, column address and DT/OE.

During Mask Write operations, the mask data is loaded at the falling edge of RAS and is maintained throughout the Page mode or Read-Modify-Write cycles.

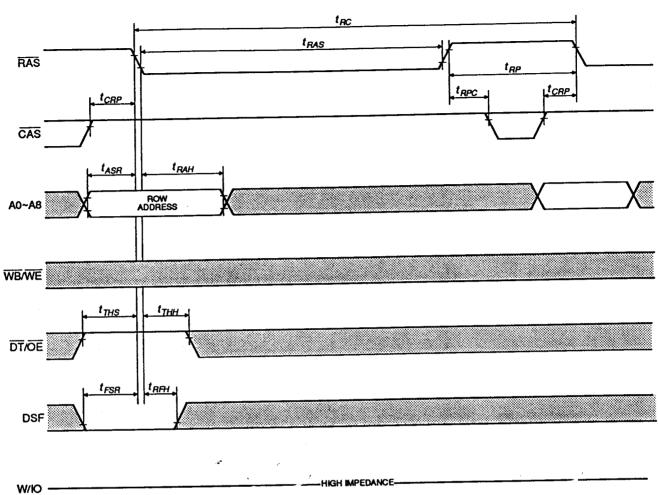

### **RAS-only Refresh**

A refresh operation must be performed to each of the 512 rows at least once every 8 ms to retain data. Although any normal memory cycle will perform this operation, refresh is most easily performed with a RAS Only cycle.

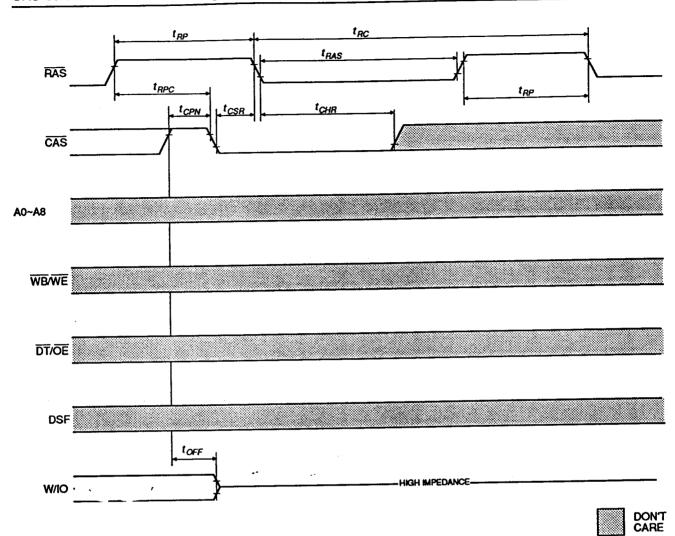

#### CAS-before-RAS Refresh

If CAS is brought low for a specified period ( $t_{\rm CSR}$ ) before RAS goes low, an internal counter and clock generators are enabled and an internal refresh operation takes place. When this refresh is complete, the address counter automatically increments in preparation for the next CAS-before-RAS cycle. For successive cycles, CAS may be held low while RAS cycles.

#### Hidden Refresh

This mode is a CAS-before-RAS refresh performed by holding CAS low from a previous Read Cycle. The output data from the previous memory cycle remains valid while performing the refresh. The internal refresh counter provides the address and the refresh is accomplished by cycling RAS.

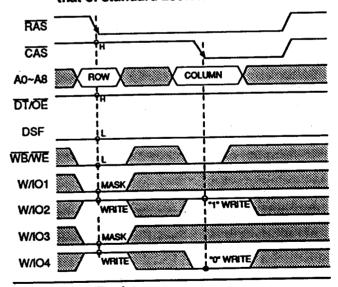

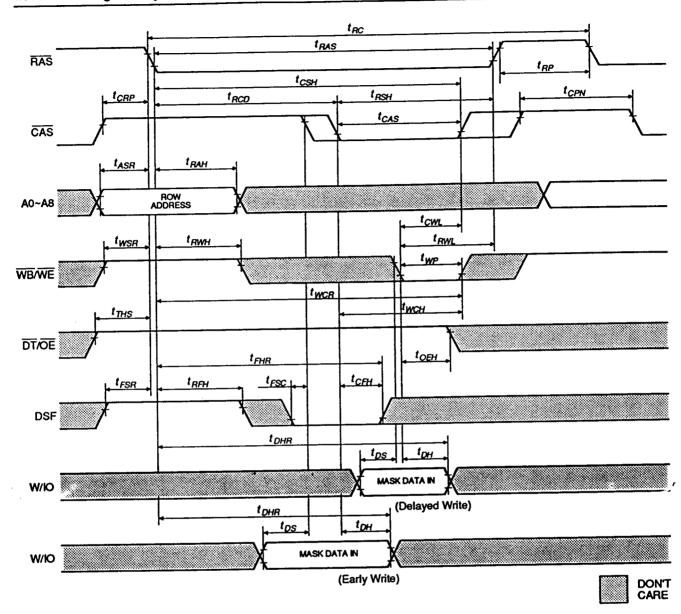

#### **Mask Write Function**

The WB/WE pin is used to select the DRAM Mask Write mode of operation. A high on WB/WE selects the Read mode and a low selects the write mode. In an early Write Cycle, WB/WE is brought low before CAS and the W/IO pins remain in the high impedance state throughout the entire cycle. During DRAM Write Cycles, holding WB/WE low on the falling edge of RAS will begin the Mask Write operation, as shown in the following table:

| Γ   |       | RASI  |     | CAS          |     |                       |

|-----|-------|-------|-----|--------------|-----|-----------------------|

| CAS | DT/OE | WB/WE | DSF | W/IO         | DSF | Function              |

| Н   | Н     | Н     | L   | Х            | ٦   | NORMAL WRITE          |

| Н   | Н     | L     | L   | MASK<br>DATA | اد  | MASK WRITE            |

| Н   | Н     | L     | Н   | Х            | L   | PERSISTENT MASK WRITE |

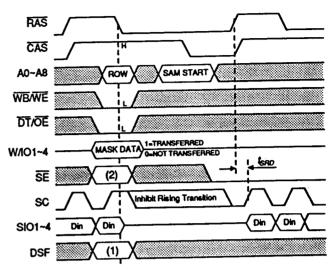

- (1) If DSF is low at the falling edge of RAS the write mask is reloaded. This means that mask data is required on the W/IO pins, latched on the falling edge of RAS, and new mask data is required at every RAS fall. This mask selects which of the four W/IO inputs are written and which are not, with a mask bit high indicating data will be written to that particular bit, and a mask bit low indicating that it will not. After RAS has latched the mask data on chip, the input data is latched on the falling edge of CAS.

- (2) If DSF is high at the falling edge of RAS, the mask is not reloaded, but instead retains the value loaded during the last mask Write Mask reload; any data on the W/IO pins is a don't care. This mode is known as Persistent Mask Write because the mask is persistent over any number of Write Cycles. The mask data is loaded into the register using either the Load Write Mask, Mask Write or Persistent Mask Write cycles.

NOTE: The Mask Write operation is initiated only if WB/WE is low at the falling edge of RAS. If it is high, the Write operation is identical to that of standard 256K x 4 DRAMs.

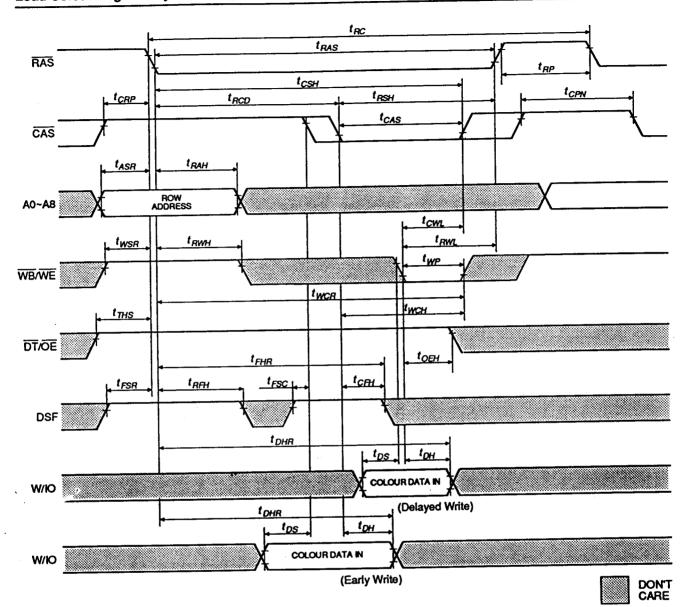

## **Load Colour Register**

The MVM4259 is provided with an on-chip 4 bit colour register which is used in the Block Write operation, with each bit of this register corresponding to one of the RAM I/O blocks. The Load Colour Register cycle is initiated by holding CAS, DT/OE, WB/WE and DSF high at the falling edge of RAS, and by holding DSF low at the falling edge of CAS. The data on the W/IO pins is

latched into the colour register at the falling edge of CAS or WB/WE, whichever occurs later. During this cycle a valid row address (A0~A8) is not required, but the cells of the row address which was latched at RAS fall will be refreshed.

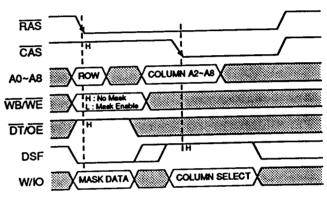

#### **Load Mask Register**

The MVM4259 is provided with an on-chip 4 bit mask register which provides the I/O mask data during the Mask Write (normal and Persistent) and Block Write (normal and Persistent) functions. Each bit of the mask register corresponds to one of the RAM I/O blocks, with the mask data being loaded into the register via the Load Write Mask Cycle prior to the execution of a Persistent Mask Cycle.

The Load Write Mask Cycle requires that CAS, DT/OE, WB/WE and DSF are high at the falling edge of RAS and by DSF high at the falling edge of CAS. The data on the W/IO pins is latched into the mask register at the falling edge of CAS or WB/WE, whichever occurs later. The data loaded into this register will also be updated by the Mask Write or Mask Block Write modes. During this cycle a valid row address (A0~A8) is not required, but the cells of the row address which was latched at RAS fall will be refreshed.

#### **Block Write**

This is a special RAM port write function which, in a single RAS cycle, allows data in the Colour Register to be written into 4 consecutive column address locations starting from a selected column in a selected row. There are three block write modes, with column mask capability applicable on all three modes. The address lines A2~A8 are latched on the falling edge of CAS giving the starting column address, with A0~A1 being replaced by the four W/IO bits, which are latched on the falling edge of CAS. These four bits are used as an address mask and indicate which of the four column address locations addressed by A2~A8 will be written with the contents of the colour register.

In the following table each W/IO enables the specified column addresses, where a 1 enables a write to that column and a 0 disables the write.

| DATA PIN | A1 | A0 |

|----------|----|----|

| W1/IO1   | 0  | 0  |

| W2/102   | 0  | 1  |

| W3/IO3   | 1  | 0  |

| W4/104   | 1  | 1  |

A Block Write Cycle is initiated by holding CAS and DT/ OE high at RAS fall and DSF high at CAS fall. The state of the WB/WE and DSF pins at the falling edge of RAS selects one of the three block write modes:

|     |       | RASI  |     |              |     | डि          |                             |  |

|-----|-------|-------|-----|--------------|-----|-------------|-----------------------------|--|

| CAS | DTAGE | WB/WE | DSF | W/IO         | DSF | W/IO        | Function                    |  |

| Н   | Н     | Н     | L   | X            | H   | COL<br>MASK | BLOCK WRITE                 |  |

| н   | Н     | L     | L   | MASK<br>DATA | Н   | COL         | MASK BLOCK WRITE            |  |

| н   | н     | L     | Н   | x            | Н   | COL         | PERSISTENT MASK BLOCK WRITE |  |

- (1) When DSF is low and WB/WE is high at RAS fall, the Block Write mode is selected.

- (2) If DSF and WB/WE are low at the falling edge of RAS, the Mask Block Write mode is selected, and the mask data on the W/IO pins is latched and used in the same way as the Mask Write mode.

- (3) When DSF is high and WB/WE is low at RAS fall, the Persistent Block Write mode is selected, and the data previously loaded into the mask register is used, as in the Persistent Mask Write mode.

The example below shows this mode with a data mask on W/IO1 and W/IO4 and a column mask on column 1.

|       | Mask<br>Data | Column<br>Select | Colour<br>Reg. |    |       | COL. | COL. | COL. | COL. |

|-------|--------------|------------------|----------------|----|-------|------|------|------|------|

| W/IO1 | 0            | 1                | 1              | ١. | W/IO1 |      |      |      |      |

| W/102 | 1            | 0                | 1              |    | W/102 | 1    |      | 1    | 1    |

| W/103 | 1            | 1                | 0              |    | W/103 | 0    |      | 0    | 0    |

| W/104 | 0            | 1                | 0              | 1  | W/104 |      |      |      |      |

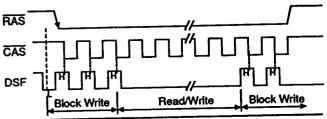

## Fast Page Mode Block Write Cycle

This mode can be used to perform high speed clear and fill operations, and is initiated by holding DSF low at the falling edge of RAS; with each subsequent CAS cycle with DSF high at CAS fall a Block Write is performed.

If DSF is low at CAS fall, a normal Page Mode Cycle occurs, thus Block Write and Read/Write operations can be mixed during a Page Mode Block Write Cycle:

## SERIAL PORT OPERATION

### Single Register Mode

Operation in this mode allows high speed read or write operations through the SAM port independent of the RAM port operations, except during Read/Write/Pseudo Write Transfer Cycles, with the preceding transfer operation determining the direction of data flow through the SAM port. If the previous transfer was a Read, the SAM is in the output mode, and if it was a Write or Pseudo Write Transfer the SAM port will be in the input mode. Note that the Pseudo Write operation only switches the SAM port from output to input mode; no data is transferred from SAM to RAM.

The 512 bits in each of the four data registers of the SAM are connected to the 512 column locations of the RAM. Serial data can be read from the SAM after a Read Transfer (RAM to SAM) has been performed, and data is accessed from the SAM starting at any of the 512 data bit locations, with the start location being selected by A0~A8 on the falling edge of CAS. The SAM is then accessed starting from this location and proceeding from the lowest to the highest significant bits, with wrap-around occurring at bits 511 and 0.

Subsequent real time Read Transfers may be performed on-the-fly as many times as necessary within the refresh time constraints of the DRAM memory array. (Simultaneous serial read operations can be performed with some timing restrictions.)

A Pseudo Write Transfer Cycle is used to change the SAM from output to input mode in order to write data into the serial registers, and subsequently a Write Transfer Cycle must be used to load the SAM data into the RAM row selected by the row address on A0~A8 at the falling edge of RAS. The starting location or Tap Point in the SAM for the next serial write is selected by the column address at the falling edge of CAS. The truth table for single register mode operation is shown below:

| SAM port<br>Operation | RASI<br>DT/OE | sc    | SE | Function for<br>Serial Read |                 |

|-----------------------|---------------|-------|----|-----------------------------|-----------------|

| Serial                |               |       | L  | Enable                      | Read            |

| Output<br>Mode        |               |       | Н  | Disable                     | Transfer        |

| Serial                | 1             |       | L  | Enable                      | Write           |

| Input<br>Mode         | Н             | -   - | Н  | Disable                     | Transfer        |

| Serial                | 1             |       | L  | Enable                      | Pseudo<br>Write |

| Input<br>Mode         |               |       | Н  | Disable                     | Transfer        |

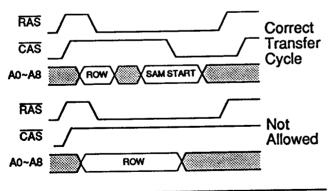

During all transfer cycles CAS must be cycled so that the column addresses are latched on the falling edge of CAS to set the SAM tap location. If CAS remains high during a transfer cycle the SAM pointer would be undefined; a transfer with CAS high is not allowed.

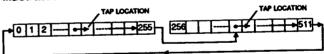

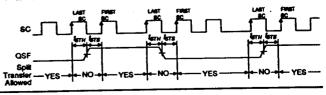

#### Split-register Mode

In this mode data can be shifted out of one half of the SAM while a Split Read Transfer is being performed on the other half. A normal non split Read Transfer (which places the SAM into output mode) must precede any Split Read Transfer operation. Split Read Transfers do not change the SAM port mode previously set by normal transfer operations. RAM port operation may be performed independently except during Split Transfers.

The low half of the SAM contains bits 0 to 255 and the upper half bits 256 to 511. When a split-register transfer is being performed, the tap address must be strobed in on the falling edge of CAS. The half of the SAM which is inactive (as indicated by the QSF pin) is loaded during a Split Read Transfer, with data being clocked out of the other half via the serial port pins.

Serial data can be shifted out of one of the split SAM registers starting from any of the 256 tap locations excluding the last address of each half. Data is shifted out sequentially starting from the selected tap location to the most significant bit (255 or 511) of the first SAM and then the SAM pointer moves to the tap location selected for the second split SAM. Data is then shifted out sequentially starting from this new tap location to the most significant bit (511 or 255) and finally wraps around to the least significant bit. This process is illustrated below.

Note that the serial start address must be supplied for every split-register transfer.

#### **Data Transfer Operations**

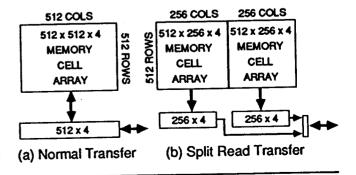

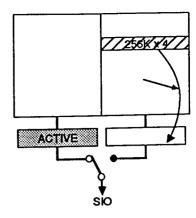

Two types of internal data transfer are possible with the MVM4259, and are shown graphically below:

During a normal transfer, 512 words x 4 bits of data can be loaded from RAM to SAM (Read Transfer) or from SAM to RAM (Write Transfer). In a split read transfer, 256 words x 4 bits of data can be loaded from the lower/upper half of the RAM into the lower/upper half of the SAM. These transfer modes are controlled by the DSF pin.

The table below illustrates all of the possible transfer operations, namely Read Transfer, Split Read Transfer, Write Transfer and Pseudo Write Transfer. Data transfer operations are invoked by holding DT/OE low at the falling edge of RAS, and the type of transfer is determined by the states of CAS, WB/WE, SE and DSF, which are latched at the falling edge of RAS.

During normal non split transfers, the SAM is switched from input to output mode by a Read Transfer Cycle, and from output to input by a Write Transfer Cycle, but its state remains unchanged during Split Read Transfer operations. During a transfer cycle, the row address A0~A8 select one of the 512 rows in the RAM to or from which data will be transferred, and the column address A0~A8 selects one of the tap locations in the SAM. This location is the start position in the SAM from which the first serial data will be read out from during subsequent Serial Read Cycles, or the start position in the SAM into which the first serial data will be written. During Split Read Transfer Cycles, column address A8 is controlled internally to determine which half of the SAM will be reloaded from the RAM.

Note that all transfer write operations will switch the SIO pins into the input (write) mode, and transfer read operations will switch the SIO pins into the output (read) mode. However, before data can be clocked into the serial port via the SIO pins and SC clock, it is necessary to switch the SIO pins into input mode via a previous transfer write operation. (The Pseudo Transfer mode serves to switch the direction of the SIO pins without actual data transfer taking place.) All transfer read operations and the pseudo transfer write operation will perform a memory refresh on the selected row.

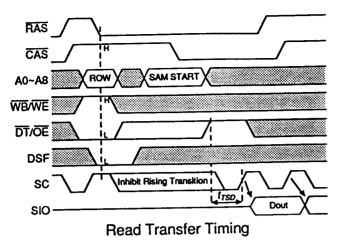

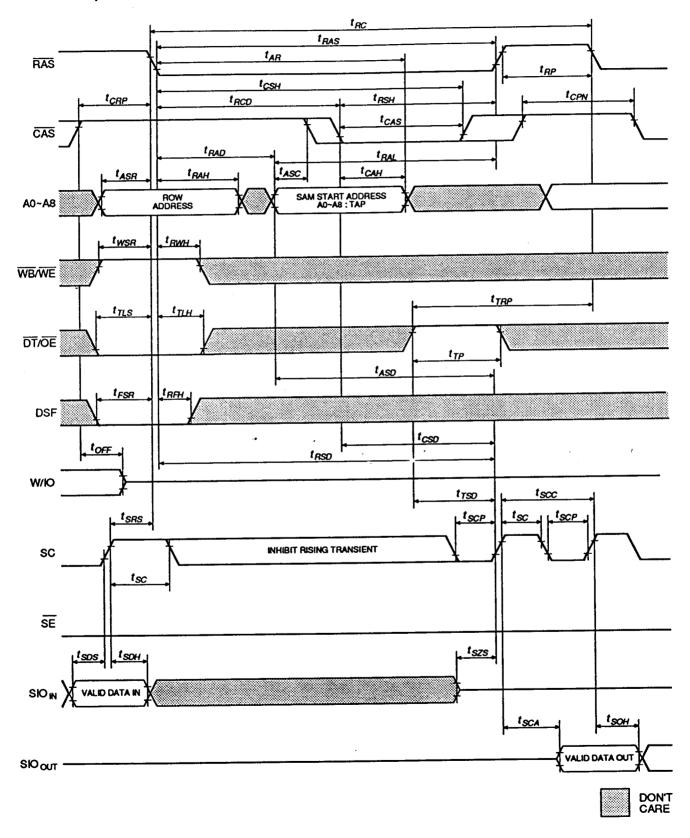

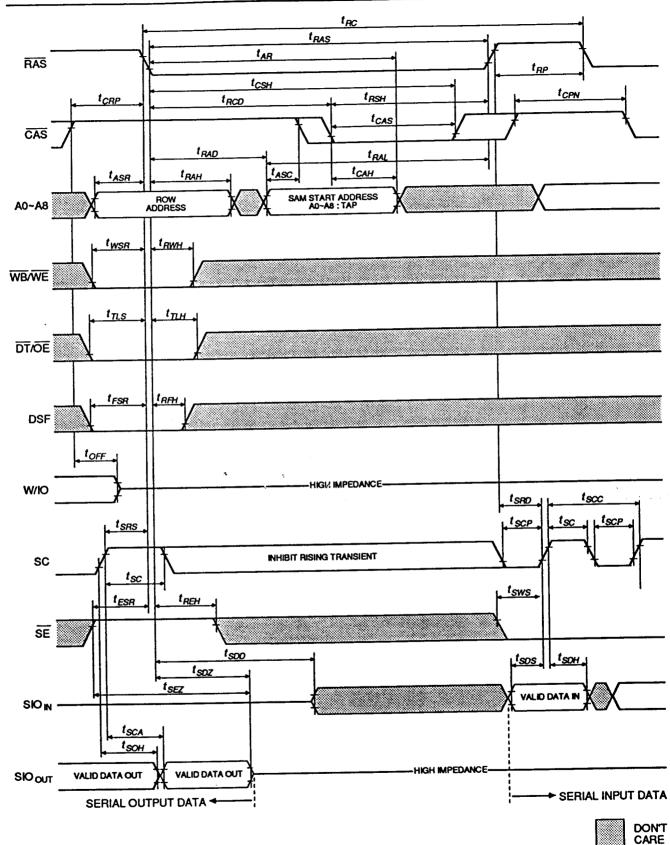

#### **Read Transfer Cycle**

A Read Transfer Cycle consists of storing a selected row of data in the RAM into the SAM. This cycle is initiated by holding CAS and WB/WE high, DT/OE and DSF low at the falling edge of RAS. The row address available at RAS fall determines to RAM row to be loaded into the SAM. The transfer cycle is completed at the rising edge of DT/OE, and the SAM is placed in the output mode.

In a Read/Real Time Read Transfer Cycle, the transfer of a new row of data is completed at the rising edge of DT/OE and this data becomes valid on the SIO pins after t<sub>SCA</sub> from the rising edge of the next SC clock cycle. The tap point for the SAM is set by the column address selected at the falling edge of CAS. The Read Transfer operation is shown diagrammatically below:

In a Read Transfer Cycle (preceded by a Write Transfer Cycle) the SC clock must be held at  $V_{\rm H}$  or  $V_{\rm L}$  after the specified SC high time has been satisfied. An SC rising edge must not occur until after  $t_{\rm TSO}$  from the rising edge of DT/OE as shown in the waveform overleaf:

#### MVM4259 Transfer Modes

|     |       | RAS↓  |    |     | Transfer              | Transfer  |         | SAM Port       |

|-----|-------|-------|----|-----|-----------------------|-----------|---------|----------------|

| CAS | DT/OE | WB/WE | SE | DSF | Mode                  | Direction | Bit     | Mode           |

| Н   | L     | Н     | Х  | L   | READ TRANSFER         | RAM → SAM | 512 x 4 | INPUT→ OUTPUT  |

| Н   | L     | L     | L  | L   | WRITE TRANSFER        | SAM → RAM | 512 x 4 | OUTPUT → INPUT |

| Н   | L     | L     | Н  | L   | PSEUDO WRITE TRANSFER |           |         | OUTPUT → INPUT |

| Н   | L     | L     | X  | Н   | WRITE TRANSFER        | SAM → RAM | 512 x 4 | OUTPUT → INPUT |

| Н   | L     | Н     | Х  | Н   | SPLIT READ TRANSFER   | RAM → SAM | 256 x 4 | NOT CHANGED    |

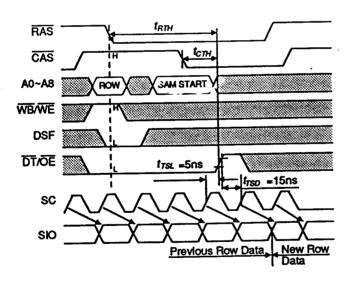

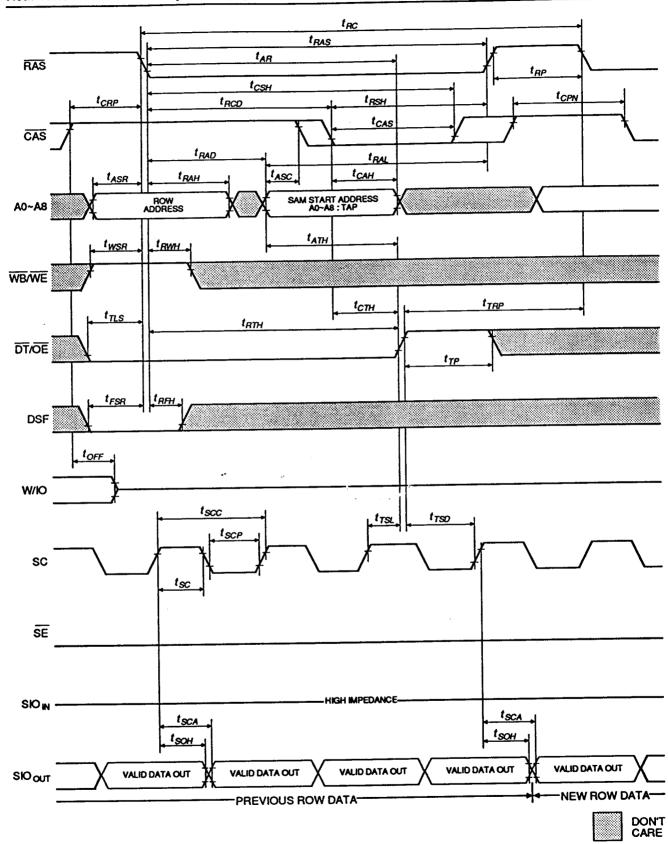

In a Real Time Read Transfer Cycle (which is preceded by another Read Transfer Cycle), the previous row data remains on the SIO pins until DT//OE goes high and serial access time  $t_{\rm SCA}$  is satisfied. This feature means that the first bit of the new row of data appears on the SIO pins as soon as the last bit of the previous row has been clocked without any timing loss. To make this continuous data flow possible, the DT/OE rising edge must be synchronised with RAS, CAS and the subsequent rising edge of SC, with  $t_{\rm RTH}$ ,  $t_{\rm CTH}$  and  $t_{\rm TSL}/t_{\rm TSO}$  being satisfied as shown below:

The timing restrictions for  $t_{\rm TSL}/t_{\rm TSD}$  are 5/15 ns minimum, but the Split Read Transfer mode eliminates these.

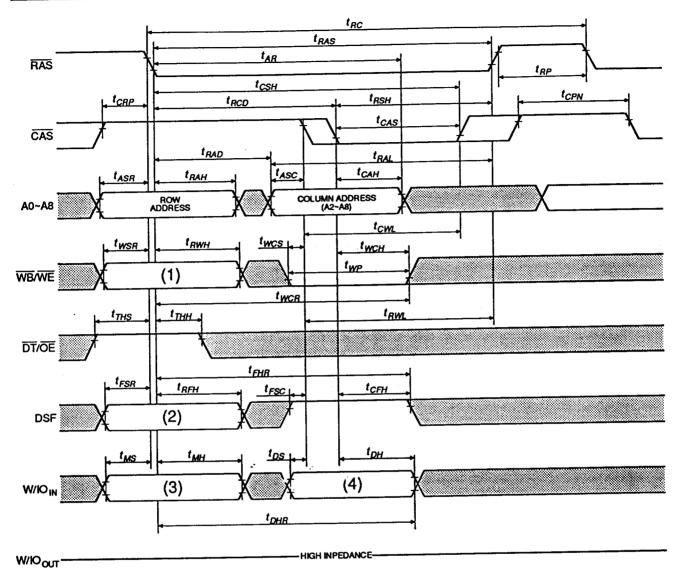

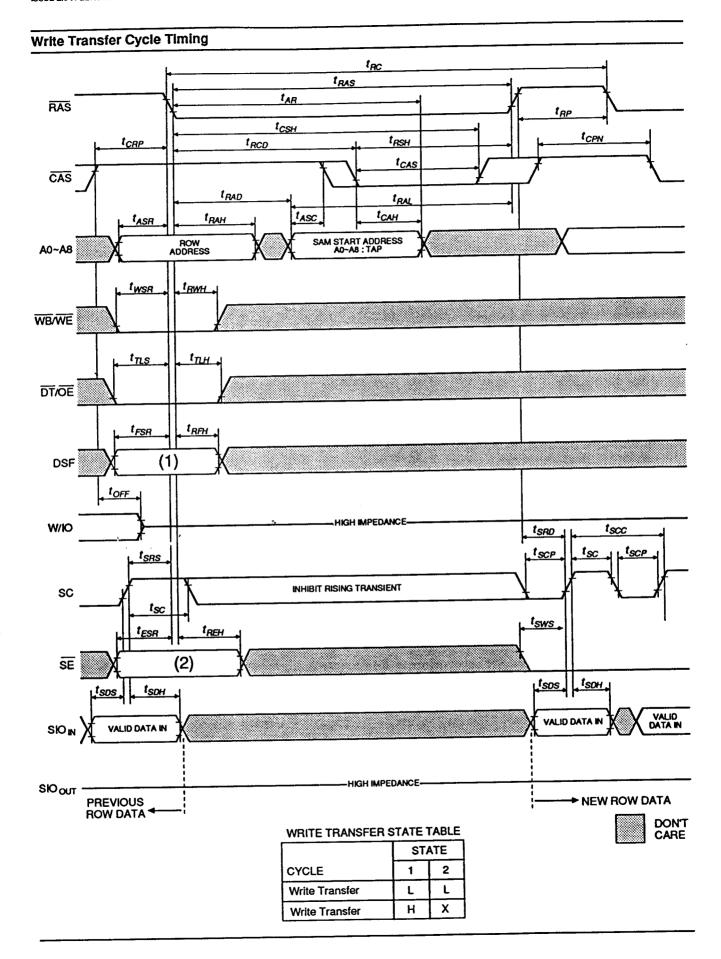

#### Write Transfer Cycle

This cycle transfers the contents of the SAM into a selected row of the RAM. If the SAM data is to be first loaded through the SAM SIO pins, a Pseudo Write Transfer operation must precede this cycle. However, if the SAM was previously loaded via a Read Transfer, the SAM to RAM transfer can be performed simply by

executing a Write Transfer Cycle. The Write Transfer Cycle is initiated by holding CAS high and DT/OE, WB/WE, SE, DSF low at RAS fall. Additionally, a Write Transfer independent of SE is possible if, at the falling edge of RAS, DSF is high and CAS, DT/OE, WB/WE are low.

The row address selected at RAS fall determines the RAM row into which the data from the SAM will be transferred, and the column address selected at CAS fall selects the tap point within the SAM. After the Write Transfer is completed, the SIO pins are placed in the input mode so that data synchronised with the SC clock can be loaded.

**Block Diagram for Write Transfer Operation**

When consecutive Write Transfer operations are performed, no new data can be written into the SAM until the RAS cycle of the preceding Write Transfer is completed; the SC clock must be held constant at  $V_{\rm M}$  or  $V_{\rm M}$  during this RAS cycle. An SC rising edge is only allowed after  $t_{\rm SRD}$  from the rising edge of RAS, at which time a new row of data can be written into the SAM.

#### **Pseudo Write Transfer Cycle**

After a Read Transfer operation has been performed a Pseudo Write Transfer Cycle must be executed before loading data into the SAM; this cycle only switches the SAM from output to input mode - no data transfer takes place. After the SAM is loaded, a Write Transfer Cycle must be invoked to transfer data from the SAM to the RAM. A Pseudo Write Transfer is initiated by holding CAS, SE high and DT/OE, WB/WE, DSF low at the falling edge of RAS. The critical timing conditions are the same as those for the Write Transfer Cycle except for the state of SE at RAS fall.

#### Split Read Transfer and QSF

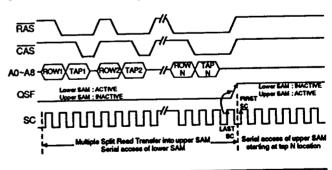

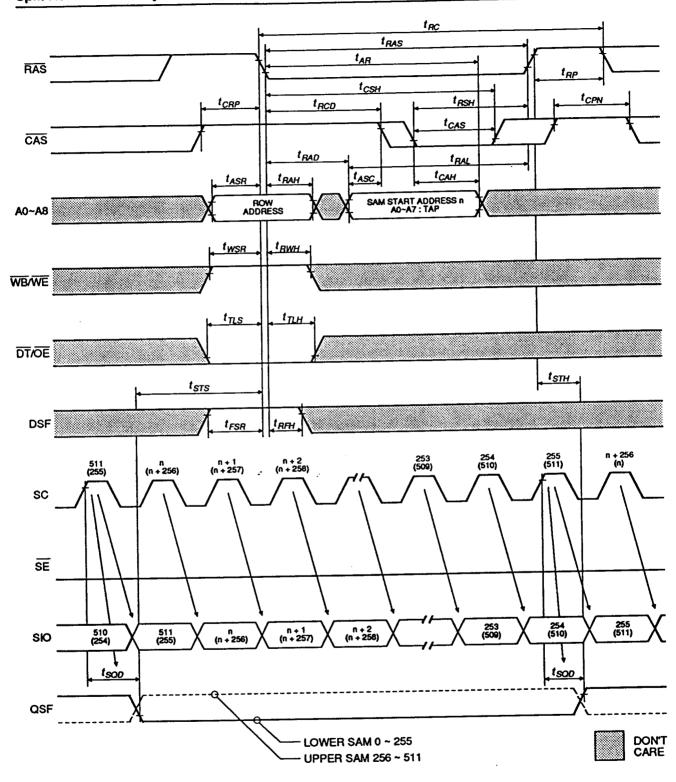

During Split Read Transfers, the SAM is split into two halves of 256 x 4 bits which can be controlled independently. Split Read Transfer operations can be performed to the inactive half of the SAM while serial data is being shifted out of the active half as shown below: Note that address A8 is controlled internally to deter-

mine which half of the SAM is loaded from the RAM, with the QSF output pin indicating which half of the SAM is currently active. To set up the tap point in the active half of the SAM, only address line A0~A7 are required, which are latched on the falling edge of CAS. QSF changes state when the last SC clock is applied to the active split SAM as shown below:

#### **Split Read Transfer Cycle**

A Split Read Transfer Cycle loads 256 words of 4 bits of data from a selected row of the split RAM into the corresponding non active half of the split SAM, with serial data being shifted out of the active half of the SAM simultaneously.

During Split Read Transfer operation, the RAM input

clocks do not have to be synchronized with the SC clock, thus eliminating timing restrictions as in the case of on-the-fly transfers. A Spit Read Transfer can be performed once the delay of tSTS after the change of state of QSF has been satisfied as shown below:

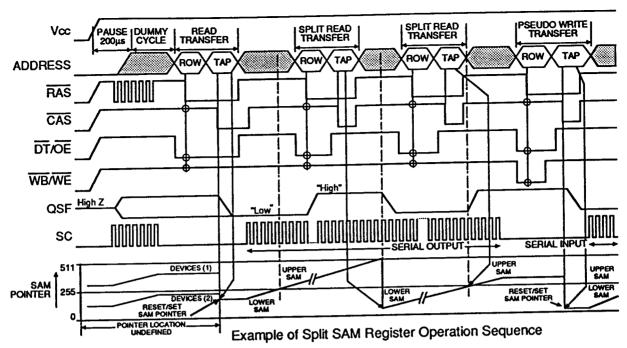

#### **Split Register Operation Sequence**

A normal non split Read Transfer MUST precede Split Read Transfer Cycles, and the following waveform illustrates the split register sequence after the MVM4259 is powered up and initialized. Initialization consists of a minimum of 8 RAS and 8 SC clock cycles. A Read Transfer is now performed, and the column address which is latched at the falling edge of CAS sets the SAM tap pointer location which was until that point undefined.

Now pointer address can be incremented by cycling SC from the starting location to the last location in the SAM (address 511), at which point it wraps around to the tap location set by the Split Read Transfer performed on the inactive half (here the lower) of the SAM while the active half (the upper) was being accessed. The SAM address is incremented as long as SC is clocked. Then, the next Split Read Transfer sets a new tap location in the inactive (upper) half of the SAM (in the example location 256) and the pointer is incremented from this location by the SC clock.

The next operation is a Pseudo Write Transfer which switches the SAM from output to input mode in preparation for either Write or Split Write Transfers. The column address latched at the falling edge of CAS during this cycle sets a new SAM tap location, and serial data will be written into the SAM starting from this tap point.

## **Transfer Operations Without CAS**

During all transfer cycles CAS must be cycled to latch the column address at CAS fall; this sets the new tap location. If CAS was held high during a transfer cycle, the SAM pointer location would be undefined, and so a transfer cycle with CAS high is not allowed - see the following examples.

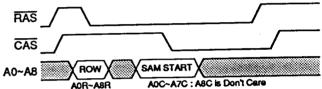

## Tap Location Selection in Split Read Transfers

In a Split Read Transfer operation, the column address A0~A7 is latched at the falling edge of CAS to set the tap point in the inactive half of the SAM. A8 is controlled internally, and so is ignored at the falling edge of CAS. During a split transfer, the tap point cannot be set to the last location of either half of the split SAM (A0~A7= $FF_{\mu}$ ).

In multiple Split Read Transfers performed into the same split SAM register, the tap location set during the last Split Read Transfer, before QSF changes state, will prevail. The example below shows multiple Split Read Transfers into the upper (non active) SAM, while the lower (active) SAM is being accessed at the time when QSF toggles. Here, the first SC clock will start shifting serial data from the tap N address location.

## **Split Read Transfer Operation Allowable Period**

The following waveform shows the relationship between the SC clock and the QSF pin during Split Read Transfers and highlights the times when Split Read Transfers are allowed.

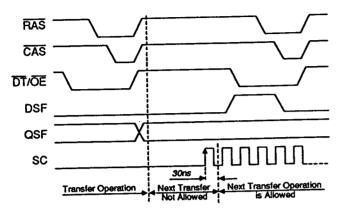

# **Split Read Transfers After Normal Read Transfers**

A Split Read Transfer may be executed after a normal Read Transfer provided that a minimum delay of 30 ns is allowed from the rising edge of the first SC clock - see waveform below.

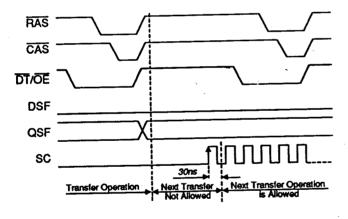

# Normal Read Transfers After a Read Transfer Cycle

Another Read Transfer may be performed following a Read Transfer providing that a minimum of 30 ns from the rising edge of the first SC clock is satisfied as shown below:

## Power Up Initialisation

At switch on, the RAS and DT/OE must be high before or at the same time as  $V_{\rm cc}$  reaches its final value. After power up, a pause of 200  $\mu$ s minimum is required with RAS and DT/OE held high. After this pause, a minimum of 8 RAS and 8 SC dummy cycles must be performed to stabilize the internal circuitry of the MVM4259 before valid Read, Write or Transfer operations can begin. During this initialization period, DT/OE must be held high. (If the internal refresh counter is used, a minimum of 8 CAS Before RAS initialization cycles are required instead of 8 RAS cycles.)

### Initial State After Power Up

When power up is achieved with RAS, CAS, DT/OE and WB/WE held high, the internal state of the MVM4259 is as follows:

|                 | State After Power Up |

|-----------------|----------------------|

| SAM Port        | Input Mode           |

| QSF Pin         | High Impedance       |

| Colour Register | All bits = 0         |

| Mask Register   | Write Enable         |

| TAP Pointer     | Invalid              |

However, for any other power up conditions and signal levels the internal states cannot be guaranteed. To achieve correct device operation it is recommended that the initial state be set by the user after the device is initialised by a 200µs pause followed by a minimum of 8 RAS cycles and 8 SC cycles and before valid operations begin.

# **MVM4259 ELECTRICAL CHARACTERISTICS**

## **Absolute Maximum Ratings**

| Voltage on any pin except W/IO and SIO | V <sub>T1</sub>  | -1 V to +7                  | ٧          |

|----------------------------------------|------------------|-----------------------------|------------|

| Voltage on W/IO and SIO                | • • •            | -1 V to +V <sub>cc</sub> +1 | · <b>V</b> |

| Power Dissipation                      | Pτ               | 1.0                         | W          |

| Operating Free air Temperature range   | T <sub>OP</sub>  | -55 to +125                 | °C         |

| Storage Temperature                    | T <sub>STG</sub> | -65 to +150                 | <b>∘</b> C |

| Clorago Tomporano                      | 514              |                             | andre Th   |

Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                                                                                | Symbol                  | Test C<br>RAM F     | onditions<br>Port <sup>(1)</sup> |                     | Test Cond                  |                              | -1<br>m | 0<br>ax      | -12<br>max         | Unit |

|------------------------------------------------------------------------------------------|-------------------------|---------------------|----------------------------------|---------------------|----------------------------|------------------------------|---------|--------------|--------------------|------|

| Operating Current                                                                        | l <sub>cc1</sub>        | RAS, C              | AS cycling                       |                     | SE = VH, S                 | SC = V <sub>IL</sub>         | •       | 90           | 75                 | m/   |

| operating current                                                                        | l <sub>cc7</sub>        | •                   | AS cycling                       |                     | SE = V <sub>L</sub> S      | C cycling                    | 1:      | 30           | 115                | m/   |

| RAS-only Refresh                                                                         | l <sub>cc3</sub>        | RAS cy              | cling, CAS                       | = V <sub>64</sub>   | SE - VH, S                 | SC = V <sub>IL</sub>         | •       | 90           | 75                 | m/   |

| The only rion out.                                                                       | l <sub>ccs</sub>        |                     | cling, CAS=                      |                     | SE = V <sub>IL</sub> , S   | C cycling                    | 1:      | 30           | 115                | m/   |

| CAS-before-RAS Refresh                                                                   |                         | RAS cy              | cling                            |                     | SE = V <sub>H</sub> , S    | SC = V <sub>IL</sub>         | ;       | 90           | <b>7</b> 5         | m/   |

|                                                                                          | l <sub>0011</sub>       | RAS cy              | rcling                           |                     | SE = V <sub>IL</sub> , S   | SC cycling                   | 1:      | 30           | 115                | m/   |

| Page-mode Current (1)                                                                    | I <sub>CC4</sub>        | RAS=V               | , CAS cyc                        | ling                | SE = V <sub>H</sub> , S    | SC = V <sub>IL</sub>         | ;       | 80           | 65                 | m/   |

| . ugooco oca aca                                                                         | l <sub>0010</sub>       |                     | V <sub>IL</sub> , CAS cy         |                     | SE = V <sub>IL</sub> , S   | SC cycling                   | 1       | 20           | 100                | m/   |

| Data Transfer Current                                                                    | l <sub>CC6</sub>        | RAS, C              | AS cycling                       |                     | SE = V <sub>H</sub> , S    | SC = V <sub>IL</sub>         | 1       | 10           | 95                 | m/   |

| Duid Hansier Commission                                                                  | <sub>CC12</sub>         | RAS, C              | AS cycling                       |                     | SE = V <sub>L</sub> , S    | SC cycling                   | 1       | 50           | 135                | m/   |

| Block Write Current                                                                      | I <sub>CC13</sub>       | RAS, C              | AS cycling                       |                     | SE = V <sub>IH</sub>       | SC = V <sub>IL</sub>         | 1       | 00           | 85                 | m/   |

| Diodit title out on                                                                      | l <sub>CC14</sub>       | RAS, C              | AS cycling                       |                     | SE = V <sub>L</sub> , S    | SC cycling                   | 1       | 40           | 125                | m    |

| Standby Current                                                                          | l <sub>cc2</sub>        | RAS, C              | AS = V                           |                     | SE = VH                    | SC = V <sub>IL</sub>         |         | 10           | 10                 | m/   |

| olando) obrioni                                                                          | l <sub>ccs</sub>        | RAS, C              | SAS = V <sub>IH</sub>            |                     | SE = V <sub>L</sub> ,      | SC cycling                   |         | 50           | 50                 | m    |

| Input Leakage Current                                                                    | l <sub>u</sub>          | V <sub>m</sub> = 01 | to +5.8V, V                      | <sub>sc</sub> = 5.5 | V                          |                              | ±       | :10          | ±10                | μA   |

| Output Leakage Current                                                                   | l <sub>ιο</sub>         | MA                  |                                  |                     | V, D <sub>out</sub> is dis | abled                        | ±       | :10          | ±10                | μA   |

| Notes (1) Where applicable                                                               |                         |                     |                                  |                     |                            |                              |         | · · ·        | - <u> </u>         |      |

| Capacitance (V <sub>∞</sub> =5V±10                                                       | 0%,T <sub>A</sub> =2    | 5°C) Ca             | pacitance c                      | alculate            | d, not meas                | ured.                        |         |              |                    |      |

| Parameter                                                                                |                         |                     | •                                | S                   | ymbol                      | typ                          | max     | Unit         |                    |      |

| Input Capacitance:                                                                       |                         |                     | ess, Clocks                      | ;                   | Cı                         | -                            | 7       | pF           |                    |      |

| I/O Capacitance:                                                                         |                         |                     | In/Out                           |                     | C'ro                       | -                            | 9<br>9  | pF<br>pF     |                    |      |

| Output Capacitance:                                                                      |                         | QSF                 | pin<br>————                      |                     | C <sub>o</sub>             |                              |         | - Pi         |                    |      |

| Recommended Operati                                                                      | ng Cond                 | litions             |                                  |                     |                            |                              |         |              |                    |      |

|                                                                                          |                         |                     |                                  | min                 | typ                        | max                          |         |              |                    |      |

| Supply Voltage                                                                           |                         |                     | V <sub>cc</sub>                  | 4.5                 | 5.0                        | 5.5                          | V       |              |                    |      |

| Input High Voltage                                                                       |                         |                     | V <sub>H</sub>                   | 2.4                 | -                          | 6.5                          | V       |              |                    |      |

| Input Low Voltage                                                                        |                         |                     | V <sub>IL</sub>                  | -1.0                | •                          | 0.8                          | V       |              |                    |      |

| Output High Voltage, Iou                                                                 | = -2.0 mA               |                     | V <sub>OH</sub>                  | 2.4                 | -                          | •                            | V       |              |                    |      |

| Output Low Voltage, Ia =                                                                 |                         |                     | Vol                              | -                   | -                          | 0.4                          | V       |              |                    |      |

| Output Low Voltage, Io.                                                                  |                         | QSF pin             | A <sup>oro</sup>                 | -                   | -                          | 0.4                          | V       |              |                    |      |

| Operating Temperature                                                                    |                         |                     | TA                               | 0                   | -                          | 70                           | °C      |              |                    |      |

| Sparania                                                                                 |                         |                     | T <sub>AI</sub>                  | -40                 | -                          | 85                           |         | suffix)      |                    |      |

|                                                                                          |                         |                     | T                                | -55                 | -                          | 125                          |         | I, MB s      |                    |      |

| AC Test Conditions                                                                       |                         |                     |                                  |                     | Output Loa                 | d - RAM                      | Output  |              |                    |      |

| * Input pulse levels: * Input rise and fall t * I/P and O/P timing * Output load: see of | times: 5n<br>; referenc | is<br>ce levels     | : 2.0V, 1.0                      |                     | / <del>```</del> •         | 45Ω<br>VV—o<br>1.76V<br>00pF | VO Pin  | 6459<br>30pF | <b>∕—∘</b><br>1.76 | v    |

|                                               |                   | -   | 10              | -1  | 2               |      |       |

|-----------------------------------------------|-------------------|-----|-----------------|-----|-----------------|------|-------|

| Parameter                                     | Symbols           | min | max             | min | max             | Unit | Notes |

| Random Read or Write cycle time               | t <sub>RC</sub>   | 180 | -               | 210 | -               | ns   |       |

| Read-modify-write cycle time                  | t <sub>RMW</sub>  | 235 | -               | 280 | -               | ns   |       |

| Fast Page Mode cycle time                     | t <sub>PC</sub>   | 55  | -               | 70  | -               | ns   |       |

| Fast Page-mode read-modify-write cycle time   | t <sub>PRMW</sub> | 100 | -               | 125 | -               | ns   | - 4   |

| Access time from RAS                          | t <sub>RAC</sub>  | -   | 100             | -   | 120             | ns   | 8,14  |

| Access time from column address               | taa               | -   | 50              | -   | 60              | ns   | 8,14  |

| Access time from CAS                          | tcac              | -   | 25              | -   | 25              | ns   | 8,15  |

| Access time from CAS Precharge                | t <sub>CPA</sub>  | -   | 50              | -   | 60              | ns   | 8,15  |

| Output Buffer turn off Delay                  | t <sub>OFF</sub>  | 0   | 20              | 0   | 20              | ns   | 10    |

| Transition time (Rise and Fall)               | t <sub>T</sub>    | 3   | 35              | 3   | 35              | ns   | 7     |

| Pulse duration, RAS high                      | $t_{RP}$          | 70  | -               | 80  | 4               | ns   |       |

| Pulse duration, RAS low                       | t <sub>RAS</sub>  | 100 | 104             | 120 | 104             | ns   |       |

| RAS Pulse Width (Fast Page Mode only)         | t <sub>RASP</sub> | 100 | 10 <sup>5</sup> | 120 | 10 <sup>5</sup> | ns   |       |

| RAS hold time                                 | t <sub>RSH</sub>  | 25  | -               | 25  | -               | ns   |       |

| CAS hold time                                 | t <sub>csH</sub>  | 100 | -               | 120 | -               | ns   |       |

| CAS Pulse Width                               | tcas              | 25  | 10 <sup>4</sup> | 25  | 104             | ns   |       |

| Delay time, RAS low to CAS low                | t <sub>RCD</sub>  | 20  | 75              | 20  | 90              | ns   | 14    |

| RAS to Column Address Delay time              | t <sub>RAD</sub>  | 15  | 50              | 15  | 65              | ns   | 14    |

| Delay time, column address to RAS high        | t <sub>RAL</sub>  | 50  | -               | 60  | -               | ns   |       |

| Delay time, CAS high to RAS low               | t <sub>CRP</sub>  | 10  | -               | 10  | -               | ns   |       |

| Pulse duration, CAS high                      | t <sub>CPN</sub>  | 10  | -               | 10  | -               |      |       |

| Pulse duration, CAS high (Fast Page Mode)     | t <sub>CP</sub>   | 10  | -               | 10  | -               | ns   |       |

| Row address setup time                        | t <sub>ASR</sub>  | 0   | •               | )   | -               |      |       |

| Row address hold time                         | t <sub>RAH</sub>  | 12  | -               | 12  | -               | ns   |       |

| Column address setup time                     | tasc              | 0   | -               | 0   | -               | ns   |       |

| Column address hold time after CAS low        | t <sub>CAH</sub>  | 15  |                 | 15  | -               | ns   |       |

| Column address hold time after RAS low        | t <sub>AR</sub>   | 70  | -               | 80  | -               | ns   |       |

| Read command setup time                       | t <sub>RCS</sub>  | 0   | -               | 0   | -               | ns   |       |

| Read Command hold time                        | t <sub>RCH</sub>  | 0   | -               | 0   | -               | ns   |       |

| Read Command hold time referenced to RAS      | t <sub>RRH</sub>  | 0   | -               | 0   | -               | ns   | 11    |

| Write Command hold time                       | twch              | 15  | -               | 15  | -               | · ns | ;     |

| Write Command hold time referenced to RAS     | twcR              | 70  | -               | 85  | •               | - ns | •     |

| Write Command pulse width                     | t <sub>WP</sub>   | 15  | -               | 15  | •               | - ns | 3     |

| Write setup time before RAS high              | t <sub>RWL</sub>  | 25  | -               | 30  | •               | - ns | 3     |

| Write setup time before CAS high              | t <sub>CWL</sub>  | 25  | -               | 30  | •               | - ns |       |

| Data Set up time                              | t <sub>DS</sub>   | 0   | -               | 0   |                 | - ns | s 1   |

| Data hold time                                | t <sub>DH</sub>   | 15  | -               | 15  |                 | - n: | s 1   |

| Data hold time after RAS low                  | t <sub>DHR</sub>  | 70  | -               | 85  |                 | - n: | S     |

| Early write command setup time before CAS low |                   | 0   | -               | 0   |                 | - n: | s 1   |

| Delay time, RAS low to WE low                 | t <sub>RWD</sub>  | 130 | -               | 155 |                 | - n  | s 1   |

| Delay time, column address to WE low          | t <sub>AWD</sub>  | 80  | -               | 100 |                 | - n  | s 1   |

| Delay time, CAS low to WE low                 | tcwp              | 55  | -               | 65  |                 | - n  | s 1   |

#### **AC Timing Parameters**

| AC Timing Parameters                                         |                  | ~   | 10              | -12 |          |      |          |

|--------------------------------------------------------------|------------------|-----|-----------------|-----|----------|------|----------|

| Parameter S                                                  | Symbols          | min | max             | min | max      | Unit | Notes    |

| Data to CAS delay time                                       | t <sub>DZC</sub> | 0   | -               | 0   | -        | ns   |          |

| Data to OE delay time                                        | t <sub>DZO</sub> | 0   | -               | 0   | •        | ns   |          |

| Access time from OE low                                      | t <sub>OEA</sub> | •   | 25              | -   | 30       | ns   | 8        |

| Output Buffer turn off delay from OE                         | t <sub>OEZ</sub> | 0   | 20              | 0   | 20       | ns   | 10       |

| OE to Data delay time                                        | t <sub>OED</sub> | 20  | -               | 30  | -        | ns   |          |

| OE hold time after WE low                                    | t <sub>OEH</sub> | 20  | -               | 30  | -        | ns   |          |

| RAS hold time referenced to OE                               | t <sub>ROH</sub> | 15  | -               | 15  | -        | ns   |          |

| CAS set up time for CAS before RAS cycle                     | t <sub>CSR</sub> | 10  | -               | 10  | -        | ns   |          |

| CAS hold time for CAS before RAS cycle                       | t <sub>CHR</sub> | 10  | -               | 10  | -        | ns   |          |

| RAS Precharge to CAS active time                             | t <sub>RPC</sub> | 0   | -               | 0   | -        | ns   |          |

| Refresh time interval, RAM                                   | t <sub>REF</sub> | -   | 8               | -   | 8        | ms   |          |

| WB setup time before RAS low                                 | twsa             | 0   | -               | 0   | •        | ns   |          |

| WB hold time                                                 | t <sub>RWH</sub> | 15  | -               | 15  | -        | ns   |          |

| DSF setup time before RAS low                                | t <sub>FSR</sub> | 0   | -               | 0   | •        | ns   |          |

| DSF hold time referenced to RAS (1)                          | t <sub>RFH</sub> | 15  | -               | 15  | -        | ns   |          |

| DSF hold time referenced to RAS (2)                          | t <sub>FHR</sub> | 70  | -               | 85  | -        | ns   |          |

| DSF setup time before CAS low                                | t <sub>FSC</sub> | 0   | -               | 0   | -        | ns   |          |

| DSF hold time after CAS low                                  | t <sub>CFH</sub> | 15  | -               | 15  | -        | ns   |          |

| Mask data set up time                                        | t <sub>MS</sub>  | 0   | -               | 0   | -        | ns   |          |

| Mask data hold time                                          | t <sub>MH</sub>  | 15  | -               | 15  | -        | ns   |          |

| DT high setup time before RAS low                            | t <sub>THS</sub> | 0   | -               | 0   | -        | ns   |          |

| DT high hold time after RAS low                              | t <sub>THH</sub> | 15  | -               | 15  | -        | ns   |          |

| DT low set up time                                           | trus             | 0   |                 | 0   | . •      | ns   |          |

| DT low hold time                                             | trun             | 15  | 104             | 15  | 104      | ns   |          |

| DT low hold time referenced to RAS                           | t <sub>RTH</sub> | 80  | 10 <sup>4</sup> | 100 | 104      | ns   |          |

| DT low hold time referenced to Column Address                | t <sub>ATH</sub> | 30  | -               | 30  | -        | ns   |          |

| DT low hold time referenced to CAS                           | t <sub>CTH</sub> | 25  | -               | 25  | -        | ns   |          |

| SE setup time referenced to RAS                              | t <sub>ESR</sub> | 0   | -               | 0   | -        | ns   |          |

| SE hold time referenced to RAS                               | t <sub>REH</sub> | 15  | -               | 15  | -        | ns   |          |

| Delay time, DT high to RAS low                               | t <sub>TRP</sub> | 70  | -               | 80  | -        | ns   |          |

| •                                                            | t <sub>TP</sub>  | 30  | -               | 40  | -        | ns   |          |

| DT Precharge time RAS to First SC delay time (Read Transfer) | t <sub>RSD</sub> | 100 | -               | 120 | -        | ns   |          |

| Column Address to First SC delay time (Read Trans            |                  | 50  | -               | 60  | -        | ns   |          |

| CAS to First SC delay time (Read Transfer)                   | t <sub>CSD</sub> | 25  | •               | 25  | -        | ns   | ;        |

|                                                              |                  | 5   | -               | 5   | -        | ns   | ;        |

| Last SC to DT lead time (Real Time Read Transfer             | t <sub>TSD</sub> | 15  | •               | 15  |          | - ns | 2        |

| Delay time, $\overline{DT}$ high to SC high                  |                  | 30  | _               | 30  |          | - ns | }        |

| Last SC to RAS set up time (Serial Input)                    | t <sub>SRS</sub> | 25  | -               | 25  |          | - ns | <b>;</b> |

| Delay time, RAS high to SC high (Serial Input)               | t <sub>SRD</sub> | 50  | -               | 50  |          | - ns | _        |

| RAS to Serial Input delay time                               | t <sub>SDD</sub> | 10  | 50              | 10  |          |      |          |

| Serial Output Buffer turn off delay from RAS                 | t <sub>SDZ</sub> | 30  | -               | 35  |          | - ns |          |

| Serial clock cycle time                                      | t <sub>scc</sub> | 10  | -               | 10  |          | - n: |          |

| Pulse duration, SC high                                      | t <sub>sc</sub>  | 10  |                 |     | <u> </u> |      |          |

| AC Timing Parameters                             |                   |     | 10        | <u></u> | 12  |      |       |

|--------------------------------------------------|-------------------|-----|-----------|---------|-----|------|-------|

| _                                                | Symbols           | min | 10<br>max | min     | max | Unit | Notes |

| Parameter                                        | Symbols           |     |           |         |     |      |       |

| Pulse duration, SC low                           | t <sub>SCP</sub>  | 10  | •         | 10      | -   | ns   | •     |

| Access time from SC high                         | t <sub>SCA</sub>  | -   | 25        | -       | 25  | ns   | 9     |

| Serial Output hold time after SC high            | t <sub>son</sub>  | 5   | -         | 5       | -   | ns   |       |

| Serial Input setup time before SC high           | t <sub>sos</sub>  | 0   | -         | 0       | -   | ns   |       |

| Serial Input hold time after SC high             | t <sub>SDH</sub>  | 15  | -         | 15      | -   | ns   | _     |

| Access time from SE                              | t <sub>SEA</sub>  | -   | 25        | -       | 25  | ns   | 9     |

| SE Pulse Width                                   | t <sub>SE</sub>   | 25  | •         | 25      | -   | ns   |       |

| SE Precharge time                                | t <sub>SEP</sub>  | 25  | -         | 25      | •   | ns   |       |

| Serial output disable time from SE high          | t <sub>SEZ</sub>  | 0   | 20        | 0       | 20  | ns   | 10    |

| Serial input to SE delay time                    | t <sub>sze</sub>  | 0   | -         | 0       | -   | ns   |       |

| Serial input to first SC delay time              | t <sub>szs</sub>  | 0   | -         | 0       | -   | ns   |       |

| Delay time, SE low to SC high                    | t <sub>sws</sub>  | 0   | -         | 0       | -   | ns   |       |

| Serial Write Enable hold time                    | t <sub>sw</sub>   | 15  | -         | 15      | -   | ns   |       |

| Serial Write Disable set up time                 | t <sub>swis</sub> | 0   | -         | 0       | -   | ns   |       |

| Serial Write Disable hold time                   | t <sub>swi</sub>  | 15  | -         | 15      | -   | ns   |       |

| Split Transfer set up time                       | t <sub>sts</sub>  | 30  | -         | 30      | -   | ns   |       |

| •                                                | t <sub>sth</sub>  | 30  | -         | 30      | •   | ns   |       |

| Split Transfer hold time<br>SC to QSF delay time | t <sub>SQD</sub>  | -   | 60        | -       | 60  | ns   | 16    |

#### NOTES:

- (1) Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

- (2) All voltages are referenced to GND.

- (3) These parameters depend on the cycle rate.

- (4) These parameters depend on the output loading. Specified values are measured with the output open.

- (5) An initial pause of 200 µs is required after power up, followed by any 8 RAS cycles (DT/OE high) and any 8 SC cycles before correct device operation is achieved. If the internal refresh counter is used, a minimum of 8 CAS before RAS initialisation cycles instead of 8 RAS cycles are required.

- (6) All measurements assume  $t_T = 5$ ns.

- (7)  $V_{H}$  (min) and  $V_{L}$ (max) are reference levels for measuring timing of input signals.

- (8) RAM port outputs are measured with the load specified under "AC Test Conditions".

- (8) SAM port outputs are measured with the load specified under "AC Test Conditions".

- (10) t<sub>OFF</sub>, t<sub>OEZ</sub>, t<sub>SEZ</sub> and t<sub>SDZ</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

- (11) Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for Read Cycles.

- (12) These parameters are referenced to the CAS leading edge in Early Write Cycles and to the WB/WE leading edge in OE controlled Write Cycles and Read-Modify-Write Cycles.

- (13) twcs, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are not restrictive operating parameters; they are included here as electrical characteristics only. If t<sub>AWD</sub> ≥ t<sub>AWD</sub> (min), the cycle is an Early Write Cycle and the data out pins will remain in the high impedance state throughout the entire write cycle. If t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min), t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min) and t<sub>AWD</sub> ≥ t<sub>AWD</sub> (min) the cycle is a Read-Modify-Write Cycle and the data out will contain data read from the selected memory cell. If neither of the above sets of conditions are satisfied, the state of the data pins at access time is indeterminate.

- (14) Operations with the t<sub>RCD</sub> (max) limit ensures that t<sub>RAC</sub> (max) can be met. t<sub>RCD</sub> (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than the maximum value, then access time is controlled by t<sub>CAC</sub>.

- (15) Operations with the t<sub>RAD</sub> (max) limit ensures that t<sub>RAC</sub> (max) can be met. t<sub>RAD</sub> (max) is specified as a reference point only; if t<sub>RAD</sub> is greater than the maximum value, then access time is controlled by t<sub>AA</sub>.

- (16) This parameter measurement assumes a pull up resistor of  $820\Omega$

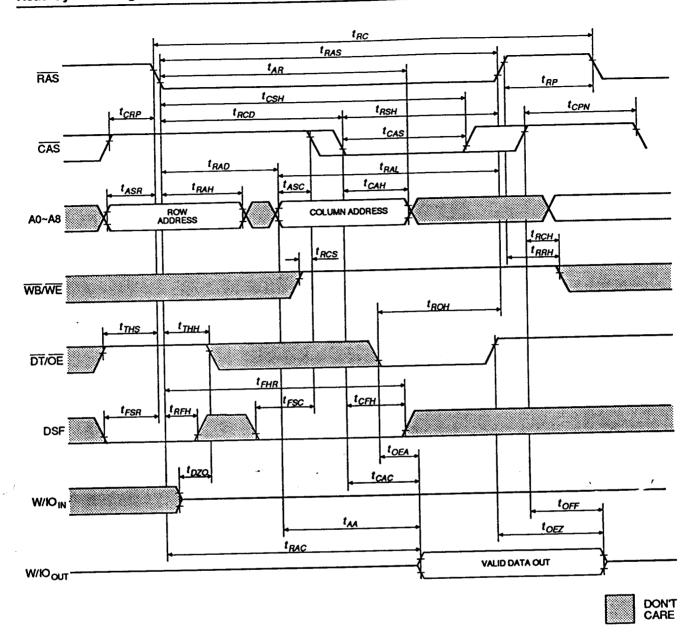

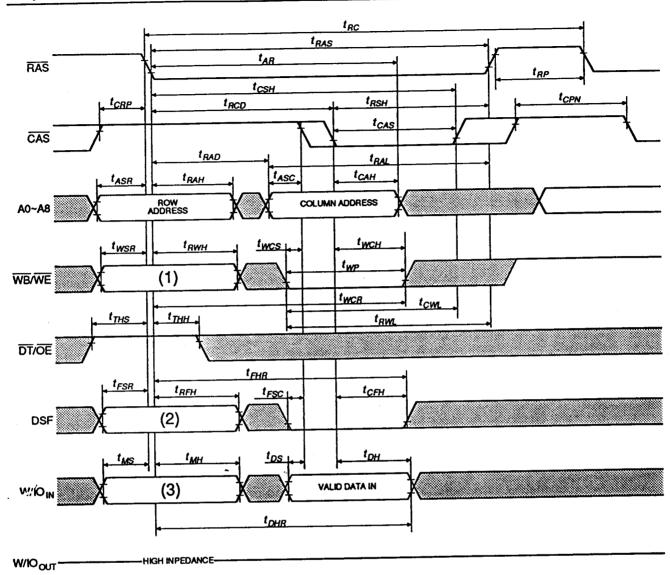

## Read Cycle Timing

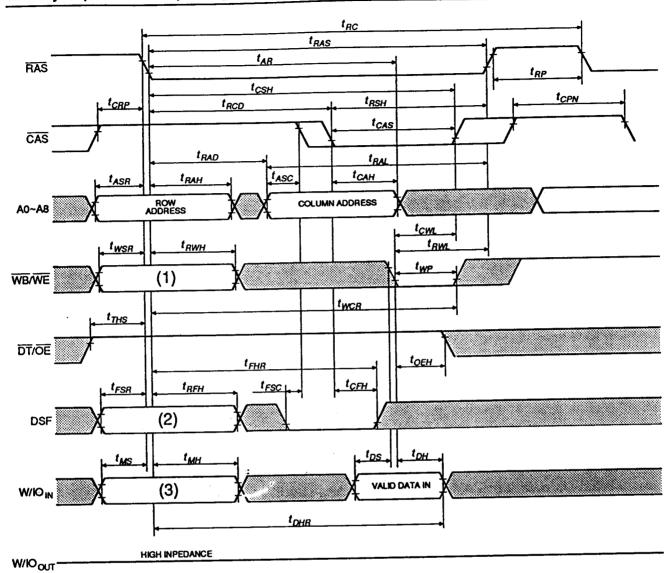

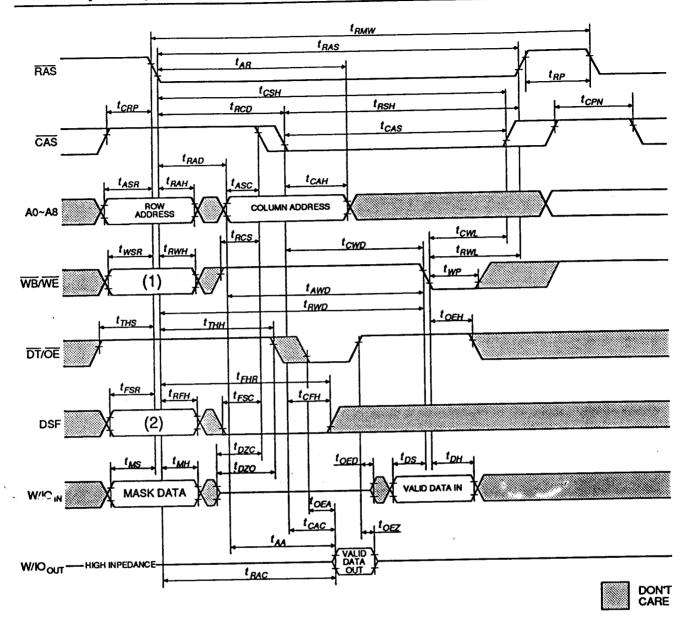

### **Early Write Cycle Timing**

DON'T CARE

|                                              | S | E |               |