**Technical Data** Datasheet 6132, Rev. -

# SiC FET Full Bridge with Integrated Gate Drive

#### FEATURES:

- 1200VDC max voltage

- 60A max current

- Compact package

- Temperature range -55°C to +125°C

- Efficient conduction cooled design

- Total weight: 1.10 oz.

#### **DESCRIPTION:**

This SiC FET Full Bridge power module can be used in various applications including, but not limited to, power converters and motor drives. The integrated gate drive simplifies the system design and optimizes the dynamic performance of the bridge.

The small size of this complete module makes it ideal for high reliability industrial, aerospace, and military applications.

#### ABSOLUTE MAXIMUM RATINGS

| PARAMETER                                                                                 | SYMBOL                | MIN | MAX  | UNIT |

|-------------------------------------------------------------------------------------------|-----------------------|-----|------|------|

| DC Bus Supply Voltage                                                                     |                       |     | 1200 | V    |

| PWM Switching Frequency                                                                   | Fsw                   | -   | 500  | kHz  |

| Continuous Drain Current, each Leg of Full Bridge                                         | ID                    | -   | 60   | А    |

| Pulsed Drain Current, each Leg of Full Bridge<br>Pulse Width limited by T <sub>jmax</sub> | I <sub>D(pulse)</sub> | -   | 120  | A    |

| Junction Temperature                                                                      | T <sub>jmax</sub>     | -55 | 150  | °C   |

| Storage Temperature                                                                       | T <sub>s max</sub>    | -55 | 150  | °C   |

| Operating Temperature on Cold Plate                                                       | T <sub>c max</sub>    | -55 | 125  | °C   |

EMICONDUCTOR

SENSITRON

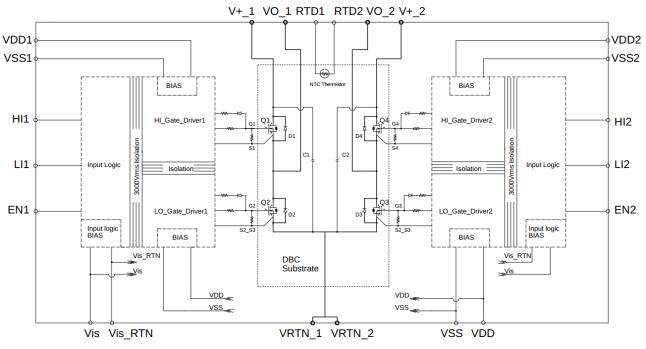

Figure 1 – Block Diagram

### **Connections for Full Bridge Application**

| V+_1, V+_2:         | both pins must connect to DC Bus power supply's Positive, no internal connection between these two pins                                                               |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VRTN_1,VRTN_2:      | both pins must connect to DC Bus power supply's Return, VRTN_1 and VRTN_2 are internally tied together                                                                |

| VO_1, VO_2:         | output connections                                                                                                                                                    |

| HI1, LI1, HI2, LI2: | gate control inputs; internally bypassed to V <sub>is_RTN</sub> with 1.0kohm resistor and 22pF capacitor, external in-line resistors [330hm, 590hm] recommended       |

| EN1, EN2:           | enable driver outputs; internally bypassed to <sub>Vis_RTN</sub> with 1.0kohm resistor<br>and 1nF capacitor, external in-line resistors [33ohm, 59ohm]<br>recommended |

| Vis /Vis, Vis_RTN:  | power supply input to logic circuitry                                                                                                                                 |

| VDD /VDD, VSS:      | power supply input to LO_Gate_Driver1 and LO_Gate_Driver2 circuitry                                                                                                   |

| VDD1 /VDD1, VSS1:   | power supply input HI_Gate_Driver1 circuitry                                                                                                                          |

| VDD2 /VDD2, VSS2:   | power supply input for HI_Gate_Driver2 circuitry                                                                                                                      |

| RTD1, RTD2          | connection to internal thermistor                                                                                                                                     |

Requirements to DC Bus power supply, |V<sub>is</sub>|, |VDD|, |VDD1| and |VDD2|: Minimum 2000VDC isolation between |VDD|, |VDD1| and |VDD2| Minimum 2000VDC isolation between |VDD1|/|VDD2| power supplies and DC Bus power supply.

Power supply to |VDD| needs to be isolated to DC Bus power supply: VSS is internally clamped 3.6V below VRTN\_1/VRTN\_2, for negative gate drive 3000VRMS isolation between power supply to |V<sub>is</sub>| and DC Bus/|VDD1|/|VDD2| power supplies

is recommended

<sup>©2022</sup> Sensitron Semiconductor • Ph (631) 586 7600 • Fax (631) 242 9798 • www.sensitron.com • sales@sensitron.com

Technical Data Datasheet 6132, Rev. -

### ELECTRICAL CHARACTERISTICS OF FULL BRIDGE, PER EACH LEG

TJ=25°C, UNLESS OTHERWISE SPECIFIED.

Production units are tested at room temperature. Low/High temperature operation is guaranteed by design.

| SYMBOL                | PARAMETER                                                                      |                                                 | MIN        | TYP              | MAX               | UNIT |

|-----------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------------|------------------|-------------------|------|

| V+_1,<br>V+_2         | DC Bus Supply Voltage,<br>to V_RTN1, V_RTN_2                                   | Absolute Max<br>Recommended                     |            | -<br>400         | 1200<br>600       | VDC  |

| MOSFET                | (Q1, Q2, Q3, Q4) Characteristics                                               |                                                 |            | 1                | 1                 |      |

| BV <sub>DSS</sub>     | Drain to Source Breakdown Voltage $I_D = 100 \ \mu$ A, V <sub>GS</sub> = 0V    |                                                 | 1200       |                  |                   | VDC  |

| I <sub>D</sub>        | Continuous Drain Current                                                       | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 125°C |            |                  | 60<br>30          | A    |

| I <sub>D(pulse)</sub> | Pulsed Drain Current                                                           |                                                 |            |                  | 120               | Α    |

| Vgs                   | Gate to Source Voltage                                                         |                                                 |            | -4/+15<br>Static | -8/+19<br>Dynamic | VDC  |

| lgss                  | Gate-Source Leakage Current $V_{GS} = +15V$ , $V_{DS} = 0V$                    |                                                 |            | 10               | 250               | nA   |

| $V_{\text{GS(th)}}$   | Gate Threshold Voltage<br>$I_D = 17.7$ mA, $V_{DS} = V_{GS}$                   | T」= 25°C<br>T」= 105°C                           | 1.8<br>-   | 2.5<br>2.0       | 3.6<br>-          | VDC  |

| IDSS                  | Zero Gate Voltage Drain Current $V_{DS} = 1200 \text{ V}, V_{GS} = 0 \text{V}$ |                                                 | -          | 1                | 25                | μA   |

| R <sub>DS(on)</sub>   | Drain-Source On-State Resistance $I_D = 50A$ , $V_{GS} = +15V$                 | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 105°C | 14<br>-    | 22<br>40         | 30<br>-           | mΩ   |

| Ciss                  | Input Capacitance                                                              |                                                 |            | 4820             |                   |      |

| $C_{\text{oss}}$      | Output Capacitance                                                             |                                                 | _          | 300              |                   | pF   |

| Crss                  | Reverse Transfer capacitance                                                   |                                                 |            | 18               |                   | P    |

|                       | $V_{DS} = 200 \text{ V}, V_{GS} = 0 \text{ V}, f = 100 \text{ kHz}, V$         | / <sub>AC</sub> = 25 mV                         |            |                  |                   |      |

| $Q_gs$                | Gate to Source Charge                                                          |                                                 |            | 49               |                   |      |

| $\mathbf{Q}_{gd}$     | Gate to Drain Charge                                                           |                                                 | -          | 50               | -                 | nC   |

| $Q_{g}$               | Total Gate Charge                                                              |                                                 |            | 162              |                   |      |

|                       | $V_{DS} = 600 \text{ V}, I_D = 50\text{A}, V_{GS} = -4\text{V}/+15\text{V}$    |                                                 |            |                  |                   |      |

| Anti-paral            | llel Diode (D1, D2, D3, D4) Characteris                                        | tics                                            |            |                  |                   |      |

| VF                    | Diode Forward Voltage<br>I <sub>F</sub> = 20A                                  | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 105°C | 1.0        | 1.5<br>2.0       | 1.8<br>-          | VDC  |

| IR                    | Reverse Current                                                                | V <sub>R</sub> = 1200V                          | -          | 35               | 200               | μA   |

| QC                    | Total Capacitive Charge<br>IF = 20A, VR =400V, di/dt = 150 A/ μs               |                                                 | -          | 68               | -                 | nC   |

| Internal D            | C Link - Snubber Capacitance betwee                                            | en V+_1/V+_2 an                                 | d VRTN_1/V | /RTN_2           |                   |      |

| C1, C2                | 1.2 kV, NP0, ±5%, -55°C to 150°C                                               |                                                 | -          | 12               | -                 | nF   |

| Stray indu            | lotance                                                                        |                                                 |            | 1                | 1                 | 1    |

| Lstray                | between pin 1 and 3 or<br>pin 7 and 6                                          |                                                 |            | 7.0              |                   | nH   |

Technical Data Datasheet 6132, Rev. -

#### ELECTRICAL CHARACTERISTICS OF LOGIC AND DRIVER INPUT

TJ=25°C, UNLESS OTHERWISE SPECIFIED.

Production units are tested at room temperature. Low/High temperature operation is guaranteed by design.

| SYMBOL                               | PARAMETER                                                                        | MIN  | TYP  | MAX                   | UNIT |

|--------------------------------------|----------------------------------------------------------------------------------|------|------|-----------------------|------|

| Absolute Maxi                        | mum Ratings                                                                      |      |      |                       |      |

| Vis                                  | Logic supply voltage, Vis to Vis_RTN                                             | -0.5 |      | 20.0                  | VDC  |

| HI1, LI1,<br>HI2, LI2                | Input logic signals to V <sub>is_RTN</sub> , TTL/CMOS compatible input threshold | -0.5 |      | V <sub>Vis</sub> +0.5 | VDC  |

| VDD, VSS<br>VDD1, VSS1<br>VDD2, VSS2 | Driver side supply voltage                                                       | -0.5 |      | 22.0                  | VDC  |

| Recommend C                          | perating Conditions                                                              |      |      |                       |      |

| V <sub>is</sub>                      | Logic supply voltage, $V_{is}$ to $V_{is_{RTN}}$                                 | 3.0  |      | 15.0                  | VDC  |

| VDD, VSS<br>VDD1, VSS1<br>VDD2, VSS2 | Driver side supply voltage                                                       | 18.0 |      | 20.0                  | VDC  |

| Vis to Vis_GND U                     | ndervoltage Thresholds                                                           |      |      |                       |      |

| Vis_ON                               | UVLO rising threshold                                                            | 2.5  | 2.7  | 2.9                   | VDC  |

| $V_{\text{is_OFF}}$                  | UVLO falling threshold                                                           | 2.3  | 2.5  | 2.7                   | VDC  |

| V <sub>is_HYS</sub>                  | UVLO threshold hysteresis                                                        |      | 0.2  |                       | VDC  |

| VDD-VSS, VDD                         | 01-VSS1, VDD2-VSS2 Undervoltage Thresholds                                       | L    | 1    | 1                     |      |

|                                      | UVLO rising threshold                                                            | 12.5 | 13.5 | 14.5                  | VDC  |

|                                      | UVLO falling threshold                                                           | 11.5 | 12.5 | 13.5                  | VDC  |

|                                      | UVLO threshold hysteresis                                                        |      | 1.0  |                       | VDC  |

| EN1, EN2 Thre                        | sholds                                                                           |      |      |                       |      |

| Venh                                 | Enable high voltage                                                              | 2.0  |      |                       | VDC  |

| V <sub>ENH</sub>                     | Enable low voltage                                                               |      |      | 0.8                   | VDC  |

| HI1, LI1, HI2 ar                     | nd LI2 Thresholds                                                                |      |      |                       |      |

|                                      | Input logic high threshold voltage                                               | 1.6  | 1.8  | 2.0                   | VDC  |

|                                      | Input logic low threshold voltage                                                | 0.8  | 1.0  | 1.2                   | VDC  |

|                                      | Input logic threshold hysteresis                                                 |      | 0.8  |                       | VDC  |

| Switching Cha                        | racteristics (Vis = 5V, VDD/VDD1/VDD2 = 15V)                                     |      |      |                       |      |

| trise                                | Output rise time, 20% to 80%, 1.8nF capacitor at gate drive output               |      | 6    | 16                    | ns   |

Technical Data Datasheet 6132, Rev. -

#### ELECTRICAL CHARACTERISTICS OF LOGIC AND DRIVER INPUT

TJ=25°C, UNLESS OTHERWISE SPECIFIED.

Production units are tested at room temperature. Low/High temperature operation is guaranteed by design.

| SYMBOL                          | PARAMETER                                                                                                                                                                                                  | MIN                                  | TYP           | MAX                  | UNIT  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|----------------------|-------|

| t <sub>FALL</sub>               | Output fall time, 90% to 10%, 1.8nF capacitor at gate drive output                                                                                                                                         |                                      | 7             | 12                   | ns    |

| <b>t</b> PDHL                   | Propagation delay from logic input to gate drive signal falling edges                                                                                                                                      | 14                                   | 19            | 30                   | ns    |

| <b>t</b> pdlh                   | Propagation delay from logic input to gate drive signal rising edges                                                                                                                                       | 14                                   | 19            | 30                   | ns    |

| <b>t</b> PWD                    | Pulse width distortion  tpdlh - tpdhl                                                                                                                                                                      |                                      |               | 5                    | ns    |

| t <sub>DM</sub>                 | Propagation delays matching between $V_{\rm G1}$ and $V_{\rm G2},V_{\rm G3}$ and $V_{\rm G4}$                                                                                                              |                                      |               | 5                    | ns    |

| NTC Thermisto                   | r Characteristics (Heraeus Nexensos's M Sens                                                                                                                                                               | or)                                  |               |                      |       |

| R <sub>0</sub>                  | Resistance @ T <sub>c</sub> = 0 °C                                                                                                                                                                         |                                      | 1             |                      | K Ohm |

| R <sub>TOL</sub>                | Resistance Tolerance                                                                                                                                                                                       |                                      |               | ±0.12                | %     |

|                                 | Measuring Current                                                                                                                                                                                          | 0.1                                  |               | 0.3                  | mA    |

| TCR                             | $TCR = \frac{R_{100} - R_0}{R_0 * 100^{\circ}C}$<br>$R_{100}$ is resistance at 100°C,<br>$R_0$ is resistance at 0°C                                                                                        |                                      | 3850          |                      | ppm/K |

|                                 | Temperature Range                                                                                                                                                                                          | -70                                  |               | 500                  | °C    |

| Resistance<br>vs<br>Temperature | $ \begin{split} t &>= 0 \ ^{\circ} \\ R(t) &= R_0 * (1 + A * t + B * t^2) \\ t &< 0 \ ^{\circ}\text{C} \\ R(t) &= R_0 * (1 + A * t + B * t^2 + C * \\ & (t - 100 \ ^{\circ}\text{C}) * t^3); \end{split} $ | A = 3.9083<br>B = -5.77<br>C = -4.18 | $5 * 10^{-7}$ | °C-1<br>°C-2<br>°C-4 |       |

| Internal Config                 | urations                                                                                                                                                                                                   |                                      |               |                      |       |

| VSS-VRTN_1<br>VSS-VRTN_2        | VSS is internally clamped below<br>VRTN_1/VTRN_2 for negative gate drive                                                                                                                                   |                                      | -3.6          |                      | VDC   |

| DT                              | Internal dead time setting                                                                                                                                                                                 |                                      | No            |                      |       |

| SENSITRON     |

|---------------|

| SEMICONDUCTOR |

### THERMAL AND MECHANICAL CHARACTERISTICS

| SYMBOL             | PARAMETER                                                                                                   | MIN | TYP  | MAX   | UNIT    |

|--------------------|-------------------------------------------------------------------------------------------------------------|-----|------|-------|---------|

| R₀јв_м             | MOSFET Junction-to- Base Plate Thermal<br>Resistance Per Leg                                                | -   | .339 | .390  | °C/W    |

| R <sub>0JB_D</sub> | Diode Junction-to-Base Plate Thermal<br>Resistance Per Leg                                                  | -   | .884 | 1.017 | °C/W    |

|                    | All pins to Base Plate/Screw mounting pads                                                                  | -   | -    | 2500  | VDC     |

| Isolations         | Logic signals to driver signals  V <sub>is</sub> -VDD <br> V <sub>is</sub> -VDD1 <br> V <sub>is</sub> -VDD2 | -   | -    | 2500  | Vrms    |

| Mounting<br>Torque | see installation instructions<br>#4 Size Screw                                                              | 3   | -    | 4     | in-Ibs. |

|                    | Weight<br>Module                                                                                            | -   | 32   | 40    | g       |

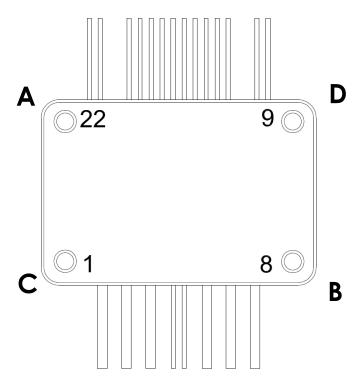

### **INSTALLATION INSTRUCTIONS:**

Recommended thermal interface material = Laird Tgon 805 (5 mil thick graphite pad)

- 1. Fasten screws to 1 to 2 in-lb. of torque in the following sequence: A, B, C, D.

- 2. Fasten screws to final torque in the same sequence: A, B, C, D

Technical Data Datasheet 6132, Rev. -

#### PART NUMBER DESCRIPTION:

- "SPG060C120P2" Straight Leads

- "SPG060C120P2A" Surface Mount Lead Formation

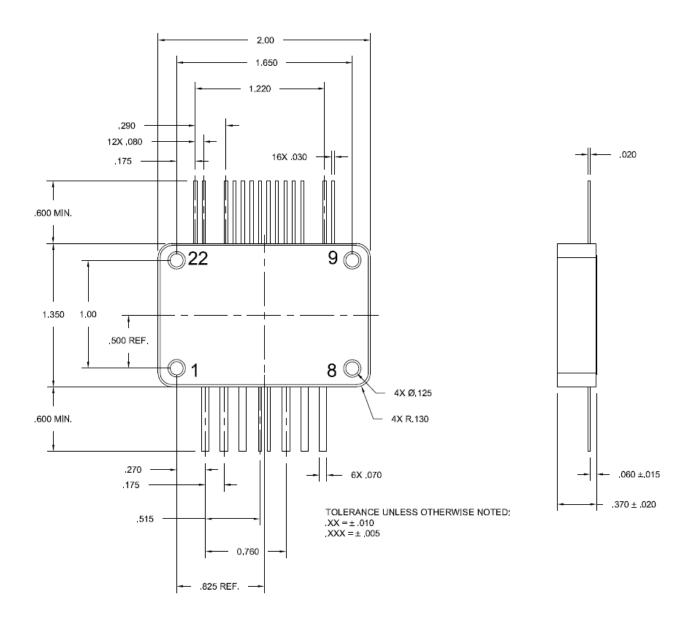

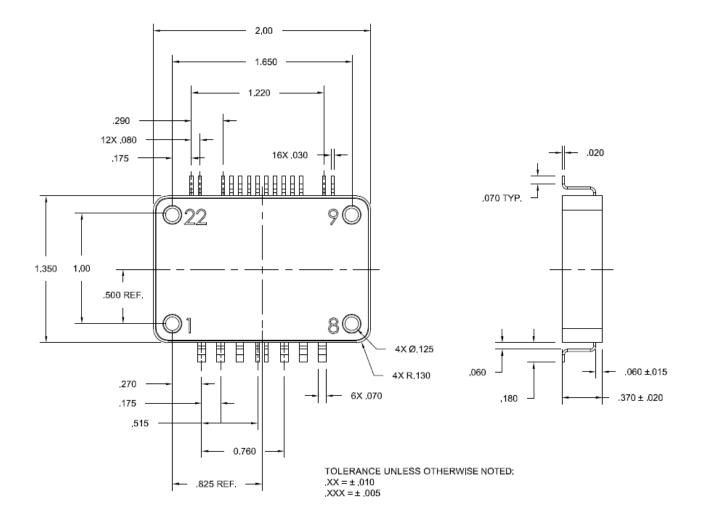

#### **MECHANICAL OUTLINES (inches)**

#### SPG060C120P2

SPG060C120P2A

#### PINOUTS

| Pin 1: V+_1   |

|---------------|

| Pin 2: VO_1   |

| Pin 3: VRTN_1 |

| Pin 4: VDD    |

| Pin 5: VSS    |

| Pin 6: VRTN_2 |

| Pin 7: VO_2   |

| Pin 8: V+_2   |

|               |

Pin 9: VSS2 Pin 10: VDD2 Pin 11: HI2 Pin 12: LI2 Pin 13: EN2 Pin 14: Vis Pin 15: RTD1 Pin 16: RTD2 Pin 17: Vis\_RTN Pin 18: LI1 Pin 19: HI1 Pin 20: EN1 Pin 21: VSS1 Pin 22: VDD1

#### DISCLAIMER:

1- The information given herein, including the specifications and dimensions, is subject to change without prior notice to improve product characteristics. Before ordering, purchasers are advised to contact the Sensitron Semiconductor sales department for the latest version of the datasheet(s).

2- In cases where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, medical equipment, and safety equipment), safety should be ensured by using semiconductor devices that feature assured safety or by means of users' fail-safe precautions or other arrangement.

3- In no event shall Sensitron Semiconductor be liable for any damages that may result from an accident or any other cause during operation of the user's units according to the datasheet(s). Sensitron Semiconductor assumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in the datasheets.

4- In no event shall Sensitron Semiconductor be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.

5- No license is granted by the datasheet(s) under any patents or other rights of any third party or Sensitron Semiconductor.

6- The datasheet(s) may not be reproduced or duplicated, in any form, in whole or part, without the expressed written permission of Sensitron Semiconductor.

7- The products (technologies) described in the datasheet(s) are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.