SSM-2100

MONOLITHIC

LOG/ANTILOG AMPLIFIER

Precision Monolithics Inc.

## **FEATURES**

- · Performs Log, Antilog, and Log Ratio Functions

- 50pA Input Bias Current (Trimmed)

- 4mV Input Offset Voltage

- On-Board Reference

- Temperature Stabilized

- 25ppm/°C Reference Drift

- 30ppm/°C Scale Factor Drift

- 0.25% Conformance

- 3-Decade Dynamic Range (Voltage Mode)

- 6-Decade Dynamic Range (Current Mode)

- Low Cost

#### **APPLICATIONS**

- Photodiode Preamplifier

- Absorption Measurement

- Low Sweep Generators

- High Resolution Data Acquisition

- Analog Computation Circuits

- Analog Compression/Expansion

- Linear-to-dB Conversion

## ORDERING INFORMATION

| PACKAGE  | OPERATING      |  |  |

|----------|----------------|--|--|

| PLASTIC  | TEMPERATURE    |  |  |

| 16-PIN   | RANGE          |  |  |

| SSM2100P | -10°C to +55°C |  |  |

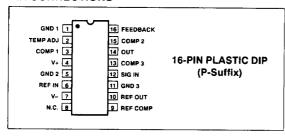

# **PIN CONNECTIONS**

# **GENERAL DESCRIPTION**

The SSM-2100 is a monolithic low-cost DC logarithmic amplifier capable of implementing log/antilog as well as log ratio transfer functions. This device offers a dynamic range of 6 decades of current and 3 decades of voltage. The circuit contains two precision operational amplifiers, a high conformance transistor pair and a precision bandgap voltage reference. An on-board substrate temperature regulator stabilizes both the scale factor and reference drift. A negative voltage reference is also available to facilitate external trimming.

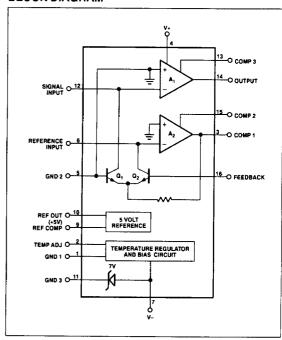

#### **BLOCK DIAGRAM**

The SSM-2100 is mask work protected under the Semiconductor Chip Protection Act of 1983.

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                     | 36V or ±18V    |

|------------------------------------|----------------|

| Junction Temperature               |                |

| Operating Temperature Range        | 10°C to +55°C  |

| Storage Temperature Range          | 65°C to +150°C |

| Maximum Current into Any Pin       | 10mA           |

| Lead Temperature Range (Soldering, | 60 sec) +300°C |

| PACKAGE TYPE           | Θ <sub>iA</sub> (Note 1) | Θ <sub>JC</sub> | UNITS |

|------------------------|--------------------------|-----------------|-------|

| 16-Pin Plastic DIP (P) | 82                       | 39              | °C/W  |

NOTE:

**ELECTRICAL CHARACTERISTICS** at  $V_S = \pm 15V$ ,  $R_{LIMIT} = 1.6k\Omega$ ,  $+5^{\circ}C \le T_A \le +50^{\circ}C$ ,  $I_{REF} = 1mA$ , unless otherwise noted.

|                                                     |                      |                                                                                               |                    | 0014 0400           |             |           |

|-----------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------|--------------------|---------------------|-------------|-----------|

| PARAMETER                                           | SYMBOL               | CONDITIONS                                                                                    | MIN                | SSM-2100<br>TYP     | MAX         | UNITS     |

| Conformity Error<br>(Note 1)                        | V <sub>ERHOR</sub>   | I <sub>I N</sub> = 100nA to 100μA<br>I <sub>I N</sub> = 10nA to 1mA<br>(Input Offset Trimmed) | -                  | 0.25<br>0.4         | -           | %         |

| Scale Factor                                        | V <sub>SCALE</sub>   | Measured at Pin 16                                                                            | 65                 | 70                  | 75          | mV/Decade |

| Scale Factor<br>Temperature Drift                   | TCV <sub>SCALE</sub> |                                                                                               | -                  | 30                  | -           | ppm/°C    |

| Input Offset Voltage<br>(Note 2)                    | V <sub>ios</sub>     |                                                                                               | _                  | 4                   | 8           | mV        |

| Input Bias Current<br>(Notes 1, 2)                  | ı <sub>B</sub>       |                                                                                               | _                  | 500                 | 2000        | pA        |

| Output Offset Voltage                               | v <sub>oos</sub>     | I <sub>IN</sub> = I <sub>REF</sub> = 1mA<br>Scale Factor Set at 1V/Decade                     | _                  | 30                  | 70          | mV        |

| Power Supply Rejection Ratio (Note 3)               | PSRR                 | +12V ≤ V+ ≤ +17V<br>-12V ≥ V− ≥ -17V<br>Scale Factor Set at 1V/Decade                         | -<br>-             | 500<br>250          | -<br>-      | μV/V      |

| Output Voltage Swing                                | V <sub>out</sub>     | R <sub>L</sub> ≥ 10kΩ<br>R <sub>L</sub> ≥ 2kΩ                                                 | −1<br><b>-</b> 0.2 | <del>-</del><br>-   | +10<br>+10  | V         |

| Reference Output Voltage                            | +V <sub>REF</sub>    | No Load                                                                                       | 4.7                | 5.0                 | 5.2         | V         |

| Reference Output Voltage<br>Temperature Coefficient | TCV <sub>REF</sub>   |                                                                                               | -                  | 25                  | _           | ppm/°C    |

| Reference Output Current                            | OUTREF               |                                                                                               | 5                  |                     | -           | mA        |

| Reference Load Regulation                           |                      | R <sub>L</sub> ≥ 1kΩ                                                                          | -                  | 0.015               | _           | %/mA      |

| Reference Supply Rejection                          | PSRR <sub>REF</sub>  | -+12V ≤ V+ ≤ +17V                                                                             | -                  | 0.04                | _           | %∧        |

| Voltage at Pin 7                                    | +V <sub>REF</sub>    |                                                                                               | 6                  | 7                   | 8           | V         |

| Positive Supply Current                             | +I <sub>SY</sub>     | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = +50°C<br>T <sub>A</sub> = +5°C<br>Heater Disabled  | -<br>-<br>-        | 35<br>20<br>50<br>5 | -<br>-<br>- | mA        |

| Negative Supply Current                             | -I <sub>SY</sub>     |                                                                                               | -                  | 5                   | 6.25        | mA        |

| Heater Start-up Current                             | I <sub>HTR</sub>     |                                                                                               | _                  | 80                  | 120         | mA        |

| Regulated Chip<br>Temperature                       | T <sub>REG</sub>     |                                                                                               | 53                 | 60                  | 75          | °C        |

## NOTES:

- 1. Guaranteed by design but not directly measured.

- 2. Applies to both signal and reference inputs.

- 3. Referred to output in log mode, or to input in antilog mode.

- 4. Specifications apply after a 50 second warmup period.

$\label{lem:specifications} \textbf{Specifications subject to change; consult latest data sheet.}$

<sup>1.</sup>  $\Theta_{|\mathbf{A}}$  is specified for worst case mounting conditions, i.e.,  $\Theta_{|\mathbf{A}}$  is specified for device in socket for P-DIP package.

## **GENERAL PRINCIPLE OF OPERATION**

The SSM-2100 utilizes the predictable logarithmic relationship between the collector currents and differential input voltage of an NPN transistor pair, given by:

$$delta V_{IN} = kT/q In I_{C2}/I_{C1}$$

(1)

where:  $k = Boltzmann's constant (1.38 x 10^{-23}) J/°K)$

$q = charge of an electron (1.6 x 10^{-23} C)$

T = absolute temperature (°K)

Deviation in the absolute temperature term is eliminated with the SSM-2100 design since the chip temperature is regulated at +60°C (333°K).

# PRINCIPLE OF LOG OPERATION

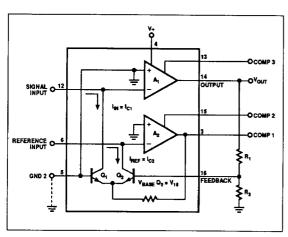

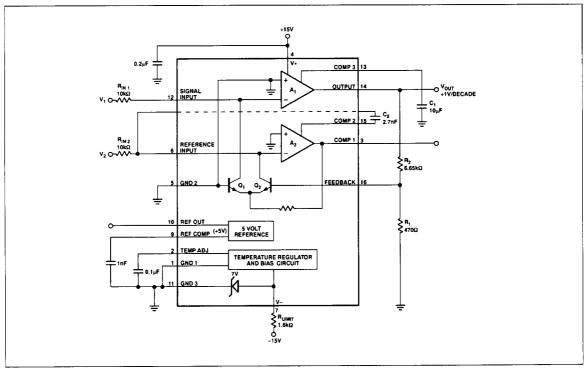

The logging function is realized by placing the antilog element (transistor pair) in the feedback loop of the output converter amplifier (A<sub>1</sub>) as shown in the block diagram. As shown in Figure 1, the loop is closed and the conversion is scaled with feedback resistors R<sub>1</sub> and R<sub>2</sub> from pin 16 to pin 14. The high-gain op amps (A<sub>1</sub> and A<sub>2</sub>) have negligible input bias current. These force the collector currents of the high conformance transistor pair to be equal to the input current (pin 12) and the reference current (pin 6).

Referring to equation (1), the input current becomes  $I_{C1}$  and the reference current  $I_{C2}$ , while delta  $V_{IN}$  is  $V_{BASE}$ ,  $Q_2$  or  $V_{18}$ , since the base of  $Q_1$  is ground. Here, the output amplifier  $A_1$  forces the base of  $Q_2$  to be at the appropriate voltage governed by equation (1) and the collector currents of  $Q_1$  and  $Q_2$ . With the reference current set at 1 mA, the input current operates at less than or equal to 1 mA. In the case of the inverting log amp, as the input current decreases, the  $V_{BE}$  of  $Q_1$  decreases which increases  $V_{16}$  or  $V_{OUT}$  since the  $V_{BE}$  of  $Q_2$  is fixed.

FIGURE 1: Basic Principle of Operation

NOTE: The output amplifier can only swing to approximately 1.5V below ground and sinks about 300µA. For this reason, they are used only with positive output voltages. For bipolar amplifier output, see Figure 7 in the Log Ratio section.

Equation (1) can be rewritten:

$$V_{16} = kT/q \text{ in } (I_{REF}/I_{IN})$$

(2)

converting to base 10:

$$V_{16} = 2.303 \text{ kT/q LOG}_{10} (I_{BEF}/I_{IN})$$

(3)

Figure 1 shows the feedback which produces the output scale factor:

$$V_{OUT} = V_{18} (R_2/(R_1 + R_2))$$

(4)

Substituting into equation 3 yields:

$$V_{OUT} = 2.303 \text{ kT/q} (R_1 + R_2)/R_1 LOG_{10} (I_{REF}/I_{IN})$$

(5)

Letting

$$K = 2.303 \, kT/q \, (R_1 + R_2)/R_2$$

(6)

or K = 0.066 (R<sub>1</sub> + R<sub>2</sub>)/R<sub>2</sub> (usually set to 1V/decade with R<sub>2</sub> =  $470\Omega$ )

For current-mode operation:

$$V_{OUT} = K LOG_{10} (I_{REF}/I_{IN})$$

(7)

For voltage-mode operation:

$$V_{OUT} = K LOG_{10} (V_{REF}/V_{IN} \times R_{IN}/R_{REF})$$

(8)

Since both op amp inputs rest at virtual ground, the reference and input currents can easily be generated by applied voltages through external resistors without generating excessive errors.

For the best results, the input and reference currents should be kept below 1mA.

A 5V reference has been included on chip for applications requiring a true log function (rather than a log ratio function).

#### INPUTS

As with all log amplifiers, the SSM-2100 has a limited dynamic range of 3 decades for voltage inputs. This is partially due to input offset voltage (trimmable) and various second order effects.

For the widest dynamic range, current-mode operation is recommended. The device can handle 5 decades of current input untrimmed and at least 6 decades when trimmed. Similarly, when operating in the log ratio mode, the device can handle 10 decades and 12 decades, respectively.

In order to ensure unconditional stability when operating with true current inputs, it is important to shunt the signal input to ground with a  $10k\Omega$  resistor and a 10nF capacitor in series.

## **NEGATIVE POWER SUPPLY CONSIDERATIONS**

Because the negative power suppply is regulated at -7V, it is necessary to add a current limiting resistor ( $R_{LIMIT}$ ) in series with pin 7. When using -15V for V-, a value of  $1.6k\Omega$  is recommended for  $R_{LIMIT}$ . This will keep the voltage at pin 7 very stable and useful for external trimming. Note that the negative power supply is internally regulated and needs no decoupling.

## POSITIVE POWER SUPPLY CONSIDERATIONS

Because of the high gain of the temperature regulator circuit, generous positive supply decoupling should be used. The  $0.2\mu F$  decoupling capacitor shown on the application circuits should be of ceramic type and mounted as close to pins 1 and 4 as possible. It should also be noted than pin 1 carries all the heater current and care should be taken when laying out ground lines to prevent this from causing errors.

#### **TEMPERATURE CONTROL**

The internal chip temperature is regulated at about 60°C if the temperature adjustment (pin 12) is not used. This on-board substrate temperature regulator stabilizes the scale factor and reduces drift of the reference.

The regulated chip temperature can be increased or decreased by the use of pin 2. To decrease the temperature by  $n^{\circ}C$ , connect a resistor of the value 3.5n M $\Omega$  between pin 2 and 10. To increase the temperature by  $n^{\circ}C$ , connect a resistor of the value 6/n M $\Omega$  between pins 2 and 7.

In some applications such as those requiring low power, the temperature regulator can be disabled entirely. This is accomplished by connecting a  $100 k\Omega$  resistor between pins 2 and 4 (V+). In this case, the reference drift is about  $70 pm/^{\circ}C$ . The scale factor drift can be compensated by using a temperature compensating resistor\* for  $R_2$ .

# **APPLICATIONS**

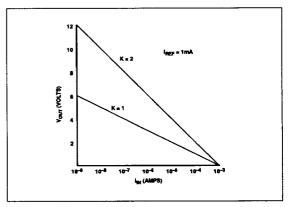

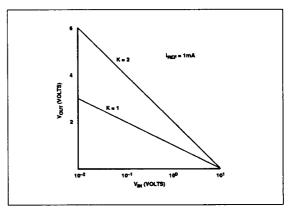

The SSM-2100 can be connected for voltage or current logging functions. Figures 2a and 2b show the transfer characteristics of the inverting log amplifier for current and voltage mode operation.

FIGURE 2a: Inverting Log Amp with Current Input

FIGURE 2b: Inverting Log Amp with Voltage Input

<sup>\*</sup> RCD Components, Inc. Part Number LP1/4, 3301 Bedford Street, Manchester, NH U.S.A., (603) 669-0054, Telex 943512

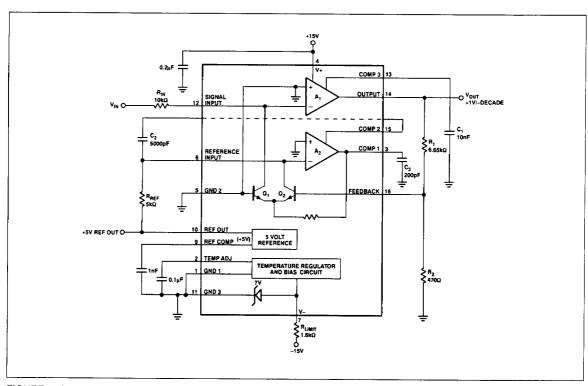

#### **INVERTING LOG AMPLIFIER**

Figure 3 shows the SSM-2100 configured in the inverting log mode. Setting  $I_{IN} = I_{REF}$  with  $V_{IN} = 10V$ , the output will be zero and increase by 1V/decade as  $I_{IN}$  is decreased. Whereas  $V_{IN}$  can be varied proportionally by varying  $R_{IN}$ , a 10V input optimizes the dynamic range with  $\pm 15V$  supplies.

To vary the scale factor, it is best to change  $R_1$ . To alter the output offset at a given input voltage, adjust  $R_{\rm REF}$ . Phase compensation for the circuit is provided by  $C_1$ ,  $C_2$  and  $C_3$ . This scheme yields 30kHz small-signal bandwidth at 1mA input current, 8kHz at  $1\mu A$  and approximately 1.6kHz at 100nA.

FIGURE 3: Inverting Logarithmic Amplifier

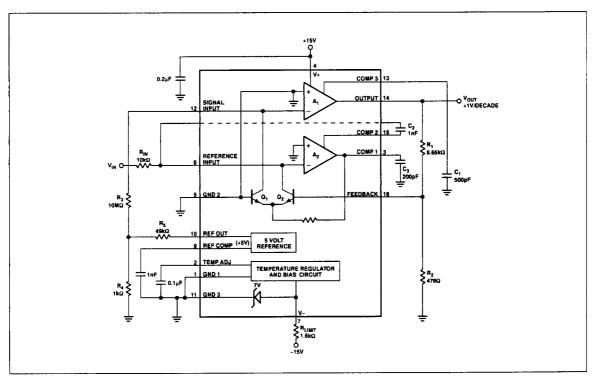

#### NONINVERTING LOG AMPLIFIER

Interchanging the signal and reference inputs yields a noninverting log amplifier as shown in Figure 4. In this configuration, the output crosses zero when the input is five decades below the full-scale value. This can be adjusted by varying  $\mathbf{R}_3$ .

$\rm R_1$  and  $\rm R_2$  can cause a slight inaccuracy because they add to the base resistance of  $\rm Q_1$  and  $\rm Q_2$ . This can be minimized by keeping  $\rm R_1$  and  $\rm R_2$  as small as possible. It is recommended that  $\rm R_2$  = 470  $\!\Omega$ .

The small-signal bandwidth of this circuit is 5kHz with inputs currents from  $1\mu A$  to 1mA. Over the full 5-decade input current range, the bandwidth is better than 2kHz.

FIGURE 4: Noninverting Logarithmic Amplifier

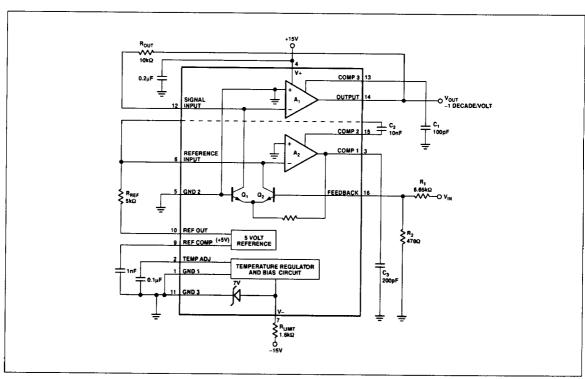

#### **ANTILOG AMPLIFIER**

Figure 5 shows the configuration for the antilog amplifier. The input range for this circuit is zero to 10V which can be adjusted by  $\rm R_1$ . The output scale factor is 1V/decade which can varied by adjusting  $\rm R_{OUT}$ .

The transfer function is also derived from equation (1). In the antilog configuration, the current  $I_{C_1}$  becomes  $I_{OUT}$  and  $V_{BASE}$   $Q_2$  or  $V_{16}$  is  $V_{IN}(R_2/(R_1+R_2))$ . Equation (2) now becomes:

$$V_{IN}(R_2/(R_1 + R_2)) = kT/q \ln(I_{REF}/I_{OUT})$$

(9)

or

$$I_{REF}/I_{OUT} = exp[R_2/(R_1 + R_2) q/kT V_{iN}]$$

0

$$I_{REF} R_{OUT} = V_{OUT} \exp[R_2/(R_1 + R_2) \text{ q/kT } V_{IN}]$$

Converting to base 10 and letting K = 2.303 kT/q (R<sub>1</sub> + R<sub>2</sub>)/R<sub>2</sub> or 0.066(R<sub>1</sub> + R<sub>2</sub>)/R<sub>2</sub> (assuming T = +60°C or 333°K)

the final antilog transfer function becomes:

$$V_{OUT} = I_{REF} R_{OUT} / 10^{(VIN R2/.066 (R1 + R2))}$$

or

$$V_{OUT} = I_{REF} R_{OUT} / 10^{[VIN/K]}$$

To set K =

$$1V/\text{decade}$$

,  $R_2/(R_1 + R_2) = 0.066$

If

$$R_p = 470\Omega$$

,  $R_1 = 6.65k\Omega$

The bandwidth of the antilog amplifier circuit is approximately 500kHz.

FIGURE 5: Antilogarithmic Amplifier

FIGURE 6: Log Ratio Amplifier,  $V_{OUT} = K LOG (V_2/V_1)$ , K = 1V/Decade with Values Shown

# LOG RATIO AMPLIFIER

The output of the log ratio amplifier is proportional to the ratio of its two input signals. The SSM-2100 is very well suited to this application because both the signal and reference inputs operate at true virtual ground. This eliminates the need for an external true current source as required by other types of log amplifiers.

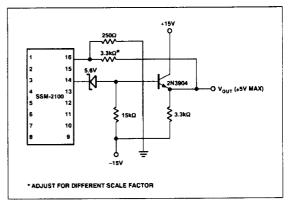

The log ratio amplifier shown in Figure 6 has a dynamic range of  $10^5$  to  $10^{-1}$  if the output buffer of Figure 7 is not used. This is because the output amplifier (A $_{\uparrow}$ ) can swing to a minimum of about 1.5V below ground and can only sink about 300 $\mu$ A maximum. Thus, the input current should not be more than one decade below the reference current.

For full four-quadrant operation, however, refer to the output buffer of Figure 7. The addition of this circuit will provide a  $\pm 5V$  output for reference/signal ratios from  $10^5$  to  $10^{-5}$  for a full 10-decade range.

FIGURE 7: Modification of Figure 6 for Four-Quadrant Operation

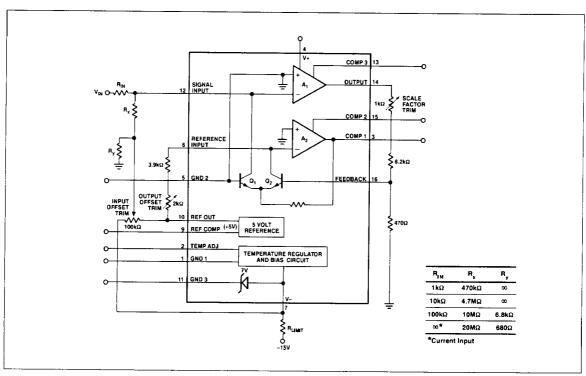

#### TRIMMING THE SSM-2100

Figure 8 shows the general trimming technique for the log and log ratio applications shown in Figures 3, 4 and 6. The trim schemes for scale factor  $(R_1)$ , input offset  $(R_x, R_y)$ , and output offset  $(R_{REF})$  factor are shown. For log ratio applications, the input offset trim can be duplicated for the reference input.

The scale factor trim scheme is identical in all applications. Simply replace R, with a 6.2k $\Omega$  resistor and 1k $\Omega$  potentiometer.

Input offset trimming removes errors from input bias current as well as amplifier offset. For optimum trim integrity, the use of the positive and negative reference voltages yields high rejection to variations in power supply voltages.

Output offset errors are essentially due to the mismatch between the base-emitter voltages of  $\mathbf{Q}_1$  and  $\mathbf{Q}_2$ . The output offset adjustment  $(\mathsf{R}_{\mathsf{REF}})$  scheme shown applies to the inverting log amp and the antilog amplifier. Output offset is adjusted in the noninverting log amplifier by changing  $\mathsf{R}_5$  in Figure 4. To adjust out the equivalent error in the log ratio amplifier, replace either of the  $10\mathrm{k}\Omega$  input resistors with a  $9\mathrm{k}\Omega$  resistor and  $2\mathrm{k}\Omega$  potentiometer.

Unlike an operational amplifier, a log amp can not be trimmed with  $V_{\rm IN}$  = 0 since the log of zero would theoretically produce an infinite output voltage.

#### LOG AMPLIFIER TRIM PROCEDURE

Log amp trim for K = 1:

- Apply full-scale input voltage or current and adjust output offset for the proper output.

- Apply an input signal one decade down from full-scale and adjust the scale factor for the desired output.

- Finally, with the minimum input signal applied, adjust the input offset trim for the correct minimum scale output voltage or current.

## **ANTILOG AMPLIFIER TRIM PROCEDURE**

Antilog trimming for K = 1:

- 1. Set full-scale by grounding  $\rm V_{IN}$  and adjusting the output offset trim until  $\rm V_{OUT}$  is 10V.

- 2. Apply 1V to V<sub>IN</sub> and adjust the scale factor for 1V output.

- Set the V<sub>IN</sub> to the maximum value to be used and adjust input offset trim for the minimum desired output. Using K = 1, adjust for V<sub>OUT</sub> of 0.1V with V<sub>IN</sub> at 2V.

FIGURE 8: Trimming the SSM-2100